### SONY

### **CXD3048**R

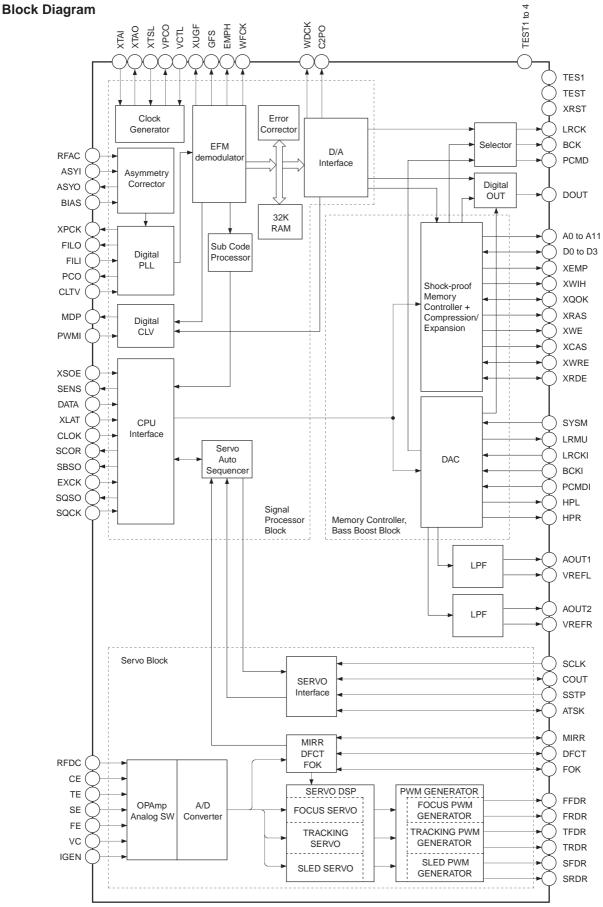

#### CD Digital Signal Processor with Built-in Digital Servo + Shock-proof Memory Controller + Digital High & Bass Boost

#### Description

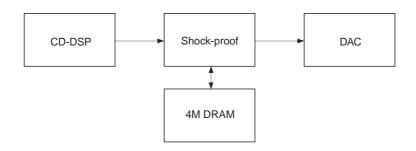

The CXD3048R is a digital signal processor LSI for CD players. This LSI incorporates a digital servo, high & bass boost, shock-proof memory controller, 1-bit DAC and analog low-pass filter.

#### **Features**

- · All digital signal processing during playback is performed with a single chip

- Highly integrated mounting possible due to a built-in RAM

#### **Digital Signal Processor (DSP) Block**

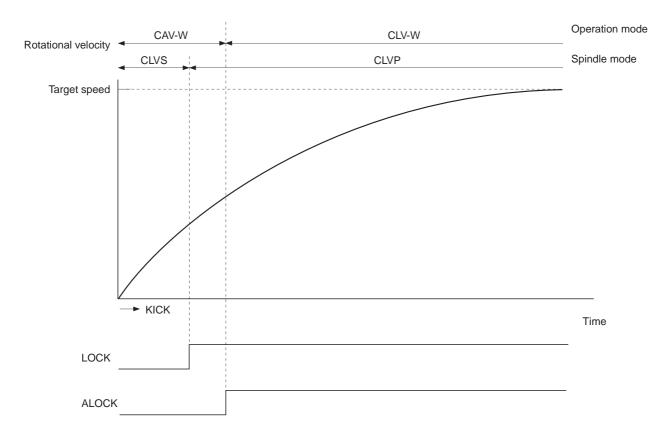

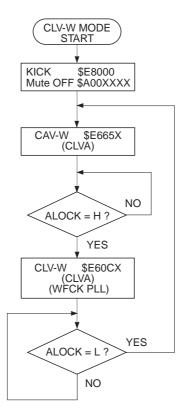

• Supports CAV (Constant Angular Velocity) playback

- Frame jitter free

- 0.5× to 4× speed continuous playback possible

- Allows relative rotational velocity readout

- · Wide capture range playback mode

- Spindle rotational velocity following method

- Supports 1× to 4× speed playback

- Supports variable pitch playback

- . The bit clock, which strobes the EFM signal, is generated by the digital PLL.

- · EFM data demodulation

- Enhanced EFM frame sync signal protection

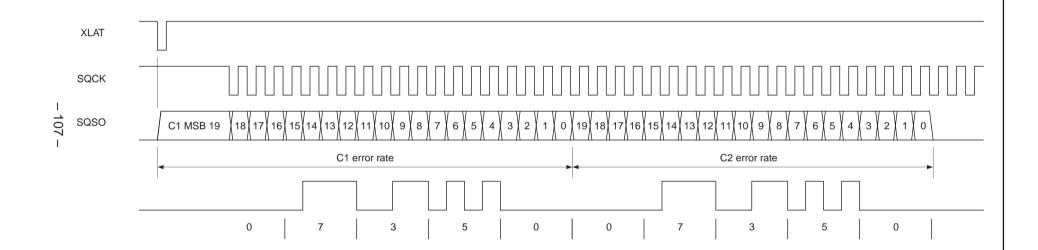

- Refined super strategy-based powerful error correction C1: double correction, C2: quadruple correction Supported during 4× speed playback

- Noise reduction during track jumps

- Auto zero-cross mute

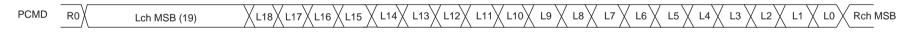

- Subcode demodulation and subcode-Q data error detection

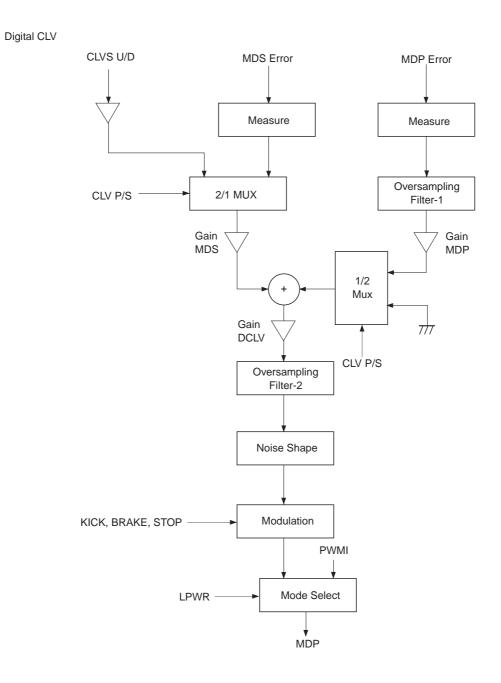

- · Digital spindle servo

- 16-bit traverse counter

- · Asymmetry correction circuit

- · CPU interface on serial bus

- · Error correction monitor signal, etc. output from a new CPU interface

- · Servo auto sequencer

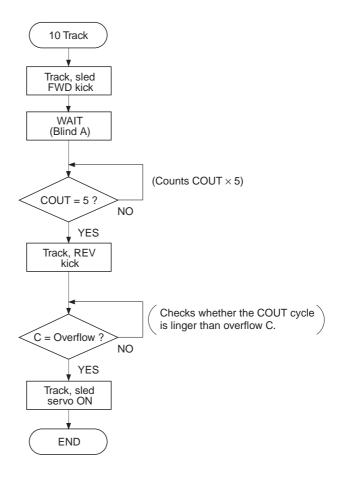

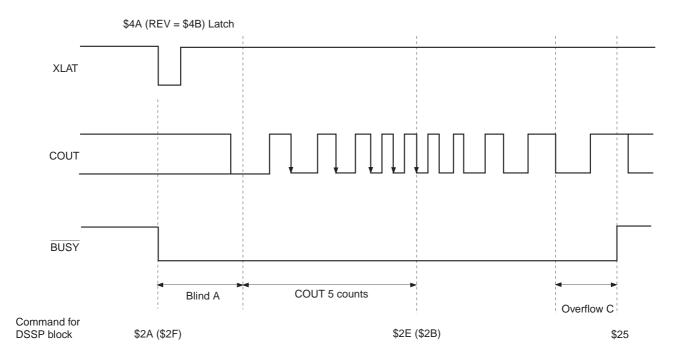

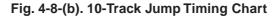

- Fine search performs track jumps with high accuracy

- · Digital audio interface outputs

- · Digital level meter, peak meter

- Bilingual compatible

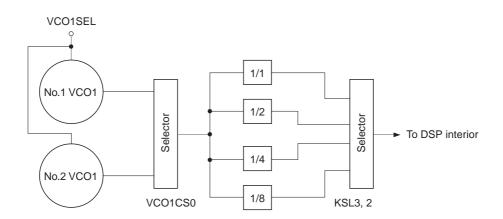

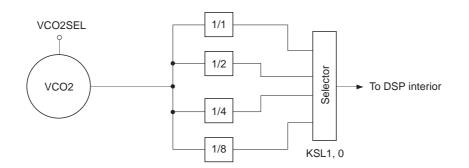

- VCO control mode

- CD TEXT data demodulation

- · Digital Out can be generated from the audio serial input. (also supported after shock-proof and digital bass boost processing, subcode-Q addition function)

#### **Digital Servo (DSSP) Block**

- Microcomputer software-based flexible servo control

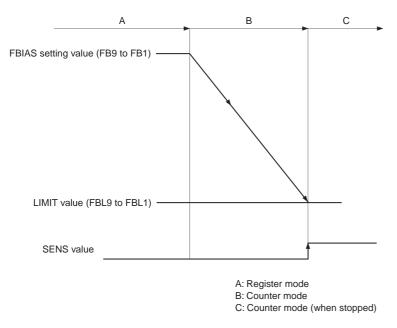

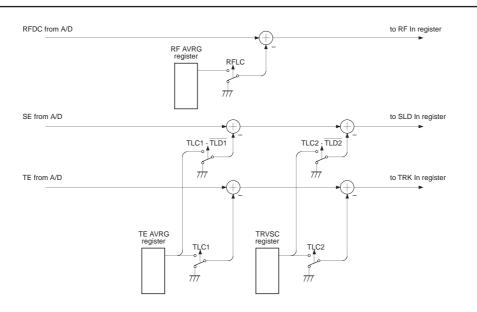

- Offset cancel function for servo error signal

- Auto gain control function for servo loop

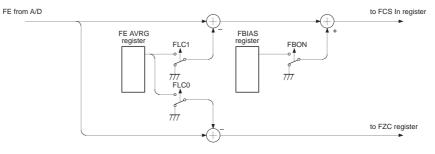

- E:F balance, focus bias adjustment functions

- · Surf jump function supporting micro two-axis

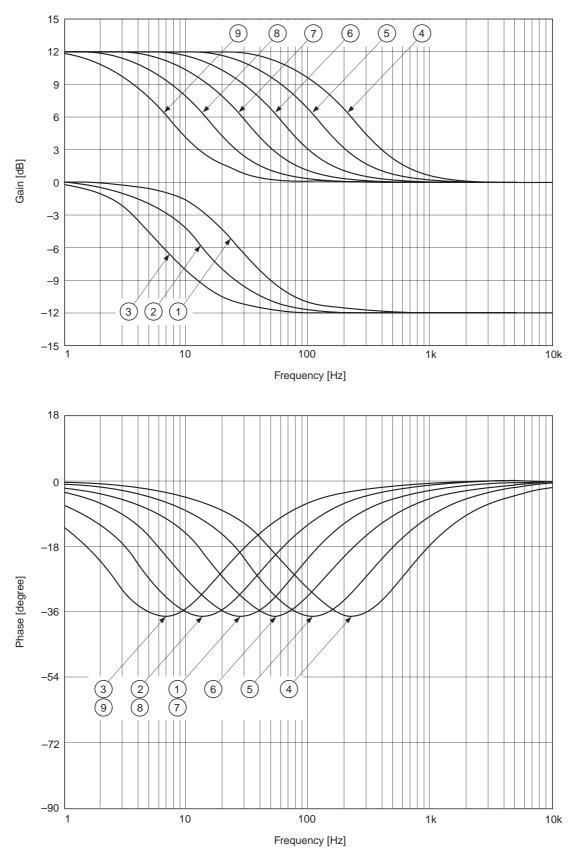

- Tracking filter: 6 stages Focus filter: 5 stages

#### **Shock-proof Memory Controller Block**

#### Supports an external 4M-bit/16M-bit DRAM

- · Time axis-based data linking

- ADPCM compression method (uncompressed/4 bits/ 6 bits/8 bits)

#### Digital Filter, DAC and Analog Low-pass Filter Blocks

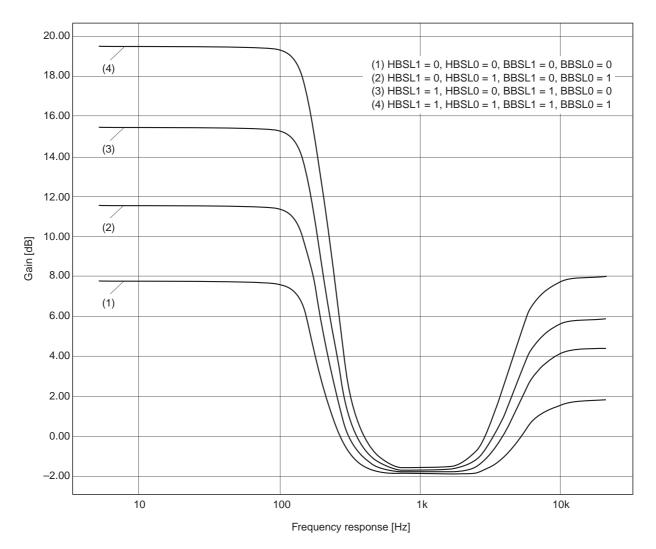

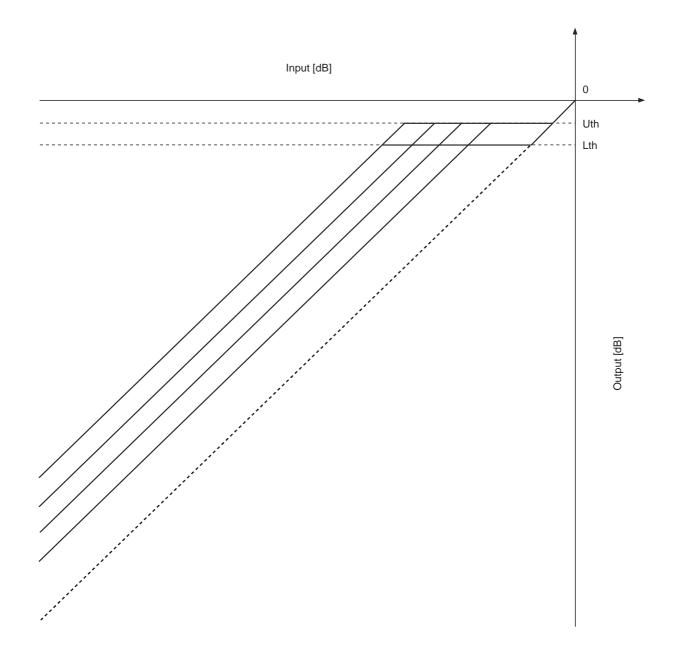

- Digital dynamic bass boost and high boost Bass Boost: 4th-order IIR 24dB/Oct +10dB/+14dB/+18dB/+22dB

- High Boost: Second-order IIR 12dB/Oct +4dB/+6dB/+8dB/+10dB

- Independent turnover frequency selection possible Bass Boost: 125Hz/160Hz/200Hz High Boost: 5kHz/7kHz

- Digital dynamics (compressor)

- Volume increased by +5dB at low level • 8× oversampling digital filter

- (attenuation: 61dB, ripple within band: ±0.0075dB)

- Digital signal output possible after boost

- Serial data format selectable from (output) 20 bits/ 18 bits/16 bits (rearward truncation, MSB first)

- Digital attenuation: -∞, -60 to +6dB, 2048 steps (linear)

- Soft mute

- · Digital de-emphasis

- High-cut filter

#### Applications

CD players

#### Structure

Silicon gate CMOS IC

#### **Absolute Maximum Ratings**

- Supply voltage VDD, AVDD Vss - 0.5 to +3.5 V Input voltage Vı Vss - 0.3 to Vpp + 0.3V

- Output voltage Vo Vss - 0.3 to Vpp + 0.3 V °C

- Storage temperature Tstg -55 to +150

- Supply voltage difference -0.3 to +0.3 ν AVss – Vss -0.3 to +0.3V (AVDD < 1.7V) AVdd - Vdd

#### -0.3 to +1.0V (AVDD = 1.7 to 2.7V) AVdd - Vdd

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul>             |            |    |

|------------------------------------------------|------------|----|

| VDD, AVDD0, 3, XVDD                            | 1.7 to 2.7 | V  |

| AVDD1, 2, DVDD                                 | VDD to 2.7 | V  |

| <ul> <li>Operating temperature Topr</li> </ul> | -20 to +75 | °C |

|                                                |            |    |

#### I/O Pin Capacitance

| <ul> <li>Input capacitance</li> </ul> | Cı        | 7 (max.)      | pF |

|---------------------------------------|-----------|---------------|----|

| Output capacitance                    | Co        | 7 (max.)      | pF |

| Note) Measurement co                  | onditions | VDD = VI = 0V |    |

| -                                     |           | fм = 1MHz     |    |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

-2-

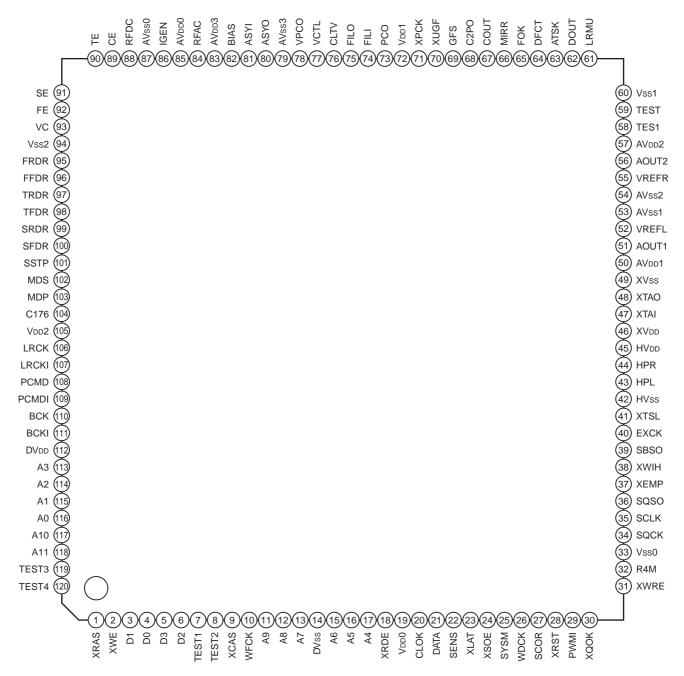

#### **Pin Configuration**

#### **Pin Description**

| Power<br>supply |    | Symbol | I/O | Value   | Description                                                                                                                    |

|-----------------|----|--------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------|

|                 | 1  | XRAS   | 0   | 1, 0    | DRAM row address strobe signal.                                                                                                |

|                 | 2  | XWE    | 0   | 1, 0    | DRAM data input enable signal.                                                                                                 |

|                 | 3  | D1     | I/O | 1, 0    | DRAM data bus 1.                                                                                                               |

|                 | 4  | D0     | I/O | 1, 0    | DRAM data bus 0.                                                                                                               |

|                 | 5  | D3     | I/O | 1, 0    | DRAM data bus 3.                                                                                                               |

|                 | 6  | D2     | I/O | 1, 0    | DRAM data bus 2.                                                                                                               |

|                 | 7  | TEST1  | 0   |         | Test pin. Do not connect.                                                                                                      |

|                 | 8  | TEST2  | 0   |         | Test pin. Do not connect.                                                                                                      |

|                 | 9  | XCAS   | 0   | 1, 0    | DRAM column address strobe signal.                                                                                             |

| DRAM<br>I/F     | 10 | WFCK   | 0   | 1, 0    | WFCK output. XOE is output by switching with the command.                                                                      |

|                 | 11 | A9     | 0   | 1, 0    | DRAM address 9.                                                                                                                |

|                 | 12 | A8     | 0   | 1, 0    | DRAM address 8.                                                                                                                |

|                 | 13 | A7     | 0   | 1, 0    | DRAM address 7.                                                                                                                |

|                 | 14 | DVss   | —   |         | DRAM interface GND.                                                                                                            |

|                 | 15 | A6     | 0   | 1, 0    | DRAM address 6.                                                                                                                |

|                 | 16 | A5     | 0   | 1, 0    | DRAM address 5.                                                                                                                |

|                 | 17 | A4     | 0   | 1, 0    | DRAM address 4.                                                                                                                |

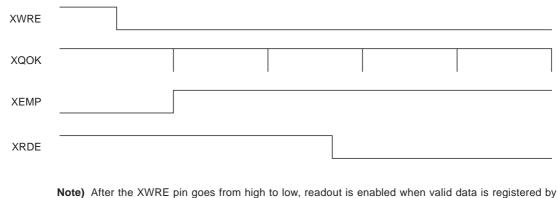

|                 | 18 | XRDE   | I/O | 1, 0    | DRAM readout enable signal input. XRDE monitor is output by switching with the command.                                        |

|                 | 19 | Vdd0   | —   | —       | Digital power supply.                                                                                                          |

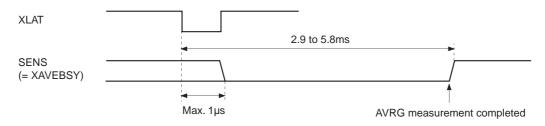

|                 | 20 | CLOK   | I   |         | Serial data transfer clock input from CPU. SQSO and SENS readout clocks are output by switching with the command.              |

|                 | 21 | DATA   | Ι   |         | Serial data input from CPU.                                                                                                    |

|                 | 22 | SENS   | 0   | 1, Z, 0 | SENS output to CPU. SQSO data is output by switching with the command.                                                         |

|                 | 23 | XLAT   | I   |         | Latch input from CPU. The serial data is latched at the falling edge. XLAT which is low for $6\mu s$ or more is enabled.       |

|                 | 24 | XSOE   | Ι   |         | Clock input mode switching from CPU. Valid when \$A4 ENXSOE = 1.                                                               |

| Disting         | 25 | SYSM   | I   |         | Mute input. Muted when high.                                                                                                   |

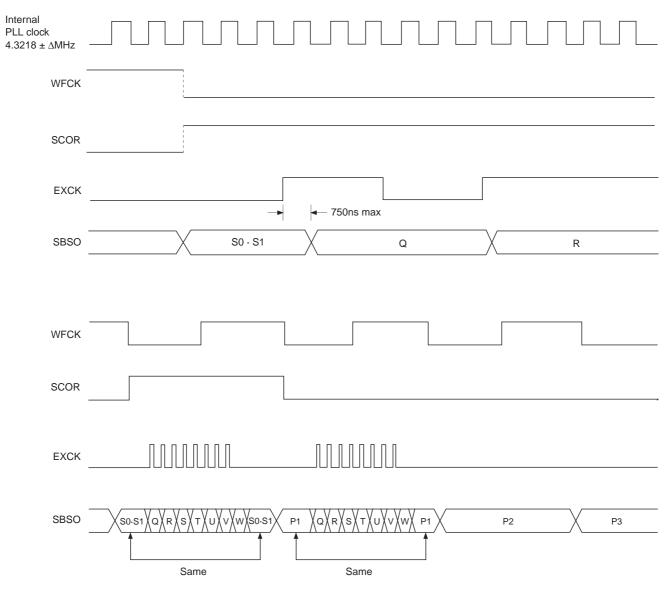

| Digital         | 26 | WDCK   | 0   | 1, 0    | Word clock output $f = 2Fs$ . GRSCOR is output by switching with the command.                                                  |

|                 | 27 | SCOR   | 0   | 1, 0    | High output when the subcode sync is detected. SCOR, which is interpolated in the IC, is output by switching with the command. |

|                 | 28 | XRST   | Ι   |         | System reset. Reset when low.                                                                                                  |

|                 | 29 | PWMI   | Ι   |         | Spindle motor external control input.                                                                                          |

|                 | 30 | XQOK   | I/O | 1, 0    | Subcode Q OK input. XQOK monitor is output by switching with the command.                                                      |

|                 | 31 | XWRE   | I/O | 1, 0    | DRAM write enable signal input. XWRE monitor is output by switching with the command.                                          |

| Power<br>supply                           |           | Symbol | I/O | Value                    | Description                                                                                                                                |  |  |  |  |

|-------------------------------------------|-----------|--------|-----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                           | 32        | R4M    | 0   | 1, 0                     | Microcomputer clock output. R8M and C4M are output by switching with the command.                                                          |  |  |  |  |

|                                           | 33        | Vss0   | —   | —                        | Digital GND.                                                                                                                               |  |  |  |  |

|                                           | 34        | SQCK   | Ι   |                          | SQSO readout clock input.                                                                                                                  |  |  |  |  |

|                                           | 35 SCLK I |        |     |                          | SENS serial data readout clock input.                                                                                                      |  |  |  |  |

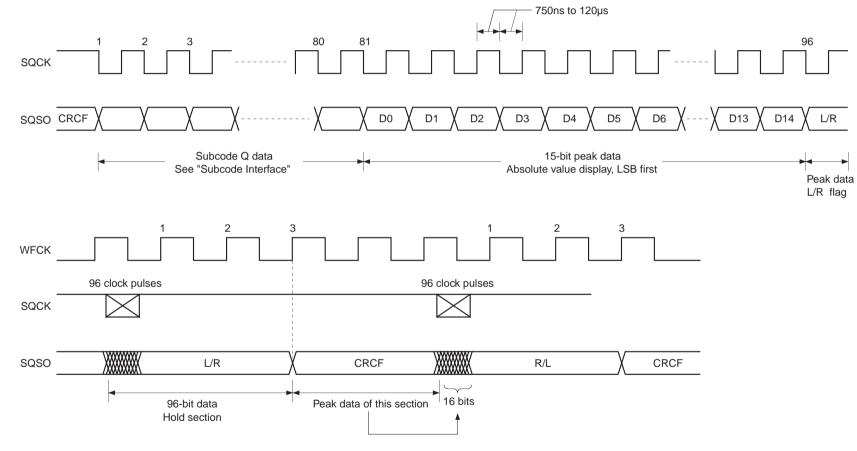

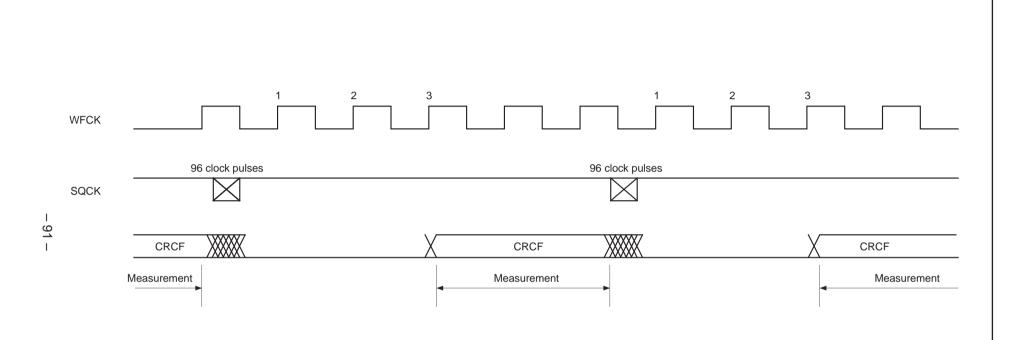

| Digital                                   | 36        | SQSO   | 0   | 1, 0                     | Subcode Q 80-bit and PCM peak and level data output. CD TEXT data output.                                                                  |  |  |  |  |

|                                           | 37        | XEMP   | 0   | 1, 0                     | RAM readout prohibited signal.                                                                                                             |  |  |  |  |

|                                           | 38        | XWIH   | 0   | 1, 0                     | Write to DRAM prohibited signal.                                                                                                           |  |  |  |  |

|                                           | 39        | SBSO   | 0   | 1, 0                     | Subcode P to W serial output.                                                                                                              |  |  |  |  |

|                                           | 40        | EXCK   | Ι   |                          | SBSO readout clock input.                                                                                                                  |  |  |  |  |

|                                           | 41        | XTSL   | I   |                          | Crystal selection input. Low when the crystal is 16.9344MHz; high when the crystal is 33.8688MHz.                                          |  |  |  |  |

|                                           | 42        | HVss   | _   | —                        | Headphone GND.                                                                                                                             |  |  |  |  |

|                                           | 43        | HPL    | 0   | 1, 0                     | Lch headphone PDM output.                                                                                                                  |  |  |  |  |

| H/P                                       | 44        | HPR    | 0   | 1, 0                     | Rch headphone PDM output.                                                                                                                  |  |  |  |  |

|                                           | 45        | HVdd   | —   | —                        | Headphone power supply.                                                                                                                    |  |  |  |  |

|                                           | 46        | XVdd   |     |                          | Master clock power supply.                                                                                                                 |  |  |  |  |

| X'tal                                     | 47        | XTAI   | I   |                          | Crystal oscillation circuit input. The master clock is externally input from this pin.                                                     |  |  |  |  |

|                                           | 48        | XTAO   | 0   |                          | Crystal oscillation circuit output.                                                                                                        |  |  |  |  |

|                                           | 49        | XVss   |     |                          | Master clock GND.                                                                                                                          |  |  |  |  |

|                                           | 50        | AVdd1  | _   | —                        | Analog power supply.                                                                                                                       |  |  |  |  |

|                                           | 51        | AOUT1  | 0   | Analog                   | Lch analog output.                                                                                                                         |  |  |  |  |

| Lch                                       | 52        | VREFL  | 0   | Analog                   | Lch reference voltage.                                                                                                                     |  |  |  |  |

|                                           | 53        | AVss1  | _   | —                        | Analog GND.                                                                                                                                |  |  |  |  |

|                                           | 54        | AVss2  | —   | —                        | Analog GND.                                                                                                                                |  |  |  |  |

|                                           | 55        | VREFR  | 0   | Analog                   | Rch reference voltage.                                                                                                                     |  |  |  |  |

| Rch                                       | 56        | AOUT2  | 0   | Analog                   | Rch analog output.                                                                                                                         |  |  |  |  |

|                                           | 57        | AVdd2  | —   | —                        | Analog power supply.                                                                                                                       |  |  |  |  |

|                                           | 58        | TES1   | Ι   |                          | Test pin. Normally GND.                                                                                                                    |  |  |  |  |

|                                           | 59        | TEST   | Ι   |                          | Test pin. Normally GND.                                                                                                                    |  |  |  |  |

|                                           | 60        | Vss1   | _   | —                        | Digital GND.                                                                                                                               |  |  |  |  |

| Digital                                   | 61        | LRMU   | 0   | 1, 0                     | OR signal output of Lch, Rch "0" detection flag (AND output) and SYSM.<br>Only "0" detection flag is output by switching with the command. |  |  |  |  |

|                                           | 62        | DOUT   | 0   | 1, 0                     | Digital Out output.                                                                                                                        |  |  |  |  |

| 63 ATSK I/O 1, 0 Anti-shock input/output. |           |        |     | Anti-shock input/output. |                                                                                                                                            |  |  |  |  |

| 64 DFCT I/O 1,0                           |           |        | I/O | 1, 0                     | Defect signal input/output.                                                                                                                |  |  |  |  |

|                                           | 65        | FOK    | I/O | 1, 0                     | Focus OK signal input/output.                                                                                                              |  |  |  |  |

| Power<br>supply |     | Symbol | I/O | Value   | Description                                                                           |

|-----------------|-----|--------|-----|---------|---------------------------------------------------------------------------------------|

|                 | 66  | MIRR   | I/O | 1, 0    | Mirror signal input/output.                                                           |

|                 | 67  | COUT   | I/O | 1, 0    | Track number count signal input/output. SCOR is output by switching with the command. |

|                 | 68  | C2PO   | 0   | 1, 0    | C2PO output. MNT3 and GTOP are output by switching with the command.                  |

| Digital         | 69  | GFS    | 0   | 1, 0    | GFS output. MNT2 and XROF are output by switching with the command.                   |

|                 | 70  | XUGF   | 0   | 1, 0    | XUGF output. MNT0, RFCK, C4M and QRCVD are output by switching with the command.      |

|                 | 71  | XPCK   | 0   | 1, 0    | XPCK output. MNT1, FSTO and GTOP are output by switching with the command.            |

|                 | 72  | Vdd1   | —   |         | Digital power supply.                                                                 |

|                 | 73  | PCO    | 0   | 1, Z, 0 | Master PLL charge pump output.                                                        |

|                 | 74  | FILI   | I   |         | Master PLL filter input.                                                              |

|                 | 75  | FILO   | 0   | Analog  | Master PLL (slave = digital PLL) filter output.                                       |

|                 | 76  | CLTV   | I   |         | Multiplier VCO1 control voltage input.                                                |

|                 | 77  | VCTL   | Ι   |         | Wide-band EFM PLL VCO2 control voltage input.                                         |

|                 | 78  | VPCO   | 0   | 1, Z, 0 | Wide-band EFM PLL charge pump output.                                                 |

| ASYM            | 79  | AVss3  | _   |         | Analog GND.                                                                           |

|                 | 80  | ASYO   | 0   | 1, 0    | EFM full-swing output (low = Vss, high = VDD).                                        |

|                 | 81  | ASYI   | I   |         | Asymmetry comparator voltage input.                                                   |

|                 | 82  | BIAS   | I   |         | Asymmetry circuit constant current input.                                             |

|                 | 83  | AVdd3  | _   |         | Analog power supply.                                                                  |

|                 | 84  | RFAC   | Ι   |         | EFM signal input.                                                                     |

|                 | 85  | AVdd0  | —   |         | Analog power supply.                                                                  |

|                 | 86  | IGEN   | I   |         | Operational amplifier constant current input.                                         |

|                 | 87  | AVss0  | _   |         | Analog GND.                                                                           |

|                 | 88  | RFDC   | I   |         | RF signal input.                                                                      |

| A/D             | 89  | CE     | I   |         | Center servo analog input or E input.                                                 |

|                 | 90  | TE     | Ι   |         | Tracking error signal input or F input.                                               |

|                 | 91  | SE     | I   |         | Sled error signal input or B input.                                                   |

|                 | 92  | FE     | I   |         | Focus error signal input or A input.                                                  |

|                 | 93  | VC     | I   |         | Center voltage input.                                                                 |

|                 | 94  | Vss2   | _   |         | Digital GND.                                                                          |

|                 | 95  | FRDR   | 0   | 1, 0    | Focus drive output.                                                                   |

|                 | 96  | FFDR   | 0   | 1, 0    | Focus drive output.                                                                   |

| Digital         | 97  | TRDR   | 0   | 1, 0    | Tracking drive output.                                                                |

|                 | 98  | TFDR   | 0   | 1, 0    | Tracking drive output.                                                                |

|                 | 99  | SRDR   | 0   | 1, 0    | Sled drive output.                                                                    |

|                 | 100 | SFDR   | 0   | 1, 0    | Sled drive output.                                                                    |

| Power<br>supply | 1   | Symbol | I/O | Value   | Description                                                                             |

|-----------------|-----|--------|-----|---------|-----------------------------------------------------------------------------------------|

|                 | 101 | SSTP   | I   |         | Disc innermost detection signal input.                                                  |

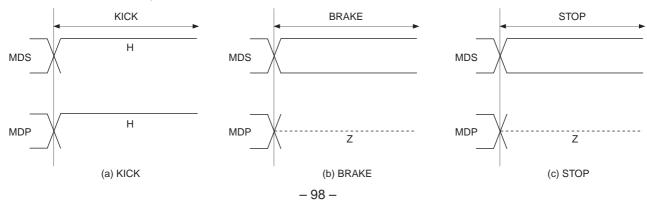

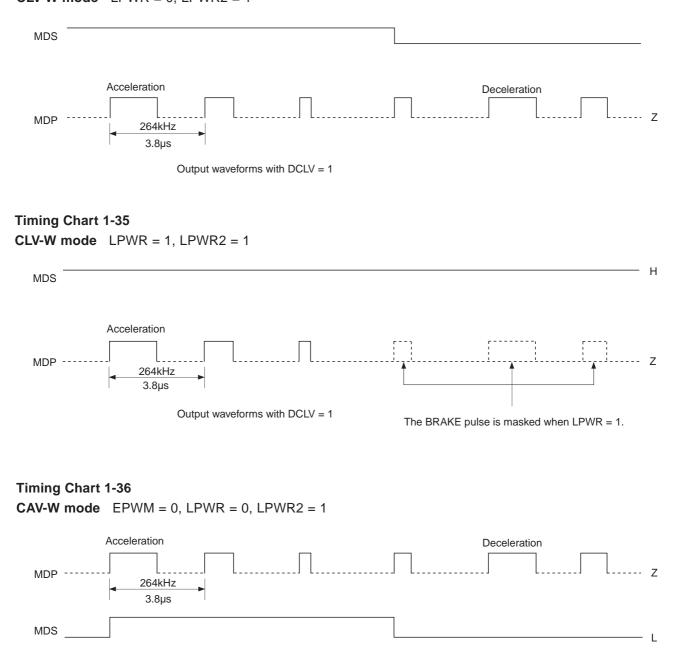

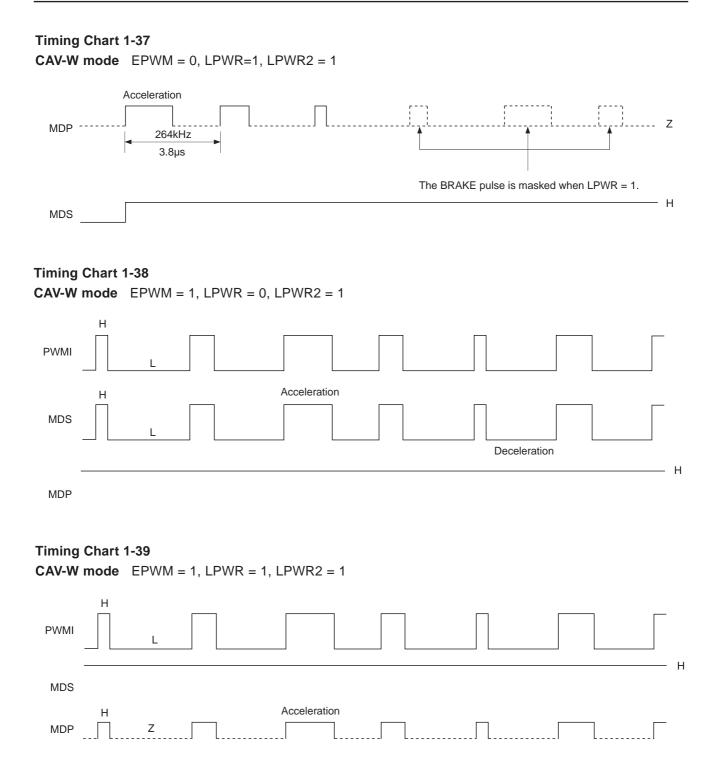

|                 | 102 | MDS    | 0   | 1, Z, 0 | Spindle drive output.                                                                   |

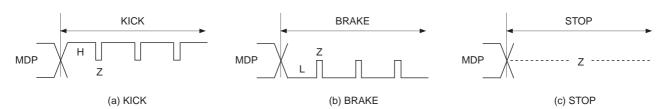

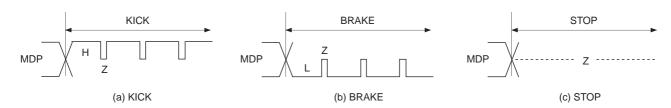

| Digital         | 103 | MDP    | 0   | 1, Z, 0 | Spindle motor servo control output.                                                     |

| Digital         | 104 | C176   | 0   | 1, 0    | 176.4kHz output. 88.2kHz for quasi-double speed setting.<br>Low output when XRST = low. |

|                 | 105 | Vdd2   | —   |         | Digital power supply.                                                                   |

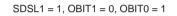

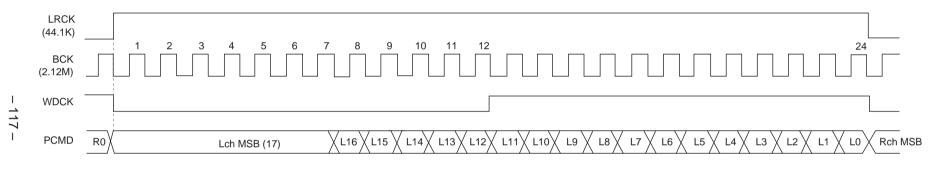

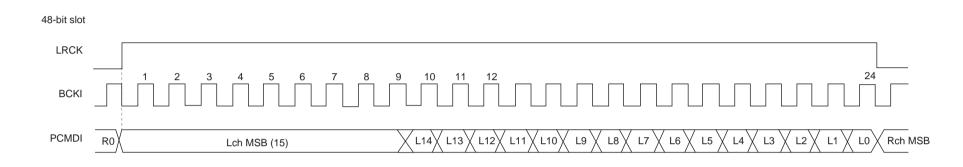

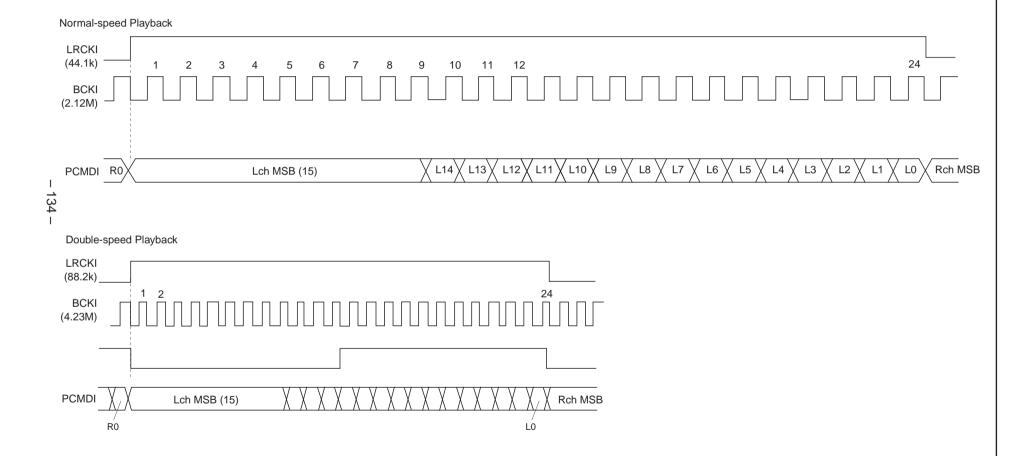

|                 | 106 | LRCK   | 0   | 1, 0    | D/A interface. LR clock output f = Fs.                                                  |

|                 | 107 | LRCKI  | I   |         | D/A interface. LR clock input.                                                          |

|                 | 108 | PCMD   | 0   | 1, 0    | D/A interface. Serial data output. (two's complement, MSB first)                        |

|                 | 109 | PCMDI  | Ι   |         | D/A interface. Serial data input. (two's complement, MSB first)                         |

|                 | 110 | BCK    | 0   | 1, 0    | D/A interface. Bit clock output.                                                        |

|                 | 111 | BCKI   | Ι   |         | D/A interface. Bit clock input.                                                         |

|                 | 112 | DVdd   |     |         | DRAM interface power supply.                                                            |

| DRAM            | 113 | A3     | 0   | 1, 0    | DRAM address 3.                                                                         |

| I/F             | 114 | A2     | 0   | 1, 0    | DRAM address 2.                                                                         |

|                 | 115 | A1     | 0   | 1, 0    | DRAM address 1.                                                                         |

|                 | 116 | A0     | 0   | 1, 0    | DRAM address 0.                                                                         |

|                 | 117 | A10    | 0   | 1, 0    | DRAM address 10.                                                                        |

|                 | 118 | A11    | I/O | 1, 0    | DRAM address 11. Write prohibition factor is input by switching with the command.       |

|                 | 119 | TEST3  | 0   |         | Test pin. Do not connect.                                                               |

|                 | 120 | TEST4  | 0   |         | Test pin. Do not connect.                                                               |

Notes) • PCMD is a MSB first, two's complement output.

- GTOP is used to monitor the frame sync protection status. (High: sync protection window released.)

- XUGF is the frame sync obtained from the EFM signal, and is negative pulse. It is the signal before sync protection.

- XPCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the EFM signal transition point coincide.

- The GFS signal goes high when the frame sync and the insertion protection timing match.

- RFCK is derived from the crystal accuracy, and has a cycle of 136µs.

- C2PO represents the data error status.

- XROF is generated when the 32K RAM exceeds the ±28 frame jitter margin.

- C4M is a 4.2336MHz output that changes in CAV-W mode and variable pitch mode.

- R8M is the 8.4672MHz output.

- FSTO is the 2/3 frequency-division output of the XTAI pin.

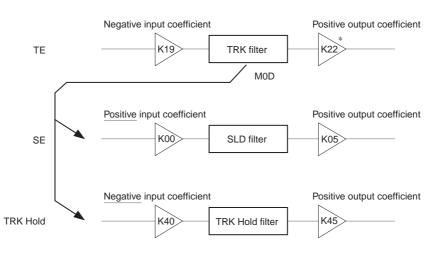

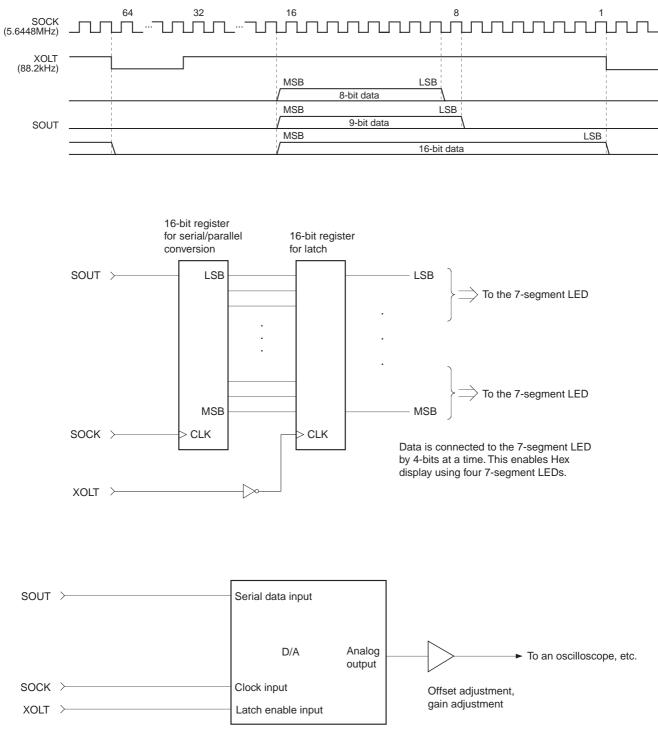

- SOUT is the serial data output inside the servo block.

- SOCK is the serial data readout clock output inside the servo block.

- XOLT is the serial data latch output inside the servo block.

#### Monitor Pin Output Combinations

|        | Command bit |       |       |       |             | Outou | ut data |      |      |  |  |

|--------|-------------|-------|-------|-------|-------------|-------|---------|------|------|--|--|

| MONSEL | SRO1        | MTSL1 | MTSL0 |       | Output data |       |         |      |      |  |  |

| 0      | 0           | 0     | 0     | XUGF  | XPCK        | GFS   | C2PO    | COUT | MIRR |  |  |

| 0      | 0           | 0     | 1     | MNT0  | MNT1        | MNT2  | MNT3    | COUT | MIRR |  |  |

| 0      | 0           | 1     | 0     | RFCK  | XPCK        | XROF  | GTOP    | COUT | MIRR |  |  |

| 0      | 0           | 1     | 1     | C4M   | FSTO        | GFS   | C2PO    | COUT | MIRR |  |  |

| 0      | 1           | 0     | 0     | SOUT  | SOCK        | XOLT  | C2PO    | COUT | MIRR |  |  |

| 1      | —           |       |       | QRCVD | GTOP        | GFS   | C2PO    | SCOR |      |  |  |

#### **Electrical Characteristics**

#### **1. DC Characteristics** (VDD1 = $2.5 \pm 0.2V$ , VDD2 (logic) = $1.8 \pm 0.1V$ , DVss = Vss = 0V, Topr = -20 to $+75^{\circ}C$ )

|                        | ltem                      | Conditions   | Min.                | Тур. | Max. | Unit | Applicable<br>pins |          |

|------------------------|---------------------------|--------------|---------------------|------|------|------|--------------------|----------|

| Input voltage          | High level input voltage  | Viн          |                     | 1.7  |      |      | V                  | *13, *15 |

| (1)                    | Low level input voltage   | Vil          |                     |      |      | 0.7  | V                  | 10, 10   |

| Input voltage          | High level input voltage  | Vt+          |                     | 1.7  |      |      |                    |          |

|                        | Low level input voltage   | Vt–          | Schmitt input       |      |      | 0.7  | V                  | *14      |

| (2)                    | Hysteresis                | Vt+ –<br>Vt– |                     |      | 0.4  |      |                    |          |

| Output                 | High level output voltage | Vон          | Iон = -4mA          | 2.0  |      |      | V                  | *12. *13 |

| voltage                | Low level output voltage  | Vol          | IoL = 4mA           |      |      | 0.4  |                    | 12, 13   |

| Input leak current (1) |                           | lı (1)       | VIN = Vss or<br>VDD | -10  |      | 10   | μA                 | *15      |

| Input leak cur         | rent (2)                  | lı (2)       | VIN = Vss or<br>VDD | -10  |      | 10   | μA                 | *13      |

|                                  | ltem                        |              | Conditions                     | Min.      | Тур. | Max. | Unit | Applicable pins   |

|----------------------------------|-----------------------------|--------------|--------------------------------|-----------|------|------|------|-------------------|

| Input voltage                    | High level input voltage    | Vін (1)      |                                | 1.7       |      |      | V    | *1, *2,           |

| (1)                              | Low level input voltage     | Vı∟ (1)      | )                              |           |      | 0.7  |      | *3, *4            |

| Input voltage<br>(2)             | Input voltage               | Vin (2)      | Analog input                   | Vss       |      | Vdd  | V    | *6, *7            |

|                                  | High level input voltage    | Vt+          |                                | 1.7       |      |      |      |                   |

| Input voltage                    | Low level input voltage     | Vt–          | Schmitt input                  |           |      | 0.7  | V    | *5                |

| (3)                              | Hysteresis                  | Vt+ –<br>Vt– |                                |           | 0.4  |      |      |                   |

| Output                           | High level output voltage   | Vон (1)      | Іон = —4mA                     | 2.0       |      |      | V    | *2, *8,           |

| voltage (1)                      | Low level output voltage    | Vol (1)      | lo∟ = 4mA                      |           |      | 0.4  |      | *10, *15          |

| Output                           | High level output voltage   | Vон (2)      | Іон = -2mA                     | 2.0       |      |      | V    | *9                |

| voltage (2)                      | Low level output voltage    | Vol (2)      | /ol (2) Iol = 2mA              |           |      | 0.4  |      | . 9               |

| Output                           | High level output voltage   | Vон (3)      | Іон = -0.28mA                  | Vdd - 0.5 |      | Vdd  | V    | *11               |

| voltage (3)                      | Low level output voltage    | Vol (3)      | lo∟ = 0.36mA                   | 0         |      | 0.4  |      |                   |

| Input leak cur                   | rent (1)                    | lı (1)       | VIN = Vss or<br>VDD            | -10       |      | 10   | μA   | *1, *3,<br>*5, *6 |

| Input leak current (2)           |                             | lı (2)       | VIN = Vss or<br>VDD            | -10       |      | 10   | μA   | *2, *4            |

| Input leak current (3)           |                             | lı (3)       | VIN = 0.25VDD<br>to 0.75VDD    | -40       |      | 40   | μA   | *7                |

| Tri-state outpu<br>(when high im | ut leak current<br>pedance) | loz          | Vo = Vss or<br>V <sub>DD</sub> | -10       |      | 10   | μA   | *10               |

(VDD = AVDD =  $2.5 \pm 0.2V$ , Vss = AVss = 0V, Topr = -20 to  $+75^{\circ}$ C)

|                                                        | Item                      |              | Conditions                     | Min.      | Тур. | Max.    | Unit | Applicable pins     |

|--------------------------------------------------------|---------------------------|--------------|--------------------------------|-----------|------|---------|------|---------------------|

| Input voltage                                          | High level input voltage  | Vін (1)      |                                | 0.65Vdd   |      |         | V    | *1, *2,             |

| (1)                                                    | Low level input voltage   | Vı∟ (1)      |                                |           |      | 0.35Vdd |      | *3, *4              |

| Input voltage<br>(2)                                   | Input voltage             | Vin (2)      | Analog input                   | Vss       |      | Vdd     | V    | *6, *7              |

|                                                        | High level input voltage  | Vt+          |                                | 0.65Vdd   |      |         |      |                     |

| Input voltage                                          | Low level input voltage   | Vt–          | Schmitt input                  |           |      | 0.35Vdd | V    | *5                  |

| (3)                                                    | Hysteresis                | Vt+ –<br>Vt– |                                |           | 0.4  |         |      |                     |

| Output                                                 | High level output voltage | Vон (1)      | Іон = -2.4mA                   | Vdd - 0.4 |      | Vdd     | v    | *2, *8,<br>*10, *16 |

| voltage (1)                                            | Low level output voltage  | Vol (1)      | IoL = 2.4mA                    | 0         |      | 0.4     |      |                     |

| Output                                                 | High level output voltage | Vон (2)      | Іон = -1.4mA                   | Vdd - 0.4 |      | Vdd     | V    | *9                  |

| voltage (2)                                            | Low level output voltage  | Vol (2)      | lo∟ = 1.4mA                    | 0         |      | 0.4     |      |                     |

| Output                                                 | High level output voltage | Vон (3)      | Іон = -0.28mA                  | Vdd - 0.5 |      | Vdd     | V    | *11                 |

| voltage (3)                                            | Low level output voltage  | Vol (3)      | lo∟ = 0.36mA                   | 0         |      | 0.4     | V    | *11                 |

| Input leak cur                                         | rent (1)                  | lı (1)       | VIN = Vss or<br>VDD            | -10       |      | 10      | μA   | *1, *3,<br>*5, *6   |

| Input leak current (2)                                 |                           | lı (2)       | VIN = Vss or<br>VDD            | -10       |      | 10      | μA   | *2, *4              |

| Input leak current (3)                                 |                           |              | VIN = 0.25VDD<br>to 0.75VDD    | -40       |      | 40      | μA   | *7                  |

| Tri-state output leak current<br>(when high impedance) |                           |              | Vo = Vss or<br>V <sub>DD</sub> | -10       |      | 10      | μA   | *10                 |

#### $(VDD = AVDD = 1.8 \pm 0.1V, Vss = AVss = 0V, Topr = -20 \text{ to } +75^{\circ}C)$

#### Applicable pins

- \*1 TEST, TES1

- \*2 COUT, MIRR, DFCT, FOK, XQOK, XWRE, ATSK

- \*3 SYSM, DATA, XSOE, XTSL

- \*4 SSTP, PWMI

- \*5 SQCK, EXCK, XRST, CLOK, SCLK, XLAT

- \*6 VCTL, FILI, CLTV, ASYI, IGEN, BIAS

- \*7 RFDC, CE, TE, SE, FE, VC

- \*8 XEMP, XWIH, SQSO, SBSO, XUGF, XPCK, GFS, C2PO, SCOR, WDCK, SFDR, SRDR, TFDR, TRDR, FFDR, FRDR, ASYO, DOUT, C176

- \*9 R4M

- \*10 SENS, MDP, VPCO, PCO, MDS

- \*11 FILO

- \*12 A0 to A10, XRAS, XCAS, XWE, WFCK, LRCK, BCK, PCMD

- \*13 D0 to D3, XRDE, A11

- \*14 LRCKI, BCKI

- \*15 PCMDI

- \*16 HPL, HPR

#### 2. AC Characteristics

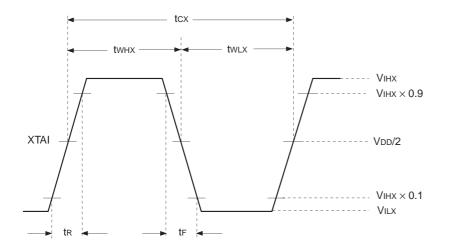

#### (1) XTAI pin

(a) When using self-excited oscillation

$$(V_{DD} = AV_{DD} = 1.8 \pm 0.1V \text{ and } 2.5 \pm 0.2V, V_{SS} = AV_{SS} = 0V, T_{OP} = -20 \text{ to } +75^{\circ}C)$$

| Item                     | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------|--------|------|------|------|------|

| Oscillation<br>frequency | fмах   | 7    |      | 34   | MHz  |

(b) When inputting pulses to XTAI pin

```

(V_{DD} = AV_{DD} = 1.8 \pm 0.1V \text{ and } 2.5 \pm 0.2V, V_{SS} = AV_{SS} = 0V, T_{OP} = -20 \text{ to } +75^{\circ}\text{C})

```

| Item                    | Symbol       | Min.   | Тур. | Max.   | Unit |

|-------------------------|--------------|--------|------|--------|------|

| High level pulse width  | twнx         | 13     |      | 500    | ns   |

| Low level pulse width   | <b>t</b> wLx | 13     |      | 500    | ns   |

| Pulse cycle             | tcx          | 26     |      | 1000   | ns   |

| Input high level        | Vihx         | 0.7Vdd |      |        | V    |

| Input low level         | Vilx         |        |      | 0.2Vdd | V    |

| Rise time,<br>fall time | tr, tr       |        |      | 10     | ns   |

Note) When the pulse is input to the XTAI pin, be sure to input it via the capacitor.

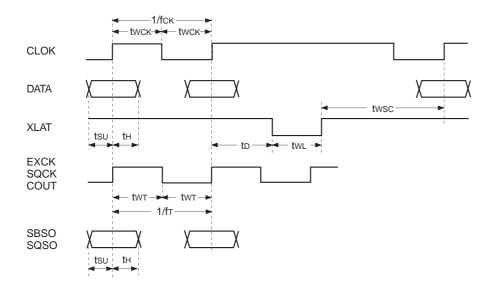

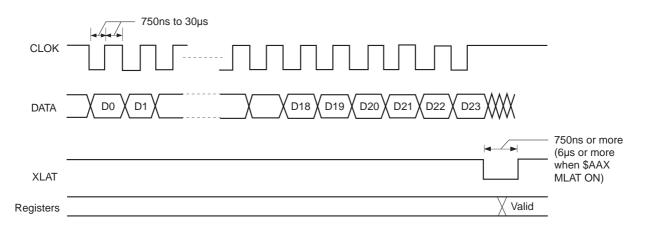

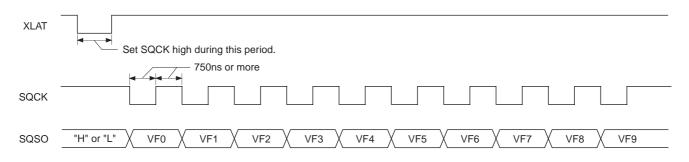

#### (2) CLOK, DATA, XLAT, SQCK and EXCK pins

|                                  | ,            |      | , I  |       | ,    |

|----------------------------------|--------------|------|------|-------|------|

| Item                             | Symbol       | Min. | Тур. | Max.  | Unit |

| Clock frequency                  | fcк          |      |      | 0.65  | MHz  |

| Clock pulse width                | <b>t</b> wcĸ | 750  |      | 30000 | ns   |

| Setup time                       | <b>t</b> su  | 300  |      |       | ns   |

| Hold time                        | tн           | 300  |      |       | ns   |

| Delay time                       | t⊳           | 300  |      | 30000 | ns   |

| Latch pulse width                | tw∟          | 750  |      |       | ns   |

| EXCK SQCK frequency              | fт           |      |      | 0.65  | MHz  |

| EXCK SQCK pulse width            | twт          | 750  |      |       | ns   |

| COUT frequency (during input)*   | fт           |      |      | 65    | kHz  |

| COUT pulse width (during input)* | twт          | 7.5  |      |       | μs   |

$^{\ast}$  Only when \$44 and \$45 are executed.

#### (3) R4M pin (when \$A4X CKOUTSL2 = CKOUTSL1 = 0)

| $(V_{DD} = AV_{DD} = 1.8 \pm 0.1V \text{ and } 2.5 \pm 0.2V, V_{SS} = AV_{SS} = 0V, T_{OPT} = -20 \text{ to } +75^{\circ}\text{C})$ |

|-------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------|

| Item             | Symbol | Min. | Тур.   | Max. | Unit |

|------------------|--------|------|--------|------|------|

| Output frequency | fouт   |      | 4.2336 |      | MHz  |

| Output duty      | Dout   |      | 50     |      | %    |

| Output amplitude | Vout   |      | Vdd    |      | V    |

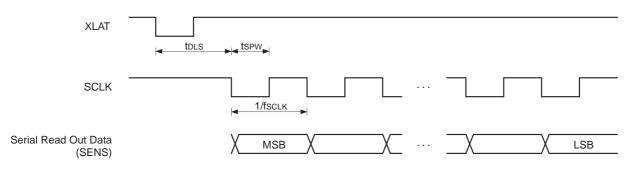

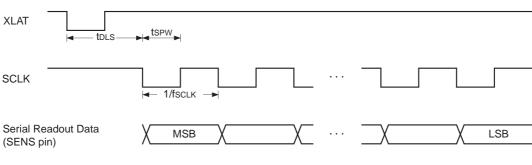

#### (4) SCLK pin

$(V_{DD} = AV_{DD} = 1.8 \pm 0.1V \text{ and } 2.5 \pm 0.2V, V_{SS} = AV_{SS} = 0V, Topr = -20 \text{ to } +75^{\circ}C)$

| Item             | Symbol       | Min. | Тур. | Max. | Unit |

|------------------|--------------|------|------|------|------|

| SCLK frequency   | fsclk        |      |      | 16   | MHz  |

| SCLK pulse width | <b>t</b> spw | 31.3 |      |      | ns   |

| Delay time       | tols         | 15   |      |      | μs   |

#### (5) COUT, MIRR and DFCT pins

#### **Operating frequency**

\*2

(VDD = AVDD =  $1.8 \pm 0.1V$  and  $2.5 \pm 0.2V$ , Vss = AVss = 0.00000, Topr = -20 to  $+75^{\circ}$ C)

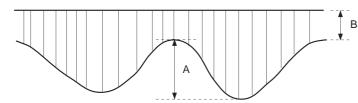

| Item                                | Symbol | Min. | Тур. | Max. | Unit | Conditions |

|-------------------------------------|--------|------|------|------|------|------------|

| COUT maximum operating frequency    | fcouт  | 40   |      |      | kHz  | *1         |

| MIRR maximum operating frequency    | fmirr  | 40   |      |      | kHz  | *2         |

| DFCT maximum<br>operating frequency | fdfcth | 5    |      |      | kHz  | *3         |

\*1 When using a high-speed traverse TZC.

When the RF signal continuously satisfies the following conditions during the above traverse.

• A = 0.11Vpd to 0.23Vpd

•

$$\frac{\mathsf{B}}{\mathsf{A} + \mathsf{B}} \le 25\%$$

\*3 During complete RF signal omission.

When settings related to DFCT signal generation are Typ.

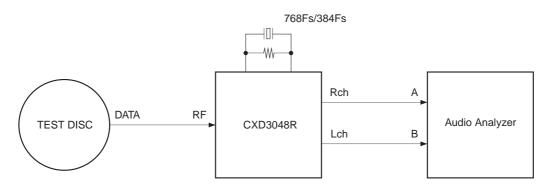

| Item            | Symbol | Conditions                                    | Crystal | Min.  | Тур.  | Max.  | Unit |

|-----------------|--------|-----------------------------------------------|---------|-------|-------|-------|------|

| Total harmonic  | THD    | 1kHz sine wave, 0dB data,                     | 384Fs   |       | 0.009 | 0.016 | %    |

| distortion      | שחו    | 20kHz LPF 768Fs                               |         | 0.009 | 0.016 | /0    |      |

| Signal-to-noise | S/N    | 1kHz sine wave, 0dB data,                     | 384Fs   | 92    | 94    |       | dB   |

| ratio 5/10 P    |        | AMUT OFF (Using A-weighting filter 20kHz LPF) | 768Fs   | 92    | 94    |       | UD   |

| 1-bit DAC and LPF | Block Analog | Characteristics |

|-------------------|--------------|-----------------|

|-------------------|--------------|-----------------|

Fs = 44.1 kHz in all cases.

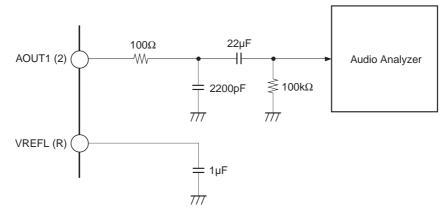

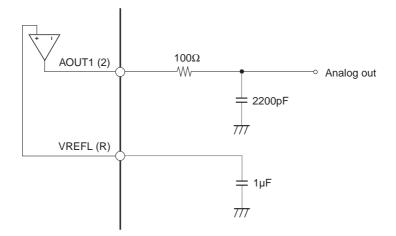

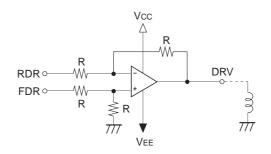

The total harmonic distortion and signal-to-noise ratio measurement circuits are shown below.

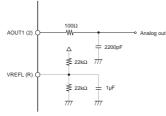

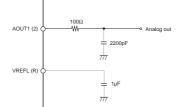

#### LPF external circuit diagram (\$A560C400 PDMSEL = 1)

#### Block diagram of analog characteristics measurement

| Item                 | Symbol | Min. | Тур. | Max. | Unit  | Applicable pins |

|----------------------|--------|------|------|------|-------|-----------------|

| Output voltage       | Vout   | 640  | 658  |      | mVrms | *1              |

| Load resistance      | R∟     | 10   |      |      | kΩ    | *1              |

| VREF pin capacitance | CVREF  |      | 1    |      | μF    | *2              |

\* Measurement is conducted for the above circuit diagrams with the sine wave output of 1kHz and 0dB.

#### Applicable pins

\*1 AOUT1, AOUT2

\*2 VREFL, VREFR

#### Contents

| §1-2. CPU Interface<br>§1-3. CPU Commar | Timing<br>Command Table<br>Ind Presets                     | 16<br>32 |

|-----------------------------------------|------------------------------------------------------------|----------|

|                                         | SENS Signals<br>Commands                                   |          |

|                                         | de Readout<br>e-Q Readout                                  |          |

| [3] Description of Mod                  |                                                            |          |

|                                         |                                                            |          |

|                                         |                                                            |          |

|                                         | ·                                                          |          |

| [4] Description of Othe                 |                                                            |          |

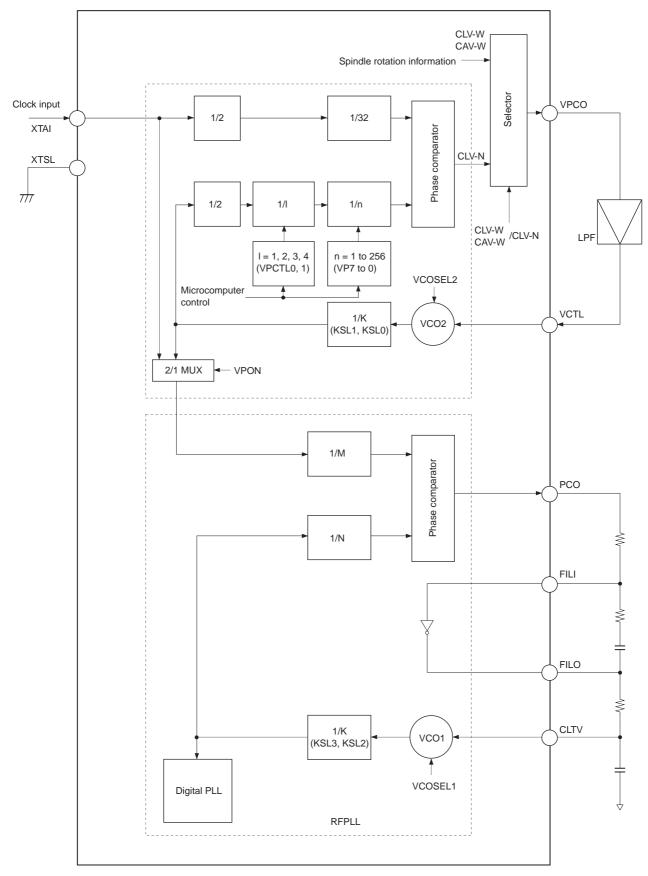

| §4-1. Channel Clock                     | k Recovery by Digital PLL Circuit                          | 112      |

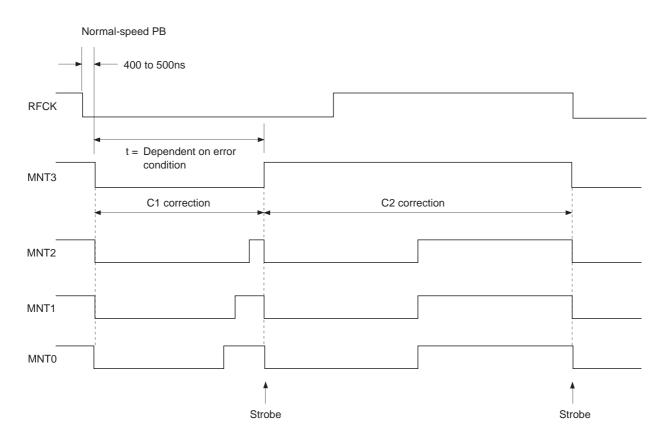

|                                         | Protection                                                 |          |

|                                         | on                                                         |          |

|                                         |                                                            |          |

| 84-5. Digital Out                       | equence                                                    | 170      |

|                                         | -quence                                                    |          |

|                                         | k Playback Speed                                           |          |

|                                         | DAC Block and Shock-proof Memory Controller Block Circuits |          |

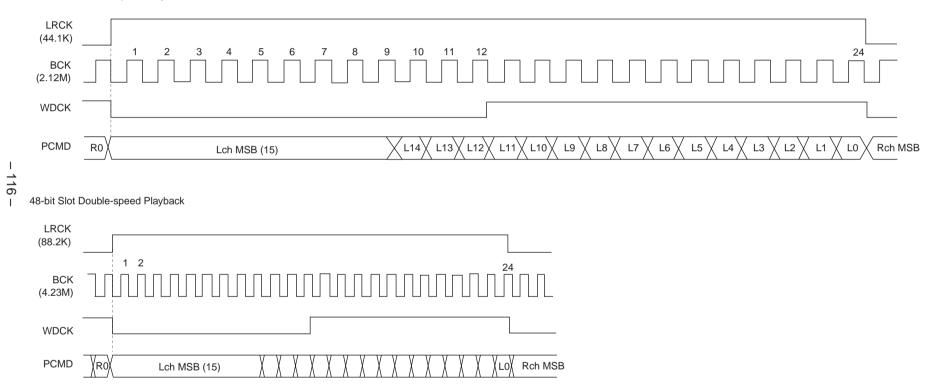

| §4-10. DAC Block Inc                    | but Timing                                                 | 134      |

|                                         | DAC Block Functions                                        |          |

| §4-12. LPF Block                        |                                                            | 140      |

| §4-13. Description of                   | Shock-proof Memory Controller Block Functions              | 141      |

|                                         | 1 Access Function                                          |          |

|                                         | a Demodulation                                             |          |

| [5] Description of Serv                 | o Signal Processing System Functions and Commands          |          |

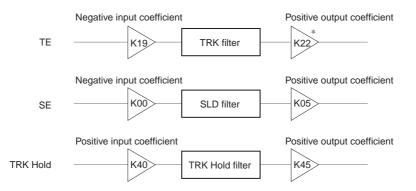

| §5-1. General Desci                     | ription of Servo Signal Processing System                  | 153      |

| §5-2. Digital Servo I                   | Block Master Clock (MCK)                                   | 154      |

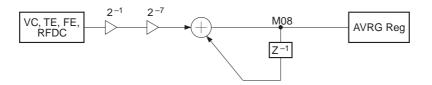

|                                         | ncel [AVRG Measurement and Compensation]                   |          |

| §5-4. E:F Balance A                     | djustment Function                                         | 156      |

|                                         | ustment Function                                           |          |

|                                         | ction<br>d FCS Search                                      |          |

|                                         | Servo Control                                              |          |

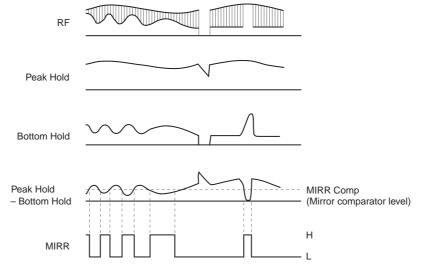

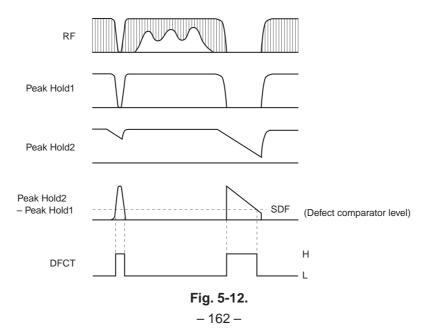

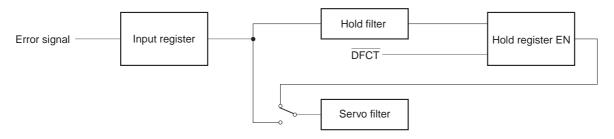

| §5-9. MIRR and DF                       | CT Signal Generation                                       | 162      |

|                                         | rmeasure Circuit                                           |          |

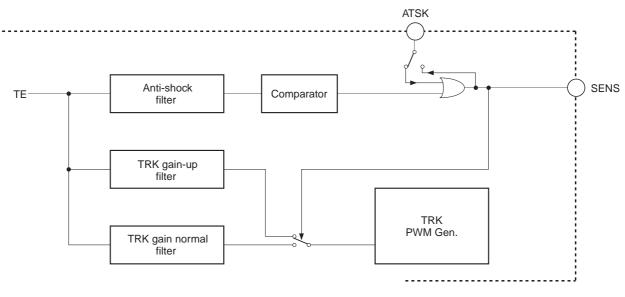

|                                         |                                                            | 163      |

|                                         | ······                                                     |          |

|                                         |                                                            |          |

|                                         | It Circuit                                                 | 165      |

|                                         |                                                            |          |

| §5-17. Servo Status (                   | Changes Produced by LOCK Signal                            | 167      |

| §5-18. Description of                   | Commands and Data Sets                                     | 167      |

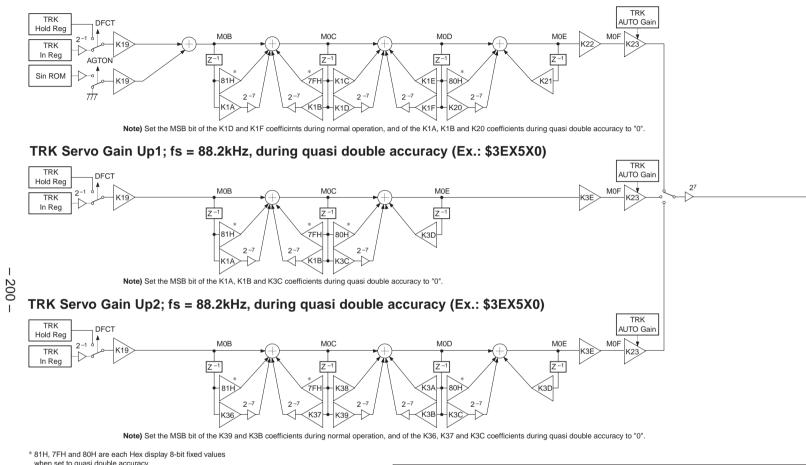

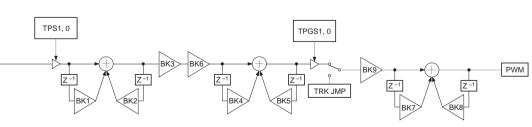

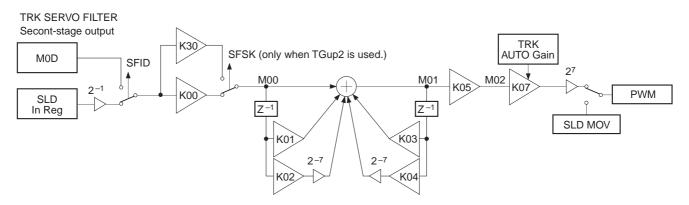

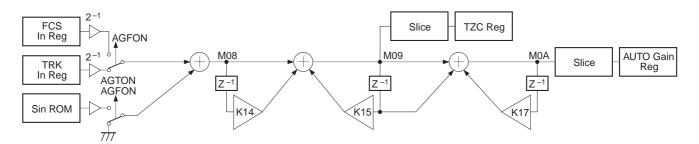

| §5-19. List of Servo F                  | Filter Coefficients                                        | 195      |

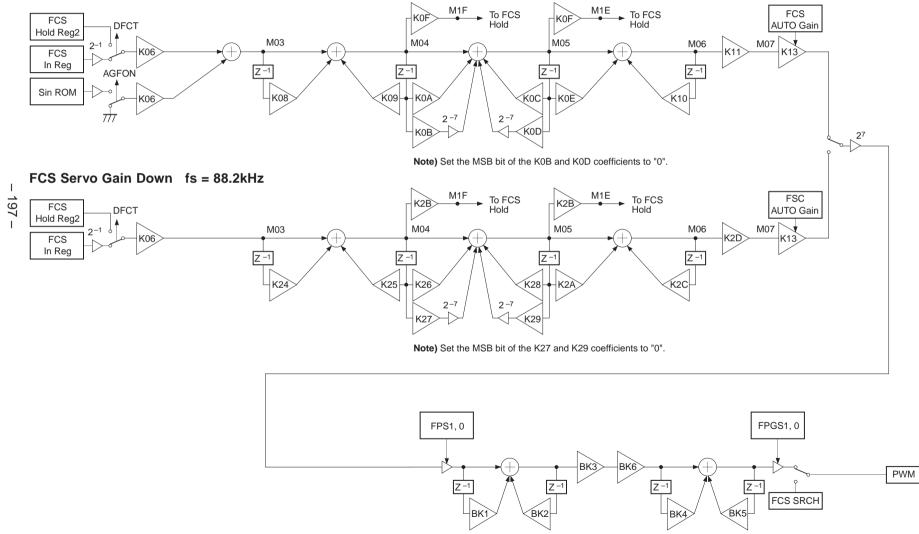

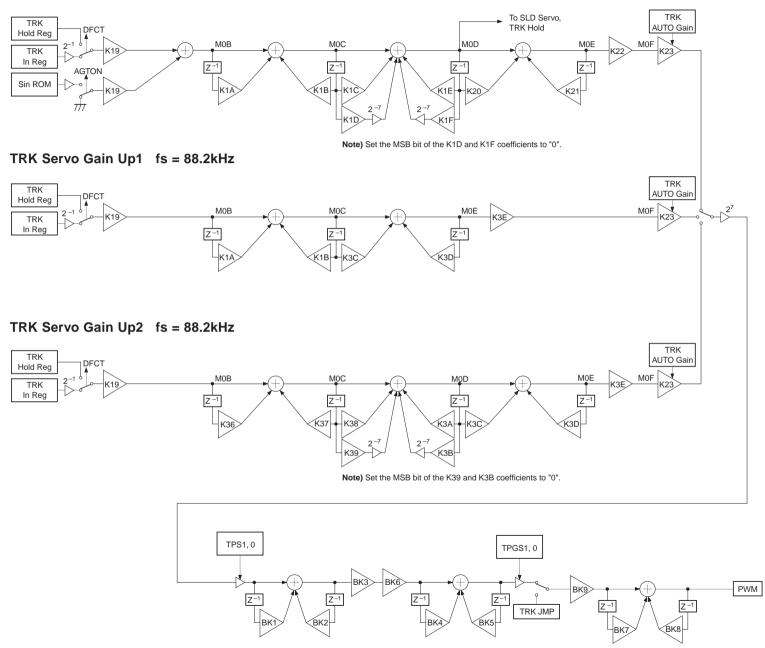

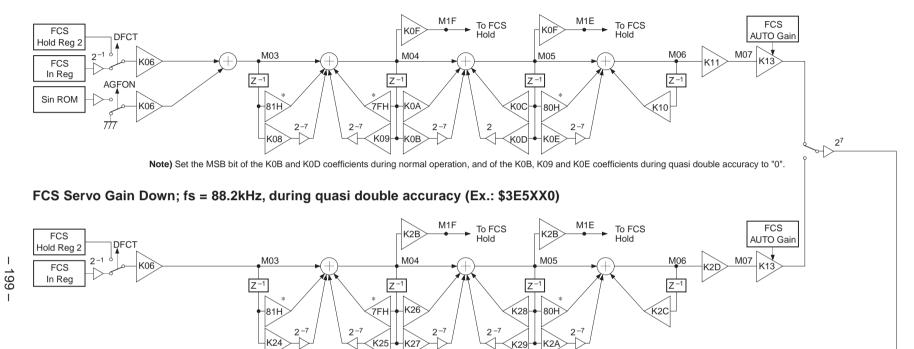

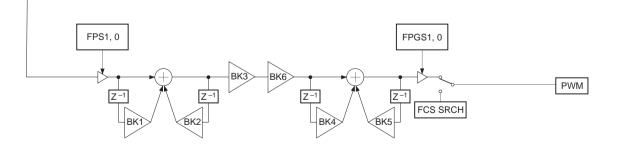

| §5-20. Filter Compos                    | ition                                                      | 197      |

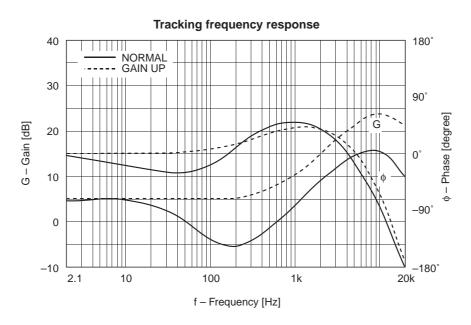

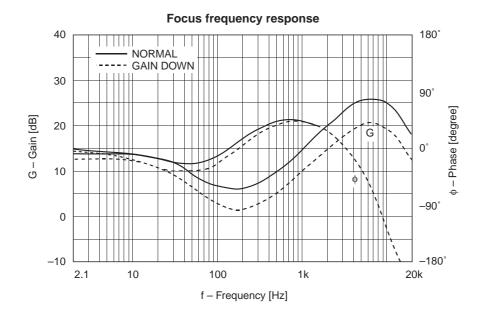

|                                         | nd FOCUS Frequency Response 2                              |          |

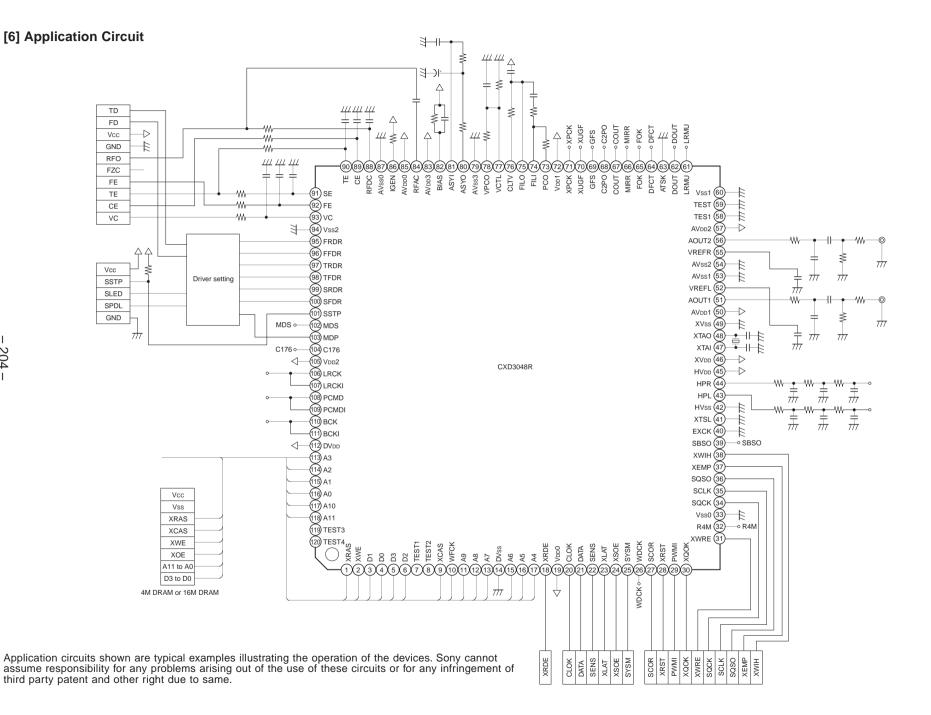

| [6] Application Circuit.                |                                                            | 204      |

|                                         | of abbreviations                                           |          |

AVRG: Average AGCNTL: Auto gain control FCS: Focus TRK: Tracking SLD: Sled DFCT: Defect

#### [1] CPU Interface

#### §1-1. CPU Interface Timing

• CPU interface

This interface uses DATA, CLOK and XLAT to set the modes.

The interface timing chart is shown below. (See 2. AC Characteristics in Electrical Characteristics, for the details of the AC characteristics.)

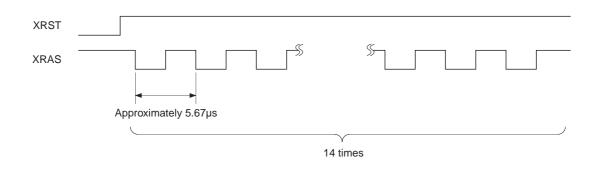

• The internal registers are initialized by a reset when XRST = 0.

#### §1-2. CPU Interface Command Table

Total bit length for each register

| Register | Total bit length |

|----------|------------------|

| 0 to 2   | 8 bits           |

| 3        | 8 to 24 bits     |

| 4 to 6   | 16 bits          |

| 7        | 20 bits          |

| 8        | 32 bits          |

| 9        | 32 bits          |

| A        | 32 bits          |

| В        | 28 bits          |

| С        | 28 bits          |

| D        | 28 bits          |

| E        | 20 bits          |

#### Command Table (\$0X to 1X)

| Regis- | Commond          | Address    |     | Dat | ta 1 |     |     | Da  | ta 2 |     |     | Dat | a 3 |    |    | Dat | a 4 |    |    | Da | ta 5 |    |                                              |

|--------|------------------|------------|-----|-----|------|-----|-----|-----|------|-----|-----|-----|-----|----|----|-----|-----|----|----|----|------|----|----------------------------------------------|

| ter    | Command          | D23 to D20 | D19 | D18 | D17  | D16 | D15 | D14 | D13  | D12 | D11 | D10 | D9  | D8 | D7 | D6  | D5  | D4 | D3 | D2 | D1   | D0 |                                              |

|        |                  |            | 1   | 0   | _    | _   | _   | _   | _    | _   |     | _   | _   | _  | _  |     | _   | _  |    | _  |      | _  | FOCUS SERVO O<br>(FOCUS GAIN<br>NORMAL)      |

|        |                  |            | 1   | 1   | _    | _   | _   | _   | _    | _   | _   | _   |     | _  | _  | _   | _   | _  | _  | _  | _    | _  | FOCUS SERVO O<br>(FOCUS GAIN<br>DOWN)        |

| 0      | FOCUS<br>CONTROL | 0000       | 0   |     | 0    |     |     | _   | _    | _   | _   | _   | _   |    | _  |     |     |    | _  | _  | _    | _  | FOCUS SERVO O<br>0V OUT                      |

|        |                  |            | 0   | _   | 1    | _   | _   | _   | _    | _   | _   | _   | _   | _  | _  | _   | _   | _  | _  | _  | _    | _  | FOCUS SERVO O<br>FOCUS SEARCH<br>VOLTAGE OUT |

|        |                  |            | 0   |     | 1    | 0   |     | _   | _    | _   | _   | _   |     |    | _  |     |     |    |    | _  | _    | _  | FOCUS SEARCH<br>VOLTAGE DOWN                 |

|        |                  |            | 0   | _   | 1    | 1   | _   | _   | _    | _   | _   | _   | _   | _  | _  | _   | _   | _  | _  | _  | _    | _  | FOCUS SEARCH<br>VOLTAGE UP                   |

|        |                  |            | 1   | 0   | _    | _   | _   | _   | _    | _   | _   | _   | _   | _  | _  | _   | _   | _  | _  | _  | _    | _  | ANTI SHOCK ON                                |

|        |                  |            | 0   | _   |      |     |     | _   | _    | _   | _   | _   |     |    | _  | _   | _   | _  | _  | _  | _    | _  | ANTI SHOCK OF                                |

|        |                  |            | _   | 1   |      |     |     | _   | _    | _   | _   | _   |     |    | _  | _   | _   | _  | —  | _  | _    | _  | BRAKE ON                                     |

| 1      | TRACKING         | 0001       | _   | 0   |      |     |     | _   | _    | _   | _   | _   |     |    | _  | _   | _   | _  | _  | _  | _    | _  | BRAKE OFF                                    |

| I      | CONTROL          | 0001       | _   | _   | 0    | _   | _   | _   | _    | _   | _   | _   | _   | _  | _  | _   |     |    | _  | _  | _    | _  | TRACKING GAIN<br>NORMAL                      |

|        |                  |            | _   |     | 1    |     |     | _   | _    | _   | _   | _   | _   |    | _  | _   | _   |    | _  | _  | _    | _  | TRACKING GAIN                                |

|        |                  |            | _   | _   | _    | 1   | _   | _   | _    | _   | _   | _   |     | _  | _  | _   | _   | _  | _  | _  | _    | _  | TRACKING GAIN<br>FILTER SELECT               |

|        |                  |            | _   | _   | _    | 0   | _   | _   | -    | _   | _   | _   | _   | _  | _  | _   | _   |    | _  | _  | _    | _  | TRACKING GAIN<br>FILTER SELECT 2             |

SONA

CXD3048R

#### Command Table (\$2X to 3X)

| Regis- | Command  | Address    |       | Dat | ta 1 |      |     | Dat | a 2  |     |     | Dat | a 3  |    |    | Dat | ta 4 |    |    | Dat | ta 5 |    |                                                     |

|--------|----------|------------|-------|-----|------|------|-----|-----|------|-----|-----|-----|------|----|----|-----|------|----|----|-----|------|----|-----------------------------------------------------|

| ter    | Command  | D23 to D20 | D19   | D18 | D17  | D16  | D15 | D14 | D13  | D12 | D11 | D10 | D9   | D8 | D7 | D6  | D5   | D4 | D3 | D2  | D1   | D0 |                                                     |

|        |          |            | 0     | 0   | _    | _    | _   | _   | _    | _   | _   | _   |      | _  | _  | _   | _    | _  | _  | _   | _    | _  | TRACKING SERVO<br>OFF                               |

|        |          |            | 0     | 1   | _    | _    | _   | _   | _    | _   | _   | _   |      | _  | _  | _   | _    | _  | _  | _   | _    | _  | TRACKING SERVO<br>ON                                |

|        |          |            | 1     | 0   | _    | _    | _   | _   | _    | _   | _   | _   |      | _  | _  | _   |      | _  | _  | _   | _    | _  | FORWARD TRACK<br>JUMP                               |

|        | TRACKING | 0.0.4.0    | 1     | 1   | _    |      |     | _   |      | _   | _   |     |      | _  | _  | _   |      |    |    |     | _    | _  | REVERSE TRACK<br>JUMP                               |

| 2      | CONTROL  | 0010       |       | _   | 0    | 0    |     |     |      |     |     |     |      |    |    |     |      |    |    |     |      |    | SLED SERVO OFF                                      |

|        |          |            | _     | _   | 0    | 1    | _   | _   | _    | _   | _   |     | _    | _  | _  | _   | _    |    |    | _   | _    | _  | SLED SERVO ON                                       |

|        |          |            |       | _   | 1    | 0    | _   | _   | _    | _   | _   | _   |      | _  | _  | _   |      | _  | _  | _   | _    | _  | FORWARD SLED<br>MOVE                                |

|        |          |            |       | _   | 1    | 1    | _   | _   | _    | _   | _   | _   |      | _  | _  | _   | _    | _  | _  | _   | _    | _  | REVERSE SLED<br>MOVE                                |

| Regis- | Command  | Add        | dress |     | Da   | ta 1 |     | Da  | ta 2 |     |     | Dat | ta 3 |    |    | Da  | ta 4 |    |    | Da  | ta 5 |    |                                                     |

| ter    | Command  | D23 to D20 | D19   | D18 | D17  | D16  | D15 | D14 | D13  | D12 | D11 | D10 | D9   | D8 | D7 | D6  | D5   | D4 | D3 | D2  | D1   | D0 |                                                     |

|        |          |            | 0     | 0   | 0    | 0    |     |     |      |     |     |     |      |    |    |     |      |    |    |     |      | _  | SLED KICK LEVEL<br>(±1 × basic value) (default)     |

| 3      | SELECT   | 0011       | 0     | 0   | 0    | 1    | _   | _   | _    | _   | _   |     |      | _  | _  | _   |      | _  | _  | _   |      | _  | SLED KICK LEVEL $(\pm 2 \times \text{basic value})$ |

| 3      | SELEUT   | 0011       | 0     | 0   | 1    | 0    |     | _   |      | _   |     |     |      | _  | _  | _   |      |    |    |     |      | _  | SLED KICK LEVEL $(\pm 3 \times \text{basic value})$ |

|        |          |            | 0     | 0   | 1    | 1    | _   | _   | _    | _   | _   | _   |      | _  | _  | _   | _    | _  |    | _   | _    |    | SLED KICK LEVEL<br>(±4 × basic value)               |

SONA

-: don't care

- 18 -

#### Command Table (\$340X)

- 19 -

| Regis- | Commond | Address 1  | Address 2  | Address 3  |     | Addre | ess 4 |    |     | Dat | a 1 |     |     | Dat | a 2 |     |                                                    |

|--------|---------|------------|------------|------------|-----|-------|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------------------------------|

| ter    | Command | D23 to D20 | D19 to D16 | D15 to D12 | D11 | D10   | D9    | D8 | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                                                    |

|        |         |            |            |            | 0   | 0     | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K00)<br>SLED INPUT GAIN                 |

|        |         |            |            |            | 0   | 0     | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K01)<br>SLED LOW BOOST FILTER A-H       |

|        |         |            |            |            | 0   | 0     | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K02)<br>SLED LOW BOOST FILTER A-L       |

|        |         |            |            |            | 0   | 0     | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K03)<br>SLED LOW BOOST FILTER B-H       |

|        |         |            |            |            | 0   | 1     | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K04)<br>SLED LOW BOOST FILTER B-L       |

|        |         |            |            |            | 0   | 1     | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K05)<br>SLED OUTPUT GAIN                |

|        |         |            |            |            | 0   | 1     | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K06)<br>FOCUS INPUT GAIN                |

| 3      | SELECT  | 0011       | 0100       | 0000       | 0   | 1     | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K07)<br>SLED AUTO GAIN                  |

| 5      | OLLEOT  | 0011       | 0100       | 0000       | 1   | 0     | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K08)<br>FOCUS HIGH CUT FILTER A         |

|        |         |            |            |            | 1   | 0     | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K09)<br>FOCUS HIGH CUT FILTER B         |

|        |         |            |            |            | 1   | 0     | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K0A)<br>FOCUS LOW BOOST FILTER A-H      |

|        |         |            |            |            | 1   | 0     | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K0B)<br>FOCUS LOW BOOST FILTER A-L      |

|        |         |            |            |            | 1   | 1     | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K0C)<br>FOCUS LOW BOOST FILTER B-H      |

|        |         |            |            |            | 1   | 1     | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K0D)<br>FOCUS LOW BOOST FILTER B-L      |

|        |         |            |            |            | 1   | 1     | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K0E)<br>FOCUS PHASE COMPENSATE FILTER A |

|        |         |            |            |            | 1   | 1     | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K0F)<br>FOCUS DEFECT HOLD GAIN          |

SONA

#### Command Table (\$341X)

| Regis- | Commond | Address 1  | Address 2  | Address 3  |     | Addr | ess 4 |    |     | Dat | a 1 |     |     | Dat | a 2 |     |                                                         |

|--------|---------|------------|------------|------------|-----|------|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|---------------------------------------------------------|

| ter    | Command | D23 to D20 | D19 to D16 | D15 to D12 | D11 | D10  | D9    | D8 | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                                                         |

|        |         |            |            |            | 0   | 0    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K10)<br>FOCUS PHASE COMPENSATE FILTER B      |

|        |         |            |            |            | 0   | 0    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K11)<br>FOCUS OUTPUT GAIN                    |

|        |         |            |            |            | 0   | 0    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K12)<br>ANTI SHOCK INPUT GAIN                |

|        |         |            |            |            | 0   | 0    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K13)<br>FOCUS AUTO GAIN                      |

|        |         |            |            |            | 0   | 1    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K14)<br>HPTZC / AUTO GAIN HIGH PASS FILTER A |

|        |         |            |            |            | 0   | 1    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K15)<br>HPTZC / AUTO GAIN HIGH PASS FILTER B |

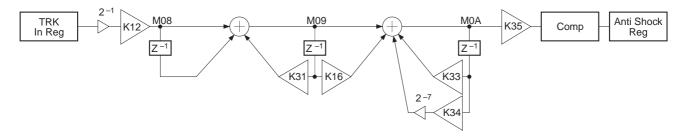

|        |         |            |            |            | 0   | 1    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K16)<br>ANTI SHOCK HIGH PASS FILTER A        |

| 3      | SELECT  | 0011       | 0100       | 0001       | 0   | 1    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K17)<br>HPTZC / AUTO GAIN LOW PASS FILTER B  |

|        | OLLO I  |            | 0100       | 0001       | 1   | 0    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K18)<br>FIX                                  |

|        |         |            |            |            | 1   | 0    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K19)<br>TRACKING INPUT GAIN                  |

|        |         |            |            |            | 1   | 0    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K1A)<br>TRACKING HIGH CUT FILTER A           |

|        |         |            |            |            | 1   | 0    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K1B)<br>TRACKING HIGH CUT FILTER B           |

|        |         |            |            |            | 1   | 1    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K1C)<br>TRACKING LOW BOOST FILTER A-H        |

|        |         |            |            |            | 1   | 1    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K1D)<br>TRACKING LOW BOOST FILTER A-L        |

|        |         |            |            |            | 1   | 1    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K1E)<br>TRACKING LOW BOOST FILTER B-H        |

|        |         |            |            |            | 1   | 1    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K1F)<br>TRACKING LOW BOOST FILTER B-L        |

SONY

Command Table (\$342X)

| Regis- | Command | Address 1  | Address 2  | Address 3  |     | Addr | ess 4 |    |     | Dat | a 1 |     |     | Dat | a 2 |     |                                                            |

|--------|---------|------------|------------|------------|-----|------|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|------------------------------------------------------------|

| ter    | Command | D23 to D20 | D19 to D16 | D15 to D12 | D11 | D10  | D9    | D8 | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                                                            |

|        |         |            |            |            | 0   | 0    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K20)<br>TRACKING PHASE COMPENSATE FILTER A      |

|        |         |            |            |            | 0   | 0    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K21)<br>TRACKING PHASE COMPENSATE FILTER B      |

|        |         |            |            |            | 0   | 0    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K22)<br>TRACKING OUTPUT GAIN                    |

|        |         |            |            |            | 0   | 0    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K23)<br>TRACKING AUTO GAIN                      |

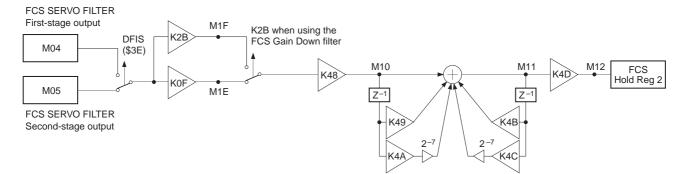

|        |         |            |            |            | 0   | 1    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K24)<br>FOCUS GAIN DOWN HIGH CUT FILTER A       |

|        |         |            |            |            | 0   | 1    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K25)<br>FOCUS GAIN DOWN HIGH CUT FILTER B       |

|        |         |            |            |            | 0   | 1    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K26)<br>FOCUS GAIN DOWN LOW BOOST FILTER A      |

| 3      | SELECT  | 0011       | 0100       | 0010       | 0   | 1    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K27)<br>FOCUS GAIN DOWN LOW BOOST FILTER A      |

| 5      |         | 0011       | 0100       | 0010       | 1   | 0    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K28)<br>FOCUS GAIN DOWN LOW BOOST FILTER B      |

|        |         |            |            |            | 1   | 0    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K29)<br>FOCUS GAIN DOWN LOW BOOST FILTER E      |

|        |         |            |            |            | 1   | 0    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K2A)<br>FOCUS GAIN DOWN PHASE COMPENSATE FILTER |

|        |         |            |            |            | 1   | 0    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K2B)<br>FOCUS GAIN DOWN DEFECT HOLD GAIN        |

|        |         |            |            |            | 1   | 1    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K2C)<br>FOCUS GAIN DOWN PHASE COMPENSATE FILTER |

|        |         |            |            |            | 1   | 1    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K2D)<br>FOCUS GAIN DOWN OUTPUT GAIN             |

|        |         |            |            |            | 1   | 1    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K2E)<br>Not used                                |

|        |         |            |            |            | 1   | 1    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K2F)<br>Not used                                |

SONA

#### Command Table (\$343X)

| Regis                 | - Command | Address 1  | Address 2  | Address 3  |     | Addre | ess 4 |    |     | Dat | ta 1 |     |     | Dat | a 2 |     |                                                                           |

|-----------------------|-----------|------------|------------|------------|-----|-------|-------|----|-----|-----|------|-----|-----|-----|-----|-----|---------------------------------------------------------------------------|

| ter                   | Command   | D23 to D20 | D19 to D16 | D15 to D12 | D11 | D10   | D9    | D8 | D7  | D6  | D5   | D4  | D3  | D2  | D1  | D0  |                                                                           |

|                       |           |            |            |            | 0   | 0     | 0     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K30)<br>SLED INPUT GAIN (when TGup2 is accessed with SFSK = 1) |

|                       |           |            |            |            | 0   | 0     | 0     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K31)<br>ANTI SHOCK LOW PASS FILTER B                           |

|                       |           |            |            |            | 0   | 0     | 1     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K32)<br>Not used                                               |

|                       |           |            |            |            | 0   | 0     | 1     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K33)<br>ANTI SHOCK HIGH PASS FILTER B-H                        |

|                       |           |            |            |            | 0   | 1     | 0     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K34)<br>ANTI SHOCK HIGH PASS FILTER B-L                        |

|                       |           |            |            |            | 0   | 1     | 0     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K35)<br>ANTI SHOCK FILTER COMPARATE GAIN                       |

|                       |           |            |            |            | 0   | 1     | 1     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K36)<br>TRACKING GAIN UP2 HIGH CUT FILTER A                    |

| 3<br> <br> <br> <br>3 | SELECT    | 0011       | 0100       | 0011       | 0   | 1     | 1     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K37)<br>TRACKING GAIN UP2 HIGH CUT FILTER B                    |

|                       | SELECT    | 0011       | 0100       | 0011       | 1   | 0     | 0     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K38)<br>TRACKING GAIN UP2 LOW BOOST FILTER A-H                 |

|                       |           |            |            |            | 1   | 0     | 0     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K39)<br>TRACKING GAIN UP2 LOW BOOST FILTER A-L                 |

|                       |           |            |            |            | 1   | 0     | 1     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K3A)<br>TRACKING GAIN UP2 LOW BOOST FILTER B-H                 |

|                       |           |            |            |            | 1   | 0     | 1     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K3B)<br>TRACKING GAIN UP2 LOW BOOST FILTER B-L                 |

|                       |           |            |            |            | 1   | 1     | 0     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K3C)<br>TRACKING GAIN UP PHASE COMPENSATE FILTER A             |

|                       |           |            |            |            | 1   | 1     | 0     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K3D)<br>TRACKING GAIN UP PHASE COMPENSATE FILTER B             |

|                       |           |            |            |            | 1   | 1     | 1     | 0  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K3E)<br>TRACKING GAIN UP OUTPUT GAIN                           |

|                       |           |            |            |            | 1   | 1     | 1     | 1  | KD7 | KD6 | KD5  | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K3F)<br>Not used                                               |

SONY

#### Command Table (\$344X)

| Regis- | Command | Address 1  | Address 2  | Address 3  |     | Addr | ess 4 |    |     | Dat | a 1 |     |     | Dat | a 2 |     |                                                                                 |

|--------|---------|------------|------------|------------|-----|------|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|---------------------------------------------------------------------------------|

| ter    | Commanu | D23 to D20 | D19 to D16 | D15 to D12 | D11 | D10  | D9    | D8 | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                                                                                 |

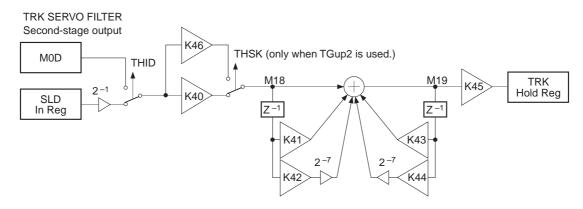

|        |         |            |            |            | 0   | 0    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K40)<br>TRACKING HOLD FILTER INPUT GAIN                              |

|        |         |            |            |            | 0   | 0    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K41)<br>TRACKING HOLD FILTER A-H                                     |

|        |         |            |            |            | 0   | 0    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K42)<br>TRACKING HOLD FILTER A-L                                     |

|        |         |            |            |            | 0   | 0    | 1     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K43)<br>TRACKING HOLD FILTER B-H                                     |

|        |         |            |            |            | 0   | 1    | 0     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K44)<br>TRACKING HOLD FILTER B-L                                     |

|        |         |            |            |            | 0   | 1    | 0     | 1  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K45)<br>TRACKING HOLD FILTER OUTPUT GAIN                             |

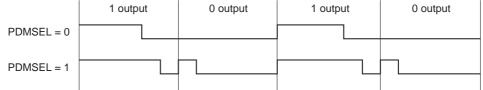

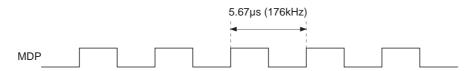

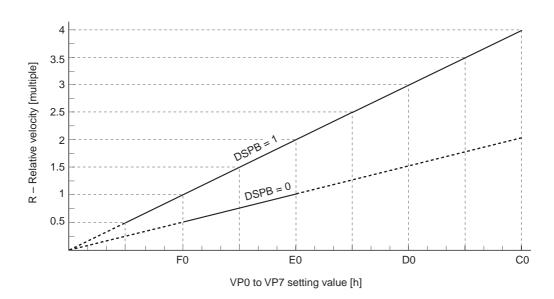

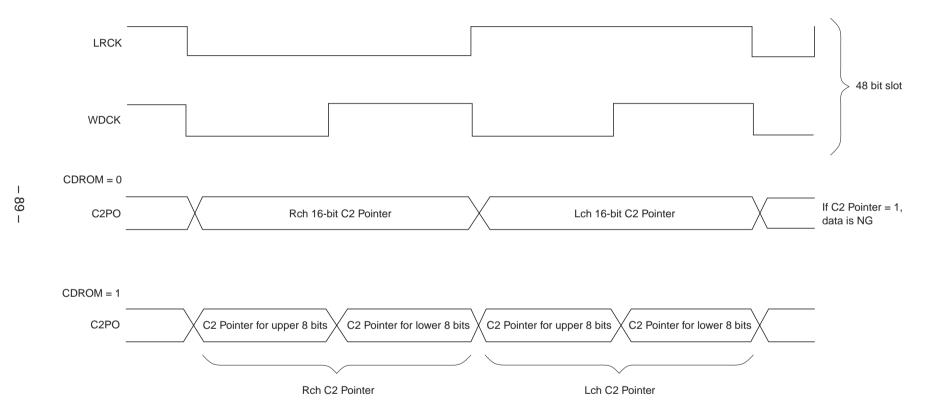

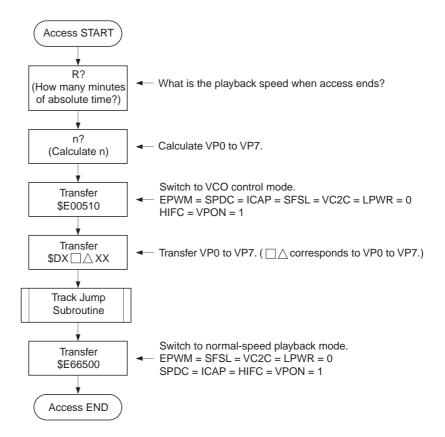

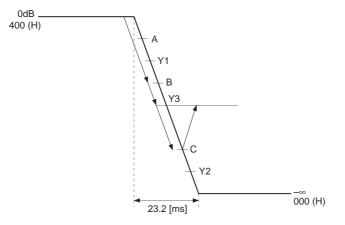

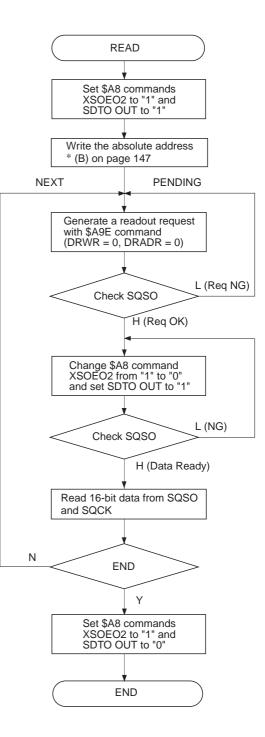

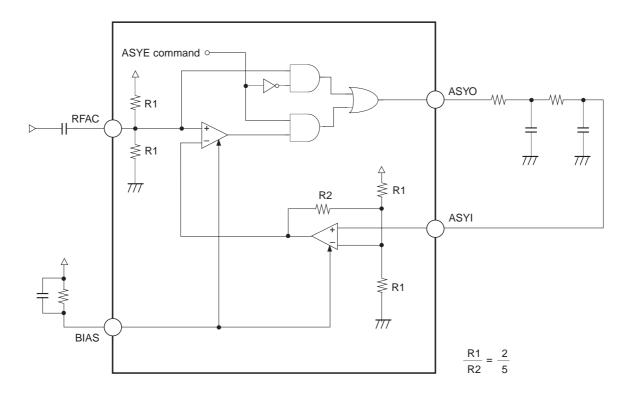

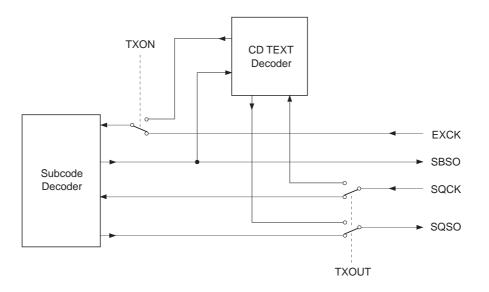

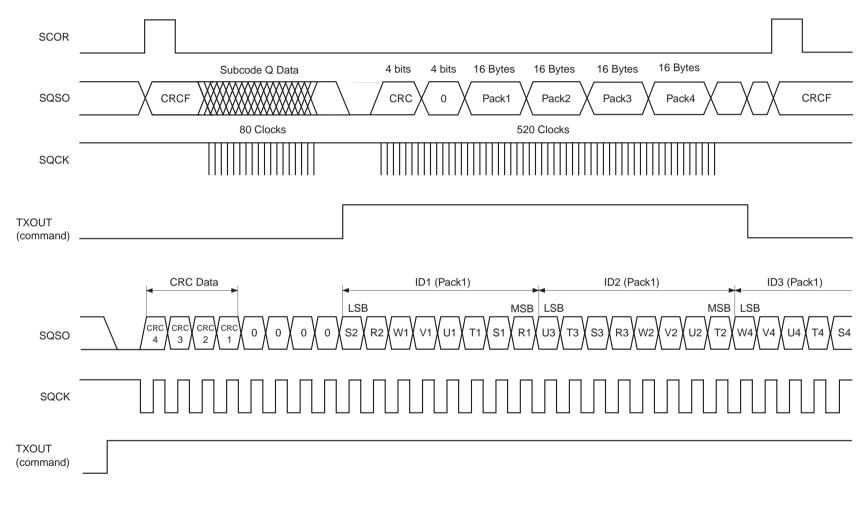

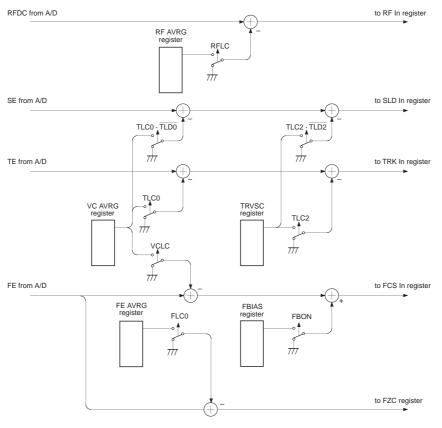

|        |         |            |            |            | 0   | 1    | 1     | 0  | KD7 | KD6 | KD5 | KD4 | KD3 | KD2 | KD1 | KD0 | KRAM DATA (K46)<br>TRACKING HOLD INPUT GAIN (when TGup2 is accessed with THSK = |