# **Smart Multi-Voltage Detector**

### **General Description**

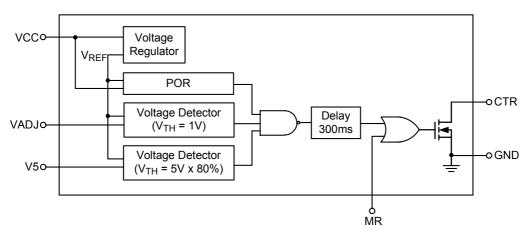

The RT9823 is an integrated smart multi voltage detector supervising two power supply voltage levels including 5V, and another voltage (such as 3.3V or 12V), which can be set via an external resistive voltage divider.

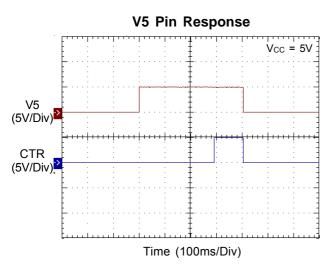

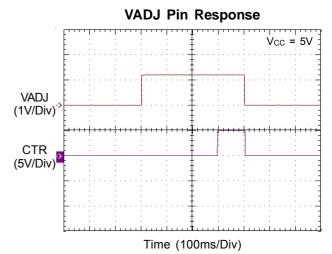

The RT9823 performs supervisory function by sending out a CTR signal whenever the monitored voltages fall below 80% of the voltage levels. The CTR signal will last the whole period before VCC recovers. Once the supervising voltages are recovered to higher than 80% of the voltage levels, the CTR signal will be released after a 300ms delay time.

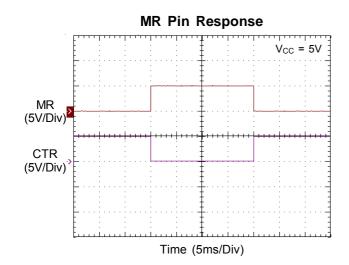

MR (Manual Reset) controls the CTR signal when the two monitored power supply voltages are at normal voltage levels. When the MR signal is in logic high, the CTR signal will be pulled low immediately.

The RT9823 is available in a SOT-23-6 package.

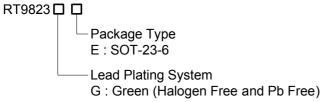

## **Ordering Information**

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# **Marking Information**

ES= : Product Code DNN : Date Code

#### **Features**

- Capable of Monitoring Two Inputs Precisely

- VCC Connect to 5V or 3.3V Standby Power

- Detection Threshold Voltages

- → V5:5V x 80%

- ▶ VADJ: 1V (Using Resistor Divider)

- Accuracy: ±2%

- CTR (Open Drain Output Active Low)

- Built-in Recovery Delay 300ms

- Manual CTR (MR) Function

- SOT-23-6 Package

- RoHS Compliant and Halogen Free

### **Applications**

- LCD TV or Monitors

- Consumer Electronic Products

- System Voltage Detector

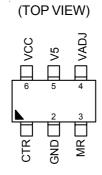

### **Pin Configurations**

SOT-23-6

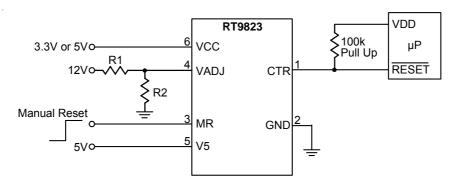

# **Typical Application Circuit**

**Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                      |  |  |  |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | CTR      | Reset Output (Open Drain, Active-Low) . When $V_{CC}$ > POR, V5 > 80%, and $V_{ADJ}$ > 1V, CTR will delay 300ms and become high. Once V5 or $V_{ADJ}$ is < 80%, the signal will become low. When MR is high, CTR will become low. |  |  |  |

| 2       | GND      | Ground.                                                                                                                                                                                                                           |  |  |  |

| 3       | MR       | Manual Reset Input. Manual reset with internal pull high resister (1M $\Omega$ ), H : CTR = Low; L : CTR signal is dependent on voltage detector output.                                                                          |  |  |  |

| 4       | VADJ     | Voltage Detection Input. Connect 12V or other power with external resistive voltage divider to this pin. The $V_{ADJ}$ logic-high threshold voltage is 1V.                                                                        |  |  |  |

| 5       | V5       | 5V Voltage Detection Input. The detection threshold is 5V x 80%.                                                                                                                                                                  |  |  |  |

| 6       | VCC      | Supply Input. Connect this pin to standby power from system.                                                                                                                                                                      |  |  |  |

# **Function Block Diagram**

### **Absolute Maximum Ratings** (Note 1)

| • VCC, MR, CTR, V5, VADJ                                                    | 0.3V to 6.5V   |

|-----------------------------------------------------------------------------|----------------|

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| SOT-23-6                                                                    | 0.4W           |

| Package Thermal Resistance (Note 2)                                         |                |

| SOT-23-6, θ <sub>JA</sub>                                                   | 250°C/W        |

| SOT-23-6, θ <sub>JC</sub>                                                   | 135°C/W        |

| • Junction Temperature                                                      | 150°C          |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C          |

| • Storage Temperature Range                                                 | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM (Human Body Mode)                                                       | 2kV            |

| MM (Machine Mode)                                                           | 200V           |

|                                                                             |                |

## **Recommended Operating Conditions** (Note 4)

#### **Electrical Characteristics**

( $V_{CC}$  = 5V,  $T_A$  = 25°C, unless otherwise specified)

| Paramete                                | er         | Symbol                | Test Conditions                                           | Min  | Тур  | Max  | Unit |  |

|-----------------------------------------|------------|-----------------------|-----------------------------------------------------------|------|------|------|------|--|

| VCC Supply Current                      |            | I <sub>VCC</sub>      | Without load                                              |      |      | 200  | μА   |  |

| VCC Operating Voltage                   |            | V <sub>CC</sub>       |                                                           | 2.97 | 5    | 5.94 | V    |  |

| VCC POR Rising                          |            | V <sub>POR</sub>      |                                                           |      | 2.8  |      | V    |  |

| VCC POR Hysteresi                       | s          | V <sub>POR_Hys</sub>  |                                                           |      | 0.15 |      | V    |  |

| Voltage Detector & MUTE Threshold       |            |                       |                                                           |      |      |      |      |  |

| V5 High Threshold Voltage               |            | V <sub>V5_TH</sub>    |                                                           | 3.92 | 4    | 4.08 | V    |  |

| VADJ High Threshold Voltage             |            | $V_{VADJ\_TH}$        |                                                           | 0.98 | 1    | 1.02 | V    |  |

| Manual Reset Input<br>Threshold Voltage | Logic-High | V <sub>IH</sub>       |                                                           | 2    |      |      | V    |  |

|                                         | Logic-Low  | V <sub>IL</sub>       |                                                           |      |      | 0.8  | ٧    |  |

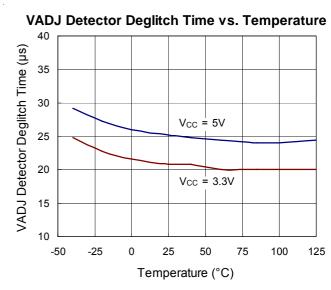

| Voltage Detector Deglitch and Delay     |            |                       |                                                           |      |      |      |      |  |

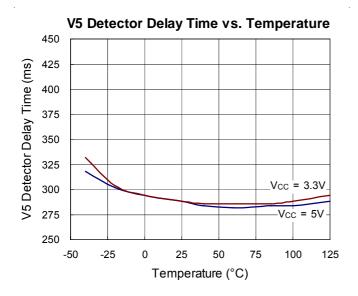

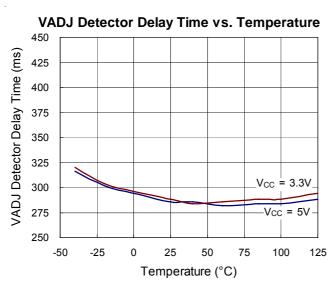

| Voltage Detectors Delay Time            |            | t <sub>DELAY</sub>    |                                                           | 200  | 300  |      | ms   |  |

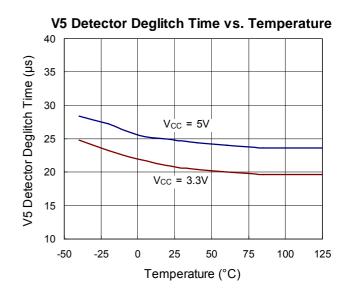

| Voltage Detectors Deglitch Time         |            | t <sub>DEGLITCH</sub> |                                                           |      | 20   |      | μS   |  |

| Output : Open Drain                     |            |                       |                                                           |      |      |      |      |  |

| CTR Output Low Voltage                  |            | V <sub>OL_CTR</sub>   | V <sub>CC</sub> = 3.3V, 5mA sinking current at CTR output |      |      | 0.3  | V    |  |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device is reliability.

- Note 2.  $\theta_{JA}$  is measured in natural convection at  $T_A$  = 25°C on a low-effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard. The measurement case position of  $\theta_{JC}$  is on the lead of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

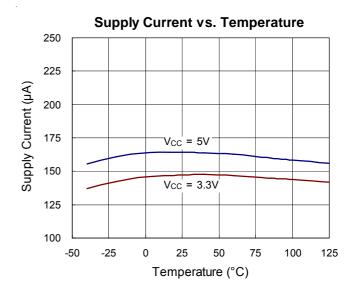

# **Typical Operating Characteristics**

### **Application Information**

The RT9823 smart voltage detector monitors two voltage levels at the same time to ensure that the micro processor is operated within the recommended input voltage range. In conventional reset IC application, to monitor one power rail needs one reset IC. The RT9823 can monitor two power rails simultaneously, by using just one reset IC. The RT9823 also provides a Manual reset (MR) function for easy application. Glitch rejection is implemented in the RT9823 to prevent false operation and eliminate additional de-bouncing circuitry.

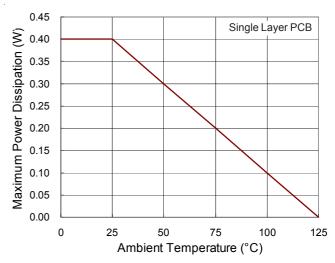

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications of the RT9823, the maximum junction temperature is 125°C and  $T_A$  is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For SOT-23-6 packages, the thermal resistance,  $\theta_{JA}$ , is 250°C/W on a standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by the following formula :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (250^{\circ}C/W) = 0.4W$  for SOT-23-6 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J~(MAX)}$  and thermal resistance,  $\theta_{JA}$ . For the RT9823 package, the derating curve in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curves for RT9823 Package

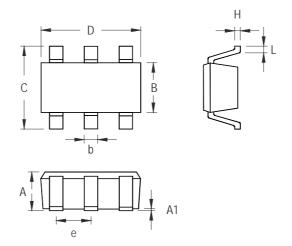

#### **Outline Dimension**

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |  |  |  |

|--------|------------|----------------|----------------------|-------|--|--|--|--|

| Symbol | Min        | Max            | Min                  | Max   |  |  |  |  |

| А      | 0.889      | 1.295          | 0.031                | 0.051 |  |  |  |  |

| A1     | 0.000      | 0.152          | 0.000                | 0.006 |  |  |  |  |

| В      | 1.397      | 1.803          | 0.055                | 0.071 |  |  |  |  |

| b      | 0.250      | 0.560          | 0.010                | 0.022 |  |  |  |  |

| С      | 2.591      | 2.997          | 0.102                | 0.118 |  |  |  |  |

| D      | 2.692      | 3.099          | 0.106                | 0.122 |  |  |  |  |

| е      | 0.838      | 1.041          | 0.033                | 0.041 |  |  |  |  |

| Н      | 0.080      | 0.254          | 0.003                | 0.010 |  |  |  |  |

| L      | 0.300      | 0.610          | 0.012                | 0.024 |  |  |  |  |

**SOT-23-6 Surface Mount Package**

#### **Richtek Technology Corporation**

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

#### **Richtek Technology Corporation**

Taipei Office (Marketing)

5F, No. 95, Minchiuan Road, Hsintien City

Taipei County, Taiwan, R.O.C.

Tel: (8862)86672399 Fax: (8862)86672377

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.