# BL22P14 LCD Type 8-Bit OTP MCU

**USER MANU**

V1.0 (2010-4-15)

上海贝岭股份有限公司 Shanghai Belling Co., Ltd.

Page 1 of 33

上海贝岭股份有限公司 Shanghai Belling Co., Ltd.

## LCD Type 8-bit OTP MCU BL22P14

## 1. General Description

BL22P14 is an 8-bit high performance single chip microcontroller. It provides two group configurable I/O ports, two timers and multiple LCD for household appliances.

#### 2. Features

- ♦ 8-bit CISC core (compatible with Motorola HC05)

- ♦ Low power (1uA@5V in stop mode)

- ♦ Operating Voltage: 2.5-5.5V(<=4MHz) , 3.5-5.5V(<=8MHz)</p>

- ♦ Operating temperature: -40°C~85°C

- ♦ 4K\*8bit ROM

- → 128byte RAM

- ♦ LCD diver with 18\*4, 19\*3, 19\*2 and 19\*1

- ♦ 14 bidirectional I/O

- ♦ PA as keyboard interrupt source

- ♦ Two external interrupt

- ♦ An 8-bit Timer

- ♦ A 16-bit Timer

- ♦ Watch dog

- ♦ Buzzer output

- ♦ LVD (typical 3.3V)

- ♦ LVR (typical 3.0V)

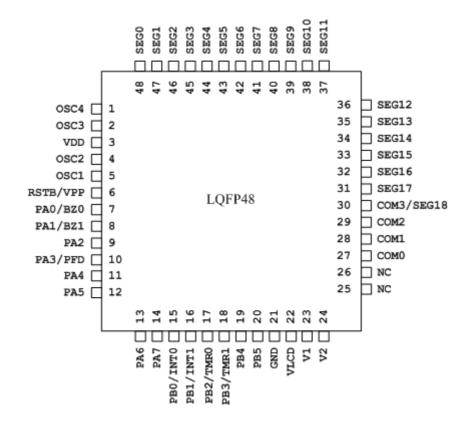

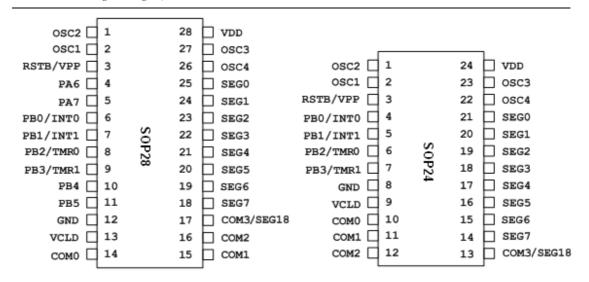

## 3. Pin Assignments

## 4. Pin Descriptions

#### SSOP48/LQFP48/SOP28/SOP24

| Pin name   | In/Out | Share Description     | Pin Description                                        |  |

|------------|--------|-----------------------|--------------------------------------------------------|--|

| PA0        | I/O    | BZ0-buzzer output (+) |                                                        |  |

| PA1        | I/O    | BZ1-buzzer output (-) | Bit-programmable I/O port                              |  |

| PA2        | I/O    |                       | for Schmitt trigger input or                           |  |

| PA3        | I/O    | PFD output            | push-pull, each bit can be                             |  |

| PA4        | I/O    |                       | configured as a input                                  |  |

| PA5        | I/O    |                       | with pull-high resistor or                             |  |

| PA6        | I/O    |                       | keyboard interrupt input                               |  |

| PA7        | I/O    |                       |                                                        |  |

| PB0        | I/O    | INT0                  | Dit was are made to 1/O mant                           |  |

| PB1        | I/O    | INT1                  | Bit-programmable I/O port for Schmitt trigger input or |  |

| PB2        | I/O    | TMR0-TIMER0 input     | push-pull, each bit can be                             |  |

| PB3        | I/O    | TMR1-TIMER1 input     | configured as a input                                  |  |

| PB4        | I/O    |                       | with pull-high resistor                                |  |

| PB5        | I/O    |                       | with pair riight redictor                              |  |

| VSS        |        |                       | Ground                                                 |  |

| VLCD       |        |                       | LCD voltage supply                                     |  |

| V1         |        |                       | LCD filter capacitor                                   |  |

| V2         |        |                       | LOD filter capacitor                                   |  |

| COM0       | 0      |                       |                                                        |  |

| COM1       | 0      |                       | COM output of LCD                                      |  |

| COM2       | 0      |                       |                                                        |  |

| COM3/SEG18 | 0      |                       | COM or SEG of LCD                                      |  |

| SEG17~SEG0 | 0      |                       | SEG output of LCD                                      |  |

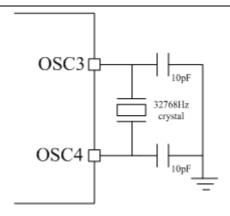

| OSC4       | 0      |                       | 32768Hz crystal oscillator                             |  |

| OSC3       | I      |                       | 32100012 Crystal Oscillator                            |  |

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 3 of 33

| VDD  |   |       | Power supply             |  |

|------|---|-------|--------------------------|--|

| OSC2 | 0 |       | Crystal oscillator or RC |  |

| OSC1 | I | clock |                          |  |

| RSTB | I | VPP   | System reset input       |  |

## 5. Function Descriptions

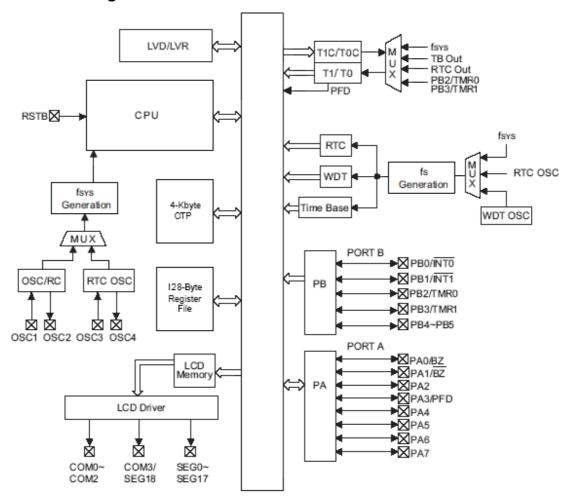

### 5.1 Block Diagram

#### 5.2 Address Spaces

\$0000-\$006F: Control registers

\$0070-\$007F: LCD data \$0080-\$00FF: RAM \$0100-\$0FFF: Reserved \$1000-\$1FFF: OTP ROM

### 5.3 Control Registers

| Register name | Address | R/W | Reset Value |

|---------------|---------|-----|-------------|

| PA            | \$00    | R/W | 0000 0000   |

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 4 of 33

| DDRA      | \$01      | R/W | 0000 0000 |  |

|-----------|-----------|-----|-----------|--|

| PB        | \$02      | R/W | 00 0000   |  |

| DDRB      | \$03      | R/W | 00 0000   |  |

| KBIM      | \$04      | R/W | 0000 1000 |  |

| PBPR      | \$05      | R/W | 00 0000   |  |

| T0D       | \$06      | R/W | 0000 0000 |  |

| T0C       | \$07      | R/W | 00-0 0000 |  |

| T1DH      | \$08      | R/W | 0000 0000 |  |

| T1DL      | \$09      | R/W | 0000 0000 |  |

| T1C       | \$0A      | R/W | 0000 0000 |  |

| INTC0     | \$0B      | R/W | 00 0000   |  |

| INTC1     | \$0C      | R/W | 0000 0000 |  |

| BZCR      | \$0D      | R/W | 000000    |  |

| MCR1      | \$0E      | R/W | 00u00     |  |

| MCR2      | \$0F      | R/W | 0000 0000 |  |

| RSTFR     | \$10      | R/W | rrrr      |  |

| LCDD[9:0] | \$79-\$70 | W   | xxxx xxxx |  |

| LCDCON    | \$7A      | R/W | 0000 0000 |  |

#### NOTE:

- : Not used:

x: Undefined;

u: Determined by OPBIT[4];

r: Determined by reset type

#### 5.4 Clock

Device supplies four clock sources: Crystal oscillator, external RC, RTC and WDT. First three clock sources can be as system clock Fsys and all can be as internal clock Fs.

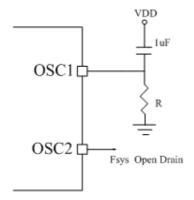

#### 5.4.1 System Clock: Fsys

System clock is main operate clock for device. It is configured by OTP OPTION BIT (FSYS1, FSYS0) to select a clock source.

FSYS1、FSYS0

00 / 11: Fsys=Fosc/2

01: Fsys=Frc/2

10: Fsys=Frtc/2

#### 5.4.2 Internal Clock: Fs

Fs is the clock of Buzzer, RTC interrupt, Time Base interrupt, LCD and Watchdog. It is configured by OTP OPTION BIT (FS1, FS0) to select a clock source. If RTC or WDT is selected, device will still operate in stop mode.

FS1、FS0

00 / 11: Fs=Fsys

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 5 of 33

01: Fs=Frtc10: Fs=Fwdt

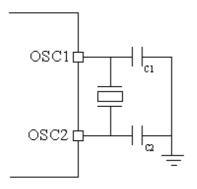

#### 5.4.3 Crystal Oscillator

Crystal oscillator provides the clock of 455KHz-8MHz. A crystal should be connected between the pin of OSC1 and OSC2.

| Frequency of crystal | Value of C1/C2 |

|----------------------|----------------|

| 8MHz                 | 0/10p          |

| 4MHz                 | 0/10p/20p      |

| 455KHz               | 100p/200p      |

#### 5.4.4 External RC Oscillator

Using external RC oscillator, a resistor between OSC1 and VSS is required. The value of resistor  $800K\Omega\sim40K\Omega$ , the frequency of clock will be  $400KHz\sim8MHz$ . OSC2 can output clock of Fsys if connecting a resistor from OSC2 to VDD. However, the frequency of oscillator may vary with VDD, temperature and chip itself due to process variations. It is therefore, not suitable for timing sensitive operations where accurate frequency is desired.

#### 5.4.5 RTC Oscillator

RTC oscillator provides the clock of 32768Hz. A crystal should be connected between the pin of OSC3 and OSC4. If it is the clock source of Fs, RTC oscillator will still work in stop mode.

The RTC Oscillator circuit can be controlled to oscillate quickly by setting the "QOSC" bit (bit 3 of register of MCR2). It is recommend to turn on the quick oscillating function upon power on and then turn it off after 2 seconds.

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 6 of 33

#### 5.4.6 WDT oscillator

WDT is a dedicated RC oscillator and output clock of T=65us@5V. If it is the source of Fs, RTC oscillator will still work in stop mode. The power is only 3uA@5V.

#### 5.5 Low Power Mode

There are two low power modes: STOP and WAIT.

In stop mode, Fsys is turn off and can be waked up by :

- ♦ Keyboard interrupt.

- ♦ External interrupt.

- ♦ Interrupt from module whose clock source is from RTC oscillator or WDT.

In wait mode, only turn off clock of CPU and all interrupt can wake it up.

#### 5.6 RESET

BL22P14 can be reset in four ways:

- 1) by external power-on-reset

- 2) by the external reset input pin(P12) pulled low

- 3) by the digital watchdog peripheral timing out

- 4) by Low Voltage reset (LVR)

There is a dedicated register to write reset type.

#### RSTFR (\$10): Reset Flag Register

.7-.4 Not used

.3 RSTF3

0: no WDT reset

1: WDT reset

Write "0" to clear the bit, write "1" is null.

.2 RSTF2

0: no LVR reset

1: LVR reset

Write "0" to clear the bit, write "1" is null.

.1 RSTF1

0: no RES reset

1: RES reset

Write "0" to clear the bit, write "1" is null.

.0 RSTF0

0: no power on reset

1: power on reset

Write "0" to clear the bit, write "1" is null.

#### **5.7 I/O PORTS**

There are two group I/O ports: PA and PB. PA has 8 I/O ports and PB has 6 I/O ports. All ports have pull up resistors. PA has the function of keyboard interrupt.

The control registers are PA, PB, DDRA, DDRB, KBIM and PBPR.

#### PA (\$00): Data register of PORT A

.7-.0 PA[7:0]

PA is the data register for Port A.

### DDRA(\$01): Data direction register of PORT A

.7-.0 DDRA[7:0] 00000000

DDRA is used to select data direction of PA.

When DDRAi is "0", PAi is input; When DDRAi is "1", PAi is output.

#### PB (\$02): Data register of PORT B

.5-.0 PB[5:0]

PB is the data register for Port B.

#### DDRB(\$03): Data direction register of PORT B

.5-.0 DDRB[5:0]

DDRB is used to select data direction of PB.

When DDRBi is "0", PBi is input; When DDRBi is "1", PBi is output.

#### KBIM(\$04): Keyboard interrupt mask register

.7-.0 KBE[7:0]

KBIM is configured to enable keyboard interrupt. When KBEi is "1", keyboard interrupt of PAi is turn on, PAi keeps input and its pull up resistor is effective. Besides, if needing keyboard interrupt active, KBIE (bit 3 of register of INTC0) should be "1". When KBEi is "0", keyboard interrupt of PAi is turn off.

#### PBPR(\$05): PORTB pull-up register

.5-.0 PBP[5:0]

PBPR is configured to enable pull up resistors of PB. When PBPi is "0", resistor of PBi is ineffective. When PBPi is "1", resistor of PBi is effective. When PB is output, PBPR is no effect.

#### 5.8 LCD

LCD drives 4\*18 at most. When the clock of LCD comes from RTC oscillator or WDT oscillator, LCD will still operate in stop mode.

#### **LCD** memory

The memory of LCD is located at 70H-79H. Any data written into 70H-79H will affect LCD

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 8 of 33

display. When written "1", the corresponding bit is turn display on; When written "0", the corresponding bit is turn display off. Before writing data to memory, the memory is inconstant.

|      | S S S S S S S S S S S S S S S S S S S | SEG | - SEG2 | SEG3 | SEG4 | OSE05 | 9SE06 | - SEG7 | SEG16  | - SEG17 | - SEG18 |     |

|------|---------------------------------------|-----|--------|------|------|-------|-------|--------|--------|---------|---------|-----|

| COMO | b0                                    | b4  | b0     | b4   | b0   | b4    | b0    | b4     | b0     | b4      | b0      |     |

| COM1 | b1                                    | b5  | b1     | b5   | b1   | b5    | b1    | b5     | b1     | b5      | b1      | П   |

| COM2 | b2                                    | b6  | b2     | b6   | b2   | b6    | b2    | b6     | <br>b2 | b6      | b2      | - : |

| COM3 | b3                                    | b7  | b3     | b7   | b3   | b7    | b3    | b7     | b3     | b7      | b3      |     |

|      | 70                                    | Н   | 71     | Н    | 17:  | 2H    | 7:    | ЗН     | <br>78 | ВН      | 79      | ЭН  |

#### **LCD register- LCDCON**

### LCDCON(\$7A): LCD Control Register

.7-.4 PS[3:0] 0000

Dividing frequency of clock source

$0000: 1/2^5$

0001: 1/2<sup>6</sup>

$0010: 1/2^7$

$0011: 1/2^8$

$0100: 1/2^9$

0101: 1/2<sup>10</sup>

0110: 1/2<sup>11</sup>

0111: 1/2<sup>12</sup>

1000: 1/2<sup>13</sup>

1001: 1/2<sup>14</sup>

1010: 1/2<sup>15</sup>

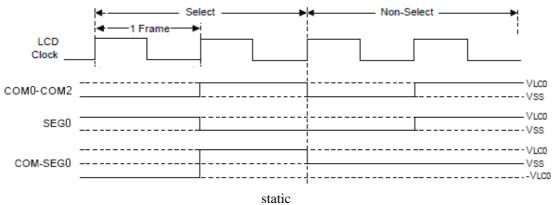

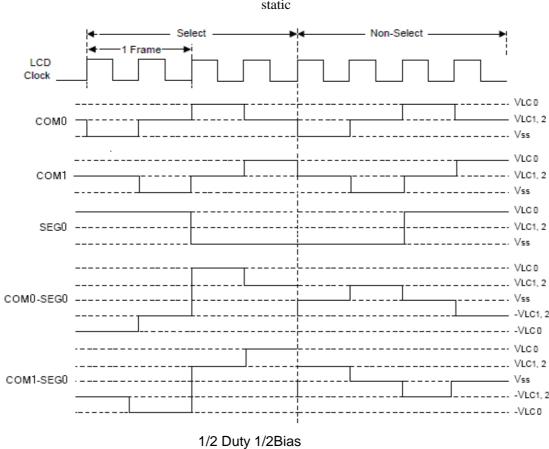

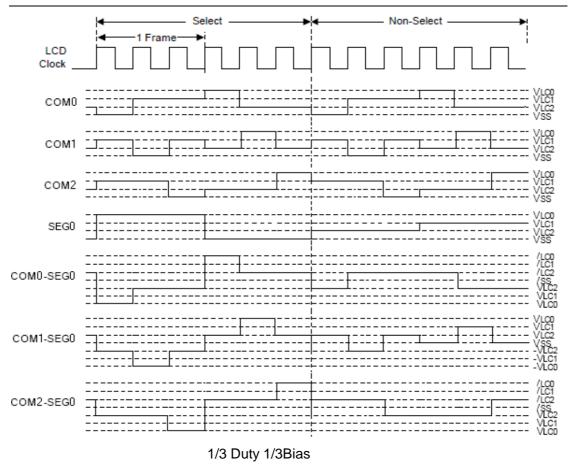

.3-.1 DBS [2:0] 000

**Duty/Bias select**

000: 1/4 Duty 1/3 Bias(COM0-COM3, SEG0-SEG17)

001: 1/3 Duty 1/3 Bias(COM0-COM2, SEG0-SEG18)

010: 1/2 Duty 1/2Bias(COM0-COM1, SEG0-SEG18)

011: 1/3 Duty 1/2Bias(COM0-COM2, SEG0-SEG18)

others: static(COM0-COM2, SEG0-SEG18)

.1 Not used

.0 LCDON 0

0: all COM/SEG output high

1: LCD can display

#### **Clock of LCD**

The clock source of LCD is Fs, and dividing frequency is set by bit 4-7 of LCDCON. Usually, the frame frequency is set at 25Hz to 250Hz.

If WDT is the clock source, dividing frequency should be  $1/2^5 \sim 1/2^8$ .

THE FRAME FREQUENCY WHEN WDT IS CLCOK SOURCE (Hz)

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 9 of 33

#### **BL22P14 USER MANUAL**

| LCD frequency             | Static | 1/2Duty | 1/3Duty | 1/4Duty |

|---------------------------|--------|---------|---------|---------|

| Fs/2 <sup>5</sup> =512 Hz | 512    | 256     | 171     | 128     |

| Fs/2 <sup>6</sup> =256 Hz | 256    | 128     | 85      | 64      |

| Fs/2 <sup>7</sup> =128 Hz | 128    | 64      | 43      | 32      |

| Fs/2 <sup>8</sup> =64 Hz  | 64     | 32      | 21      | 16      |

If RTC oscillator is the clock source, dividing frequency should be  $1/2^6 \sim 1/2^9$ .

THE FRAME FREQUENCY WHEN RTC IS CLCOK SOURCE(Hz)

| LCD frequency             | Static | 1/2Duty | 1/3Duty | 1/4Duty |

|---------------------------|--------|---------|---------|---------|

| Fs/2 <sup>6</sup> =512 Hz | 512    | 256     | 171     | 128     |

| Fs/2 <sup>7</sup> =256 Hz | 256    | 128     | 85      | 64      |

| Fs/2 <sup>8</sup> =128 Hz | 128    | 64      | 43      | 32      |

| Fs/2 <sup>9</sup> =64 Hz  | 64     | 32      | 21      | 16      |

Other dividing frequency  $(1/2^{10} \sim 1/2^{15})$  is used when OSC or RC is clock source.

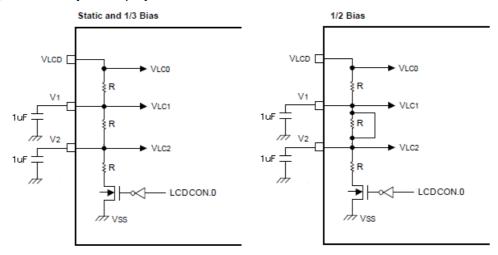

#### LCD drive voltage

VLCD is the voltage source of LCD and divided to four voltage level by internal resistors. VLCD may connect to VDD or other voltage. Two capacitors connecting to V1 and V2 will improve stability for display.

| LCD Power Supply | Static Mode          | 1/2 Bias             | 1/3 Bias             |  |

|------------------|----------------------|----------------------|----------------------|--|

| V <sub>LC0</sub> | V <sub>LCD</sub>     | V <sub>LCD</sub>     | V <sub>LCD</sub>     |  |

| V <sub>LC1</sub> | 2/3 V <sub>LCD</sub> | 1/2 V <sub>LCD</sub> | 2/3 V <sub>LCD</sub> |  |

| V <sub>LC2</sub> | 1/3 V <sub>LCD</sub> | 1/2 V <sub>LCD</sub> | 1/3 V <sub>LCD</sub> |  |

| V <sub>SS</sub>  | 0 V                  | 0 V                  | 0 V                  |  |

#### **COM/SEG** output

The output number can be 4 COM and 18 SEG (48pin), 4 COM and 8 SEG (28pin and 24pin). COM3 and SEG18 are at common pin. COM3 is effective only at 1/4duty mode and other mode is SEG18.

| pin duty Drive number | bias |

|-----------------------|------|

|-----------------------|------|

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 10 of 33

|          | 1 (static) | 19×1          | 1/3 |

|----------|------------|---------------|-----|

| 40       | 1/2        | 19×2          | 1/2 |

| 48       | 1/3        | 19 <b>×</b> 3 | 1/3 |

|          | 1/4        | 18×4          | 1/3 |

| 24 or 28 | 1 (static) | 9×1           | 1/3 |

|          | 1/2        | 9×2           | 1/2 |

|          | 1/3        | 9×3           | 1/3 |

|          | 1/4        | 8×4           | 1/3 |

#### **COM and SEG output wave**

TEL: 86-21-64850700 WEB: www.belling.com.cn

#### 5.9 Timer - TIMER0

TIMER0 is an 8bit count-up counter. The counter clock source may come from Fsys or RTC time-out signal or external source. Using external clock input from TMR0 (PB2) allows the user to count external events, measure time internals or pulse widths or generate an accurate time base. While using the internal clock allows the user to generate an accurate time base.

There is a data register - T0D. Before use, a data must be written to T0D. TIMER0 will count from \$00 to this data and generate an interrupt. Then counter restart from \$00. TIMER0 has three operate mode:

- Timer mode The timer clock comes from internal selected clock source.

- ♦ Event mode To count external signal from TMR0, may count up when the signal is from low to high or high to low.

- ❖ Pulse width measure mode To measure pulse width from TMR0. When TE is "1", TIMER0 will start counting after TMR0 receives a transient from low to high(from high to low when TE is "0") until TMR0 returns to the original level and resets the TON. (Note: TON is the enable of TIMER0, and only automatic reset at pulse width measure mode. If other two modes, resetting TON must be finished by program.) In other words, only one cycle measurement can be made until TON is set. Then data reading from T0D is the value of pulse width. In the case of counter overflows, the counter is reload from the counter preload register and issues an interrupt request as other two modes. And the value of pulse width

must add the time of generating the interrupt.

It has two registers: T0D、T0C。

#### T0D (\$06): Timer0 data register

#### .7-.0 T0D[7:0] 00000000

The data register of Timer0 is writable and readable. When writing it, this data is the overflow data and TIMER0 will count from \$00 to this data driven by internal or external signal. When reading, it is the real-time counting data. If writing to T0D, new overflow data will be effective in next counting cycle.

When TON is "0", writing to T0D will clear the counting data, and count from \$00 after TON is set. But if do not writing to T0D when TON is "0", it will count from previous data which TIMER0 stop at.

#### T0C (\$07): Timer 0 control register

#### .7-.6 TM[1:0] 00

Mode select

00: TIMER0 not work

01: Event mode, and setting PB2 input

10: Timer mode

11: Pulse wide mode, and setting PB2 input

#### .5 Not used

.4 TS 0

Internal clock source select, ineffective in event mode.

0: Fsys as clock source

1: RTC time-out signal as clock source

#### .3 TON 0

Counting enable bit

0: TIMER0 disable

1: TIMER0 enable

#### .2 TE 0

Defining active edge of counting, Ineffective in timer mode.

0: active on low to high

1: active on high to low

#### .1-.0 PS[1:0] 00

Dividing frequency select, ineffective in event mode. The clock source is select by TS.

00: 1

01: 1/4

10: 1/16

11: 1/64

The overflow of TIMER0 can be applied to a PFD output (Programmable frequency divider)

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 13 of 33

at PA3 by option.

#### 5.10 Timer – TIMER1

TIMER1 is a 16bit count-up counter. The counter clock source may come from Fsys or RTC time-out signal or external source or overflow from TIMER0. Using external clock input from TMR1 (PB3) allows the user to count external events, measure time internals or pulse widths or generate an accurate time base.

There are two data register- T1DH and T1DL. Before use, data must be written to T1DH and T1DL. TIMER1 will count from \$0000 to this data and generate an interrupt. Then counter restart from \$0000.

TIMER1 has three operate mode:

- ♦ Timer mode The timer clock comes from internal selected clock source.

- ♦ Event mode To count external signal from TMR1, may count up when the signal is from low to high or high to low.

- ❖ Pulse width measure mode To measure pulse width from TMR1. When TE is "1", TIMER0 will start counting after TMR1 receives a transient from low to high(from high to low when TE is "0") until TMR1 returns to the original level and resets the TON. (Note: TON is the enable of TIMER1, and only automatic reset at pulse width measure mode. If other two modes, resetting TON must be finished by program.) In other words, only one cycle measurement can be made until TON is set. Then data reading from T1DH and T1DL is the value of pulse width. In the case of counter overflows, the counter is reload from the counter preload register and issues an interrupt request as other two modes. And the value of pulse width must add the time of generating the interrupt.

It has three registers: T1DH, T1DL, T1C.

T1DH (\$08): Timer 1 data register (High byte)

.7-.0 T1DH[7:0]

T1DL (\$09): Timer 1 data register (Low byte)

.7-.0 T1DL[7:0]

The data registers of Timer1 are writable and readable. When writing it, this data is the overflow data and TIMER1 will count from \$0000 to this data driven by internal or external signal. When reading, it is the real-time counting data. If writing to the data registers, new overflow data will be effective in next counting cycle.

When TON is "0", writing to the data registers will clear the counting data, and count from \$00 after TON is set. But if do not writing to the data registers when TON is "0", it will count from previous data which TIMER1 stop at.

One point must be note: there are two data registers, so it can not read or write

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 14 of 33

data synchronously. When writing, it must write T1DL at first and then T1DH. When reading, it must read T1DH at first and then T1DL.

#### T1C (\$0A): Timer 1 control register

.7-.6 TM[1:0] 00

Mode select

00: TIMER0 not work

01: Event mode, and setting PB3 input

10: Timer mode

11: Pulse wide mode, and setting PB3 input

.5-.4 TS[1:0] 00

Internal clock source select, ineffective in event mode.

00: Fsys as clock source

01: RTC time-out signal as clock source

10: Ftbi (time base interrupt) as clock source

11: Ftmr0 (overflow from TIMER0) as clock source

.3 TON 0

Counting enable bit

0: TIMER1 disable

1: TIMER1 enable

.2 TE 0

Defining active edge of counting, Ineffective in timer mode.

0: active on low to high

1: active on high to low

.1-.0 PS[1:0] 00

Dividing frequency select, ineffective in event mode. The clock source is select by TS.

00: 101: 1/410: 1/16

11: 1/64

The overflow of TIMER0 can be applied to a PFD output (Programmable frequency divider) at PA3 by option.

#### 5.11 Interrupt

The device provides two external interrupts, two internal timer interrupts, an internal time base interrupt, an internal real time clock interrupt, eight keyboard interrupts, a software interrupt and an external reset. Interrupts PC address and priority are in the following table (priority is from low to high).

| Address   | Interrupt |

|-----------|-----------|

| 1FE0:1FE1 | Reserved  |

| 1FE2:1FE3 | Reserved  |

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 15 of 33

| 1FE4:1FE5 | Reserved |

|-----------|----------|

| 1FE6:1FE7 | Reserved |

| 1FE8:1FE9 | Reserved |

| 1FEA:1FEB | Reserved |

| 1FEC:1FED | Reserved |

| 1FEE:1FEF | TBI      |

| 1FF0:1FF1 | RTCI     |

| 1FF2:1FF3 | T1I      |

| 1FF4:1FF5 | TOI      |

| 1FF6:1FF7 | KBI      |

| 1FF8:1FF9 | INT1     |

| 1FFA:1FFB | INT0     |

| 1FFC:1FFD | SWI      |

| 1FFE:1FFF | RESET    |

The interrupt control registers INTC0 and INTC1 are used to set enable/disable status and interrupt request flags. Once an interrupt subroutine is serviced, other interrupts are all blocked. This scheme may prevent any further interrupt nesting.

All these interrupts except software interrupt support a wake-up function.

The request flags of KBI, INTO and INT1 are "0" if relevant interrupt is turn off. But the request flags of T0I, T1I, RTCI and TBI are not affected by enable bit.

### INTC0 (\$0B): Interrupt control register 0

- .7-.6 not used

- .5 KBIE 0

Keyboard interrupt enable/disable

- 0: KBI disable

- 1: KBI enable

- .4 KBIF 0

Keyboard interrupt flag

- 0: KBI has not interrupt request

- 1: KBI has interrupt request

- .3 INT1E 0

External interrupt 1 enable/disable

- 0: INT1 disable

- 1: INT1 enable and setting PB1 input with pull-up resistor

- .2 INT1F 0

External interrupt 1 flag

- 0: INT1 has not interrupt request

- 1: INT1 has interrupt request

- .1 INT0E 0

External interrupt 0 enable/disable

- 0: INT0 disable

- 1: INTO enable and setting PB0 input with pull-up resistor

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 16 of 33

#### .0 INT0F 0

External interrupt 0 flag

- 0: INTO has not interrupt request

- 1: INTO has interrupt request

#### INTC1 (\$0C): Interrupt control register 1

#### .7 TBIE 0

Time base interrupt enable/disable

- 0: TBI disable

- 1: TBI enable

#### .6 TBIF 0

Time base interrupt flag

- 0: TBI has not interrupt request

- 1: TBI has interrupt request

#### .5 RTCIE 0

Real time clock (RTC) interrupt enable/disable

- 0: RTCI disable

- 1: RTCI enable

#### .4 RTCIF 0

RTC interrupt flag

- 0: RTCI has not interrupt request

- 1: RTCI has interrupt request

#### .3 T1IE 0

TIMER1 interrupt enable/disable

- 0: T1I disable

- 1: T1I enable

#### .2 T1IF 0

TIMER1 interrupt flag

- 0: T1I has not interrupt request

- 1: T1I has interrupt request

#### .1 TOIE 0

TIMER0 interrupt enable/disable

- 0: T0I disable

- 1: T0I enable

#### .0 T0IF 0

TIMER0 interrupt flag

- 0: T0I has not interrupt request

- 1: T0I has interrupt request

#### 5.12 Low Voltage Detect - LVD

LVD provides the function to monitor voltage supply of chip. The typical LVD voltage is 3.3V. LVDE (bit 7 of MCR1) is enable bit and makes LVD active if it is set. LVDF (bit 5 of MCR1) is flag of LVD and is "1" when VDD is lower than 3.3V.

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 17 of 33

### 5.13 Watch Dog Timer - WDT

The WDT clock source is implemented by Fs. The timer is designed to prevent a software malfunction or sequence from jumping to an unknown location with unpredictable results. WDT can be disabled by clearing WDTE (bit 7 of MCR2) and be cleared by WDTC (bit 5 of MCR2).

WDT is a 16bit timer and will make the device reset when counting to 2<sup>16</sup>. Overflow time is:

```

65536*65us=4.2s (Fs=Fwdt)

65536*30.5us=2s (Fs=Frtc)

65536*0.5us=32.7ms (4MHz crystal, Fs=Fosc/2)

```

### 5.14 Buzzer

BZ0 and BZ1 are buzzer driving output pair. If willing to use the function, the related PA port should be set as an output. The clock source is from Fs. The buzzer is controlled by register BZCR.

#### BZCR (\$0D): Buzzer control register

```

.7-.5 PS[3:0] 0000

Dividing frequency of Fs

Fs/2<sup>12</sup>

0000:

Fs/2<sup>11</sup>

0001:

Fs/2<sup>10</sup>

0010:

Fs/2<sup>9</sup>

0011:

Fs/2<sup>8</sup>

0100:

0101:

Fs/2<sup>7</sup>

Fs/2<sup>6</sup>

0110:

Fs/2<sup>5</sup>

0111:

Fs/2<sup>4</sup>

1000:

Fs/2<sup>3</sup>

1001:

Fs/2^2

1010:

Others: Fs/2

.3-.2 not used

.1 BZ1E 0

0: BZ1 disable

1: BZ1 enable

.0 BZ0E 0

0:

BZ0 disable

```

BZ0 enable

#### 5.15 Timer Base

1:

Timer base offers a periodic time out period to generate a regular internal interrupt. Its time out period ranges from Fs/2<sup>12</sup> to Fs/2<sup>15</sup> selected by bit 5 and bit 4 of MCR2. If time

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 18 of 33

base time out occurs, the related interrupt request flag is set.

#### 5.16 Real Time Clock - RTC

RTC is operated in the same manner as time base that is used to supply a regular internal interrupt. Its time out period ranges from Fs/2<sup>8</sup> to Fs/2<sup>15</sup> selected by bit 2 and bit 0 of MCR2. If RTC time out occurs, the related interrupt request flag is set. RTC time out signal also can be applied to be a clock source of timer for getting a longer time out period.

RTC and time base use the same 15bit counter which is cleared only by system reset. So the first time out period of RTC or time base is uncertain.

## 5.17 Miscellaneous Control Register

There are two miscellaneous control registers to control some functions.

#### MCR1 (\$0E): Miscellaneous control register 1

- .7 LVDE 0

- 0: LVD disable

- 1: LVD enable

- .6 LVDF 0

- 0: VDD is higher than V<sub>LVD</sub>

- 1: VDD is lower than V<sub>LVD</sub>

- .5 LVRE

- 0: LVR disable

- 1: LVR enable

- .4-.2 not used

- .1 PFDE 0

- 0: PFD disable

- 1: PFD enable

- .0 PFDC 0

- 0: PFD clock is from time out of TIMER0

- 1: PFD clock is from time out of TIMER1

**Note:** PFD is share with PA3. If outputting PFD, PA3 should be output and data register of PA3 must be written "0".

#### MCR2 (\$0F): Miscellaneous control register 2

- .7 WDTE 0

- 0: WDT disable

- 1: WDT enable

- .6 WDTC 0

- 0: useless

- 1: clear WDT

Note: when read this bit, it is always "0".

.5-.4 TBPS[1:0] 00

Time base interrupt period select

00: 2<sup>15</sup>\*Fs 01: 2<sup>14</sup>\*Fs

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 19 of 33

10: 2<sup>13</sup>\*Fs

11: 2<sup>12</sup>\*Fs

.3 QOSC 0

Quickly oscillating select

0: Quickly oscillating enable

1: Quickly oscillating disable

.2-.0 RT[2:0] 000

RTC interrupt period select

000: 2<sup>15</sup>\*Fs

001: 2<sup>14</sup>\*Fs

010: 2<sup>13</sup>\*Fs

011: 2<sup>12</sup>\*Fs

100: 2<sup>11</sup>\*Fs

101: 2<sup>10</sup>\*Fs

110: 2<sup>9</sup>\*Fs

111: 2<sup>8</sup>\*Fs

#### **5.18 OPBIT**

OPBIT is a special byte in OTP ROM and used to configure some initial functions for the device. OPBIT is set when OTP written.

.7 ENCR

0: OTP read protection

1: OTP can be read

.6 Not used

.5 LCD control in stop mode

0: LCD on in stop mode

1: LCD off in stop mode

.4 LVREO

0: LVR off

1: LVR on

.3-.2 FS[1:0]

00、11: Fs=Fsys

01: Fs=Frtc

10: Fs=Fwdt

.1-.0 FSYS[1:0]

00 \ 11: Fsys=Fosc/2

01: Fsys=Frc/2

10: Fsys=Frtc/2

#### 6. ELECTRICAL DATA

#### 6.1 Absolute Maximum Ratings

(T<sub>A</sub>=25°C)

| Parameter             | Symbol         | Condition | Rating                         | Unit       |

|-----------------------|----------------|-----------|--------------------------------|------------|

| Supply voltage        | $V_{DD}$       | -         | $V_{SS}$ -0.3 to $V_{SS}$ +6.5 | V          |

| Input voltage         | VI             | All ports | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 | V          |

| Operating temperature | T <sub>A</sub> | -         | -40 to +85                     | $^{\circ}$ |

| Storage temperature   | Ts             | -         | -65 to +150                    | $^{\circ}$ |

#### **6.2 DC Electrical Characteristics**

$(T_A=25^{\circ}C \ VDD=2.7-5.5V)$

| Parameter                      |                                                    |                               | Min                | Тур | Max                | Unit |

|--------------------------------|----------------------------------------------------|-------------------------------|--------------------|-----|--------------------|------|

| Operate                        | $V_{DD}$                                           | Oscillator Frequency <=4MHz   | 2.5                | -   | 5.5                | V    |

| voltage                        | V DD                                               | Oscillator Frequency <=8MHz   | 3.5                |     | 5.5                | V    |

| LCD operate voltage            | V <sub>LCD</sub>                                   | -                             | 2.5                | -   | 5.5                | V    |

| Input high voltage             | V <sub>IH1</sub>                                   | All ports                     | 0.7V <sub>DD</sub> | ı   | $V_{DD}$           | V    |

| Input low voltage              | V <sub>IL1</sub>                                   | All ports                     | 0                  | ı   | 0.3V <sub>DD</sub> | ٧    |

| I/O ports<br>source<br>current | I <sub>OH</sub>                                    | $V_{OH}=0.9V_{DD}$            | 5                  | 12  | -                  | mA   |

| I/O ports sink current         | I <sub>OL</sub>                                    | $V_{OL}$ =0.1 $V_{DD}$        | 10                 | 20  | -                  | mA   |

| Pull-up<br>resistors           | R <sub>PH</sub>                                    | PA, PB                        | 10                 | 25  | 40                 | kΩ   |

| LVR                            | $V_{LVR}$                                          | -                             | 2.7                | 3.0 | 3.3                | V    |

| LVD                            | $V_{LVD}$                                          | -                             | 3.0                | 3.3 | 3.6                | V    |

| Dynamic<br>working<br>current  | I <sub>DD</sub>                                    | 4MHz clock                    | -                  | 3   | 5                  | mA   |

| Standby                        | STOP mode, LVR off,<br>LCD off                     |                               | -                  | ı   | 1                  | uA   |

| working<br>current             | tandby vorking I <sub>STB</sub> STOP mode, LVR on, |                               | -                  | 10  | 15                 | uA   |

| Current                        |                                                    | STOP mode, LVR off,<br>LCD on | -                  | 20  | 30                 | uA   |

## 7. Instruction Set

## 7.1 Addressing Modes

The addressing modes define the manner in which an instruction is to obtain the data

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 21 of 33

required for its execution. There are 8 modes:

- 1) Inherent

- 2) Immediate

- 3) Direct

- 4) Extended

- 5) Indexed, no offset

- 6) Indexed, 8-bit offset

- 7) Indexed, 16-bit offset

- 8) Relative

#### 7.1.1 Inherent Addressing Mode

In inherent addressing mode, all information required for the operation is already inherently known to the CPU, and no external operand from memory or from the program is needed. The operands, if any, are only the index register and accumulator, and are always 1-byte instructions.

#### 7.1.2 Immediate Addressing Mode

In the immediate addressing mode, the operand is contained in the byte immediately following the opcode. This mode is used to hold a value or constant which is known at the time the program is written and which is not changed during program execution. These are 2-byte instructions, one for the opcode and one for the immediate data byte.

#### 7.1.3 Direct Addressing Mode

The direct addressing mode is similar to the extended addressing mode except the upper byte of the operand address is assumed to be \$00. Thus, only the lower byte of the operand address needs to be included in the instruction. Direct addressing allows you to efficiently address the lowest 256 bytes in memory. This area of memory is called the direct page and includes on-chip RAM and I/O registers. Direct addressing is efficient in both memory and time. Direct addressing mode instructions are usually two bytes, one for the opcode and one for the low-order byte of the operand address.

#### 7.1.4 Extended Addressing Mode

In the extended addressing mode, the address of the operand is contained in the two bytes following the opcode. Extended addressing references any location in the MCU memory space including I/O, RAM, ROM and EPROM. Extended addressing mode instructions are three bytes, one for the opcode and two for the address of the operand.

#### 7.1.5 Indexed, No Offset Addressing Mode

In the indexed, no-offset addressing mode, the effective address of the instruction is contained in the 8-bit index register. Thus, this addressing mode can access the first 256 memory locations. These instructions are only one byte.

#### 7.1.6 Indexed, 8-bit Offset Addressing Mode

In the indexed, 8-bit offset addressing mode, the effective address is obtained by adding

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 22 of 33

the contents of the byte following the opcode to the contents of the index register. This mode of addressing is useful for selecting the kth element in an n element table. To use this mode, the table must begin in the lowest 256 memory locations and may extend through the first 511 memory locations (IFE is the last location which the instruction may access). Indexed 8-bit offset addressing can be used for ROM, RAM, or I/O. This is a 2-byte instruction with the offset contained in the byte following the opcode. The content of the index register (X) is not changed. The offset byte supplied in the instruction is an unsigned 8-bit integer.

#### 7.1.7 Indexed, 16-bit Offset Addressing Mode

In the indexed, 16-bit offset addressing mode, the effective address is the sum of the contents of the 8-bit index register and the two bytes following the opcode. The content of the index register is not changed. These instructions are three bytes, one for the opcode and two for a 16-bit offset.

#### 7.1.8 Relative Addressing Mode

The relative addressing mode is used only for branch instructions. Branch instructions, other than the branching versions of bit-manipulation instructions, generate two machine-code bytes: one for the opcode and one for the relative offset. Because it is desirable to branch in either direction, the offset byte is a signed twos-complement offset with a range of –127 to +128 bytes (with respect to the address of the instruction immediately following the branch instruction). If the branch condition is true, the contents of the 8-bit signed byte following the opcode (offset) are added to the contents of the program counter to form the effective branch address; otherwise, control proceeds to the instruction immediately following the branch instruction.

#### 7.2 Instruction Type

There are 65 instructions in CPU, and can be divided into 5 types.

- 1) Register/Memory Instructions

- 2) Read/Modify-Write Instructions

- 3) Branch Instructions

- 4) Control Instructions

- 5) bit manipulate Instructions

#### 7.3 Instruction Set

| Instruction | Operation      | Function       |   | 5 | Statu | s |   | Address | е      | a      | d)     |

|-------------|----------------|----------------|---|---|-------|---|---|---------|--------|--------|--------|

|             |                |                | Н | I | N     | Z | С | ing     | Opcode | Opdata | #Cvcle |

|             |                |                |   |   |       |   |   | MODE    | 0      | 0      | #      |

| ADC #opr    |                |                |   |   |       |   |   | IMM     | A9     | ii     | 2      |

| ADC opr     |                |                |   |   |       |   |   | DIR     | В9     | dd     | 3      |

| ADC opr     | Add with Carry | A← (A)+(M)+(C) | * | - | *     | * | * | EXT     | C9     | hh     | 4      |

| ADC opr,X   |                |                |   |   |       |   |   | IX2     | D9     | II     | 5      |

TEL: 86-21-64850700 WEB: www.belling.com.cn Page 23 of 33

## **BL22P14 USER MANUAL**

|             | Shanghai Belling Co., Ltd. | T                |   |   | 1 |   |   | ,         |          |    |   |

|-------------|----------------------------|------------------|---|---|---|---|---|-----------|----------|----|---|

| ADC opr,X   |                            |                  |   |   |   |   |   | IX1       | E9       | ee | 4 |

| ADC ,X      |                            |                  |   |   |   |   |   | IX        | F9       | ff | 3 |

|             |                            |                  |   |   |   |   |   |           |          | ff |   |

| ADD #opr    |                            |                  |   |   |   |   |   | IMM       | AB       | ii | 2 |

| ADD opr     |                            |                  |   |   |   |   |   | DIR       | ВВ       | dd | 3 |

| ADD opr     | Add without Carry          | A← (A)+(M)       | * | - | * | * | * | EXT       | СВ       | hh | 4 |

| ADD opr,X   |                            |                  |   |   |   |   |   | IX2       | DB       | II | 5 |

| ADD opr,X   |                            |                  |   |   |   |   |   | IX1       | EB       | ee | 4 |

| ADD ,X      |                            |                  |   |   |   |   |   | IX        | FB       | ff | 3 |

|             |                            |                  |   |   |   |   |   |           |          | ff |   |

| AND #opr    |                            |                  |   |   |   |   |   | IMM       | A4       | ii | 2 |

| AND opr     |                            |                  |   |   |   |   |   | DIR       | B4       | dd | 3 |

| AND opr     | Logical AND                | A← (A) ∧(M)      | - | - | * | * | - | EXT       | C4       | hh | 4 |

| AND opr,X   |                            |                  |   |   |   |   |   | IX2       | D4       | II | 5 |

| AND opr,X   |                            |                  |   |   |   |   |   | IX1       | E4       | ee | 4 |

| AND ,X      |                            |                  |   |   |   |   |   | IX        | F4       | ff | 3 |

|             |                            |                  |   |   |   |   |   |           |          | ff |   |

| ASL opr     |                            |                  |   |   |   |   |   | DIR       | 38       | dd | 5 |

| ASLA        | Arithmetic Shift Left      |                  |   |   |   |   |   | INH       | 48       |    | 3 |

| ASLX        | (Same as LSL)              | 0                | - | - | * | * | * | INH       | 58       |    | 3 |

| ASL opr,X   | (Same as LSL)              | b7 b0            |   |   |   |   |   | IX1       | 68       | ff | 6 |

| ASL ,X      |                            |                  |   |   |   |   |   | IX        | 78       |    | 5 |

| ASR opr     |                            |                  |   |   |   |   |   | DIR       | 37       | dd | 5 |

| ASRA        |                            |                  |   |   |   |   |   | 1.1.1.1.1 | 47       |    | 3 |

| ASRX        |                            |                  | - | - | * | * | * |           | 57       |    | 3 |

| ASR opr,X   | Arithmetic Shift Right     | b7 b0            |   |   |   |   |   | INH       | 67       | ff | 6 |

| ASR ,X      |                            |                  |   |   |   |   |   | IX1       | 77       |    | 5 |

|             |                            |                  |   |   |   |   |   | IX        |          |    |   |

| BCC rel     | Branch if Carry Bit Clear  | PC ←(PC)+2+rel ? | _ | _ | _ | _ | _ | REL       | 24       | rr | 3 |

| BOO IEI     | Branch ii Garry Bit Glear  | C=0              | _ |   |   |   |   | IVEE      | 27       | '' | 3 |

|             |                            | 0-0              |   |   |   |   |   | DIR(bo)   | 11       | dd | 5 |

|             |                            |                  |   |   |   |   |   | DIR(b1)   | 13       | dd | 5 |

|             |                            |                  |   |   |   |   |   | DIR(b1)   | 15       | dd | 5 |

|             |                            |                  |   |   |   |   |   | DIR(b2)   | 17       | dd | 5 |

| BCLR n opr  | Clear Bit n                | Mn←0             | _ |   | _ | _ | _ | DIR(b3)   | 17       | dd | 5 |

| BOLK II OPI | Olear Dit II               | IVIII—U          |   | _ | _ |   | _ | DIR(b4)   | 19<br>1B | dd | 5 |

|             |                            |                  |   |   |   |   |   | טוע(מס)   | ΙĎ       | uu | Э |

## **BL22P14 USER MANUAL**

| BCS rel   Branch if Carry Bit Set   PC (PC)+2+rel ?   -   -   -   -   REL   25   rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | Shanghai Bennig Co., Etc. |                      |   |   | , | 1 | , |         |    | _  |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------|----------------------|---|---|---|---|---|---------|----|----|---|

| BCS rel   Branch if Carry Bit Set   PC (PC)+2+rel ? REL   25   rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                           |                      |   |   |   |   |   |         |    | dd | 5 |

| BEQ rel   Branch if Equal   PC - (PC)+2+rel ?   REL   27   rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                           |                      |   |   |   |   |   | DIR(b7) |    | dd | 5 |

| BEQ rel         Branch if Equal         PC - (PC)+2+rel ? REL 27 rr           Z=1         Z=1           BHCC rel         Branch if Half Carry Bit Clear         PC - (PC)+2+rel ? REL 28 rr           BHCS rel         Branch if Half Carry Bit PC - (PC)+2+rel ? REL 29 rr           BHI rel         Branch if Higher or Same         PC - (PC)+2+rel ? (C REL 22 rr           BHS rel         Branch if Higher or Same         PC - (PC)+2+rel ? REL 24 rr           BIT #opr         Bit Test Accumulator with Memory Byte         (A) \( \lambda \) (M)         REL 24 rr           BIT opr With Memory Byte         (A) \( \lambda \) (M)         REL 25 rr           BIT opr, X         BIT opr, X           BIT, X         BIT opr, X           BIT, X         C=1           BLO rel         Branch if Lower (Same as BCS)         PC - (PC)+2+rel ? REL 25 rr           BLS rel         Branch if Lower or Same PC - (PC)+2+rel ? (C REL 23 rr           BMC rel         Branch if Interrupt Mask PC - (PC)+2+rel ? I=0 REL 20 rr           Clear         PC - (PC)+2+rel ? I=0 REL 28 rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BCS rel   | -                         | , ,                  | - | - | - | - | - | REL     | 25 | rr | 3 |

| BHCC rel   Branch   PC (PC)+2+rel   ?   -   -   -   -   REL   28   rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | (Same as BLO)             | C=1 (与 BLO 相同)       |   |   |   |   |   |         |    |    |   |

| BHCC rel         Branch if Half Carry Bit Clear         PC (PC)+2+rel ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BEQ rel   | Branch if Equal           | PC ← (PC)+2+rel ?    | - | - | - | - | - | REL     | 27 | rr | 3 |

| BHCS rel   Branch if Half Carry Bit   PC - (PC)+2+rel   ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                           | Z=1                  |   |   |   |   |   |         |    |    |   |

| BHCS rel         Branch if Half Carry Bit Set         PC — (PC)+2+rel ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BHCC rel  | Branch                    | PC← (PC)+2+rel ?     | - | - | - | - | - | REL     | 28 | rr | 3 |

| BHI rel       Branch if Higher       PC ← (PC)+2+rel ? (C → → → → → ← REL → Z2 rr         BHS rel       Branch if Higher or Same       PC ← (PC)+2+rel ? → → → → → ← REL → Z2 rr         BIT #opr Same       Bit Test Accumulator       DIR → B5 → DIR                                                                                                                                           |           | if Half Carry Bit Clear   | H=0                  |   |   |   |   |   |         |    |    |   |

| BHI rel         Branch if Higher         PC - (PC)+2+rel ? (C ∨Z)=0         REL 22 rr           BHS rel         Branch if Higher or Same         PC - (PC)+2+rel ? REL 24 rr           BIT #opr Bit Test Accumulator with Memory Byte         (A) ∧ (M)         REL DIR B5 dd           BIT opr, X BIT opr, X BIT opr, X BIT, X         (A) ∧ (M)         REXT C5 hh           BIT, X         BIT opr, X BIT, X         (A) ∧ (M)         REL DIX F5 ff           BLO rel         Branch if Lower (Same as BCS)         PC - (PC)+2+rel ? REL DIX REL                                                                                                                                                                                                                                                                                                                                                         | BHCS rel  | Branch if Half Carry Bit  | PC← (PC)+2+rel ?     | - | - | - | - | - | REL     | 29 | rr | 3 |

| BHS rel       Branch if Higher or Same       PC → (PC)+2+rel ? → → → → → → → REL       24       rr         BIT #opr       Bit Test Accumulator BIT opr       Bit Test Accumulator with Memory Byte       (A) ∧ (M)       → → → → → → → → → → → → → → → → → → →                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | Set                       | H=1                  |   |   |   |   |   |         |    |    |   |

| BHS rel         Branch if Higher or Same         PC — (PC)+2+rel ? REL         24         rr           BIT #opr Bit Test Accumulator BIT opr With Memory Byte         (A) ∧ (M)         * * * - EXT         C5 hh           BIT opr,X BIT opr,X BIT opr,X BIT, X         IX1         E5 ee           BIT, X         IX1         E5 ee           BIT, X         IX1         E5 ee           BIT, X         C=1         F5 ff           BLS rel         Branch if Lower (Same as BCS)         PC — (PC)+2+rel ? (C over the context of the                                                                                                                                                                                                                                                                                                                                                                    | BHI rel   | Branch if Higher          | PC← (PC)+2+rel ? (C  | - | - | - | - | - | REL     | 22 | rr | 3 |

| Same   C=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                           | ∨Z )=0               |   |   |   |   |   |         |    |    |   |

| BIT #opr BIT pr Bit Test Accumulator With Memory Byte  (A) \( \text{(M)} \)  (A) \( \text{(M)} \)  (A) \( \text{(M)} \)  (BIT opr, X  (BIT opr, X)  (CE option of the companies of th | BHS rel   | Branch if Higher or       | PC ← (PC)+2+rel ?    | - | - | - | - | - | REL     | 24 | rr | 3 |

| BIT opr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | Same                      | C=0                  |   |   |   |   |   |         |    |    |   |

| BIT opr       with Memory Byte       (A) ∧ (M)       * * * - EXT       C5 hh         BIT opr,X       IX2       D5 II         BIT opr,X       IX1       E5 ee         BIT, X       IX       F5 ff         BLO rel       Branch if Lower (Same as BCS)       PC ← (PC)+2+rel ? REL       25 rr         BLS rel       Branch if Lower or Same PC ← (PC)+2+rel ? (C REL       23 rr         VZ )=1       PC ← (PC)+2+rel ? I=0 REL       2C rr         BMI rel       Branch if Minus       PC ← (PC)+2+rel ? REL       2B rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BIT #opr  |                           |                      |   |   |   |   |   | IMM     | A5 | ii | 2 |

| BIT opr,X  BIX  BIX  BIX  BIX  BIX  BIX  BIX  B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BIT opr   | Bit Test Accumulator      |                      |   |   |   |   |   | DIR     | B5 | dd | 3 |