# Asahi KASEI

# AK8853XQ/ VN NTSC/PAL/SECAM Digital Video Decoder

#### Overview

The AK8853 is a single-chip digital decoder for NTSC, PAL, and SECAM composite video signals. Its output data is in YCbCr format, compliant with ITU-R BT.601. Its pixel clock, with a generated clock rate of 27 MHz, synchronizes with the input signal. Its output interface is ITU-R BT.656 compliant. Closed-caption, VBID, and WSS encoded information in the input signal is externally accessible. Microprocessor access is via a I<sup>2</sup>C interface.

#### Features

- Decodes composite video signals NTSC (J, M, 4.43), PAL (B, D, G, H, I, M, N, Nc, 60), SECAM.

- Four input channels, with internal video switch.

- 10-bit ADC 1 channel.

- Internal line-locked and frame-locked PLLs for generation of clock synchronized with input signal.

- Internal PGA (-6 dB to 6 dB).

- Adaptive automatic gain control (AGC).

- Auto color control (ACC).

- Image adjustment (contrast, saturation, brightness, hue, sharpness).

- Automatic input signal detection.

- Adaptive 2-D Y/C separation.

- PAL decoding phase correction.

- ITU-R BT.656 format output (with 4:2:2\_8 bit parallel\_EAV/SAV)

- Closed-caption signal decoding (output via register).

- WSS signal decoding (output via register).

- Macrovision signal detection (Macrovision certification).

- Power down function.

- I<sup>2</sup>C control.

- 1.70~2.00 V core power supply.

- 1.70~3.60 V interface power supply.

- Operating temperature range: -40°C to 105°C. (AK8853XQ)

- Operating temperature range: −40°C to 85°C. (AK8853VN)

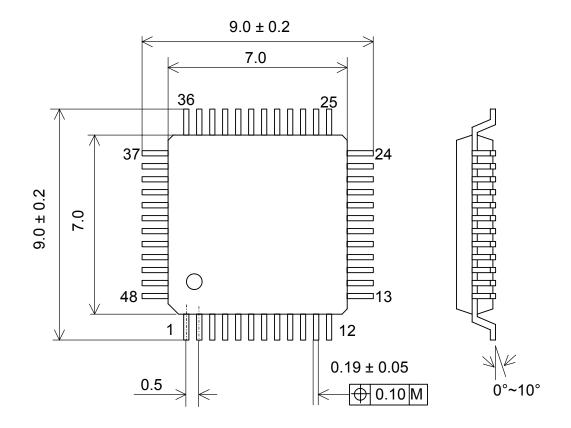

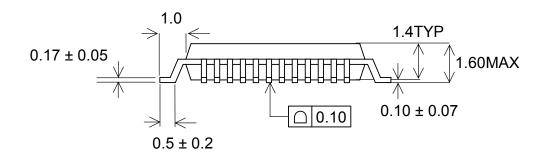

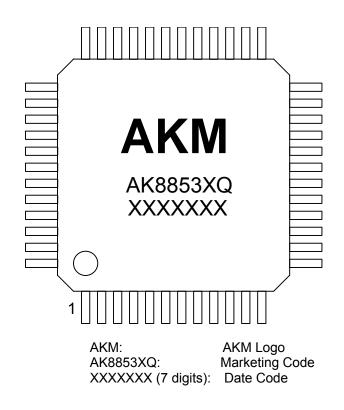

- 48-pin LQFP package. (AK8853XQ)

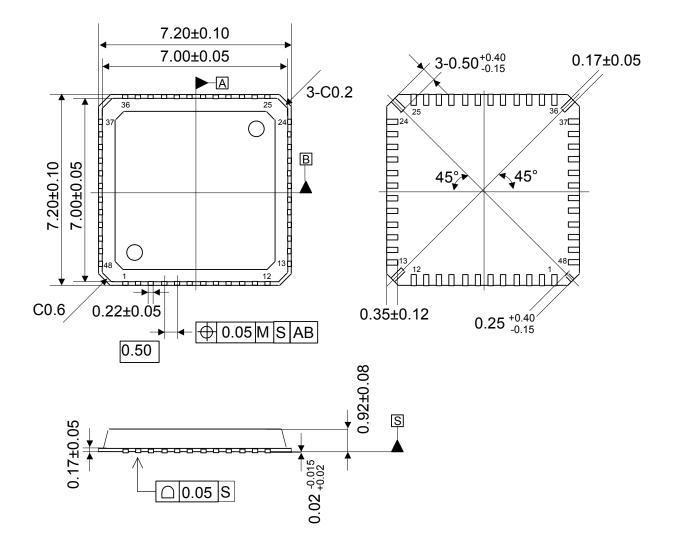

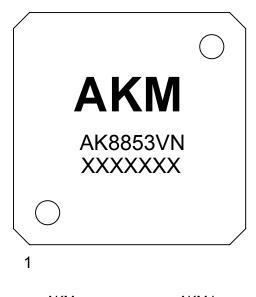

- 48-pin QFN package. (AK8853VN)

(Note) The difference between AK8853XQ and AK8853VN is operating temperature range and package type.

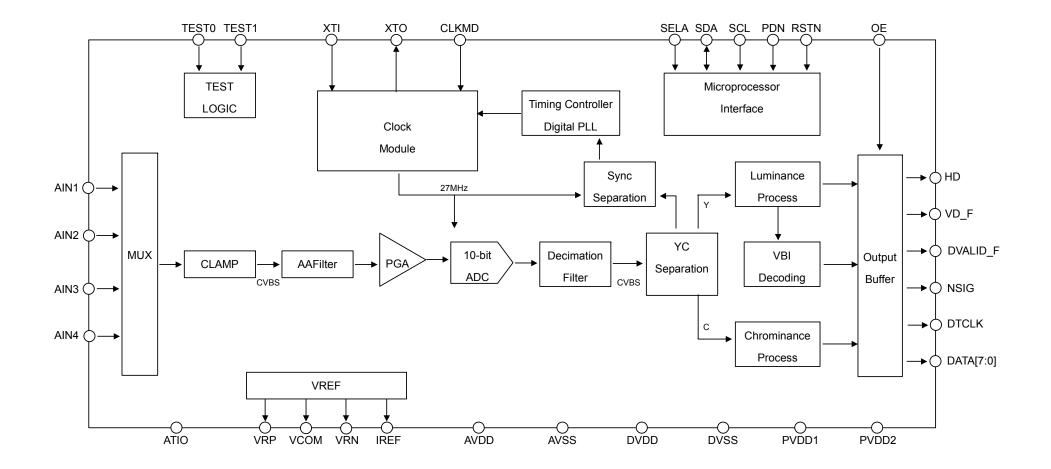

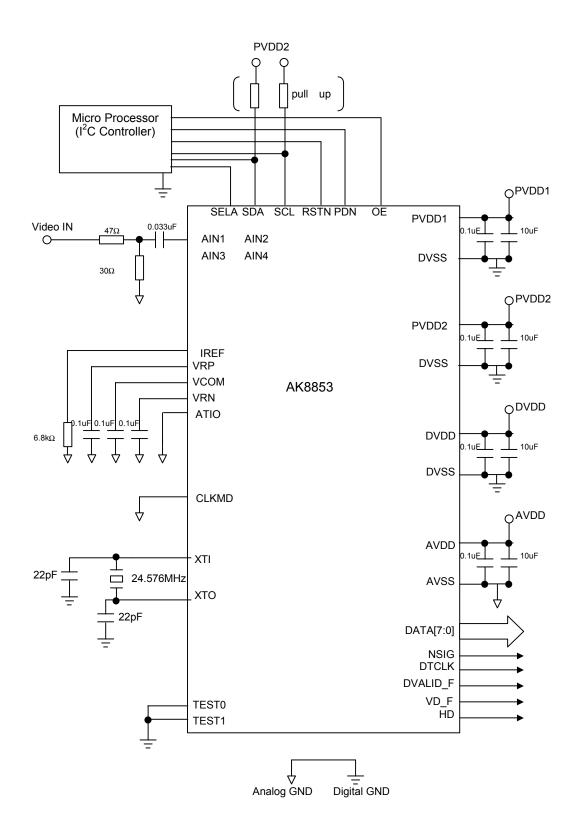

# 1. Functional block diagram

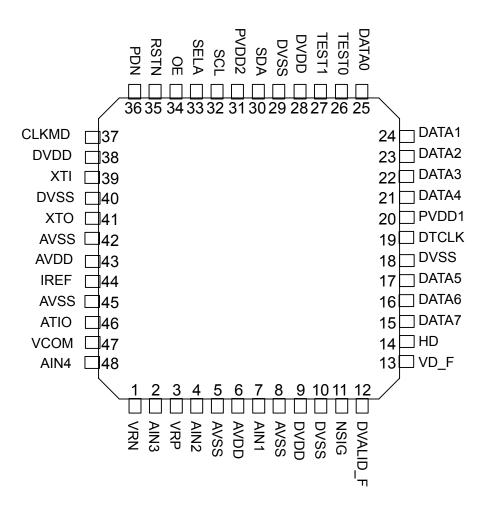

2. Pin assignment – 48 pins LQFP/ 48 pins QFN

# 3. Pin functions

| Pin<br>No. | Symbol       | P/S <sup>1</sup> | I/O <sup>2</sup> | Description                                                                                                                                                                                                       |

|------------|--------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VRN          | А                | 0                | Internal reference negative voltage pin for AD converter.<br>Connect to AVSS via ≥0.1 µF ceramic capacitor.                                                                                                       |

| 2          | AIN3         | А                | I                | Analog video signal input pin. Connect via 0.033 $\mu F$ capacitor and voltage-splitting resistors as shown in Sec. 11.                                                                                           |

| 3          | VRP          | А                | 0                | Internal reference positive voltage pin for AD converter.<br>Connect to AVSS via ≥0.1 µF ceramic capacitor.                                                                                                       |

| 4          | AIN2         | А                | I                | Analog video signal input pin. Connect via 0.033 $\mu F$ capacitor and voltage-splitting resistors as shown in Sec. 11.                                                                                           |

| 5          | AVSS         | А                | G                | Analog ground pin.                                                                                                                                                                                                |

| 6          | AVDD         | Α                | Р                | Analog power supply pin.                                                                                                                                                                                          |

| 7          | AIN1         | А                | I                | Analog video signal input pin. Connect via 0.033 $\mu F$ capacitor and voltage-splitting resistors as shown in Sec. 11.                                                                                           |

| 8          | AVSS         | Α                | G                | Analog ground pin.                                                                                                                                                                                                |

| 9          | DVDD         | D                | Р                | Digital power supply pin.                                                                                                                                                                                         |

| 10         | DVSS         | D                | G                | Digital ground pin.                                                                                                                                                                                               |

| 11         | NSIG         | P1               | 0                | Shows status of synchronization with input signal.<br>Low: Signal present (synchronized).<br>High: Signal not present or not synchronized.<br>See Table below for relation of output to OE, PDN, RSTN pin status. |

| 12         | DVALID_<br>F | P1               | 0<br>(I/O)       | DVALID/FIELD signal output pin.<br>DVALID and FIELD output signals switched by register setting.<br>Used as I/O pin in Test Mode.<br>See Table below for relation of output to OE, PDN, RSTN pin status.          |

| 13         | VD_F         | P1               | 0                | Vertical timing/ field timing signal output pin.<br>VD and FIELD output signals switched by register setting.<br>See Table below for relation of output to OE, PDN, RSTN pin status.                              |

| 14         | HD           | P1               | 0<br>(I/O)       | Horizontal timing signal output pin.<br>Used as I/O pin in Test Mode.<br>See Table below for relation of output to OE, PDN, RSTN pin status.                                                                      |

| 15         | DATA7        | P1               | 0<br>(I/O)       | Data output pin. (MSB)<br>Used as I/O pin in Test Mode.<br>See Table below for relation of output to OE, PDN, RSTN pin status.                                                                                    |

| 16         | DATA6        | P1               | 0<br>(I/O)       | Data output pin.<br>Used as I/O pin in Test Mode.<br>See Table below for relation of output to OE, PDN, RSTN pin status.                                                                                          |

| 17         | DATA5        | P1               | 0<br>(I/O)       | Data output pin.<br>Used as I/O pin in Test Mode.<br>See Table below for relation of output to OE, PDN, RSTN pin status.                                                                                          |

| 18         | DVSS         | D                | G                | Digital ground pin.                                                                                                                                                                                               |

| 19         | DTCLK        | P1               | 0                | Data clock output pin.<br>Approx. 27 MHz clock output.<br>See Table below for relation of output to OE, PDN, RSTN pin status.                                                                                     |

| 20         | PVDD1        | P1               | Р                | I/O power supply pin.                                                                                                                                                                                             |

| 21         | DATA4        | P1               | 0<br>(I/O)       | Data output pin.<br>Used as I/O pin in Test Mode.<br>See Table below for relation of output to OE, PDN, RSTN pin status.                                                                                          |

<sup>1</sup>Power supply: A, AVDD; D, DVDD; P1, PVDD1; P2, PVDD2. <sup>2</sup>Input/Output: O, output pin; I, intput pin; I/O, input/output pin; P, power supply pin; G, ground connection pin.

| Pin<br>No. | Symbol | P/S <sup>1</sup> | I/O <sup>2</sup> | Description                                                                                                                                                                                       |

|------------|--------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | DATA3  | P1               | 0<br>(I/O)       | Data output pin.<br>Used as I/O pin in Test Mode.<br>See table below for relation of output to OE, PDN, RSTN pin status.                                                                          |

| 23         | DATA2  | P1               | 0<br>(I/O)       | Data output pin.<br>Used as I/O pin in Test Mode.<br>See table below for relation of output to OE, PDN, RSTN pin status.                                                                          |

| 24         | DATA1  | P1               | 0<br>(I/O)       | Data output pin.<br>Used as I/O pin in Test Mode.<br>See table below for relation of output to OE, PDN, RSTN pin status.                                                                          |

| 25         | DATA0  | P1               | 0<br>(I/O)       | Data output pin.<br>Used as I/O pin in Test Mode.<br>See table below for relation of output to OE, PDN, RSTN pin status.                                                                          |

| 26         | TEST0  | D                | I                | Pin for test mode setting. Connect to DVSS.                                                                                                                                                       |

| 27         | TEST1  | D                | I                | Pin for test mode setting. Connect to DVSS.                                                                                                                                                       |

| 28         | DVDD   | D                | Р                | Digital power supply pin.                                                                                                                                                                         |

| 29         | DVSS   | D                | G                | Digital ground pin.                                                                                                                                                                               |

| 30         | SDA    | P2               | I/O              | <ul> <li>I<sup>2</sup>C data pin. Connect to PVDD2 via a pull-up register.</li> <li>Hi-z input possible when PDN=L.</li> <li>Will not accept SDA input during reset sequence.</li> </ul>          |

| 31         | PVDD2  | P2               | Р                | Microprocessor I/F power supply pin.                                                                                                                                                              |

| 32         | SCL    | P2               | I                | I <sup>2</sup> C clock input pin. Use PVDD2 or lower for input.<br>Hi-z input possible when PDN=L.<br>Will not accept SCL input during reset sequence.                                            |

| 33         | SELA   | P2               | I                | I <sup>2</sup> C bus address selector pin.<br>PVDD2 connection: Slave address [0x8A]<br>DVSS connection: Slave address [0x88]                                                                     |

| 34         | OE     | P2               | I                | Output enable pin.<br>L: Digital output pin in Hi-z output mode.<br>H: Data output mode.<br>Hi-z input to OE pin is prohibited.                                                                   |

| 35         | RSTN   | P2               | I                | Reset signal input pin.<br>Hi-z input is prohibited.<br>L: Reset.<br>H: Normal operation.                                                                                                         |

| 36         | PDN    | P2               | I                | Power-down control pin.<br>Hi-z input is prohibited.<br>L: Power-down.<br>H: Normal operation.                                                                                                    |

| 37         | CLKMD  | D                | I                | Clock mode selection pin. Connect to DVDD or DVSS.<br>DVSS connection: For crystal.<br>DVDD connection: For quartz generator or other external<br>clock input; not for crystal.                   |

| 38         | DVDD   | D                | Р                | Digital power supply pin.                                                                                                                                                                         |

| 39         | XTI    | D                | I                | Crystal connection pin.<br>Connect to digital ground via 22 pF capacitor as shown in Sec. 11.<br>Use 24.576 MHz crystal resonator.<br>For input from 24.576 MHz crystal oscillator, use this pin. |

<sup>1</sup>Power supply: A, AVDD; D, DVDD; P1, PVDD1; P2, PVDD2. <sup>2</sup>Input/Output: O, output pin; I, intput pin; I/O, input/output pin; P, power supply pin; G, ground connection pin.

| Pin<br>No. | Symbol | P/S <sup>1</sup> | I/O <sup>2</sup> | Description                                                                                                                                                                                                     |

|------------|--------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40         | DVSS   | D                | G                | Digital ground pin.                                                                                                                                                                                             |

| 41         | ХТО    | D                | 0                | Crystal connection pin.<br>Connect to digital ground via 22 pF capacitor as shown in Sec. 11.<br>Use 24.576 MHz crystal.<br>When PDN=L, output level is DVSS.<br>If crystal is not used, connect to NC or DVSS. |

| 42         | AVSS   | Α                | G                | Analog ground pin.                                                                                                                                                                                              |

| 43         | AVDD   | Α                | Р                | Analog power supply pin.                                                                                                                                                                                        |

| 44         | IREF   | А                | 0                | Reference current setting pin.<br>Connect to ground via 6.8 kΩ (≤1% accuracy) resistor.                                                                                                                         |

| 45         | AVSS   | Α                | G                | Analog ground pin.                                                                                                                                                                                              |

| 46         | ATIO   | Α                | I/O              | Analog test pin. For normal operation, connect to AVSS.                                                                                                                                                         |

| 47         | VCOM   | А                | 0                | Common internal voltage for AD convertor.<br>Connect to AVSS via ≥0.1 µF ceramic capacitor.                                                                                                                     |

| 48         | AIN4   | А                | I                | Analog video signal input pin. Connect via 0.033 $\mu F$ capacitor and voltage-splitting resistors as shown in Sec. 11.                                                                                         |

<sup>1</sup>Power supply: A, AVDD; D, DVDD; P1, PVDD1; P2, PVDD2.

<sup>2</sup>Input/Output: O, output pin; I, intput pin; I/O, input/output pin; P, power supply pin;

G, ground connection pin.

Output pin status as determined by OE, PDN, and RSTN pin status.

| OE | PDN | RSTN | Output1 <sup>1</sup>          | Output2 <sup>1</sup>          |  |

|----|-----|------|-------------------------------|-------------------------------|--|

| L  | х   | х    | Hi-z output                   | L output                      |  |

| Н  | L   | х    | L output                      | L output                      |  |

| н  | Ц   | L    | L output                      | L output                      |  |

|    | 11  | Н    | Default Data Out <sup>2</sup> | Default Data Out <sup>2</sup> |  |

<sup>1</sup> Output1: DATA[7:0], HD, VD\_F, DVALID\_F, DTCLK NSIG

Output2:

If OE=H and PDN=H just after power is turned on, output pin status will be indefinite until internal state is determined by reset sequence.

<sup>2</sup>In the absence of AIN signal input, output will be black data ((Y=0x10, Cb/Cr=0x80). (Blueback output can be obtained by register setting.)

# 4. Electrical specifications

#### 4.1 Absolute maximum ratings

| Parameter                                                | Min  | Max                          | Units | Notes                 |

|----------------------------------------------------------|------|------------------------------|-------|-----------------------|

| Supply voltage                                           |      |                              |       |                       |

| DVDD, AVDD                                               | -0.3 | 2.2                          | V     | _                     |

| PVDD1, PVDD2                                             | -0.3 | 4.2                          | V     |                       |

| Analog input pin voltage A<br>(VinA)                     | -0.3 | AVDD + 0.3 (≤2.2)            | V     | _                     |

| Digital input pin voltage D                              | -0.3 | DVDD + 0.3 (≤2.2)            | V     | XTI, XTO, CLKMD,      |

| (VinD)                                                   | -0.5 | DVDD + 0.3 ( <u>3</u> 2.2)   | v     | TEST0, TEST1          |

| Digital output pin voltage P1                            | -0.3 | PVDD1 + 0.3 (≤4.2)           | V     | DTCLK, DATA[7:0], HD, |

| (VoutP)                                                  | -0.5 | FVDDT+0.3 ( <b>2</b> 4.2)    | v     | VD_F, DVALID_F, NSIG  |

| Digital input pin current P2                             | -0.3 | PVDD2 + 0.3 (≤4.2)           | V     | OE, SELA, PDN, RSTN,  |

| (VinP)                                                   | -0.5 | F VDD2 + 0.3 ( <b>2</b> 4.2) | v     | SDA, SCL              |

| Input pin current (lin)<br>(except for power supply pin) | -10  | 10                           | mA    | _                     |

| Storage temperature                                      | -40  | 125                          | °C    | _                     |

The above supply voltages are referenced to ground pins (DVSS=AVSS) at 0 V (the Reference Voltage). All power supply grounds (AVSS, DVSS) should be at the same electric potential.

If digital output pins are connected to data bus, the data bus operating voltage should be in the same range as shown above for the digital output pin.

#### 4.2 Recommended operating conditions

| Parameter                                                     | Min  | Тур  | Max  | Units | Condition                |

|---------------------------------------------------------------|------|------|------|-------|--------------------------|

| Analog supply voltage (AVDD)<br>Digital supply voltage (DVDD) | 1.70 | 1.80 | 2.00 | V     | AVDD=DVDD                |

| I/O supply voltage (PVDD1)<br>MPU I/F supply voltage (PVDD2)  | 1.70 | 1.80 | 3.60 | V     | PVDD1≥DVDD<br>PVDD2≥DVDD |

| Operating temp. (Ta)                                          | -40  | _    | 105  | °C    | AK8853XQ                 |

| Operating temp. (Ta)                                          | -40  | _    | 85   | °C    | AK8853VN                 |

The above supply voltages are referenced to ground pins (DVSS=AVSS) at 0 V (the Reference Voltage). All power supply grounds (AVSS, DVSS) should be at the same electric potential.

#### 4.3 DC characteristics

Where no specific condition is indicated in the following table, the supply voltage range is the same as that shown for the recommended operating conditions in 4-2 above.

| Parameter                      | Symbol | Min      | Тур | Max       | Units | Condition           |

|--------------------------------|--------|----------|-----|-----------|-------|---------------------|

| Digital P2 input high          | VIH    | 0.8PVDD2 | -   | –         | V     | Case 1 <sup>a</sup> |

| voltage                        | VIC    | 0.7PVDD2 | _   | _         | V     | Case 2 <sup>b</sup> |

| Digital P2 input low           | VIL    | -        | -   | 0.2PVDD2  | V     | Case 1 <sup>a</sup> |

| voltage                        | VIL    | —        | _   | 0.3PVDD2  | V     | Case 2 <sup>b</sup> |

| Digital D input high voltage   | VDIH   | 0.8DVDD  | _   | Ι         | V     | —                   |

| Digital D input low voltage    | VDIL   | Ι        | -   | 0.2DVDD   | V     | —                   |

| Digital input leak current     | IL     | _        | _   | ±10       | uA    | -                   |

| Digital output high voltage    | VOH    | 0.7PVDD1 | _   | Ι         | -     | IOH = -600uA        |

| Digital output low voltage     | VOL    | _        | _   | 0.3PVDD1  | _     | IOL = 1mA           |

| I <sup>2</sup> C (SDA)L output | VOLC   | _        | _   | 0.3 PVDD2 | V     | IOLC = 3mA          |

<sup>a</sup>DVDD = 1.70V~2.00V, 1.70V≤PVDD1<2.70V, 1.70V≤PVDD2<2.70V, Ta: Recommended Operating Temp. <sup>b</sup>DVDD = 1.70V~2.00V, 2.70V≤PVDD1≤3.60V, 2.70V≤PVDD2≤3.60V, Ta: Recommended Operating Temp.

#### Definition of above input/output terms

Digital P2 input: Collective term for SDA, SCL, SELA, OE, PDN, RSTN pin inputs.

Digital D input: Collective term for CLKMD, TEST0, TEST1 pin inputs.

Digital output: Collective term for DTCLK, DATA[7:0], HD, VD\_F, DVALID\_F, NSIG pin outputs. SDA pin output: Not termed digital pin output unless otherwise specifically stated.

# 4.4 Analog characteristics (AVDD=1.8V, Temp.25°C)

Selector clamp

| Selector clamp                |        |     |       |       |          |                                                        |

|-------------------------------|--------|-----|-------|-------|----------|--------------------------------------------------------|

| Parameter                     | Symbol | Min | Тур   | Max   | Units    | Condition                                              |

| Maximum input range           | VIMX   | 0   | 0.50  | 0.60  | $V_{PP}$ | Max value at minimum<br>PGA_GAIN setting               |

| PGA                           |        |     |       |       |          |                                                        |

| Parameter                     | Symbol | Min | Тур   | Max   | Unit     | s                                                      |

| Resolution                    |        | _   | 7     | _     | bits     | 3                                                      |

| Minimum gain                  | GMN    | _   | -6    | —     | dB       |                                                        |

| Maximum gain                  | GMX    | _   | 6     | _     | dB       |                                                        |

| Gain step                     | GST    | _   | 0.094 | 0.235 | dB       |                                                        |

| AD converter                  |        |     |       |       |          |                                                        |

| Parameter                     | Symbol | Min | Тур   | Max   | Units    | Condition                                              |

| Resolution                    | RES    |     | 10    | -     | bits     | _                                                      |

| Operating clock<br>frequency  | FS     | -   | 27    | -     | MHz      | -                                                      |

| Integral nonlinearity         | INL    | -   | 1.0   | 3.0   | LSB      | FS = 27 MHz,<br>PGA_GAIN default setting               |

| Differential nonlinearity     | DNL    | -   | 0.5   | 1.5   | LSB      | FS = 27 MHz,<br>PGA_GAIN default setting               |

| S/N                           | SN     | -   | 53    | _     | dB       | Fin = 1 MHz*, FS = 27 MHz,<br>PGA_GAIN default setting |

| S/(N+D)                       | SND    | -   | 51    | _     | dB       | Fin=1MHz*, FS=27MHz<br>PGA_GAIN default setting        |

| ADC internal common voltage   | VCOM   | _   | 0.9   | _     | V        | -                                                      |

| ADC internal<br>positive VREF | VRP    | -   | 1.1   | _     | V        | -                                                      |

| ADC internal<br>negative VREF | VRN    | _   | 0.7   | _     | V        | -                                                      |

\*Fin = AIN input signal frequency

#### AAF (Anti-Aliasing Filter)

| Parameter          | Symb<br>ol | Min | Тур | Max | Units | Condition |

|--------------------|------------|-----|-----|-----|-------|-----------|

| Pass band ripple   | Gp         | -1  |     | +1  | dB    | 6 MHz     |

| Stop band blocking | Gs         | 10  | 22  | -   | dB    | 27 MHz    |

#### **4.5 Current consumption** (at DVDD = AVDD = PVDD1 = PVDD2 = 1.8V, Ta = Recommended Operating Temp.)

| Parameter         | Symbol | Min | Тур | Max | Units | Condition               |

|-------------------|--------|-----|-----|-----|-------|-------------------------|

| (Active mode)     |        |     |     |     |       | а                       |

| Total             | IDD    |     | 58  | 76  | mA    |                         |

| Analog block      | AIDD   |     | 35  |     | mA    |                         |

| Digital block     | DIDD   |     | 19  |     | mA    | With crystal connected  |

| I/O block         | PIDD   |     | 4   |     | mA    | Load condition: CL=15pF |

| (Power down mode) |        |     |     |     |       |                         |

| Total             | SIDD   |     | ≤1  | 200 | uA    |                         |

| Analog block      | ASIDD  |     | ≤1  |     | uA    |                         |

| Digital block     | DSIDD  |     | ≤1  |     | uA    |                         |

| I/O block         | PSIDD  |     | ≤1  |     | uA    |                         |

<sup>a</sup>With NTSC-J 100% color bar input.

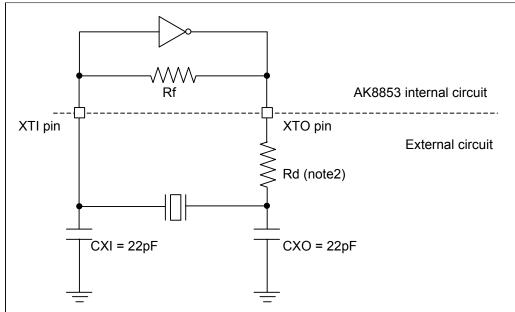

#### 4.6 Crystal circuit block

| ( | Ta  | Recommended    | Operating | Temp)  |

|---|-----|----------------|-----------|--------|

| 1 | Tu. | 1 COOMING TOCO | operating | remp./ |

| Parameter                                            | Symbol         | Min | Тур    | Max  | Units | Notes       |

|------------------------------------------------------|----------------|-----|--------|------|-------|-------------|

| Frequency                                            | f <sub>0</sub> | _   | 24.576 | _    | MHz   | _           |

| Frequency tolerance                                  | ∆f/f           | Ι   |        | ±100 | ppm   | -           |

| Load capacitance                                     | CL             | Ι   | 15     | I    | pF    | -           |

| Effective equivalent resistance                      | Re             | -   | -      | 100  | Ω     | See note 1  |

| Crystal parallel capacitance                         | CO             | -   | 0.9    | -    | pF    | -           |

| XTI terminal external<br>connection load capacitance | CXI            | -   | 22     | -    | pF    | lf CL=15 pF |

| XTO terminal external<br>connection load capacitance | СХО            | _   | 22     | _    | pF    | lf CL=15 pF |

(note1) Effective equivalent resistance generally may be taken as Re = R1 x (1+CO/CL)<sup>2</sup>, where R1 is the crystal series equivalent resistance.

#### Example connection

(note2) Determine need for and appropriate value of limiting resistance (Rd) in accordance with the crystal specifications.

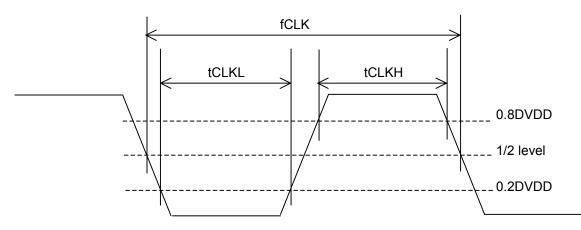

**5. AC timing** (DVDD=1.70V~2.00V, PVDD1=PVDD2=1.70V~3.60V, Recommended Operating Temp.) Load condition: CL=15pF

#### 5.1 Clock input

Set AK8853 clock input as follows.

| Parameter           | Symbol | Min | Тур    | Max  | Units |

|---------------------|--------|-----|--------|------|-------|

| Input CLK           | fCLK   | -   | 24.576 |      | MHz   |

| CLK pulse width H   | tCLKH  | 16  | -      | -    | ns    |

| CLK pulse width L   | tCLKL  | 16  | -      | -    | ns    |

| Frequency tolerance | _      | -   | -      | ±100 | ppm   |

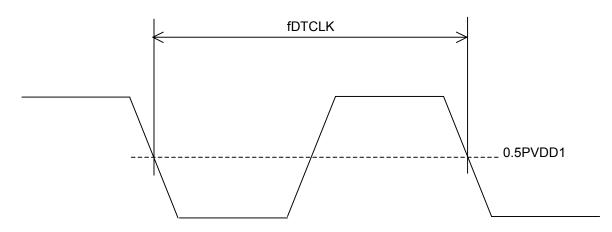

#### 5.2 Clock output (DTCLK output)

| Parameter | Symbol | Min | Тур | Max | Units |

|-----------|--------|-----|-----|-----|-------|

| DTCLK     | fDTCLK | -   | 27  | -   | MHz   |

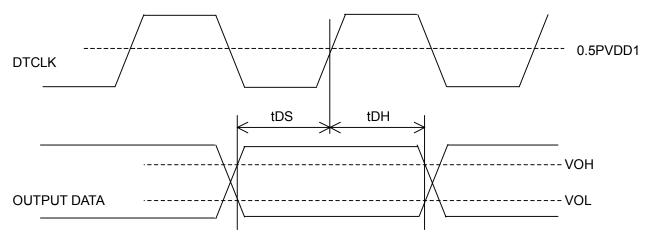

# 5.3 Output data (DATA[7:0], HD, VD\_F, DVALID\_F) timing

| Parameter              | Symbol | Min | Тур | Max | Units |

|------------------------|--------|-----|-----|-----|-------|

| Output Data Setup Time | tDS    | 10  |     |     | nsec  |

| Output Data Hold Time  | tDH    | 10  |     |     | nsec  |

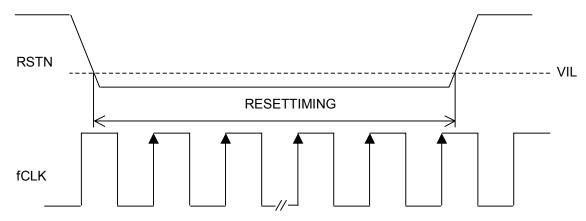

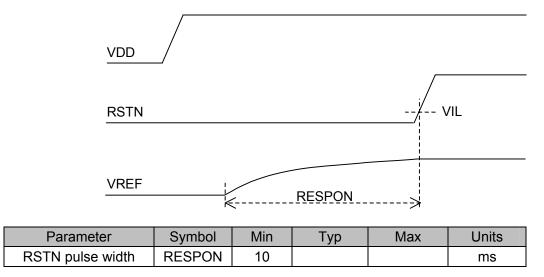

# 5.4 Register reset timing

| Parameter        | Symbol      | Min          | Тур | Max | Units         | Notes                       |

|------------------|-------------|--------------|-----|-----|---------------|-----------------------------|

| RSTN pulse width | RESETTIMING | 100<br>(4.1) | -   | -   | CLK<br>(µsec) | Based on clock leading edge |

Note. Clock input is necessary for reset operation.

RSTN pin must be pulled low following clock application.

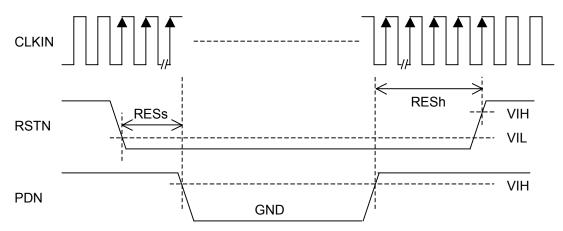

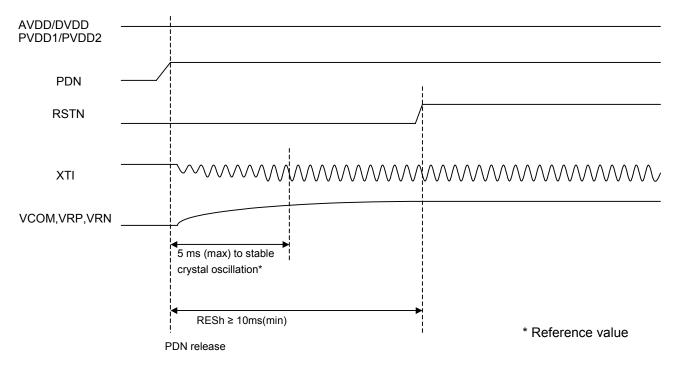

#### 5.5 Power-down sequence and Reset sequence after power-down

Reset must be applied for at least 2048 clock cycles (or 83.33 µs) before setting PDN (PDN=Low). Reset must be applied for at least 10 ms after PDN release (PDN=Hi).

| Parameter                      | Symbol | Min             | Тур | Max | Units       |

|--------------------------------|--------|-----------------|-----|-----|-------------|

| Reset width before setting PDN | RESs   | 2048<br>(83.33) | -   | -   | CLK<br>(µs) |

| Reset width after PDN release  | RESh   | 10              | _   | _   | ms          |

To perform power-down, all control signals must always be brought to the voltage polarity to be used or to ground level.

For any power supply removal, all power supplies must be removed.

Clock input is necessary for resetting.

The power-down sequence for connection of the crystal is as follows.

#### 5.6 Power-on reset

At power-on, reset must be applied until the analog reference voltage and current have stabilized.<sup>1</sup> AVDD/DVDD/PVDD1/PVDD2 should be raised simultaneously at power-on.<sup>2</sup>

<sup>1</sup>Clock input is necessary for resetting.

<sup>2</sup>If not simultaneous, then raise in the order PVDD2 -> AVDD/DVDD -> PVDD1.

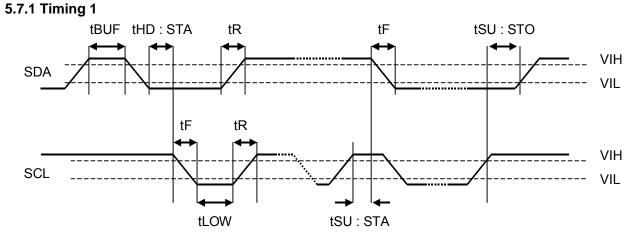

5.7 I<sup>2</sup>C bus input timing (DVDD=1.70V~2.00V, PVDD1=PVDD2=1.70V~3.60V, Recommended Operating Temp.)

| Parameter                   | Symbol  | Min | Max | Units |

|-----------------------------|---------|-----|-----|-------|

| Bus Free Time               | tBUF    | 1.3 |     | usec  |

| Hold Time (Start Condition) | tHD:STA | 0.6 |     | usec  |

| Clock Pulse Low Time        | tLOW    | 1.3 |     | usec  |

| Input Signal Rise Time      | tR      |     | 300 | nsec  |

| Input Signal Fall Time      | tF      |     | 300 | nsec  |

| Setup Time(Start Condition) | tSU:STA | 0.6 |     | usec  |

| Setup Time(Stop Condition)  | tSU:STO | 0.6 |     | usec  |

Note. The timing relating to the I<sup>2</sup>C bus is as stipulated by the I<sup>2</sup>C bus specification, and not determined by the device itself. For details, see I<sup>2</sup>C bus specification.

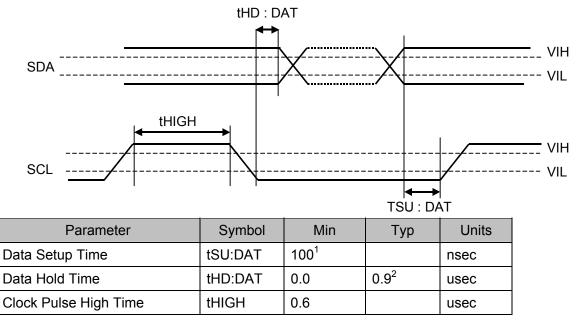

#### 5.7.2 Timing 2

<sup>1</sup> If I<sup>2</sup>C is used in standard mode, tSU: DAT  $\ge$  250 ns is required.

<sup>2</sup> This condition must be met if the AK8853 is used with a bus that does not extend tLOW (to use tLOW at minimum specification).

#### 6. Functional overview

The following key functions are characteristic of the AK8853 and its operational performance.

- (1) It accepts composite video signal (CVBS) input, with 4 input pins available for this purpose. The decode signal is selected via the register.

- (2) It contains an internal analog band limiting filter (anti-aliasing) in front of the AD converter input.

- (3) Its analog circuit clamps the input signal to the sync tip (analog sync tip clamp). Its digital circuit clamps the digitized input data to the pedestal level (digital pedestal clamp).

- (4) It decodes NTSC-M, J; NTSC-4.43; PAL-B, D, G, H, I, N; PAL-Nc, PAL-M, PAL-60; and SECAM video signals, as selected by register setting for input signal category. In auto detection mode, it automatically recognizes the input signal category.

- (5) Its VBI data slicing function enables output of the slicing results as ITU-R BT.601 format digital data.

- (6) Its adaptive AGC function enables measurement of the input signal size and determination of the input signal level.

- (7) Its ACC function enables measurement of the input signal color burst size and determination of the appropriate color burst level.

- (8) It performs adaptive two-dimensional Y/C separation, in which its phase detector selects the best correlation from among vertical, horizontal, and diagonal samples and the optimum Y/C separation mode.

- (9) Its digital pixel spacing adjustor can align vertical positions by vertical pixel positioning.

- (10) It operates in line-locked, frame-locked, or fixed clock mode, with automatic transition and optimum mode selection by automatic scanning.

- (11) In PAL-B, D, G, H, I, and N decoding, it can perform phase-difference correction for each line.

- (12) Its decoded data is ITU-R BT.656 compliant, except in certain cases of fixed-clock operation or poor-quality input signal.

- (13) For connection of devices having no ITU-R BT.656 interface, it shows the active video region by DVALID signal output.

- (14) Its input-stage embedded PGA can be adjusted in the range -6~+6dB by register setting, in gain steps of approximately 0.1 dB/step.

- (15) It detects and separates the sync signal from the digitized input signal. The detected sync signal provides the base timing for decode processing, and the separated sync signal as the basis for calculation of phase error signal and for sampling clock control.

- (16) It judges the chroma signal quality from the color burst of the input signal, and can apply color kill if the signal quality is judged insufficient. It can also apply color kill if the color decode PLL lock is lost.

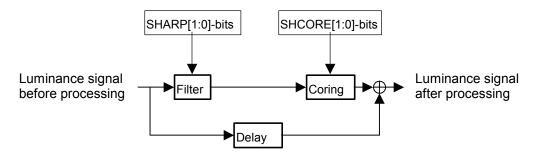

- (17) Its image quality adjustment function includes contrast, brightness, hue, color saturation, and sharpness adjustment.

- (18) Its luminance band limiting filter is adjustable via register setting.

- (19) It can provide sepia output of decoded results.

- (20) It can decode conflated closed caption data, closed caption extended data, VBID(CGMS), and WSS signals, and write them separately to the storage register.

- (21) Its monitoring register enables monitoring of a number of internal functions.

- (22) It enables Macrovision signal type notification, in cases where the Macrovision signal is included in the decoded data.

- (23) It enables U/V signal band adjustment, by switching the low pass filter after C signal demodulating.

- (24) It enables C filter band switching via the register, for Y/C separation.

#### 7. Functional description

#### 7.1 Analog interface

The AK8853 accepts composite video signal (CVBS) input, with 4 input pins available for this purpose. The decode signal is selected via the register.

| INSEL[1:0]-bits | Input channel selection | Notes |

|-----------------|-------------------------|-------|

| [00]            | AIN1                    |       |

| [01]            | AIN2                    |       |

| [10]            | AIN3                    |       |

| [11]            | AIN4                    |       |

#### 7.2 Analog band limiting filter and analog clamp circuit

#### 7.2.1 Analog band limiting filter

The characteristics of the AK8853 internal analog band limiting filter (anti-aliasing), which is in front of the AD converter input, are as follows:

±1dB (~6MHz )

-22dB (27MHz)....Typical value

#### 7.2.2 Analog clamp circuit

The analog circuit of the AK8853 clamps the input signal to the sync tip (analog sync tip clamp). The clamp timing pulse, with its origin at the falling edge of the internally synchronized and separated sync signal, is generated at approximately the central position of the sync signal. Its digital circuit clamps the digitized input data to the pedestal level (digital pedestal clamp), as described in Sec. 7.20 below.

#### 7.3 Input video signal categorization

The AK8853 can decode the following video signals, in accordance with the register setting.

NTSC-M,J NTSC-4.43 PAL-B,D,G,H,I,N PAL-Nc PAL-M PAL-60 SECAM

In auto detection mode, it automatically recognizes the input signal category, from among the above.

# AKM

The register settings for the input signal characterization are essentially as follows.

| VSCF[1:0]-bits | Subcarrier frequency (MHz) | Formats                                            |

|----------------|----------------------------|----------------------------------------------------|

| [00]           | 3.57954545                 | NTSC-M,J                                           |

| [01]           | 3.57561149                 | PAL-M                                              |

| [10]           | 3.58205625                 | PAL-Nc                                             |

| [11]           | 4.43361875                 | PAL-B, D, G, H, I, N, NTSC-4.43,<br>PAL-60, SECAM* |

VSCF[1:0]-bits: Setting for subcarrier frequency of input signal.

\*For SECAM input signal, set VSCF[1:0] to [11].

VCEN[1:0]-bits: Setting for color encode format of input signal.

| VCEN[1:0]-bits | Color encode format | Notes |

|----------------|---------------------|-------|

| [00]           | NTSC                |       |

| [01]           | PAL                 |       |

| [10]           | SECAM               |       |

| [11]           | Reserved            |       |

VLF-bit: Setting for line frequency of each input frame.

| VLF-bit | Number of lines | Notes                               |

|---------|-----------------|-------------------------------------|

| [0]     | 525             | NTSC-M, J, NTSC-4.43, PAL-M, PAL-60 |

| [1]     | 625             | PAL-B, D, G, H, I, N, Nc, SECAM     |

BW-bit: Setting for decoding of input signal as monochrome signal (monochrome mode)

| BW-bit | Signal type                                      |  |  |

|--------|--------------------------------------------------|--|--|

| [0]    | Not monochrome (monochrome mode OFF)             |  |  |

| [1]    | Decode as monochrome signal (monochrome mode ON) |  |  |

In the monochrome mode, the input signal is treated as a monochrome signal, and all sampling data digitized the the AD converter passes through the luminance process and is processed as a luminance signal. Thus, with this bit ON, the signal input to the Y/C separation block is all output as luminance signal data to the luminance signal processing block.

In the monochrome mode, the CbCr code is output as 0x80 (601 level data) regardless of the input.

#### SETUP-bit: Setting for presence or absence of input signal SETUP.

| SETUP-bit | SETUP presence/absence | Notes        |

|-----------|------------------------|--------------|

| [0]       | Setup absent           | -            |

| [1]       | Setup present          | 7.5IRE Setup |

With the Setup present setting, the luminance and color signals are processed as follows:

Luminance signal: Y=(Y-7.5)/0.925

Color signal: U=U/0.925, V=V/0.925

The register settings for auto detection are essentially as follows.

| AUTODET-bit | Auto detection | Notes          |

|-------------|----------------|----------------|

| [0]         | OFF            | Manual setting |

| [1]         | ON             | _              |

The auto detection recognizes the following parameters.

| Number of lines per frame: 525/ | 625 |

|---------------------------------|-----|

| Carrier frequencies: 3.57954545 | ;   |

| 3.57561149                      | )   |

| 3.58205625                      | ;   |

| 4.43361875                      | ;   |

| Color encoding formats: NTSC    |     |

| PAL                             |     |

| SECAN                           | Λ   |

| Monochrome signal: Not monoch   | rom |

onochrome signal: Not monochrome/monochrome Note: Automatic monochrome detection is active if the color kill setting is ON (COLKILL-bit = [1].)

The AK8853 stores the detected parameter to the Input Video Status Register (thus, as an internal notice function).

This enables the host to distinguish among the formats NTSC-M, J; NTSC-4.43; PAL-B, D, G, H, I, N; PAL-M; PAL-Nc; PAL-60; SECAM; and monochrome.

It should be noted that it does not detect NTSC-M, NTSC-J, or PAL-B, D, G, H, I, N formats.

In auto detection, the candidates for detection can be limited as shown below.

| NDMODE Register: For lir | miting auto detection candidates |

|--------------------------|----------------------------------|

|--------------------------|----------------------------------|

| Bit   | Register<br>Name |                         | R/W | Definition                                               |

|-------|------------------|-------------------------|-----|----------------------------------------------------------|

| bit 0 | NDPALM           | No Detect PAL-M bit     | R/W | [0]: PAL-M candidate<br>[1]: PAL-M non-candidate         |

| bit 1 | NDPALNC          | No Detect PAL-Nc bit    | R/W | [0]: PAL-Nc candidate<br>[1]: PAL-Nc non-candidate       |

| bit 2 | NDSECAM          | No Detect SECAM bit     | R/W | [0]: SECAM candidate<br>[1]: SECAM non-candidate         |

| bit 3 | Reserved         | Reserved                | R/W | Reserved                                                 |

| bit 4 | NDNTSC443        | No Detect NTSC-4.43 bit | R/W | [0]: NTSC-4.43 candidate<br>[1]: NTSC-4.43 non-candidate |

| bit 5 | NDPAL60          | No Detect PAL-60 bit    | R/W | [0]: PAL-60 candidate<br>[1]: PAL-60 non-candidate       |

| bit 6 | ND525L           | No Detect 525Line bit   | R/W | [0]: 525 line candidate<br>[1]: 525 line non-candidate   |

| bit 7 | ND625L           | No Detect 625Line bit   | R/W | [0]: 625 line candidate<br>[1]: 625 line non-candidate   |

In making the above register settings, the following restrictions apply,

- 1. Setting both NDNTSC443(bit 4) and NDPAL60(bit 5) to [1] (High) is prohibited.

- 2. Setting both ND525L(bit 6) and ND625L(bit 7) to [1] (High) is prohibited.

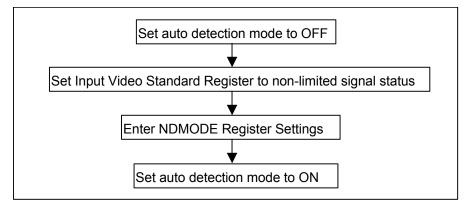

- 3. To limit candidate formats, it is necessary to have the auto detection mode OFF while first setting the register to non-limited signal status and next the NDMODE settings, and then setting the auto detection mode to ON.

#### 7.4 Output data format

In the AK8853, the settings for the output code and the vertical blanking intervals for the output signal are as follows.

| VBIL[2:0]-bits | 525/625 lines | Vertical blanking interval             | Notes    |

|----------------|---------------|----------------------------------------|----------|

| [001]          | 525           | Line1~Line20 and Line263.5~Line283.5   | +1Line   |

| [001]          | 625           | Line623.5~Line23 and Line311~Line336.5 |          |

| [010]          | 525           | Line1~Line21 and Line263.5~Line284.5   | +2Lines  |

|                | 625           | Line623.5~Line24 and Line311~Line337.5 | TZLINES  |

| [011]          | 525           | Line1~Line22 and Line263.5~Line285.5   | +3Lines  |

|                | 625           | Line623.5~Line25 and Line311~Line338.5 | TJLINES  |

| [000]          | 525           | Line1~Line19 and Line263.5~Line282.5   | Default  |

|                | 625           | Line623.5~Line22 and Line311~Line335.5 | Delault  |

| [101]          | 525           | Line1~Line16 and Line263.5~Line279.5   | -3Lines  |

| [101]          | 625           | Line623.5~Line19 and Line311~Line332.5 | -SLITIES |

| [110]          | 525           | Line1~Line17 and Line263.5~Line280.5   | -2Lines  |

| [ 1 I U ]      | 625           | Line623.5~Line20 and Line311~Line333.5 | -2LINES  |

| [111]          | 525           | Line1~Line18 and Line263.5~Line281.5   | -1Line   |

| [111]          | 625           | Line623.5~Line21 and Line311~Line334.5 | - ILINE  |

| [100]          | Reserved      | Reserved –                             |          |

VBIL[2:0]-bits: Settings for vertical blanking interval

As indicated in this table, the default values are Lines 1~19 and 263.5~282.5 for 525-line signals and Lines 623.5~22 and 311~335.5 for 625-line signals, and other specific values are set by entering the difference from these default values.

#### 601LIMIT-bit: Settings for output data code Min/Max

| 601LIMIT-bit | Output data code Min~Max    | Notes   |

|--------------|-----------------------------|---------|

| [0]          | Y: 1∼254<br>Cb, Cr: 1∼254   | Default |

| [1]          | Y: 16∼235<br>Cb, Cr: 16∼240 |         |

The AK8853 data code output format (Y:Cb:Cr=4:2:2) is compliant with ITU-R BT.601. All internal calculating operations are made with Min = 1, Max = 254.

With 601LIMIT-bit set to [1], codes 1~15 and 236~254 are respectively clipped to 16,235.

#### TRSVSEL-bit: Settings for V-bit handling in ITU-R BT.656 format

| TRSVSEL-bit                                     | 525-line                          |                                 | 625-line        |                                    |

|-------------------------------------------------|-----------------------------------|---------------------------------|-----------------|------------------------------------|

|                                                 | V-bit=0                           | V-bit=1                         | V-bit=0         | V-bit=1                            |

| [0]<br>ITU-R BT 656-3<br>compliant              | Line10~Line263<br>Line273~Line525 | Line1~Line9<br>Line264~Line272  | Line23~Line310  | Line1~Line22                       |

| [1]<br>ITU-R BT 656-4<br>SMPTE125M<br>compliant | Line20~Line263<br>Line283~Line525 | Line1~Line19<br>Line264~Line282 | Line336~Line623 | Line311~Line335<br>Line624~Line625 |

These values are unaffected by the VBIL[2:0]-bits setting.

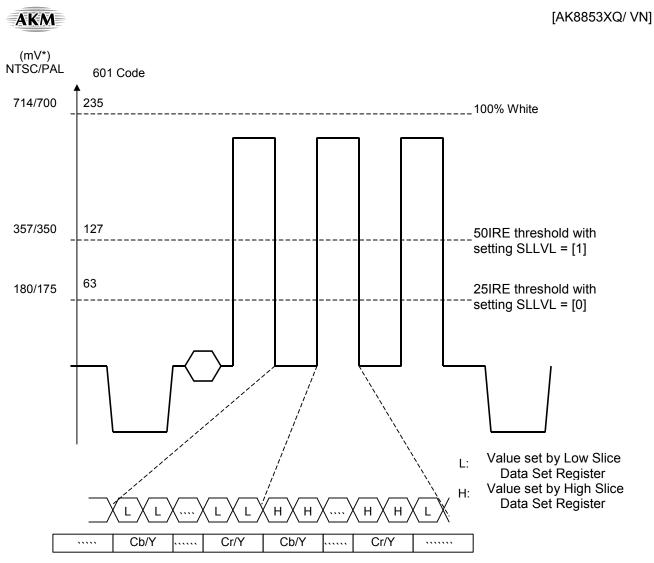

#### SLLVL-bit: Settings for slice level

| SLLVL-bit | Slice level |

|-----------|-------------|

| [0]       | 25IRE       |

| [1]       | 50IRE       |

The results of VBI slicing by the AK8853 slicing function are output as ITU-R BT.601 digital data. The VBI interval is set via VBIL[2:0]-bits. VBI slicing is performed in the luminance signal processing path, so that the Cb/Cr value of the effective line 601 output code is output at the same level as the corresponding luminance signal.

The slice level and the output code are set via the register. The output code value is set via the Hi/Low Slice Data Set Register, as follows.

Hi Slice Data Set Register\*: Setting for higher of two values resulting from slicing.

Default: 0xEB(235)

Low Slice Data Set Register\*: Setting for lower of two values resulting from slicing.

Default: 0x10(16) \*Note that a setting of 0x00 or 0xFF corresponds to a special 601 code.

| VBIDEC[1:0]-bits | Decode data                   | Notes                                                                                         |

|------------------|-------------------------------|-----------------------------------------------------------------------------------------------|

| [00]             | Black level output            | Y = 0x10<br>Cb/Cr = 0x80                                                                      |

| [01]             | Monochrome mode               | Y = data converted to 601 level<br>Cb/Cr = 0x80                                               |

| [10]             | Sliced data output during VBI | Y/Cb/Cr = value corresponding to slice level<br>(Value set at Hi/Low Slice Data Set Register) |

| [11]             | Reserved                      | Reserved                                                                                      |

#### VBIDEC[1:0]-bits: Settings for decode data in the VBI period

Note that, with VBI period settings of Lines 1~9 and 263.5~272.5 in the 525 Line and Lines 623.5~6.5 and 311~318 in the 625 Line, the setting VBIDEC[1:0] will not be entered and the output will be in Black level code.

\*Threshold values (mV) are approximate.

High/Low conversion is performed for either the Cb/Y or the Cr/Y combination. The above figure is an example of the conversion points for Cb/Y.

#### 7.5 Output pin status

For normal operation, the output from the DATA[7:0], VD\_F, DVALID\_F, NSIG, and HD pins can each be fixed at Low via the Output Control Register. Note, however, that the OE, PDN, and RSTN pin states will have priority regardless of these register settings.

#### 7.6 VLOCK mechanism

The AK8853 synchronizes internal operation with the input signal frame structure. If, for example, the frame structure of the input signal comprises 524 lines, the internal operation will have a structure of 524 lines per frame. This mechanism is termed the VLOCK mechanism. If an input signal changes from a structure of 525 lines per frame to one of 524 lines per frame, internal operation will change accordingly, and the VLOCK mechanism will go to UnLock via a pull-in process. In such case, the UnLock status can be confirmed via the control register [VLOCK-bit]. Note that the time required for locking of the VLOCK mechanism upon channel or other input signal switching will be about 4 frames.

| ACTSTA[2:0]-bits | Line and active video start |                          | Approximate delay/advance (ns)  |  |

|------------------|-----------------------------|--------------------------|---------------------------------|--|

| [001]            | 525 Line                    | 124 <sup>th</sup> sample | 74 dolov                        |  |

|                  | 625 Line                    | 134 <sup>th</sup> sample | 74, delay                       |  |

| [010]            | 525 Line                    | 125 <sup>th</sup> sample | 149. dolov                      |  |

| [010]            | 625 Line                    | 135 <sup>th</sup> sample | – 148, delay                    |  |

| [011]            | 525 Line                    | 126 <sup>th</sup> sample | 222, delay                      |  |

| [011]            | 625 Line                    | 136 <sup>th</sup> sample |                                 |  |

| [000]            | 525 Line                    | 123 <sup>th</sup> sample | Default value (normal position) |  |

| [000]            | 625 Line                    | 133 <sup>th</sup> sample |                                 |  |

| [101]            | 525 Line                    | 120 <sup>th</sup> sample | 222, advance                    |  |

|                  | 625 Line                    | 130 <sup>th</sup> sample |                                 |  |

| [110]            | 525 Line                    | 121 <sup>th</sup> sample | – 148, advance                  |  |

|                  | 625 Line                    | 131 <sup>th</sup> sample |                                 |  |

| [111]            | 525 Line                    | 122 <sup>th</sup> sample | 74, advance                     |  |

|                  | 625 Line                    | 132 <sup>th</sup> sample | 74, advance                     |  |

| [100]            | Reserved                    | Reserved                 | -                               |  |

ACTSTA[2:0]-bits: Adjustment of active video start position

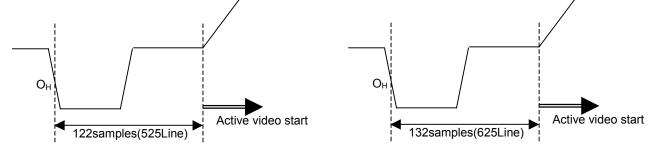

With the default value, the start position is as follows (with ITU-R BT.601 format compliance).

#### 7.7 Auto Gain Control\_AGC

The AGC of the AK8853 measures the size of the input sync signal (i.e., the difference between the sync tip and pedestal levels), and adjusts the PGA value to bring the sync signal level to 286<sup>a</sup> or 300<sup>b</sup> mV. The AGC function amplifies the input signal to the appropriate size and enables input to the AD converter. The AGC function in the AK8853 is adaptive, and thus includes peak AGC as well as sync AGC. Peak AGC is effective for input signals in which the sync signal level is appropriate and only the active video signal is large.

<sup>a</sup> NTSC-M, J; NTSC-4.43; PAL-M <sup>b</sup> PAL-B, D, G, H, I, N; PAL-Nc; PAL-60; SECAM

| AGCT[1:0]-bits Time constant |              | Time constant | Notes                          |  |  |

|------------------------------|--------------|---------------|--------------------------------|--|--|

|                              | [00] Disable |               | AGC OFF, PGA register enabled. |  |  |

|                              | [01]         | Fast          | T= 1Field                      |  |  |

|                              | [10]         | Middle        | T= 7Fields                     |  |  |

|                              | [11]         | Slow          | T= 29Fields                    |  |  |

#### AGCT[1:0]-bits: Settings for AGC time constant

T is the time constant.

Manual setting of the PGA register is possible only if AGC is disabled.

#### AGCC-bit: Settings for AGC non-sensing range

| AGCC[1:0]-bits | Non-sensing range | Notes |

|----------------|-------------------|-------|

| [00]           | ±2LSB             | _     |

| [01]           | ±3LSB             | _     |

| [10]           | ±4LSB             | -     |

| [11]           | None              | _     |

#### AGCFRZ-bit: Settings for freezing AGC function

| AGCFRZ-bit | AGC status | Notes |

|------------|------------|-------|

| [0]        | Non-frozen | -     |

| [1]        | Frozen     | _     |

Note. The gain value at the time of freezing is maintained during the frozen state, and it is then possible to read out the gain value via the PGA1,2 Control Register.

AGCTL-bit: Settings for selection of quick or slow transition between peak and sync AGC

| AGCTL-bit | AGC transition | Notes |

|-----------|----------------|-------|

| [0]       | Quick          | -     |

| [1]       | Slow           | _     |

#### 7.8 Auto Color Control\_ACC

The ACC of the AK8853 measures the level of the input signal color burst, and adjusts the level to  $286^{a}$  or  $300^{b}$  mV, as appropriate. The ACC is not applicable to SECAM. As in AGC, both ACC time constant and ACC freeze settings can be entered.

<sup>a</sup> NTSC-M,J, NTSC-4.43, PAL-M

<sup>b</sup> PAL-B, D, G, H, I, N, PAL-Nc, PAL-60

#### ACCT[1:0]-bits: Settings for ACC time constant

| ACCT[1:0]-bits | Time constant | Notes       |

|----------------|---------------|-------------|

| [00]           | Disable       | ACC OFF     |

| [01]           | Fast          | T= 2Fields  |

| [10]           | Middle        | T= 8Fields  |

| [11]           | Slow          | T= 30Fields |

#### ACCFRZ-bit: Settings for freezing ACC function

| ACCFRZ-bit | ACC status | Notes |

|------------|------------|-------|

| [0]        | Non-frozen | _     |

| [1]        | Frozen     | _     |

Note. The burst-level setting at the time of freezing is maintained during the frozen state.

The ACC and Color saturation functions operate independently. If ACC is enabled, the color saturation adjustment is applied to the signal that has been adjusted to the appropriate level by the ACC.

#### 7.9 Y/C separation

The adaptive two-dimensional Y/C separation of the AK8853 utilizes a correlation detector to select the best-correlated direction from among vertical, horizontal, and diagonal samples, and selects the optimum Y/C separation mode. For NTSC-4.43, PAL-60, and SECAM inputs, the Y/C separation is one-dimensional only, regardless of the setting.

| YCSEP[1:0]-bits | Y/C separation mode | Notes                                                                |

|-----------------|---------------------|----------------------------------------------------------------------|

| [00]            | Adaptive            | Selects [01] or [10] setting, as appropriate                         |

| [01]            | 1-D                 | 1D (BPF)                                                             |

| [10]            | 2-D                 | NTSC-M, J, PAL-M: 3 Line 2-D<br>PAL-B, D, G, H, I, N, Nc: 5 Line 2-D |

| [11]            | Reserved            | _                                                                    |

YCSEP[1:0]-bits: Settings for Y/C separation method

For NTSC-4.43, PAL-60, and SECAM inputs, Y/C separation is 1-D only, regardless of the setting.

#### 7.10 C filter

The bandwidth of the C filter can be set via the register, as follows.

C358FIL[1:0]: Settings for C filter bandwidth, for input signal with 3.58 MHz subcarrier wave

| C358FIL[1:0] -bits | Notes    | Notes                            |

|--------------------|----------|----------------------------------|

| [00]               | Narrow   |                                  |

| [01]               | Medium   | NTSC-M, J, PAL-M, PAL-Nc         |

| [10]               | Wide     | IN I SC-IVI, J, FAL-IVI, FAL-INC |

| [11]               | Reserved |                                  |

C443FIL[1:0]: Settings for C filter bandwidth, for input signal with 4.43 MHz subcarrier wave

| C443FIL[1:0] -bits | Notes    | Notes                                   |  |

|--------------------|----------|-----------------------------------------|--|

| [00]               | Narrow   |                                         |  |

| [01]               | Medium   | PAL-B, D, G, H, I, N, NTSC-4.43, PAL-60 |  |

| [10]               | Wide     | FAL-B, D, G, H, I, N, N13C-4.43, FAL-00 |  |

| [11]               | Reserved |                                         |  |

Note. No bandwidth selection is possible for SECAM input.

#### 7.11 UV filter

The UV bandwidth can be changed by switching between two low pass filter types for the demodulated C signal.

#### UVFILSEL-bit: Settings for UV filter switching

| UVFILSEL -bit | Bandwidth | Notes |

|---------------|-----------|-------|

| [0]           | Wide      |       |

| [1]           | Narrow    |       |

#### 7.12 Digital Pixel Interpolator

The digital pixel interpolator of the AK8853 aligns vertical pixel positions in both frame-lock and fixed-clock operating modes. The pixel interpolator can be set to ON or OFF via the register. With a register setting of AUTO, the pixel interpolator is OFF or ON depending on the clock mode, as follows.

| Line-locked clock mode  | OFF |

|-------------------------|-----|

| Frame-locked clock mode | ON  |

| Fixed-clock mode        | ON  |

INTPOL[1:0]-bits: Settings for pixel interpolator operation

| INTPOL[1:0]-bits | Interpolator operation | Notes                    |

|------------------|------------------------|--------------------------|

| [00]             | Auto                   | Dependent on clock mode. |

| [01]             | ON                     | —                        |

| [10]             | OFF                    |                          |

| [11]             | Reserved               |                          |

#### 7.13 Clock generation

The AK8853 operates in the following three clock modes.

Line-locked clock mode The "line-locked clock" is generated by PLL using the horizontal sync signal within the input signal. If no input signal is present, the AK8853 will switch from this mode to fixed-clock mode.

Frame-locked mode The "frame-locked clock" is generated by PLL using the vertical sync signal within the input signal. If no input signal is present, the AK8853 will switch from this mode to fixed-clock mode.

3. Fixed-clock mode

No PLL control is applied in this mode, which is enabled only when either it is set via the register or no input signal is present. In this mode, data capture cannot be performed in EAV (end active video), and must be performed in SAV (start active video) format. The number of pixels per line is not guaranteed in this mode, but data guarantee is performed in the interval from SAV to EAV.

The AK8853 transition function automatically switches among the above modes and selects the optimum one, and when no input signal is present switches to the fixed-clock mode.

In the line-locked and frame-locked clock modes, the clock is synchronized with the input signal and the output is thus ITU-R BT.656 compliant. It should be noted, however, that ITU-R BT.656-compliant output may not be possible with low-quality input signals.

It should also be noted that in the fixed-clock mode the sample number will be insufficient for ITU-R BT.656 compliance, due to non-synchronization of the input data.

|                                    | CERMODE[1.0]-bits. Settings for selection of clock generation mode |                       |       |  |  |

|------------------------------------|--------------------------------------------------------------------|-----------------------|-------|--|--|

| CLKMODE[1:0]-bits Clock generation |                                                                    | Clock generation mode | Notes |  |  |

|                                    | [00]                                                               | Automatic             | —     |  |  |

|                                    | [01] Line-locked                                                   |                       | —     |  |  |

|                                    | [10]                                                               | Frame-locked          | —     |  |  |

|                                    | [11]                                                               | Fixed-clock           | —     |  |  |

CLKMODE[1:0]-bits: Settings for selection of clock generation mode

#### 7.14 Phase correction

In PAL-B, D, G, H, I, N, Nc, 60, and M decoding, the AK8853 performs phase correction for each line. With this function ON, color averaging is performed for each line. In the adaptive phase correction mode, interline phase correlation is sampled and color averaging is performed for correlated samples.

Interline color averaging is also performed in NTSC-M and J decoding.

No phase correction or color averaging is performed in SECAM decoding.

# DPAL[1:0]-bitsStatusNotes[00]Adaptive phase correction mode—[01]Phase correction ON—[10]Phase correction OFF—[11]Reserved—

#### DPAL[1:0]-bits: Settings for phase correction

#### 7.15 No-signal output

If no input signal is found (as shown by the control bit NOSIG-bit), the output signal is black-level, blue level (blueback), or input-state (sandstorm), depending on the register setting.

#### NSIGMD-bits: Settings for output signals for no input signal

| NSIGMD [1:0]-bits | Output                  | Notes |

|-------------------|-------------------------|-------|

| [00]              | Black-level             | _     |

| [01]              | Blue-level (blueback)   |       |

| [10]              | Input-state (sandstorm) | _     |

| [11]              | Reserved                | —     |

#### 7.16 Output interface

#### 7.16.1 656 interface

#### 7.16.1.1 Line-locked and frame-locked clock modes

In both of these modes, the decoded data output is compliant with ITU-R BT.656, which requires the following sample and line numbers.

Samples per line: 858 (525 line) or 864 (625 line)

Lines per frame: 525 or 625

It may not be possible, however, to meet these requirements if the input signal quality is poor.

In the AK8853, PLL is locked to the input signal and output-stage buffers absorb input signal jitter, but if the jitter is excessive PLL tracking may be impracticable and ITU-R BT.656 compliance may thus be lost.

In such cases, the following processing can be applied via the indicated register settings.

- (a) Line drop/repeat processing

A line drop or line repeat will result in output signals with 524/624 or 526/626 lines per frame, respectively. Line drop/repeat processing may be performed at any line in the frame.

- (b) Pixel drop/repeat processing

A pixel drop or pixel repeat will result in output signals less or more than the required 858/864 samples in the last line of the frameor field, respectively.

Note: In the event of output-stage buffer failure, line drop/repeat processing will be performed even if the register setting is for pixel drop/repeat processing.

| ERRHND-bits | Processing mode                    | Notes   |

|-------------|------------------------------------|---------|

| [00]        | Line Drop / Line Repeat            | Default |

| [01]        | Pixel Drop / Pixel Repeat by Field | _       |

| [10]        | Pixel Drop / Pixel Repeat by Frame | —       |

| [11]        | Reserved                           |         |

#### ERRHND-bits: Settings for line and pixel drop/repeat processing

#### 7.16.1.2 Fixed-clock mode

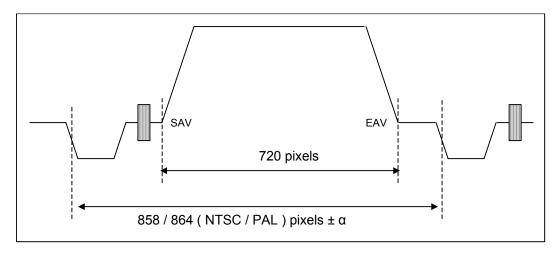

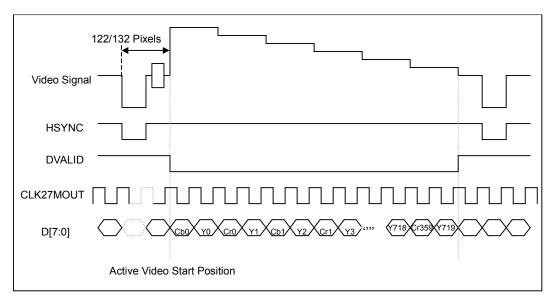

In fixed-clock mode, operation is at an internally generated 27 MHz clock, from a 24.576 MHz input clock. The output signal is therefore not synchronized with the input signal, and thus not ITU- BT.656 compliant. Data is output in SAV format. As shown in the following figure, EAV is guaranteed for 720 pixels from SAV, but the sample number from EAV to SAV is not.

#### 7.16.2 DVALID and timing signal interface

For connection with devices having no ITU-R.BT.656 interface, the AK8853 DVALID signal output identifies the active video interval by remaining low throughout that period, as shown in the following figure.

In fixed-clock mode, the internal clock is not synchronized with the output signal, but a space of 122/132 (NTSC/PAL) pixels is guaranteed between the horizontal sync signal and the start of the active video interval.

# AKM

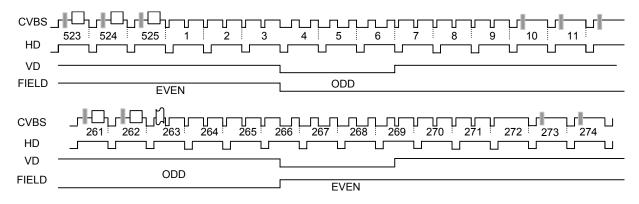

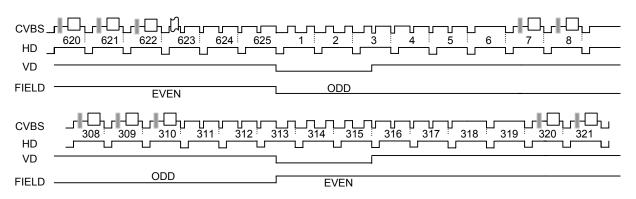

The AK8853 outputs the following signals from the HD, VD\_F, and DVALID\_F pins, and the indicated VD\_F and DVALID\_F output signals can also be selected via the register settings shown below.

| Timing signal output pin | 525-line                                   |                                  | 625-line                                |

|--------------------------|--------------------------------------------|----------------------------------|-----------------------------------------|

| HD                       | Low for 4.7 µs at 15.734 kHz interval      |                                  | Low for 4.7 µs at 15.625 kHz interval   |

| VD_F<br>DVALID_F         | VD Low during lines 4~6<br>and 266.5~269.5 |                                  | Low during lines 1~3.5<br>and 313.5~315 |

|                          | FIELD                                      | ODD-Field: Low; EVEN-Field: High |                                         |

|                          | DVALID                                     | Active-Low                       |                                         |

VFDSEL[1:0]-bits: Settings for VD/FIELD/DVALID selection

|                  | P            | in output     |

|------------------|--------------|---------------|

| VFDSEL[1:0]-bits | VD_F pin     | DVALID_F pin  |

| [00]             | VD signal    | DVALID signal |

| [01]             | VD signal    | Field signal  |

| [10]             | Field signal | DVALID signal |

| [11]             | Reserved     | Reserved      |

Output timing with 525-line input

Output timing with 625-line input

The output signal polarities of the DTCLK, HD, VD\_F and DVALID\_F pins can be reversed via "Output Control Register" and "Control 0 Register" settings.

#### 7.17 Automatic setup processing

In auto detection mode, the AK8853 can perform automatic setup processing in accordance with the detected signal. The automatic setup selection is made via the STUPATOFF-bit register, as shown in the table below.

Setup processing of the signal to be decoded consists of the following.

Luminance signal: Y=(Y-7.5)/0.925 Color signal: U=U/0.925, V=V/0.925

Automatic setup processing (AK8853 in auto detection mode)

|                                   | Register setting |                                               | Detected signal setup |

|-----------------------------------|------------------|-----------------------------------------------|-----------------------|

| Detected signal                   | Setup-bit        | STUPATOFF-bit<br>(Automatic setup processing) | processing status     |

|                                   | [0]              | [0]                                           | Disabled              |

| NTSC-M, J<br>PAL-B, D, G, H, I, N | [0]              | [1]                                           | Disabled              |

| PAL-Nc, 60<br>SECAM               | [1]              | [0]                                           | Enabled               |

|                                   |                  | [1]                                           | Enabled               |

| PAL-M<br>NTSC-4.43                | [0]<br>PAL-M     | [0]                                           | Enabled               |

|                                   |                  | [1]                                           | Disabled              |

|                                   | SC-4.43 [1] —    | [0]                                           | Enabled               |

|                                   |                  | [1]                                           | Enabled               |

In the auto detection mode, the setup processing status will be determined by the register setting on the basis of the detected signal category, with no detection as to the presence or absence of input signal setup.

#### 7.18 PGA (programmable gain amp)

The PGA, located in the input stage of the AK8853, can be set in a gain range of -6~6 dB in gain steps of 0.1 dB.

PGA[7:0]-bits: Sets the PGA value.

This register can read the AGC setting value.

If AGC is enabled, the PGA[7:0]-bits setting value has no effect, and the PGA setting can be manually entered in the register only if AGC is disabled.

Signal input to the AK8853 should be made with the input level attenuated approximately 39% (-8.19 dB) by resistance splitting.

#### 7.19 Sync separation, sync detection, and black-level fine tuning

The AK8853 performs sync separation and sync detection on the digitized input signal, uses the detected sync signal as the timing reference for the decoding process, and calculates the phase error from the separated sync signal and applies it to control of the sampling clock.

Black-level tuning can be performed in the sync separation block. The black-level fine-tuning band, which is 10 bits wide before REC 601 conversion, can be adjusted -8~+7 LSB in 1-LSB steps, with one step resulting in a change of about 0.4 LSB in the output code.

| BKLVL[3:0]-bits | Code adjustment of black level | Approx. change in 601 level (LSB) |

|-----------------|--------------------------------|-----------------------------------|

| [0001]          | +1                             | +0.4                              |

| [0010]          | +2                             | +0.8                              |

| [0011]          | +3                             | +1.2                              |

| [0100]          | +4                             | +1.6                              |

| [0101]          | +5                             | +2.0                              |

| [0110]          | +6                             | +2.4                              |

| [0111]          | +7                             | +2.8                              |

| [0000]          | Default                        | None                              |

| [1000]          | -8                             | -3.2                              |

| [1001]          | -7                             | -2.8                              |

| [1010]          | -6                             | -2.4                              |

| [1011]          | -5                             | -2.0                              |

| [1100]          | -4                             | -1.6                              |

| [1101]          | -3                             | -1.2                              |

| [1110]          | -2                             | -0.8                              |

| [1111]          | -1                             | -0.4                              |

BKLVL[3:0]-bits: Settings for black-level fine tuning

The black level is adjusted upward or downward by the value of the setting, which must be in 2's-complement form. Black-level adjustment is also enabled during the vertical blanking interval.

#### 7.20 Digital pedestal clamp

The digitally converted input signal is clamped in the digital signal processing block. The internal clamp position depends on the input signal type (either 286 mV sync or 300 mV sync), but pedestal position is output as code 16 for both types. The digital pedestal clamp function can adjust the time constant and set the coring level.

DPCT[1:0]-bits: Settings for digital pedestal clamp time constant

|   | DPCT[1:0]-bits | Transition time constant | Notes                      |

|---|----------------|--------------------------|----------------------------|

| ſ | [00]           | Fast                     | —                          |

| ſ | [01]           | Middle                   | —                          |

| ſ | [10]           | Slow                     | —                          |

| ſ | [11]           | Disable                  | Digital pedestal clamp OFF |

DPCC[1:0]-bits: Settings for digital clamp pedestal coring level

| DPCC[1:0]-bits | Transition time constant (bit) | Notes |

|----------------|--------------------------------|-------|

| [00]           | ±1                             |       |

| [01]           | ±2                             | _     |

| [10]           | ±3                             |       |

| [11]           | Non-coring                     | _     |

#### 7.21 Color killer

The chroma signal quality of the input signal is determined by comparison of its color burst level against the threshold setting in the color killer control register. If the level is below the threshold, the color killer is activated, resulting in processing of the input as a monochrome signal and thus with CbCr data fixed at 0x80. Depending on the register setting, the color killer may also be activated by failure of the color decode PLL lock.

COLKILL-bit: Settings for color killer ON and OFF

| COLKILL-bit |         | Notes |

|-------------|---------|-------|

| [0]         | Enable  | —     |

| [1]         | Disable | —     |

CKLVL[3:0]-bits: For threshold setting; default setting [1000] = -23dB.

CKSCM[1:0]-bits: Used for threshold setting with SECAM input; expands 2-bit for CKLVL[3:0]-bit

CKILSEL: Settings for color killer activation

| CKILSEL-bit | Condition for activation                                                                       | Notes |

|-------------|------------------------------------------------------------------------------------------------|-------|