# SANYO Semiconductors DATA SHEET

# **CMOSIC \_C823410-10R** — Ultra-Low Power Consumption 7.0mW Large-Scale System LSI, GokLow, for IC Recorders

### **Overview**

The LC823410-10R is a system IC that uses ultra-low power consumption technology to realize long-time playback and recording, and has various IC recorder functions. The IC is optimal for use in IC recorder applications.

### Features

- ARM7TDMI-S<sup>TM \*1</sup>, AMBA<sup>®</sup> (AHB/APB) system

- -On-chip SRAM (160kbytes)

- -On-chip ROM (256kbytes)

- -DMA controller (2 channels)

- -Interrupt controller (external 6 channels)

- -SIO (2 channels), UART (3 channels, of which 2 channels run on the 12MHz oscillator XT1.)

Continued on next page.

ARM ARM \*1: ARM logo, ARM Powered logo and, ARM7TDMI are registered trademark of ARM Limited.

Supply of this product does not convey license nor imply any right to distribute content created with this product in revenue-generating broadcast systems (terrestrial, satellite, cable and/or other distribution channels), streaming applications (via Internet, intranets and/or networks), other content distribution systems (pay-audio or audio-on-demand applications and the like) or on physical media (compact discs, digital versatile discs, semiconductor chips, hard drives, memory cards and the like).

Supply of this product does not convey license under the relevant intellectual property of Thomson and/or Fraunhofer Gesellschaft nor imply any right to use this product in any finished end user or ready-to-use final product. An independent license for such use is required. For details, please visit http://mp3licensing.com/.

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications of our customer who is considering such use and/or outside the scope of our intended standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

SANYO Semiconductor Co., Ltd. http://semicon.sanyo.com/en/network

Continued from preceding page.

- -I<sup>2</sup>C (1 channel, single master, full speed mode/standard mode support)

- -GPIO (multiplexed port I/O pin, 32 channels)

- -Plain timer, multiple timer (2 channels, runs on the 12MHz oscillator XT1)

- -10-bit A/D converter (4 channels)

- -NAND flash memory I/F (multi-level cell NAND)

- 4-bit correctable ECC, automatic correction of error bits

- -SD card I/F (CPRM not supported) [optional]

- SD card clock can be generated through AHB clock.

- -Memory stick I/F [optional]

- -USB2.0 device I/F with PHY

- Communication operation possible even when the AHB runs at a low clock rate. Insertion/extraction detection possible even when the PHY clock is stopped.

- -RTC (realtime clock)

- Operation at a voltage independent from the internal core operating voltage, and RTC only power on operation possible.

- -JTAG ICE

- MP3<sup>\*2</sup> hard-wired encoder/decoder

- -MPEG1, MPEG2, MPEG2.5

- (Fs=8kHz to 48kHz, 8kbps to 320kbps)

- High quality sound technologies & functions (<u>underlined</u> functions support 96kHz sampling)

- -SANYO "AViSS" surround circuit

- -YY filter high frequency compensation circuit (2 modes, LP2: High bit rate and LP4: Low bit rate)

- -Sampling rate converter. Convertible up to 96kHz (max.) within the range of 0.5 to 64 times

- -6-band equalizer. Equalizer characteristics can be adjusted by setting the coefficient.

- -Digital volume and mute functions (except the recording system). Both dB and linear rate of change can be designated.

- -Level meter (except the recording system)

- -Audio timer function. LR clock count and interrupt generation function

- On-chip 16-bit PCM input/output interface. Master/slave mode, I<sup>2</sup>S support

- 12MHz oscillator XT1 + PLL dedicated for audio enable audio clock generation Also supports audio operations using 16.9344MHz oscillator XT2 (optional).

- Supply voltages (typical)

- -LOGIC, USB PHY1, XTAL, PLL1, RTC = 1.1V (when no USB devices connected) or 1.5V (when USB devices connected)

- -I/O, ADC, USB PHY2, PLL2 = 2.8V (when no USB devices connected) or 3.3V (when USB devices connected)

\*2: MPEG Layer-3 audio coding technology licensed from Fraunhofer IIS and Thomson.

### Specifications

Absolute Maximum Ratings at  $*V_{SS}* = 0V$

| Parameter                     | Symbol                                                                                                           | Conditions     | Ratings                                  | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------|------|

| Maximum supply voltage        | V <sub>DD</sub> 1<br>V <sub>DD</sub> RTC<br>V <sub>DD</sub> XT<br>AV <sub>DD</sub> PHY1<br>AV <sub>DD</sub> PLL1 |                | -0.3 to 1.8                              | V    |

|                               | V <sub>DD</sub> 2<br>V <sub>DD</sub> 3<br>AV <sub>DD</sub> ADC<br>AV <sub>DD</sub> PHY2<br>AV <sub>DD</sub> PLL2 |                | -0.3 to 3.96                             | V    |

| Input voltage                 | VI                                                                                                               |                | -0.3 to *V <sub>DD</sub> *+0.3 (max3.96) | V    |

|                               | VIUSB                                                                                                            | DP and DM pins | -0.3 to 5.25                             | V    |

| Operating ambient temperature | Topr                                                                                                             |                | -30 to +70                               | °C   |

| Storage ambient temperature   | Tstg                                                                                                             |                | -55 to 125                               | °C   |

### Allowable Operating Range at Ta = -30 to $+70^{\circ}C$

| Deremeter      | Symphol               | Conditions        | Low '    | Voltage Oper | ation              | High | Voltage Oper | ation              | Unit |

|----------------|-----------------------|-------------------|----------|--------------|--------------------|------|--------------|--------------------|------|

| Parameter      | Symbol                | Symbol Conditions |          | typ          | max                | min  | typ          | max                | Unit |

| Supply voltage | V <sub>DD</sub> 1     |                   | 1.05     | 1.1          | 1.2                | 1.35 | 1.5          | 1.65               | V    |

|                | V <sub>DD</sub> XT    |                   | 1.05     | 1.1          | 1.2                | 1.35 | 1.5          | 1.65               | V    |

|                | AV <sub>DD</sub> PLL1 |                   | 1.05     | 1.1          | 1.2                | 1.35 | 1.5          | 1.65               | V    |

|                | AV <sub>DD</sub> PLL2 |                   | 2.7      | 2.8          | 3.3                | 2.7  | 2.8          | 3.6                | V    |

|                | V <sub>DD</sub> RTC   |                   | 0.9      | 1.1          | 1.65               | 0.9  | 1.5          | 1.65               | V    |

|                | V <sub>DD</sub> 2     |                   | 2.7      | 2.8          | 3.3                | 2.7  | 2.8          | 3.6                | V    |

|                | V <sub>DD</sub> 3     |                   | 2.7      | 2.8          | 3.3                | 2.7  | 2.8          | 3.6                | V    |

|                |                       |                   | 1.7      | 1.8          | 1.95               | 1.7  | 1.8          | 1.95               | V    |

|                | AV <sub>DD</sub> ADC  |                   | 2.7      | 2.8          | 3.3                | 2.7  | 2.8          | 3.6                | V    |

|                | AV <sub>DD</sub> PHY1 |                   | 1.05(*1) | 1.1          | 1.2                | 1.35 | 1.5          | 1.65               | V    |

|                | AV <sub>DD</sub> PHY2 |                   | 2.7(*1)  | 2.8          | 3.3                | 3.0  | 3.3          | 3.6                | V    |

| Input voltage  | VIN                   |                   | 0        |              | *V <sub>DD</sub> * | 0    |              | *V <sub>DD</sub> * | V    |

(\*1) In the low-voltage operation state, although transition from this state to the high-voltage operation state and operation after the transition are guaranteed, all operations are not guaranteed in the low-voltage state.

(\*2) The relations below are assumed in all operation states.

• V<sub>DD</sub>1=V<sub>DD</sub>XT=AV<sub>DD</sub>PLL1=AV<sub>DD</sub>PHY1

- AVDDPHY2>=AVDDADC

- $V_{DD}2 > = AV_{DD}PLL2$

- V<sub>DD</sub>2>=V<sub>DD</sub>3

- where,

- $V_{DD}$ 1,  $V_{DD}$ XT, and AV<sub>DD</sub>HY1 have the same electrical potential because they are connected within the IC.

- AVDDPLL1>=VDD1

- Besides the above two points, voltage differences up to 0.1V are considered to be equal. Also, during RTC-only operation,

The above  $V_{DD}RTC$  voltage can be applied at BACKUPB = Low input and application of  $V_{DD}^* = 0V$  except for  $V_{DD}RTC$ .

(\*3) Low-voltage operation: This is an operation state that enables low power consumption during music playback and other operations.

High-voltage operation: This is an operation state on the assumption that USB is used.

| Descention         | O mark al | Function                                        | Low | Voltage Ope | ration | High  | Voltage Ope | ration     | 1.1  |

|--------------------|-----------|-------------------------------------------------|-----|-------------|--------|-------|-------------|------------|------|

| Parameter          | Symbol    | Function                                        | min | typ         | max    | min   | typ         | max        | Unit |

| Input oscillation  | Fxin1     | ARM & Peripherals                               |     | 12          |        | 12MHz | ±100p-pm (ι | ising USB) | MHz  |

| frequency          | FxinRTC   | RTC                                             |     | 32.768      |        |       | 32.768      |            | kHz  |

|                    | Fxin2     | AUDIO                                           |     | 16.9344     |        |       | 16.9344     |            | MHz  |

|                    | Frc       | RC                                              | 0.4 | 1           | 2      | 0.4   | 1           | 2          | MHz  |

| Internal operating | Fahb      | ARM AHB                                         | 0   |             | 30     | 0     |             | 60         | MHz  |

| frequency          | Fapb      | ARM APB                                         | 0   |             | 30     | 0     |             | 60         | MHz  |

|                    | Faud      | AUDIO                                           | 0   | 16.9344     | 36.864 | 0     | 16.9344     | 36.864     | MHz  |

| SD I/F             | Fsdclk    | Normal                                          |     |             | 19     |       |             | 24         | MHz  |

| clock frequency    |           | High speed<br>(V <sub>DD</sub> 3>=2.7V SDDRV=1) |     |             | 25     |       |             | 40         | MHz  |

| MS I/F             | Fsclk     | Parallel                                        |     |             | 30     |       |             | 30         | MHz  |

| clock frequency    |           | Serial                                          |     |             | 20     |       |             | 20         | MHz  |

# **DC characteristic** at Ta = -30 to +70°C, $V_{DD}2 = 2.7$ to 3.6V, $V_{DD}RTC = 0.9$ to 1.65V, $V_{DD}3=1.7$ to 1.95V, 2.7 to 3.6V

| Parameter                 | Cumbal          | Pins             | Conditions              |                         | Ratings |                         | Unit |

|---------------------------|-----------------|------------------|-------------------------|-------------------------|---------|-------------------------|------|

| Parameter                 | Symbol          | Filis Conditions |                         | min                     | typ     | max                     | Unit |

| Input high level voltage  | VIH             | (1)              |                         | 0.7×V <sub>DD</sub> 2   |         |                         | V    |

|                           |                 | (2)              | Schmitt                 | 0.75×V <sub>DD</sub> 2  |         |                         | V    |

|                           |                 | (3)              |                         | 0.7×V <sub>DD</sub> RTC |         |                         | V    |

| Input low level voltage   | VIL             | (1)              |                         |                         |         | 0.3×V <sub>DD</sub> 2   | V    |

|                           |                 | (2)              | Schmitt                 |                         |         | 0.25×V <sub>DD</sub> 2  | V    |

|                           |                 | (3)              |                         |                         |         | 0.2×V <sub>DD</sub> RTC | V    |

| Output high level voltage | VOH             | (4)              | I <sub>OH</sub> =-2mA   | V <sub>DD</sub> 2-0.4   |         |                         | V    |

|                           |                 | (5)              | I <sub>OH</sub> =-4mA   | V <sub>DD</sub> 3-0.34  |         |                         | V    |

|                           |                 | (6)              | I <sub>OH</sub> =-0.3mA | V <sub>DD</sub> RTC-0.3 |         |                         | V    |

| Output low level voltage  | V <sub>OL</sub> | (4)              | I <sub>OL</sub> =2mA    |                         |         | 0.4                     | V    |

|                           |                 | (5)              | I <sub>OL</sub> =4mA    |                         |         | 0.34                    | V    |

|                           |                 | (6)              | I <sub>OL</sub> =0.3mA  |                         |         | 0.3                     | V    |

| Output leakage current    | I <sub>OZ</sub> | (7)              | Hi-Z output             | -10                     |         | 10                      | μA   |

| Pull-up resistor          | Rup             | (8)              |                         | 50                      | 100     | 150                     | kΩ   |

| Pull-up resistor          | Rup             | (9)              |                         | 30                      | 45      | 80                      | kΩ   |

| Pull-down resistor        | Rdn             | (10)             |                         | 40                      | 70      | 160                     | kΩ   |

| Pull-down resistor        | Rdn             | (11)             |                         | 20                      | 50      | 90                      | kΩ   |

(1) FD7-0, SDCMD, SDAT3-0, BCK, LRCK, MCLK, SCL, SDA, TIOCA1-0, SDI1, RXD2-0, SDO0, TXD2-0, XFCE1-0, PHI, TCK, TDI, TMS, SDI0, DIN, SDCD, SDWP

(2) TEST6-1, NTRST, NRES, EXTINT6-0, EXTFIQ, SCK1-0, XFBSY

(3) BACKUPB, VDET

(4) SCK1-0, FD7-0, EXD15-0, BCK, LRCK, MCLK, SCL, SDA, TIOCA1-0, SDI1, SDI0, RXD2-0, TXD2-0, XFCE1-0, PHI, EXTFIQ, EXTINT4-0, DOUT, RTCK, TDO, XALE, XCLE, XFRE, XFWE, XFWP

(5) SDCLK, SDCMD, SDAT3-0

(6) RTCINT

(7) SCK1-0, FD7-0, SDCMD, SDAT4-1, BCK, LRCK, MCLK, SCL, SDA, TIOCA1-0, SDI1, RXD2-0, SDO1-0, TXD2-0, XFCE1-0, PHI, EXTFIQ, EXTINT4-0, RTCK, XALE, XCLE, XFRE, XFWE, XFWP, RTCINT

- (8) EXTFIQ, SCK1, SDO1, TXD2-0, RXD2-0, TIOCA1-0, SDI1, EXTINT4-0, XFCE1-0, SCL, SDA, LRCK, MCLK, PHI, SCK0, SDI0, SDO0, TCK, TDI, TMS, NTRST ,XFWE, XFRE, XALE, XCLE, XFWP

- (9) SDCMD, SDAT3-0, SDCD

- (10) SDAT3-0

- (11) DIN, FD7-0

(Caution)

The following pins are not included in DC characteristics.

RREF, DM, DP, VCNT1, VCNT2, AN3-0, XIN1, XIN2, XIN32K, XOUT1, XOUT2, XOUT32K

### **PLL1 Characteristics** at Ta = -30 to $+70^{\circ}C$

| Parameter                            | Sumbal | Conditions | AV <sub>D</sub> | DPLL1=1.05 | to 1.2V               | AV <sub>D</sub> | to 1.65V | Unit                  |      |

|--------------------------------------|--------|------------|-----------------|------------|-----------------------|-----------------|----------|-----------------------|------|

| Parameter                            | Symbol | Conditions | min             | typ        | max                   | min             | typ      | max                   | Unit |

| VCO voltage                          | VCNT1  |            | 0               |            | AV <sub>DD</sub> PLL1 | 0               |          | AV <sub>DD</sub> PLL1 | V    |

| VCO maximum oscillation<br>frequency | Fmax   |            | 90              |            |                       | 180             |          |                       | MHz  |

| VCO minimum oscillation<br>frequency | Fmin   |            |                 |            | 60                    |                 |          | 60                    | MHz  |

| Phase comparison<br>frequency        | Fref   |            |                 |            | 30                    |                 |          | 30                    | MHz  |

| PLL lock time                        | Tlock  |            |                 | 5          | 10                    |                 | 5        | 10                    | ms   |

#### **PLL2 Characteristics** at Ta = -30 to +70°C, $AV_{DD}PLL2 = 2.7$ to 3.6V

| Deremeter                         | Sumbol | Conditions |     |     | Unit                  |      |

|-----------------------------------|--------|------------|-----|-----|-----------------------|------|

| Parameter                         | Symbol | Conditions | min | typ | max                   | Unit |

| VCO voltage                       | VCNT2  |            | 0   |     | AV <sub>DD</sub> PLL2 | V    |

| VCO maximum oscillation frequency | Fmax   |            | 40  |     |                       | MHz  |

| VCO minimum oscillation frequency | Fmin   |            |     |     | 15 (*1)               | MHz  |

| Phase comparison frequency        | Fref   |            |     |     | 17                    | MHz  |

| PLL lock time                     | Tlock  |            |     | 10  | 15                    | ms   |

(\*1) When a clock with a frequency lower than 15MHz is required, for example 12.288MHz (= 32kHz \* 384, audio circuit operation clock at a sampling frequency of 32kHz), this is generated by frequency dividing the clock by 2 as follows.

12.288MHz = 24.576MHz/2

#### **10-bit AD Converter Characteristics** at $Ta = 25^{\circ}C$ , $AV_{DD}ADC = 3.3V$ , $AV_{SS}ADC = 0V$

|                                                                  | Oursels al | Oraclitican         |           | Ratings |           | Unit | Pin                  |  |

|------------------------------------------------------------------|------------|---------------------|-----------|---------|-----------|------|----------------------|--|

| Parameter                                                        | Symbol     | Conditions          | min       | typ     | max       | Unit | Pin                  |  |

| ADC power supply                                                 | VAVRH      |                     | 2.7       |         | 3.6       | V    | AV <sub>DD</sub> ADC |  |

| ADC ground voltage                                               | VAVRL      |                     | 0         |         |           | V    | AV <sub>SS</sub> ADC |  |

| Analog input voltage                                             | VAN        |                     | VAVRL     |         | VAVRH     | V    | AN3-AN0              |  |

| ADC resolution                                                   | Ν          |                     |           |         | 10        | Bit  | AN3-AN0              |  |

| ADC operation clock                                              | FC         |                     |           |         | 16.5      | MHz  |                      |  |

| ADC conversion frequency                                         | Fs         |                     |           |         | 1.04      | MHz  |                      |  |

| ADC sample hold time                                             | Twr        |                     | 120       |         |           | ns   |                      |  |

| Differential linearity error                                     | FDIF       | NEFFECT=10          |           |         | ±1.5      | LSB  | AN3-AN0              |  |

| Linearity error                                                  | FLN        | NEFFECT=10          |           |         | ±4.0      | LSB  | AN3-AN0              |  |

| Zero-scale offset voltage<br>(Transit voltage from 0 to 1)       | Vtz        |                     | VAVRL-0.1 | VAVRL   | VAVRL+0.1 | V    | AN3-AN0              |  |

| Full-scale offset voltage<br>(Transit voltage from 1022 to 1023) | Vtf        |                     | VAVRH-0.1 | VAVRH   | VAVRH+0.1 | V    | AN3-AN0              |  |

| Ladder stabilization time (*1)                                   | Tstr       | After STBY released | 1         |         |           | μs   |                      |  |

| Reference resistor (*1)                                          | Rr         |                     |           | 770     |           | Ω    |                      |  |

| Power dissipation (*1)                                           | Pd         |                     |           | 15      |           | mW   |                      |  |

(\*1) All the characteristics are design values.

# USB Interface Characteristics at Ta = -30 to +70°C, $V_{DD}1=1.35$ to 1.65V, $AV_{DD}PHY1=1.35$ to 1.65V, $AV_{DD}PHY2=3.0$ to 3.6V

|                                                                      | AvDD               | PHY2=3.0 to 3.6V                                      | 1     |         | -     |      |

|----------------------------------------------------------------------|--------------------|-------------------------------------------------------|-------|---------|-------|------|

| Parameter                                                            | Symbol             | Conditions                                            |       | Ratings |       | Unit |

| Falamelei                                                            | Symbol             | Conditions                                            | min   | typ     | max   | Unit |

| Output pin impedance                                                 | Z <sub>HSDRV</sub> | Includes R <sub>S</sub> resistor                      | 40.5  |         | 49.5  | Ω    |

| Bus pull-up resistor on upstream<br>forcing port                     | R <sub>PU1</sub>   | FS idle                                               | 0.900 |         | 1.575 | kΩ   |

| Bus pull-up resistor on upstream<br>forcing port                     | R <sub>PU2</sub>   | FS receiving or transmitting                          | 1.425 |         | 3.090 | kΩ   |

| Termination voltage for upstream<br>forcing port pullup (full-speed) | VTERM              |                                                       | 3.15  |         | 3.45  | V    |

| Input levels for full-speed:                                         |                    |                                                       |       |         |       |      |

| High-level input voltage (drive)                                     | VIH                |                                                       | 2.0   |         |       | V    |

| High-level input voltage (floating)                                  | VIHZ               |                                                       | 2.7   |         | 3.6   | V    |

| Low-level input voltage                                              | VIL                |                                                       |       |         | 0.8   | V    |

| Differential input sensitivity                                       | V <sub>DI</sub>    | (D+)-(D-)                                             | 0.2   |         |       | V    |

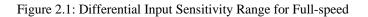

| Differential common mode range                                       | V <sub>CM</sub>    | Includes V <sub>DI</sub> range<br>Refer to figure 2.1 | 0.8   |         | 2.5   | V    |

| Output levels for full-speed:                                        | •                  | -                                                     |       |         |       |      |

| High-level output voltage                                            | VOH                | R <sub>L</sub> of 14.25k $\Omega$ to V <sub>SS</sub>  | 2.8   |         | 3.6   | V    |

| Low-level output voltage                                             | VOL                | $R_L$ of 1.425k $\Omega$ to 3.6V                      | 0.0   |         | 0.3   | V    |

| SE1                                                                  | VOSE1              |                                                       | 0.8   |         |       | V    |

| Output signal crossover point voltage                                | VCRS               | Refer to figure 2.1                                   | 1.3   |         | 2.0   | V    |

| Input levels for high-speed:                                         | 1                  | •                                                     | т.    |         |       |      |

| High-speed squelch detection<br>threshold (differential signal)      | VHSSQ              |                                                       | 100   |         | 150   | mV   |

| High-speed data signaling common mode voltage range                  | V <sub>HSCM</sub>  |                                                       | -50   |         | +500  | mV   |

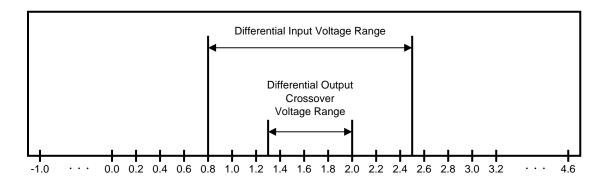

| High-speed differential input signaling level                        | Refer to figu      | ire 2.2                                               |       |         |       |      |

| Output levels for high-speed:                                        |                    |                                                       |       |         |       |      |

| High-speed idle state                                                | VHSOI              |                                                       | -10.0 |         | +10   | mV   |

| High-speed data signaling high                                       | VHSOH              |                                                       | 360   |         | 440   | mV   |

| High-speed data signaling low                                        | VHSOL              |                                                       | -10.0 |         | +10   | mV   |

| Chirp J level (different signal)                                     | VCHIRPJ            |                                                       | 700   |         | 1100  | mV   |

| Chirp K level (different signal)                                     | VCHIRPK            |                                                       | -900  |         | -500  | mV   |

| Time to active-state:                                                |                    |                                                       |       |         |       |      |

| Time from idle (standby/ suspend)<br>state to active state (*)       | T <sub>ACT</sub>   |                                                       |       |         | 1     | ms   |

States identified by an asterisk (\*)

• Idle (standby/suspend) state: Either one of the following 4 states:

- Either one of AV<sub>DD</sub>PHY1 and AV<sub>DD</sub>PHY2 is lower than the guaranteed operating voltage.

- (USB register) DeviceControl: SuspendSts=Susp3endSet=1 (USBPHY suspended state)

- (USB register) DeviceControl: RstPhy=1 (USBPHY reset state)

- (SYSCON register) USBCTL: SHSTBY=1 (USBPHY standby state)

For details on the registers, see the LC823410-09C-E User's Manual (Expansion Module).

• Active-state: Any state in which the IC is not in any of the Idle (standby/suspend) states.

Figure 2.2: Differential Input Sensitivity Range for High-speed

## LC823410-10R

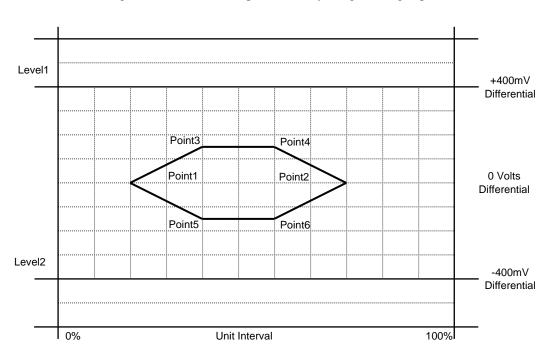

### AC Characteristics: Reset at Ta = -30 to $+70^{\circ}C$ , $V_{DD}1 = 1.05$ to 1.65V, $V_{DD}2 = 2.7$ to 3.6V

| Deservator        | Querra ha a l                  | O an alitica a                                                                                    |     | Ratings |     | l la it |  |

|-------------------|--------------------------------|---------------------------------------------------------------------------------------------------|-----|---------|-----|---------|--|

| Parameter         | Symbol                         | Conditions                                                                                        | min | typ     | max | Unit    |  |

| Reset active time | <sup>t</sup> RESW <sup>1</sup> | Time after both of $V_{DD}$ 1 and $V_{DD}$ 2 reached within the allowable operation voltage range | 10  |         |     | μs      |  |

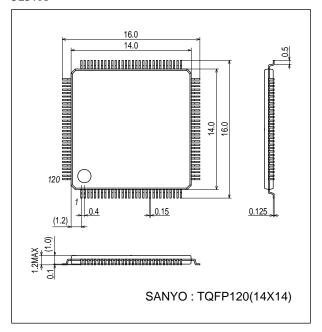

## Package Dimensions

unit : mm (typ) 3257A

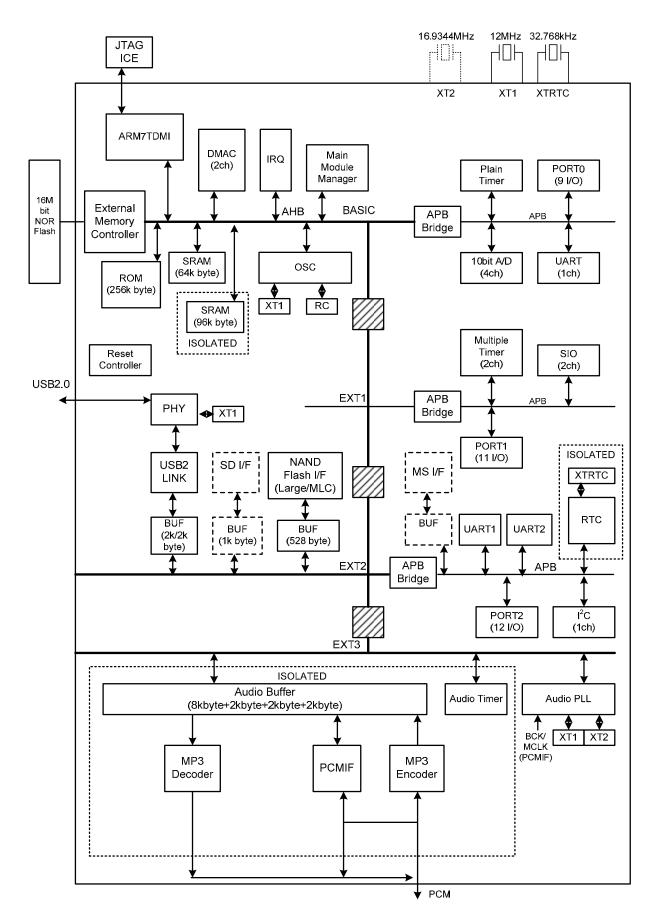

### **Block Diagram**

## **Pin Assignments**

|   | I/O                |      | Pin Ch                    | aracteristics |                            |

|---|--------------------|------|---------------------------|---------------|----------------------------|

| Ι | Input pin          | 3IC  | 3.3V CMOS input           | 1IC           | 1.5V CMOS input            |

| 0 | Output pin         | 3IS  | 3.3V Schmitt input        | 1T3           | 1.5V 0.3mA tristate output |

| В | Bi-directional pin | 3ICU | 3.3V CMOS input pullup    | х             | Oscillation amplifier      |

| Р | Power supply pin   | 3ICD | 3.3V CMOS input pulldown  | ЗA            | 3.3V analog                |

|   |                    | 3ISU | 3.3V Schmitt input pullup | 1A            | 1.5V analog                |

|   |                    | 302  | 3.3V 2mA output           |               |                            |

|   |                    | 3T2  | 3.3V 2mA tristate output  |               |                            |

|   |                    | 306  | 3.3V 6mA output           |               |                            |

|   |                    | 3T6  | 3.3V 6mA tristate output  |               |                            |

| No. | Name              | I/O | Characteristic | Function                                            |

|-----|-------------------|-----|----------------|-----------------------------------------------------|

| 1   | TEST3             | I   | 3IS            | Test pin (normally tied to low)                     |

| 2   | TEST4             | I   | 3IS            | Test pin (normally tied to low)                     |

| 3   | TEST5             | I   | 3IS            | Test pin (normally tied to low)                     |

| 4   | TEST6             | I   | 3IS            | Test pin (normally tied to low)                     |

| 5   | ТСК               | I   | 3ICU           | JTAG test clock                                     |

| 6   | RTCK              | 0   | 302            | JTAG test returned clock                            |

| 7   | NTRST             | I   | 3ISU           | JTAG test reset                                     |

| 8   | TDI               | I   | 3ICU           | JTAG test data input                                |

| 9   | TMS               | I   | 3ICU           | JTAG test mode select                               |

| 10  | TDO               | 0   | 302            | JTAG test data output                               |

| 11  | NRES              | I   | 3IS            | Reset input                                         |

| 12  | PHI(P11)          | В   | 3ICU/3T2       | AHB bus clock output/32.768kHz clock output/GPIO    |

| 13  | EXTFIQ(P2F)       | В   | 3ISU/3T2       | External FIQ interrupt/GPIO                         |

| 14  | SCK0(P08)         | В   | 3ISU/3T2       | Serial I/F 0 clock/GPIO                             |

| 15  | SDO0(P09)         | В   | 3ICU/3T2       | Serial I/F 0 output data/GPIO                       |

| 16  | SDI0(P0A)         | В   | 3ICU/3T2       | Serial I/F 0 input data/GPIO                        |

| 17  | SCK1(P14)         | В   | 3ISU/3T2       | Serial I/F 1 clock/GPIO                             |

| 18  | SDO1(P15)         | В   | 3ICU/3T2       | Serial I/F 1 output data/GPIO                       |

| 19  | SDI1(P16)         | В   | 3ICU/3T2       | Serial I/F 1 input data/GPIO                        |

| 20  | TXD1(P2A)         | В   | 3ICU/3T2       | UART1 transmit data/GPIO                            |

| 21  | RXD1(P2B)         | В   | 3ICU/3T2       | UART1 receive data/GPIO                             |

| 22  | TI0CA0(P19)       | В   | 3ICU/3T2       | Multiple timer input capture/output compare A0/GPIO |

| 23  | TI0CA1(P1B)       | В   | 3ICU/3T2       | Multiple timer input capture/output compare A1/GPIO |

| 24  | V <sub>DD</sub> 1 | Р   |                | Digital 1.5V power supply                           |

| 25  | V <sub>DD</sub> 2 | Р   |                | Digital 3.3V power supply                           |

| 26  | V <sub>SS</sub>   | Р   |                | Digital ground                                      |

| 27  | TXD0(P1D)         | В   | 3ICU/3T2       | UART0 transmit data/GPIO                            |

| 28  | RXD0(P1E)         | В   | 3ICU/3T2       | UART0 receive data/GPIO                             |

| 29  | XFWE(P01)         | В   | 3ICU/3T2       | NAND FLASH write enable                             |

| 30  | XFRE(P02)         | В   | 3ICU/3T2       | NAND FLASH read enable                              |

| 31  | XALE(P03)         | В   | 3ICU/3T2       | NAND FLASH address latch enable                     |

| 32  | XCLE(P04)         | В   | 3ICU/3T2       | NAND FLASH command latch enable                     |

| 33  | XFCE1(P1F)        | В   | 3ICU/3T2       | NAND FLASH chip enable 1/GPIO                       |

| 34  | XFCE0(P00)        | В   | 3ICU/3T2       | NAND FLASH chip enable 0/GPIO                       |

| 35  | XFWP(P05)         | В   | 3ICU/3T2       | NAND FLASH write protect/GPIO                       |

| 36  | XFBSY             | 1   | 3IS            | NAND FLASH busy                                     |

| 37  | FD0               | В   | 3ICD/3T2       | NAND FLASH data bit0                                |

| 38  | FD1               | B   | 3ICD/3T2       | NAND FLASH data bit                                 |

| 39  | V <sub>DD</sub> 2 | P   |                | Digital 3.3V power supply                           |

| 40  | V <sub>SS</sub>   | P   |                | Digital ground                                      |

|     | n preceding page.                    |     | Characteristic | Function                                               |

|-----|--------------------------------------|-----|----------------|--------------------------------------------------------|

| No. |                                      | 1/0 | Characteristic | Function                                               |

| 41  | FD2                                  | В   | 3ICD/3T2       | NAND FLASH data bit2                                   |

| 42  | FD3                                  | В   | 3ICD/3T2       | NAND FLASH data bit3                                   |

| 43  | FD4                                  | В   | 3ICD/3T2       | NAND FLASH data bit4                                   |

| 44  | FD5                                  | В   | 3ICD/3T2       | NAND FLASH data bit5                                   |

| 45  | FD6                                  | В   | 3ICD/3T2       | NAND FLASH data bit6                                   |

| 46  | FD7                                  | В   | 3ICD/3T4       | NAND FLASH data bit7                                   |

| 47  | EXTINT0(P21)                         | В   | 3ISU/3T2       | External interrupt bit0/GPIO                           |

| 48  | EXTINT1(P22)                         | В   | 3ISU/3T2       | External interrupt bit1/GPIO                           |

| 49  | EXTINT2(P23)                         | В   | 3ISU/3T2       | External interrupt bit2/GPIO                           |

| 50  | EXTINT3(P24)                         | В   | 3ISU/3T2       | External interrupt bit3/GPIO                           |

| 51  | EXTINT4(P25)                         | В   | 3ISU/3T2       | External interrupt bit4/GPIO                           |

| 52  | V <sub>DD</sub> 1                    | Р   |                | Digital 1.5V power supply                              |

| 53  | V <sub>DD</sub> 2                    | Р   |                | Digital 3.3V power supply                              |

| 54  | V <sub>SS</sub>                      | Р   |                | Digital ground                                         |

| 55  | DOUT                                 | 0   | 302            | PCM output data                                        |

| 56  | DIN                                  | I   | 3ICD           | PCM input data                                         |

| 57  | ВСК                                  | В   | 3IC/3T2        | PCM bit clock                                          |

| 58  | LRLK(P12)                            | В   | 3ICU/3T2       | PCM LR clock/GPIO                                      |

| 59  | MCLK(P13)                            | В   | 3ICU/3T2       | PCM main clock/GPIO                                    |

| 60  | SCL(P28)                             | В   | 3ICU/3T2       | I <sup>2</sup> C SCL clock/GPIO                        |

| 61  | SDA(P29)                             | В   | 3ICU/3T2       | I <sup>2</sup> C SDA data/GPIO                         |

| 62  | TXD2(P2C)                            | В   | 3ICU/3T2       | UART2 transmit data/GPIO                               |

| 63  | RXD2(P2D)                            | В   | 3ICU/3T2       | UART2 receive data/GPIO                                |

| 64  | TEST1                                | I   | 3IS            | Test pin (normally tied to Low)                        |

| 65  | TEST2                                |     | 3IS            | Test pin (normally tied to Low)                        |

| 66  | V <sub>DD</sub> 1                    | Р   |                | Digital 1.5V power supply                              |

| 67  | SDWP                                 | 1   | 3IC            | SD card write protect                                  |

| 68  | SDCD/INS                             |     | 3ICU           | SD card detect/MSINS                                   |

| 69  | SDCMD/BS                             | В   | 3ICU/3T6       | SD card command/MSBS                                   |

| 70  | SDCLK/SCLK                           | 0   | 306            | SD card clock/MS clock                                 |

| 70  | SDAT0/DATA0                          | В   | 3ICUD/3T6      | SD card data/MS data                                   |

| 72  |                                      | P   | 516667,516     | Digital ground                                         |

| 72  | V <sub>SS</sub><br>V <sub>DD</sub> 3 | P   |                | Digital 3.3V/1.8V power supply                         |

| 73  |                                      | В   |                |                                                        |

|     | SDAT1/DATA1                          |     | 3ICUD/3T6      | SD card data/MS data                                   |

| 75  | SDAT2/DATA2                          | В   | 3ICUD/3T6      | SD card data/MS data                                   |

| 76  | SDAT3/DATA3                          | В   | 3ICUD/3T6      | SD card data/MS data                                   |

| 77  | AV <sub>DD</sub> PLL1                | P   |                | PLL1 analog power supply                               |

| 78  | AV <sub>SS</sub> PLL1                | P   |                | PLL1 analog ground                                     |

| 79  | VCNT1                                | 0   | 1A             | PLL1 VCO control                                       |

| 80  | V <sub>DD</sub> XT                   | Р   |                | System /USB PHY oscillation amplifier 1.5V power suppl |

| 81  | V <sub>SS</sub> XT                   | Р   |                | System /USB PHY oscillation amplifier ground           |

| 82  | X <sub>IN</sub> 1                    | I   | Х              | System /USB PHY oscillation amplifier input            |

| 83  | X <sub>OUT</sub> 1                   | В   | Х              | System /USB PHY oscillation amplifier output           |

| 84  | V <sub>DD</sub> RTC                  | Р   |                | RTC power supply                                       |

| 85  | V <sub>SS</sub> RTC                  | Р   |                | RTC ground                                             |

| 86  | XOUT32K                              | 0   | Х              | RTC 32.768kHz oscillation amplifier output             |

| 87  | XIN32K                               | I   | Х              | RTC 32.768kHz oscillation amplifier input              |

| 88  | VDET                                 | I   | 1IC            | Voltage detect input                                   |

| 89  | RTCINT                               | 0   | 1T3            | RTC interrupt output                                   |

| 90  | BACKUPB                              | I   | 1IC            | RTC mode (RTC only or whole IC)                        |

| 91  | AV <sub>DD</sub> PHY1                | Р   |                | USB PHY 1.5V power supply                              |

| 92  | AV <sub>SS</sub> PHY1                | Р   |                | USB PHY analog ground                                  |

| No. |                       | I/O | Characteristic | Function                           |

|-----|-----------------------|-----|----------------|------------------------------------|

| 93  | AV <sub>SS</sub> PHY1 | Р   |                | USB PHY analog ground              |

| 94  | RREF                  | В   | ЗA             | USB PHY reference resistor         |

| 95  | AV <sub>SS</sub> PHY2 | Р   |                | USB PHY analog ground              |

| 96  | AV <sub>DD</sub> PHY2 | Р   |                | USB PHY analog 3.3V power supply   |

| 97  | AV <sub>DD</sub> PHY2 | Р   |                | USB PHY analog 3.3V power supply   |

| 98  | AV <sub>SS</sub> PHY2 | Р   |                | USB PHY analog ground              |

| 99  | AV <sub>SS</sub> PHY2 | Р   |                | USB PHY analog ground              |

| 100 | AV <sub>SS</sub> PHY2 | Р   |                | USB PHY analog ground              |

| 101 | AV <sub>DD</sub> PHY2 | Р   |                | USB PHY analog 3.3V power supply   |

| 102 | DP                    | В   | ЗA             | USB D+                             |

| 103 | DM                    | В   | ЗA             | USB D-                             |

| 104 | AV <sub>SS</sub> PHY2 | Р   |                | USB PHY analog ground              |

| 105 | AV <sub>DD</sub> PHY2 | Р   |                | USB PHY analog 3.3V power supply   |

| 106 | AV <sub>DD</sub> ADC  | Р   |                | A/D converter analog power supply  |

| 107 | AN0                   | I   | ЗA             | A/D converter analog input Ch0     |

| 108 | AN1                   | I   | ЗA             | A/D converter analog input Ch1     |

| 109 | AN2                   | I   | ЗA             | A/D converter analog input Ch2     |

| 110 | AN3                   | I   | ЗA             | A/D converter analog input Ch3     |

| 111 | AV <sub>SS</sub> ADC  | Р   |                | A/D converter analog ground        |

| 112 | V <sub>SS</sub>       | Р   |                | Digital ground                     |

| 113 | X <sub>IN</sub> 2     | I   | Х              | Audio 16.9344MHz oscillator input  |

| 114 | X <sub>OUT</sub> 2    | 0   | Х              | Audio 16.9344MHz oscillator output |

| 115 | V <sub>DD</sub> 1     | Р   |                | Digital 1.5V power supply          |

| 116 | AV <sub>DD</sub> PLL2 | Р   |                | PLL2 analog power supply           |

| 117 | AV <sub>SS</sub> PLL2 | Р   |                | PLL2 analog ground                 |

| 118 | VCNT2                 | 0   | 3A             | PLL2 VCO control                   |

| 119 | V <sub>DD</sub> 2     | Р   |                | Digital 3.3V power supply          |

### **Pin Functions**

| I | Input pin          |  |  |  |

|---|--------------------|--|--|--|

| 0 | Output pin         |  |  |  |

| В | Bi-directional pin |  |  |  |

| Р | Power supply pin   |  |  |  |

| Pin name                               | Direction | Count | Function                                    |  |

|----------------------------------------|-----------|-------|---------------------------------------------|--|

| (1) Clock, reset, system pin (12 pins) |           |       |                                             |  |

| TEST[6:1]                              | I         | 6     | Test pin                                    |  |

| NRES                                   | I         | 1     | Reset input                                 |  |

| X <sub>IN</sub> 1                      | I         | 1     | System/USB PHY oscillator amplifier input   |  |

| X <sub>OUT</sub> 1                     | 0         | 1     | System/USB PHY oscillator amplifier output  |  |

| X <sub>IN</sub> 2                      | I         | 1     | Audio 16.9344MHz oscillator input           |  |

| X <sub>OUT</sub> 2                     | 0         | 1     | Audio 16.9344MHz oscillator output          |  |

| PHI(P11)                               | O(B)      | 1     | AHB bus clock output/32.768kHz clock output |  |

|                                        |           |       | Functions as P11 after hard reset           |  |

| (2) Interrupt (6 pins)                 |           |       |                                             |  |

| EXTFIQ(P2F)                            | I(B)      | 1     | External FIQ interrupt                      |  |

|                                        |           |       | Functions as P2F after hard reset           |  |

| EXTINT[4:0]                            | I(B)      | 5     | External interrupt                          |  |

| (P[25:21])                             |           |       | Functions as port after hard reset          |  |

|                                 |           |       | 23410-101                                                                                |

|---------------------------------|-----------|-------|------------------------------------------------------------------------------------------|

| Continued from preceding page   | e.        |       |                                                                                          |

| Pin name                        | Direction | Count | Function                                                                                 |

| (3) NAND FLASH I/F (16 pins     | ;)        |       |                                                                                          |

| XFCEO(P00)                      | O(B)      | 1     | NAND FLASH chip enable 0<br>Functions as P00 after hard reset                            |

| XFCE1(P1F)                      | O(B)      | 1     | NAND FLASH chip enable 1<br>Functions as P1F after hard reset                            |

| XFWE(P01)                       | O(B)      | 1     | NAND FLASH write enable                                                                  |

| XFRE(P02)                       | O(B)      | 1     | Functions as P01 after hard reset           NAND FLASH read enable                       |

| XALE(P03)                       | O(B)      | 1     | Functions as P02 after hard reset           NAND FLASH address latch enable              |

| XCLE(P04)                       | O(B)      | 1     | Functions as P03 after hard reset           NAND FLASH command latch enable              |

| XFWP(P05)                       | O(B)      | 1     | Functions as P04 after hard reset           NAND FLASH write protect                     |

| XFBSY                           | 1         | 1     | Functions as P05 after hard reset<br>NAND FLASH busy                                     |

| FD[7:0]                         | В         | 8     | NAND FLASH data                                                                          |

| (4) SD card I/F, MS I/F (8 pins |           | Ŭ     |                                                                                          |

| SDWP0                           |           | 1     | SD card write protect                                                                    |

| SDCD0/INS                       | 1         |       | SD card card detect / MSINS                                                              |

|                                 | -         | 1     |                                                                                          |

| SDCMD0/BS                       | В         | 1     | SD card command / MSBS                                                                   |

| SDCLK0/SCLK                     | 0         | 1     | SD card clock / MS clock                                                                 |

| SDAT0[3:0]/DATA[3:0]            | В         | 4     | SD card data / MS data                                                                   |

| (5) PCM I/F (5 pins)            |           |       |                                                                                          |

| DOUT                            | 0         | 1     | PCM output data                                                                          |

| DIN                             | I         | 1     | PCM input data                                                                           |

| BCK                             | В         | 1     | PCM bit clock                                                                            |

| LRCK(P12)                       | B(B)      | 1     | PCM LR clock<br>Functions as LRCK after hard reset                                       |

| MCLK(P13)                       | B(B)      | 1     | PCM main clock<br>Functions as MCLK after hard reset                                     |

| (6) Serial I/F (14 pins)        |           |       | •                                                                                        |

| SCK0 (P08)                      | В         | 1     | Serial I/F 0 clock<br>Functions as P08 after hard reset                                  |

| SDO0 (P09)                      | O (B)     | 1     | Serial I/F 0 output data<br>Functions as P09 after hard reset                            |

| SDI0 (P0A)                      | I (B)     | 1     | Serial I/F 0 input data<br>Functions as P0A after hard reset                             |

| SCK1 (P14)                      | B (B)     | 1     | Serial I/F 1 clock<br>Functions as P14 after hard reset                                  |

| SDO1 (P15)                      | O (B)     | 1     | Serial I/F 1 output data                                                                 |

| SDI1 (P16)                      | I (B)     | 1     | Functions as P15 after hard reset Serial I/F 1 input data                                |

| TXD0 (P1D)                      | O (B)     | 1     | Functions as P16 after hard reset         UART transmit data                             |

| RXD0 (P1E)                      | I (B)     | 1     | Functions as P1D after hard reset         UART receive data                              |

| TXD1 (P2A)                      | O (B)     | 1     | Functions as P1E after hard reset           UART1 transmit data                          |

| RXD1 (P2B)                      | I (B)     | 1     | Functions as P2A after hard reset           UART1 receive data                           |

| TXD2(P2C)                       | O (B)     | 1     | Functions as P2B after hard reset         UART2 transmit data                            |

| RXD2(P2D)                       | I (B)     | 1     | Functions as P2C after hard reset         UART2 receive data                             |

| SCL (P28)                       | B (B)     | 1     | Functions as P2D after hard reset         I <sup>2</sup> C SCL clock (open drain output) |

| SDA (P29)                       | В (В)     | 1     | Functions as P28 after hard reset<br>I <sup>2</sup> C SDA data (open drain output)       |

|                                 |           |       | Functions as P29 after hard reset                                                        |

| Pin name                  | Direction | Count | Function                                                          |

|---------------------------|-----------|-------|-------------------------------------------------------------------|

| (7)Timer (2 pins)         |           |       |                                                                   |

| TIOCA0 (P19)              | B(B)      | 1     | Multiple timer input capture/output compare A0                    |

| · · ·                     |           |       | Functions as P19 after hard reset                                 |

| TIOCA1 (P1B)              | B(B)      | 1     | Multiple timer input capture/output compare A1                    |

| (8) JTAG (6 pins)         |           |       | Functions as P1B after hard reset                                 |

| TCK                       |           | 1     | JTAG test clock                                                   |

| RTCK                      | 0         | 1     | JTAG test returned clock                                          |

| NTRST                     |           | 1     | JTAG test reset                                                   |

| TDI                       |           | 1     | JTAG test data input                                              |

| TMS                       |           | 1     | JTAG test mode select                                             |

| TDO                       | 0         | 1     | JTAG test data output                                             |

| (9) RTC (5 pins)          | 0         | I     |                                                                   |

| XOUT32K                   | 0         | 1     | RTC 32.768kHz oscillator amplifier output                         |

| XIN32K                    |           | 1     | RTC 32.768kHz oscillator amplifier input                          |

| VDET                      |           | 1     | Voltage detect input                                              |

| RTCINT                    | 0         | 1     | RTC interrupt output                                              |

| ВАСКИРВ                   | 1         | 1     | RTC mode (RTC only or LSI whole)                                  |

| (10) PLL (2 pins)         |           |       |                                                                   |

| VCNT1                     | 0         | 1     | PLL1 VCO control                                                  |

| VCNT2                     | 0         | 1     | PLL2 VCO control                                                  |

| (11) USB (3 pins)         | Ŭ         |       |                                                                   |

| DP                        | В         | 1     | USB D+ (Device)                                                   |

| DM                        | B         | 1     | USB D- (Device)                                                   |

| RREF                      | В         | 1     | USB PHY reference resistor                                        |

| (12) Analog (4 pins)      |           |       |                                                                   |

| AN[3:0]                   | 1         | 4     | Analog input                                                      |

| (13) Power supply pin (37 | pins)     |       |                                                                   |

| V <sub>DD</sub> 1         | P         | 4     | Digital 1.5V power supply                                         |

| V <sub>DD</sub> 2         | Р         | 4     | Digital 3.3V power supply                                         |

| V <sub>DD</sub> 3         | Р         | 1     | Digital 3.3V/1.8V power supply (SD card I/F, MS I/F power supply) |

| V <sub>SS</sub>           | Р         | 6     | Digital ground                                                    |

| AV <sub>DD</sub> PLL1     | Р         | 1     | PLL1 analog power supply                                          |

| AV <sub>SS</sub> PLL1     | Р         | 1     | PLL1 analog ground                                                |

| AV <sub>DD</sub> PLL2     | Р         | 1     | PLL2 analog power supply                                          |

| AV <sub>SS</sub> PLL2     | Р         | 1     | PLL2 analog ground                                                |

| V <sub>DD</sub> RTC       | Р         | 1     | RTC power supply                                                  |

| V <sub>SS</sub> RTC       | Р         | 1     | RTC ground                                                        |

| V <sub>DD</sub> XT        | Р         | 1     | Oscillation amplifier 1.5V power supply                           |

| V <sub>SS</sub> XT        | Р         | 1     | Oscillation amplifier ground                                      |

| AV <sub>DD</sub> PHY1     | Р         | 1     | USB PHY analog 1.5V power supply                                  |

| AV <sub>SS</sub> PHY1     | Р         | 2     | USB PHY analog ground                                             |

| AV <sub>DD</sub> PHY2     | Р         | 4     | USB PHY analog 3.3V power supply                                  |

| AV <sub>SS</sub> PHY2     | Р         | 5     | USB PHY analog ground                                             |

| AV <sub>DD</sub> ADC      | Р         | 1     | A/D converter analog power supply                                 |

| AV <sub>SS</sub> ADC      | Р         | 1     | A/D converter analog ground                                       |

### Peripheral Circuit Example

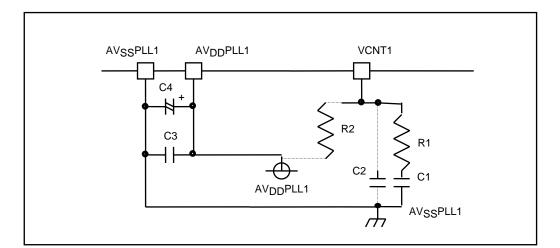

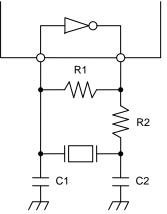

### PLL Peripheral Circuit 1 (for system)

The PLL1 circuit configuration is shown in the figure below. On the wiring board, connect the decoupling capacitors as close as possible to the pin, and separate the power line from other power supply lines to minimize noise.

| Symbol  | Value            | Model or Accuracy                                            |  |

|---------|------------------|--------------------------------------------------------------|--|

| R1      | 100 to 200Ω      | ±5%                                                          |  |

| R2      | *MΩ              | ±5%                                                          |  |

| C1      | 0.1 to 0.22µF    | Capacitance error: ±10%<br>Temperature characteristics: ±10% |  |

| C2      | (Approx. C1/100) |                                                              |  |

| C3      | 0.1µF            | (-25 to +85°C)                                               |  |

| C4 33µF |                  | 16CV33BS                                                     |  |

\* C4: This is based on SANYO Electric's Surface Mount Device Catalog (CV-BS Series).

Note:

Generally, use R2 and C2 without mounting.

However, if there is a problem that affects the PLL characteristics, the PLL characteristics may be improved by mounting R2 and C2. Therefore, be sure to prepare R2 and C2 wiring patterns beforehand.

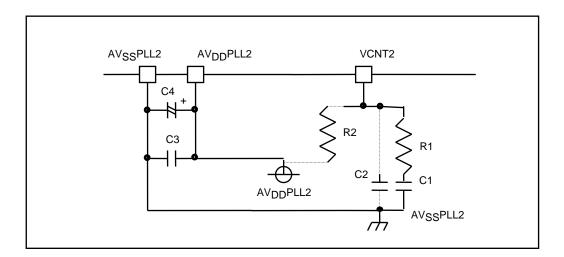

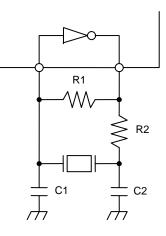

### PLL Peripheral Circuit 2 (for audio)

The PLL2 circuit configuration is shown in the figure below. On the wiring board, connect the decoupling capacitors as close as possible to the pins, and separate the power line from other power supply lines to minimize noise.

| Symbol | Value            | Model or Accuracy                 |

|--------|------------------|-----------------------------------|

| R1     | 100 to 200Ω      | ±5%                               |

| R2     | *MΩ              | ±5%                               |

| C1     | 1.0 to 2.0μF     | Capacitance error: ±10%           |

| C2     | (Approx. C1/100) | Temperature characteristics: ±10% |

| C3     | 0.1µF            | (-25 to +85°C)                    |

| C4     | 33µF             | 16CV33BS                          |

\* C4: This is based on SANYO Electric's Surface Mount Device Catalog (CV-BS Series).

Note:

Generally, use R2 and C2 without mounting.

However if there is a problem that affects the PLL characteristics, the PLL characteristics may be improved by mounting R2 and C2. Therefore, be sure to prepare R2 and C2 wiring patterns beforehand.

#### Reference

For audio applications, experiments have confirmed that

C1=1.0µF, C2=0.01µF

can be effective in maximizing the jitter reduction of the PLL output clock.

(Note that this depends on the board and other environmental conditions, and the result is not guaranteed.)

#### **USB2.0** Peripheral Circuit

Be sure to always observe the items below when designing the circuit board.

• Differential impedance control

The DP/DM routing width, routing clearance, and PCB layer spacing must be determined so that differential impedance of  $90\Omega$  can be achieved. We recommend a microstrip structure for realizing impedance matching.

• Power supply (AV<sub>DD</sub>PHY2, AV<sub>DD</sub>PHY1) and ground (AV<sub>SS</sub>PHY2, AV<sub>SS</sub>PHY1) lines The separation of the power line and ground line only for USB usage is recommended. At a minimum, insert 10 $\mu$ F, 0.1 $\mu$ F, and 0.01 $\mu$ F capacitors between the power supply and ground for filtering. To reject high-frequency noise, inserting the 0.01 $\mu$ F capacitor directly under the power pin and ground pin is recommended.

Note that  $0.1\mu F$  capacitor is also effective for latch-up protection.

• Crystal oscillator

Use a crystal oscillator connected to the  $X_{IN1}$  and  $X_{OUT1}$  pins that has a fundamental wave of 12MHz, oscillation accuracy of 100p-pm or less, and place it near the IC.

• Reference resistor

Connect the RREF pin to the ground near the IC through the  $680\Omega$  (tolerance 1% or less) reference resistor.

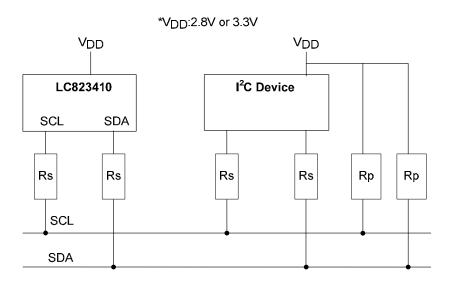

### I<sup>2</sup>C Peripheral Circuit

For the Rs and Rp values, see the  $I^2C$  standards.

### **XTAL Peripheral Circuit**

#### XTAL1 (12MHz)

12MHz oscillation amplifier RC reference values  $\rightarrow$  R1=1M $\Omega$ , R2=0 $\Omega$ , C1=C2=22pF Applicable pins: XIN1, XOUT1 |

### XTAL2 (16.9344MHz)

16.9344MHz oscillation amplifier RC reference values  $\to$  R1=1MΩ, R2=0Ω, C1=C2=22pF Applicable pins: X<sub>IN</sub>2, X<sub>OUT</sub>2

#### XTALRTC (32.768kHz)

32.768kHz oscillation amplifier RC reference values  $\rightarrow$  R1=5.1M $\Omega$ , R2=330k $\Omega$ , C1=C2=22pF Applicable pins: XIN32K, XOUT32K

(Reference) Oscillator product: DT-38 (DAISHINKU Corp.)

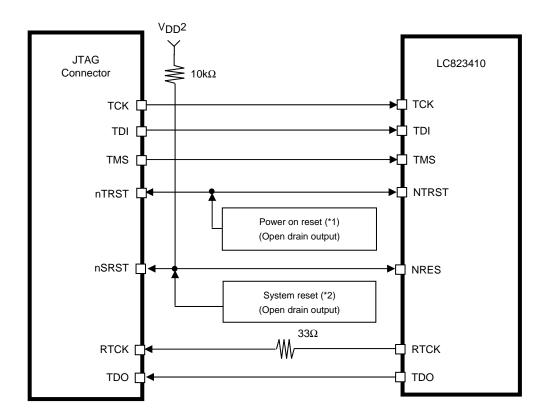

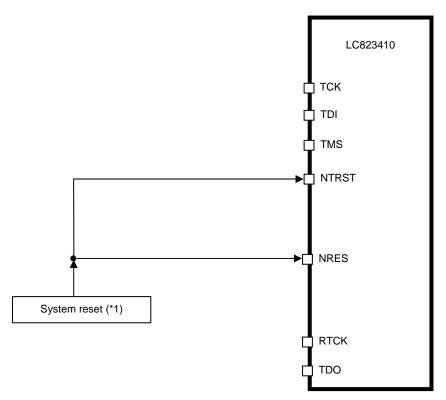

### JTAG Pin Treatment Examples (both for use of ICE and non-use of ICE)

- (\*1) The power-on reset is a reset signal that becomes active-low only when the power is turned on. Set so that the NTRST pin is reset only by a reset from JTAG and power-on reset.

- (\*2) System reset includes a power-on reset and a reset signal, requested by the system, that becomes active-low by a manual reset or other means.

Set so that the NRES pin is reset by the reset from JTAG and by system reset.

See the data sheet for the NRES pin reset specifications. The NTRST pin has the same specifications as those of the NRES pin.

The power-on reset (open drain output) can be implemented, for example, by connecting it to the ground through a capacitor.

The above configuration is a peripheral circuit example that assumes the use of a JTAG ICE by YDC (Yokogawa Digital Computer) and can be applied both in cases where ICE is and is not used. To use other products, inquire at the manufacturer.

### JTAG Pin Treatment Examples (non-use of ICE)

(\*1) System reset includes a power-on reset that becomes active-low only when power is turned on, or a reset signal, requested by the system, that becomes active-low by a manual reset or other means.

The NTRST pin has the same specifications as those of the NRES pin, and at least a power-on reset must be implemented.

As shown in this example, system reset can be connected to the NRES pin directly.

The above configuration is a simplified example of a peripheral circuit in the case that ICE is not used.

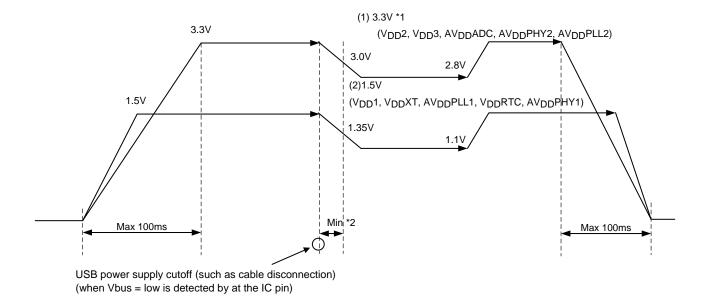

### **Power-on Sequence**

\*1 The following relations must be satisfied.

• AVDDPHY2>=AVDDADC VDD2>=AVDDPLL2 VDD2>=VDD3

\*2

• This is a period required only when the AHB clock is operating at a frequency higher than the internal operating frequency guaranteed by  $V_{DD}1 >= 1.35V$ , and this is needed for switching to an operating frequency guaranteed by  $V_{DD}1 >= 1.0V$ . The minimum time depends on the system. For the guaranteed operating frequency at each voltage, see the data sheet.

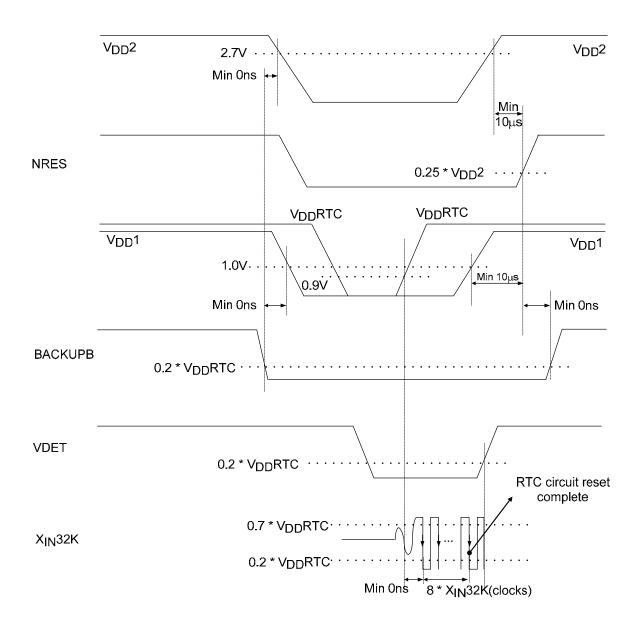

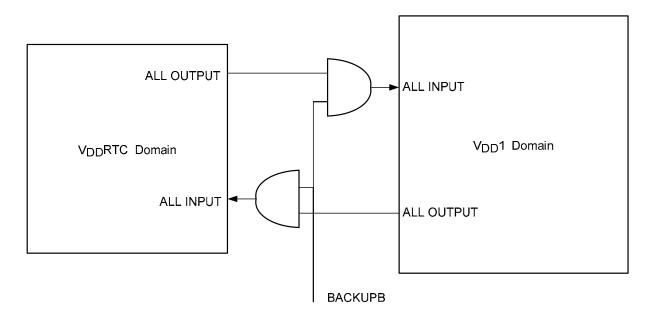

### **RTC Pin Power On/Off Control Sequence**

When running RTC only at power-off of the device, it is required to detect the voltage drop of  $V_{DD}1$ ,  $V_{DD}2$  and set BACKUPB to low. Determine the detection level of  $V_{DD}1$  and  $V_{DD}2$  according to the conditions of the device. The VDET pin needs to be set to low when the RTC power supply is cut off (when RTC operation is stopped). Also, when drop in the RTC power supply voltage is detected, VDET must be set to low. The figure below shows the power on/off sequence when the detection level of  $V_{DD}RTC$  is 0.9V or less. Determine the detection level of  $V_{DD}RTC$  according to the conditions of the device.

(Reference: Internal control by BACKUPB)

NOTE: VDD1 can be shut down while BACKUPB=Low

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of June, 2010. Specifications and information herein are subject to change without notice.