#### **Typical Applications**

- Low Jitter Clock Generation

- Low Bandwidth Jitter Attenuation

- Low Frequency PLL

- Frequency Translation

- OCXO Frequency Multiplier

- Phase Lock clean high frequency references to 10MHz equipment

#### Features

Low Current Consumption: <2 mA Typical High Phase Frequency Detector Rate: 140 MHz Hardware Pin Programmable Clock Multiplication Ratios: x1/ x5/ x10 Lock Detect Indicator Power Down Mode (0.7 µA typical)

8 Lead MS8E Package: 4.8 mm x 3.0 mm

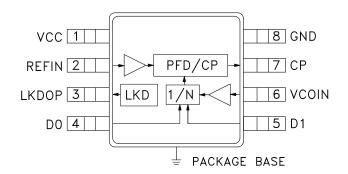

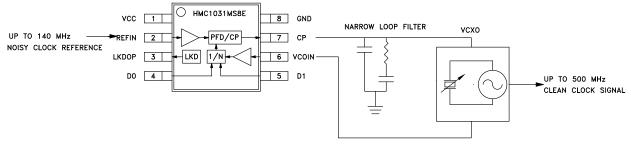

#### **Functional Diagram**

#### **General Description**

Together with an external loop filter and a VCXO, the HMC1031MS8E forms a complete clock generator solution targeted at low frequency jitter-cleaner and reference clock generation applications.

The HMC1031MS8E features a low power integer-N divider supporting divide ratios of 1/5/10, that is controlled via external hardware pins and requires no serial port.

The Integrated Phase Detector and Charge Pump are capable of operating up to 140 MHz, and a maximum VCXO input of 500 MHz ensure frequency compliance with a wide variety of system clocks and VCXOs.

Additional features include Integrated Lock Detect Indicator available on a dedicated hardware pin, and a built-in Power Down Mode.

The HMC1031MS8E is housed in a 8 lead MS8E SMT package.

#### **Electrical Specifications**

$T_A = +25 \text{ °C}, \text{ VCC} = 3.3 \text{ V}, \text{ Unless Otherwise Specified.}$

| Parameter                                                                      | Conditions                                                                                | Min       | Тур                     | Max          | Units            |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------|-------------------------|--------------|------------------|

| Power Supply Voltage                                                           |                                                                                           | 2.7       | 3.3                     | 3.5          | V                |

| Operating Temperature                                                          |                                                                                           | -40       | 27                      | 85           | °C               |

| Reference Frequency                                                            | Externally AC coupled [1]                                                                 |           |                         | 140          | MHz              |

| VCO Frequency                                                                  |                                                                                           |           |                         | 500          | MHz              |

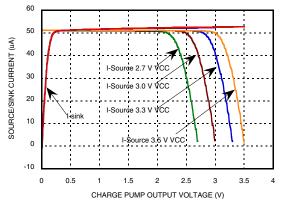

| Charge Pump Current                                                            |                                                                                           |           | 50                      |              | μA               |

| Input Voltage Swing (Reference & VCO Inputs) [2]                               | Exernally AC Coupled to the Chip. 0.1 3.5                                                 |           |                         |              | Vpp              |

| REF, VCO Input DC Bias                                                         | 0.5*VCC approximately                                                                     |           | 1.65                    |              | V                |

| Input Duty Cycle                                                               |                                                                                           | 40        |                         | 60           | %                |

| Charge Pump Output Range                                                       |                                                                                           | (         | <b>X</b> <sup>[3]</sup> |              |                  |

| Input Impedance at 50 MHz                                                      | Applicable to REF an VCO Input Pins. 3600  4                                              |           |                         |              | ΩllpF            |

| Divide Ratios                                                                  | VCO/VCXO Feedback Divider                                                                 |           | 1/5/10                  |              |                  |

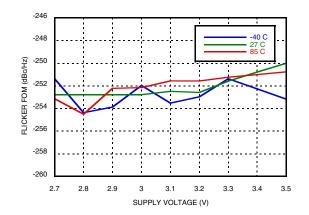

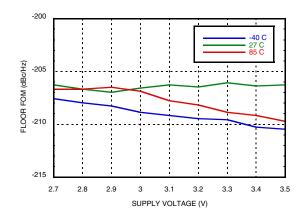

| Phase Noise <sup>[4]</sup><br>Floor Figure of Merit<br>Flicker Figure of Merit |                                                                                           |           |                         | -204<br>-248 | dBc/Hz<br>dBc/Hz |

| Flicker Noise at foffset                                                       | PN <sub>flick</sub> = Flicker FOM +20log(f <sub>vcxo</sub> ) -10log(f <sub>offset</sub> ) |           |                         |              |                  |

| Phase Noise Floor at f <sub>vcxo</sub> with f <sub>pd</sub>                    | $PN_{floor} = Floor FOM + 10log(f_{pd}) + 20log(f_{vcxo}/f_{pd})$                         |           |                         |              |                  |

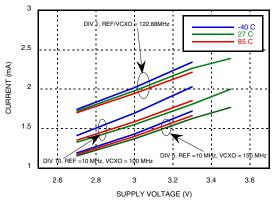

| Supply Current <sup>[5]</sup>                                                  | 100 MHz REF=VCXO, 3.3 V VCC                                                               |           | mA                      |              |                  |

| Power Down Current <sup>[6]</sup><br>[D0,D1 = 00]                              | 3.0 V VCC, 25 °C<br>3.3 V VCC, 85 °C<br>3.6 V VCC, 85°C                                   | 85 °C 0.8 |                         |              | uA<br>uA<br>uA   |

| Lock Detect Output Current                                                     | CMOS Output Level 3                                                                       |           |                         |              | mA               |

[1] The lower limit of operation is limited by off-chip AC coupling. The size of the AC coupling should be chosen to have insignificant impedance relative to the 3.6kOhm input impedance of the part, and any termination impedances on the evaluation board (50Ohm by default).

[2]REF and VCO inputs should be AC coupled to HMC1031MS8E. Peak Input level should not exceed VCC+0.4 V with respect to GND.

[3] PLL may lock in the voltage range of 0.2 to VCC - 0.4 V. However, the charge pump gain may be reduced. See Figure 9 CP Compliance

[4] See Figure 15, 16 for addional Flicker FOM and Floor FOM data.

[5] See Figure 10 for additional supply current data. Base Frequency 100MHz, Base VCC: 3.3V, 0.8 to 1mA/V, Base PFD current: 1.8 mA, 8  $\mu$ A/MHz Base DIV current: 1.15mA, 15  $\mu$ A/MHz. For example, the device current for a 10 MHz ref and 50 MHz VCO at 3.0 V VCC can be calculated as PFD Current delta = (10-100)\*8e-6 = -0.72, DIV current delta = (50-100)\*15e-6=-0.75 mA, Device current = (1.8-0.72)+(1.15-0.75)=1.48 mA at 3.3V VCC At 3 V VCC device current would be approx: 1.48 - 0.85e-3\*(3.3-3.0) = 1.225 mA

[6] In Power down mode, the REF/VCO inputs and charge pump outputs are tri-stated. The power down leakage current is measured without any signal applied to HMC1031MS8E.

# HMC1031MS8E

## CLOCK GENERATOR WITH INTEGER-N PLL 0.1 - 500 MHz

#### **Typical Performance Characteristics**

$T_{A} = +25 \text{ °C}$ , VCC = 3.3 V, Unless Otherwise Specified.

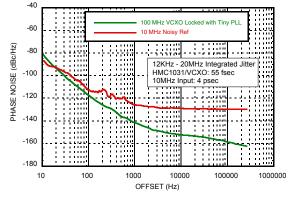

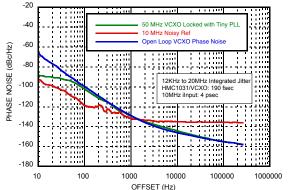

# Figure 1. 10 MHz to 100 MHz with Noisy Reference Phase Noise <sup>[1]</sup>

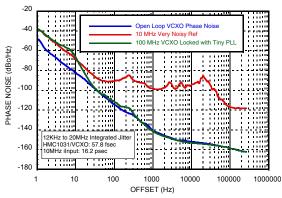

Figure 3. 10MHz to 100MHz with Very Noisy Reference Phase Noise

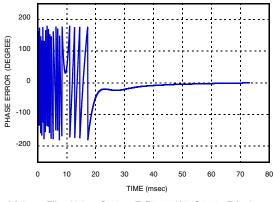

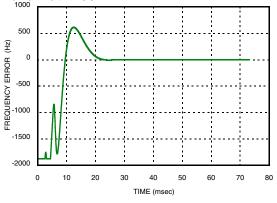

Figure 5. Phase Error during Lock Time for DIV 5, 10 MHz IN,50 MHz OUT, Loop Bandwidth 100 Hz

# Figure 2. 10MHz to 50MHz with Noisy Reference Phase Noise

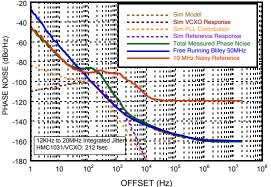

Figure 4. Typical Close Loop Phase Noise, HMC1031MS8E as Jitter Attenuator, Loop Bandwidth 100 Hz

Figure 6. Frequency Error during Lock Time for DIV 5, 10 MHz IN,50 MHz OUT, Loop Bandwidth 100 Hz <sup>III</sup>

[1] Loop Filter Value: C1 4.7  $\mu$ F, R2 1.2 K $\Omega$ , C2 62  $\mu$ F for Loop Filter bandwidth 8 Hz, VCXO: Crystek CVHD-950 100 MHz [2] Loop Filter Value: C1 220 nF, R2 3.3 K $\Omega$ , C2 2.2  $\mu$ F for Loop Filter bandwidth 50 Hz, VCXO: Bliley V105ACACB 50 MHz

[2] Loop Filter Value Refer to Loop Filter Configuration Table No 1. VCXO: Crystek CVHD-950 100MHz

[4] Loop Filter Value Refer to Loop Filter Configuration Table No 2. Simulated data is generated from Hittite PLL Design Software.

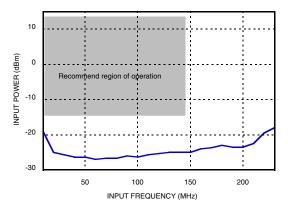

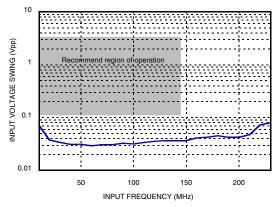

Figure 9. HMC1031MS8E REF Input Sensitivity vs. Frequency <sup>III</sup>

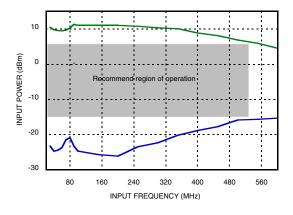

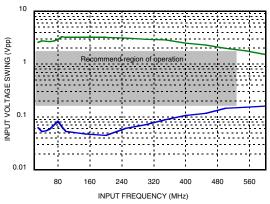

Figure 11. HMC1031MS8E VCO Input Sensitivity vs. Frequency <sup>[5]</sup>

Figure 8. HMC1031MS8E Current vs. Different Config

Figure 10. HMC1031MS8E REF Input Sensitivity vs. Frequency <sup>(4)</sup>

Figure 12. HMC1031MS8E VCO Input Sensitivity vs. Frequency <sup>[5]</sup>

[5] Maximum frequency is guaranteed in the recommended region of operation across temperature and process variation.

0.1 - 500 MHz

ROHS V

# EARTH FRIENDLY Figure 13. HMC1031MS8E Flicker FOM Figure

#### Figure 14. HMC1031MS8E Floor FOM

**CLOCK GENERATOR WITH INTEGER-N PLL**

For price, delivery and to place orders: Hittite Microwave Corporation, 2 Elizabeth Drive, Chelmsford, MA 01824 Phone: 978-250-3343 Fax: 978-250-3373 Order On-line at www.hittite.com Application Support: Phone: 978-250-3343 or apps@hittite.com

**CLOCK GENERATORS - SMT**

# HMC1031MS8E

## CLOCK GENERATOR WITH INTEGER-N PLL 0.1 - 500 MHz

#### Absolute Maximum Ratings

| VCC to GND                                                       | - 0.3 V to 3.6 V      |

|------------------------------------------------------------------|-----------------------|

| D0, D1 pins to GND                                               | -0.3 V to 3.6 V       |

| Maximum REF input voltage                                        | VCC + 0.4 V           |

| Maximum VCO input voltage                                        | VCC + 0.4 V           |

| Maximum Junction Temperature                                     | +125 °C               |

| Storage Temperature                                              | -65 to +150 °C        |

| Operating Temperature                                            | -40 to +85 °C         |

| Thermal Resistance                                               | 0.2 °C/mW             |

| Reflow Soldering<br>Peak Temperature<br>Time at Peak Temperature | +260 °C<br>40 seconds |

| ESD Sensitivity (HBM)                                            | Class 2               |

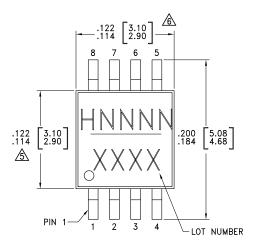

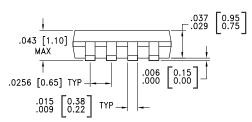

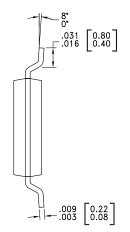

**Outline Drawing**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The absolute maximum ratings apply individually only and not in combination.

ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

NOTES:

- 1. PACKAGE BODY MATERIAL: LOW STRESS INJECTION MOLDED PLASTIC SILICA AND SILICON IMPREGNATED.

- 2. LEAD MATERIAL: COPPER ALLOY

- 3. LEAD PLATING: 100% MATTE TIN

- 4. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.15mm PER SIDE.

- A DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.25mm PER SIDE.

- 7. ALL GROUND LEADS MUST BE SOLDERED TO PCB RF GROUND.

#### Package Information

| Part Number | Number Package Body Material                       |               | MSL Rating          | Package Marking <sup>[1]</sup> |  |

|-------------|----------------------------------------------------|---------------|---------------------|--------------------------------|--|

| HMC1031MS8E | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 <sup>[2]</sup> | <u>1031</u><br>XXXX            |  |

[1] 4-Digit lot number XXXX

[2] Max peak reflow temperature of 260 °C

#### **Pin Descriptions**

| Pin Number | Function | Description                                                         | Interface Schematic |

|------------|----------|---------------------------------------------------------------------|---------------------|

| 1          | VCC      | Supply voltage Typical +3.3 V                                       |                     |

| 2          | REFIN    | Reference input, externally AC coupled reference<br>frequency input |                     |

| 3          | LKDOP    | Lock Detect output, CMOS drive                                      |                     |

| 4, 5       | D0, D1   | CMOS inputs used to specify integer-N division ratio                |                     |

| 6          | VCOIN    | VCO input, AC coupled VCO/VCXO input                                |                     |

| 7          | СР       | Charge Pump output                                                  |                     |

| 8          | GND      |                                                                     |                     |

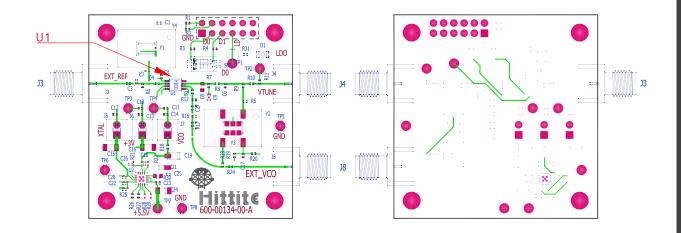

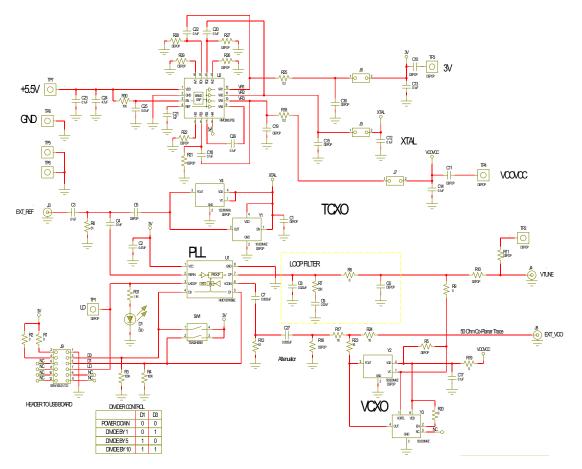

#### **Evaluation PCB**

A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

#### **Evaluation Order Information**

| Item                | Contents                   | Part Number        |

|---------------------|----------------------------|--------------------|

| Evaluation PCB Only | HMC1031MS8E Evaluation PCB | EVAL01-HMC1031MS8E |

ROHS V EARTH FRIENDLY CLOCK GENERATOR WITH INTEGER-N PLL 0.1 - 500 MHz

#### **Evaluation PCB Schematic**

#### Frequency Multiplication Truth Table

| HMC1031MS8E Pins [Set by SW1 | PLL Feedback Division |                 |

|------------------------------|-----------------------|-----------------|

| D0                           | D1                    | Ratio (N)       |

| 0                            | 0                     | Power Down Mode |

| 1                            | 0                     | 1               |

| 0                            | 1                     | 5               |

| 1                            | 1                     | 10              |

#### Loop Filter Configuration Table

| No. | Fref [MHz] | Fvco [MHz] | Div | BW [Hz] | C8     | R7     | C9     |

|-----|------------|------------|-----|---------|--------|--------|--------|

| 1   | 10         | 100        | 10  | 10      | 220 nF | 7.5 kΩ | 4.7 uF |

| 2   | 10         | 50         | 5   | 100     | 100 nF | 5.6 kΩ | 1 uF   |

| 3   | 10         | 50         | 5   | 2k      | 300 pF | 100 kΩ | 3.9 nF |

To view the <u>Eval PCB Schematic</u> please visit <u>www.hittite.com</u> and choose HMC1031MS8E from the "Search by Part Number" pull down menu.

HMC1031MS8E Application Information

Figure 15. HMC1031MS8E Application Diagram

#### **Jitter Attenuation**

In some cases, reference clocks to the system may come from external noisy sources with high jitter. The HMC1031MS8E may be used to attenuate this incoming jitter and distribute a clean clock in the system. In such a scheme, a narrow loop filter is selected for the HMC1031MS8E. The device frequency locks to the external VCXO but the reference jitter is attenuated as defined by the set loop filter bandwidth. The final output frequency and phase noise characteristics outside the loop bandwidth is defined by the phase noise characteristics of the VCXO used. A low jitter clock reference yields better clocking performance, better LO performance of RF PLLVCOs, and improves the SNR performance of data converters (ADC/DAC).

#### **Frequency Translation**

Quite often, the reference clock in a Test & Measurement or a Communications system is a high accuracy OCXO (Oven Controlled Crystal Oscillator) with excellent long-term stability. The HMC1031MS8E may find applications when the OCXO frequency needs to be multiplied up to a higher rate to drive the primary clock inputs in a system. The device offers a very low power, small package and high performance method to multiply its incoming frequency in x1, x5 and x10 rates. Such multiplication is needed because the higher reference clocks improve Phase Noise, ADC/DAC SNR, clock generator jitter and PHY BERs. In this scheme, the HMC1031MS8E may be connected to an external low cost VCXO (e.g. at 50MHz or 100MHz), and lock this external VCXO to the excellent long-term stability of the OCXO.

#### Loop Bandwidths with HMC1031MS8E

In typical jitter attenuation applications, an incoming reference clock is frequency locked with a narrow PLL Loop Bandwidth such that its incoming noise is filtered out by the PLL and VCXO combination. The out of band phase noise of the PLL follows the VCXO that it's locked to. A narrow PLL loop bandwidth ensures that the output jitter is determined by the VCXO (or any other type of high quality factor VCO) and not affected by the spectral noise of the incoming clock beyond the set loop bandwidth.

Considering that the HMC1031MS8E will be used in narrow loop filter bandwidth configurations, the device is designed to have a low charge pump current of 50uA. This architecture offers advantages in low power consumption and loop filter design. Typically, narrow loop filter bandwidths require large filter capacitors. Thanks to the low charge pump current design of the HMC1031MS8E, smaller loop filter capacitor sizes may be used to implement narrow loop filters. It should be kept in mind that the HMC1031MS8E is designed to operate in only a few kHz loop bandwidths in its widest-loop bandwidth configuration.

#### Using VCO/VCXO's with Negative Tuning Slope

In its normal configuration, HMC1031MS8E will work with any VCO/VCXO that has a positive tuning slope. For any VCO/VCXO with negative tuning slope i.e where frequency decreases with increasing tuning voltage, the loop filter AC ground should be connected to VCC instead of GND.