# **TLE6270R**

Quad Low Side Injector Driver

**Automotive Power**

## **Table of Contents**

# **Table of Contents**

| 1                                                  | Overview         Features         Application         General Description                                                                                                                                      | 4                                    |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 2                                                  | Block Diagram                                                                                                                                                                                                  | 6                                    |

| <b>3</b><br>3.1<br>3.2                             | Pin Configuration         Pin Assignment         Pin Definitions and Functions                                                                                                                                 | 7                                    |

| <b>4</b><br>4.1<br>4.2<br>4.3                      | General Product Characteristics Absolute Maximum Ratings Functional Range Thermal Resistance                                                                                                                   | 10                                   |

| <b>5</b><br>5.1<br>5.2<br>5.3                      | Functional Description List of Functionalities Load Control Output Current Control Current Control Configurations according to NON and Pch Signals                                                             | . 11<br>. 11<br>. 12                 |

| 5.4<br>5.4.1                                       | Diagnostic Failures Detection OFF State open load Functionality OFF State Overvoltage Functionality: HS Diag Filter Functionality: Diagnostic Control Circuit Functionality: SCn/OLn Definition Circuit Table: | . 14<br>. 15<br>. 16<br>. 16<br>. 16 |

| 5.4.2                                              | Failures Information (via SPI) Failure Register Output Coder Input Coder Shift Register SPI Control SDO Driver                                                                                                 | . 17<br>. 17<br>. 18<br>. 19         |

| 5.5<br>5.5.1<br>5.5.2<br>5.6                       | Protections All Inputs/Outputs T1, T4 Power Transistors Reset                                                                                                                                                  | . 21<br>. 21<br>. 21                 |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7 | Electrical Characteristics  Supply Current Inputs Outputs Current Control Current Control Timings Diagnostic and Protections SPI Timings                                                                       | . 22<br>. 23<br>. 25<br>. 26<br>. 26 |

| <b>7</b><br>7.1<br>7.2                             | Diagrams       Typical Laws         Output Timings Diagram       Typical Laws                                                                                                                                  | . 29                                 |

# TLE6270R Quad Low Side Injector Driver

## **Table of Contents**

| 8   | Application Information                                   | 31 |

|-----|-----------------------------------------------------------|----|

| 8.1 | Principle Diagram of Injection System                     | 31 |

| 8.2 | Typical Waveform Diagrams for One and Two Outputs Control | 32 |

| 9   | Package Outlines                                          |    |

| 10  | Revision History                                          |    |

Data Sheet 3 V1.3, 2008-12-23

#### **Quad Low Side Injector Driver**

**TLE6270R**

### 1 Overview

#### **Features**

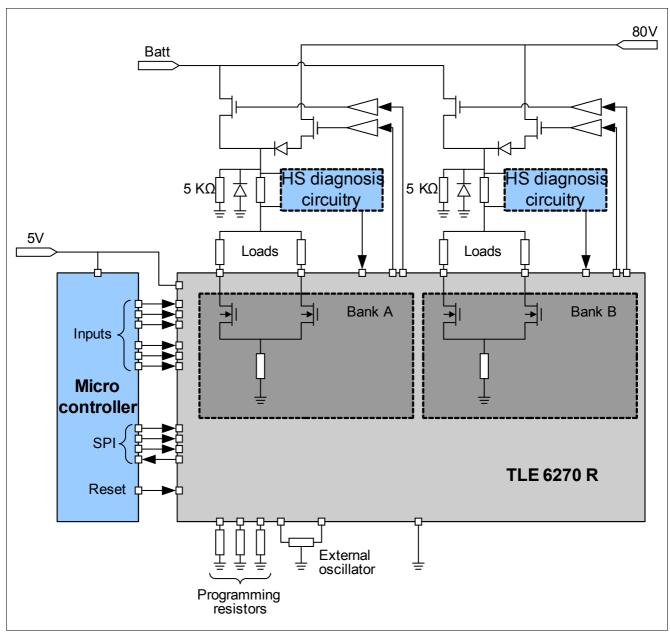

- Four integrated Low Side Switches, control logic and -outputs for external High Side Switches

- Programmable Peak and Hold output current control to adapt to application requirements.

- Detailed diagnostic of defective or missing injector connections

- Serial Peripheral Interface (SPI) for diagnostics and control of the device

- Short Circuit-, ESD and Overtemperature Protection

- Undervoltage Reset

- Green Product (RoHs compliant)

- AEC Qualified

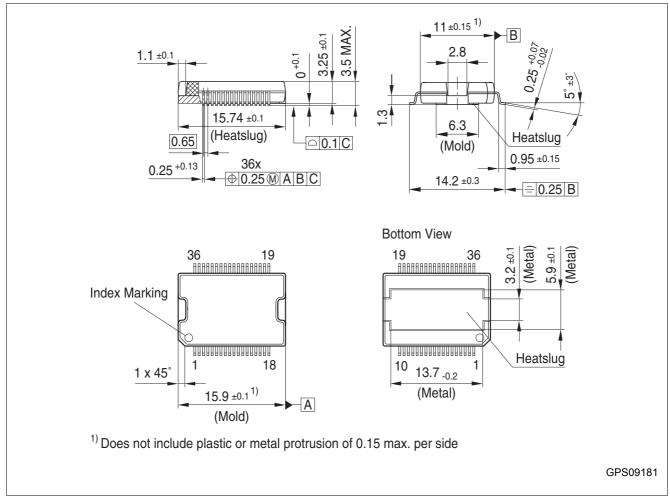

PG-DSO-36

#### **Application**

· Gasoline Direct Injection

#### **General Description**

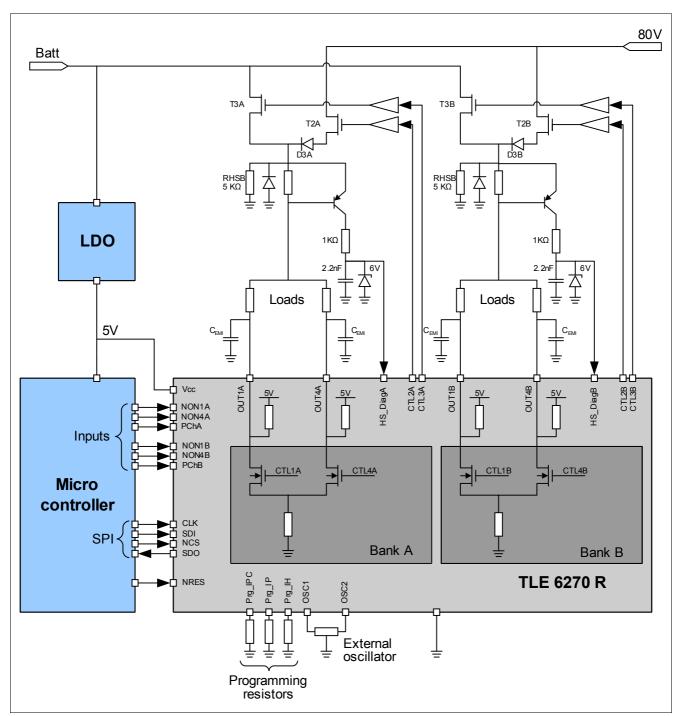

TLE6270R is specially suited for Gasoline Direct Injection Systems in Automotive Applications. The device controls the external High Side Transistors to supply the injectors alternating with battery Voltage and a boosted high voltage according the requirement of the applied injectors. The device incorporates the Low Side driver Transistors for four Injector Channels.

#### **Product Summary**

| Parameter                      | Symbol    | Value | Unit |

|--------------------------------|-----------|-------|------|

| Output channels                |           | 4     |      |

| Continuous output voltage max. | $V_{OUT}$ | 80    | V    |

| Clamping voltage typ.          | $V_{CLP}$ | 87    | V    |

| Peak current typ.              | $I_{P_C}$ | 11.50 | Α    |

| Hold current typ.              | $I_{H}$   | 2.30  | Α    |

| On resistance max. at 150 °C   | $R_{ON}$  | 300   | mΩ   |

| Туре     | Package   | Marking  |

|----------|-----------|----------|

| TLE6270R | PG-DSO-36 | TLE6270R |

Overview

Figure 1 Application Diagram

**Block Diagram**

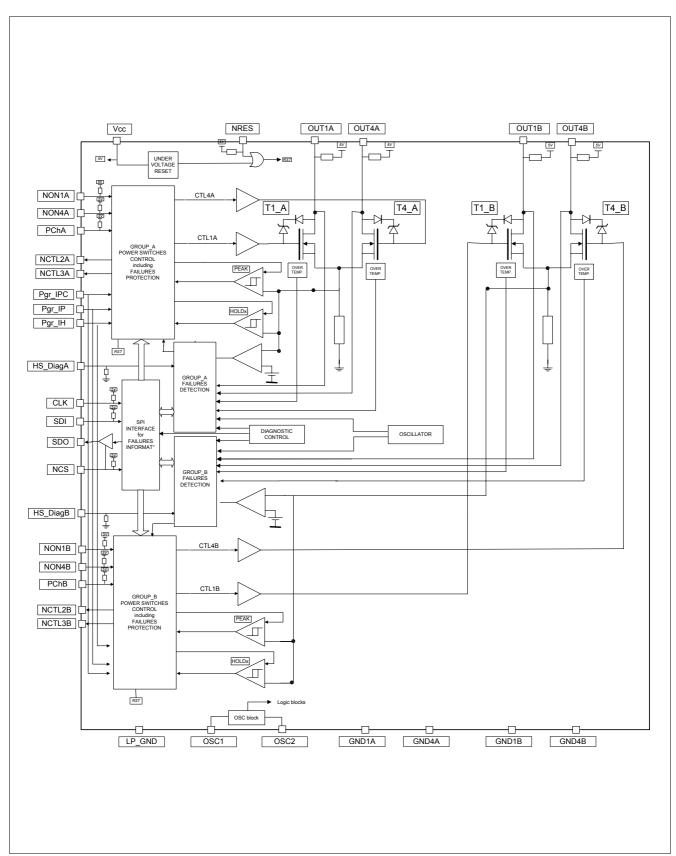

# 2 Block Diagram

Figure 2 Block Diagram

**Pin Configuration**

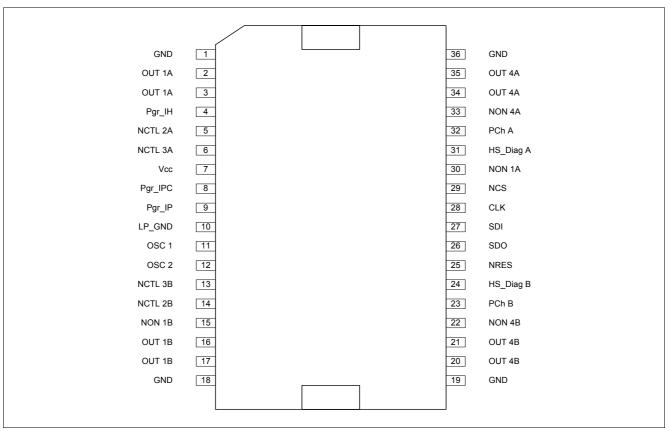

# **3** Pin Configuration

## 3.1 Pin Assignment

Figure 3 Pin Configuration P-DSO-36

# TLE6270R Quad Low Side Injector Driver

**Pin Configuration**

## 3.2 Pin Definitions and Functions

| Pin | Symbol       | Function                                    |

|-----|--------------|---------------------------------------------|

| 7   | $V_{\sf CC}$ | 5 V Power Supply                            |

| 10  | LPGND        | Low Power Ground                            |

| 1   | GND          | High Power Ground                           |

| 18  | GND          | High Power Ground                           |

| 19  | GND          | High Power Ground                           |

| 36  | GND          | High Power Ground                           |

| 2   | OUT1A        | OUTPUT channel 1A                           |

| 3   | OUT1A        | OUTPUT channel 1A                           |

| 34  | OUT4A        | OUTPUT channel 4A                           |

| 35  | OUT4A        | OUTPUT channel 4A                           |

| 16  | OUT1B        | OUTPUT channel 1B                           |

| 17  | OUT1B        | OUTPUT channel 1B                           |

| 20  | OUT4B        | OUTPUT channel 4B                           |

| 21  | OUT4B        | OUTPUT channel 4B                           |

| 30  | NON1A        | Control input channel 1A                    |

| 33  | NON4A        | Control input channel 4A                    |

| 15  | NON1B        | Control input channel 1B                    |

| 22  | NON4B        | Control input channel 4B                    |

| 32  | PChA         | Pre-charge input group A                    |

| 23  | PChB         | Pre-charge input group B                    |

| 8   | Pgr_IPC      | IPC programming input <sup>1)</sup>         |

| 9   | Pgr_IP       | IP programming input                        |

| 4   | Pgr_IH       | IH programming input                        |

| 5   | NCTL2A       | Control output high side 2A                 |

| 6   | NCTL3A       | Control output high side 3A                 |

| 14  | NCTL2B       | Control output high side 2B                 |

| 13  | NCTL3B       | Control output high side 3B                 |

| 31  | HS_Diag A    | High side diagnostic input A                |

| 24  | HS_Diag B    | High side diagnostic input B                |

| 25  | NRES         | Reset input                                 |

| 27  | SDI          | Serial Data Input                           |

| 26  | SDO          | Serial Data Output                          |

| 28  | CLK          | Clock input for serial interface            |

| 29  | NCS          | Chip-select input                           |

| 11  | OSC1         | External resonator input                    |

| 12  | OSC2         | External resonator output                   |

|     | Case         | Note: Has to be connected to GND on the PCB |

<sup>1)</sup> If there is no pre-charge resistor this pin has to be connected to  $V_{\rm CC}$  on the PCB

**General Product Characteristics**

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings 1)

$T_J$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                                    | Symbol       | Limit Values |      | Unit | Conditions                                      |  |

|----------|----------------------------------------------|--------------|--------------|------|------|-------------------------------------------------|--|

|          |                                              |              | Min.         | Max. |      |                                                 |  |

| 4.1.1    | Supply voltage                               | $V_{\sf CC}$ | -0.3         | 7    | V    | _                                               |  |

| Outputs  | 5                                            |              |              |      | -    |                                                 |  |

| 4.1.2    | Continuous output voltage                    | $V_{OUT}$    | -1.5         | 80   | V    | _                                               |  |

| 4.1.3    | Continuous output current, one output active | $I_{OUTC}$   | -5           | 5    | А    | _                                               |  |

| 4.1.4    | Peak output current                          | $I_{OUTP}$   | -10          | 20   | Α    | see Chapter 5.5                                 |  |

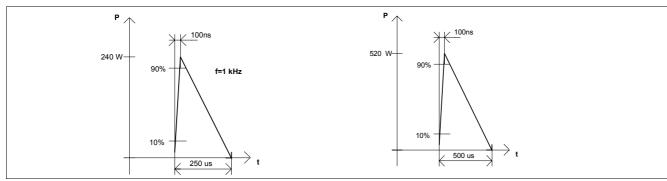

| 4.1.5    | Clamping energy repetitive pulse             | $W_{OFFr}$   | _            | 30   | mJ   | all T°, see Figure 4                            |  |

| 4.1.6    | Clamping energy single pulse                 | $W_{OFFs}$   | _            | 130  | mJ   | all T°, see Figure 4                            |  |

| Inputs a | and NCTL, SDO outputs                        | 1            | - 1          |      |      | -                                               |  |

| 4.1.7    | Continuous voltage                           | $V_{IN}$     | -0.3         | 7    | V    | _                                               |  |

| All pins | sceptibility                                 |              |              |      |      |                                                 |  |

| 4.1.8    | Electrostatic discharge                      | $V_{ESD}$    | -2000        | 2000 | V    | R = 1.5 kΩ;<br>C = 100 pF;<br>HBM <sup>2)</sup> |  |

| Operati  | ng Range                                     | 1            | •            |      | '    |                                                 |  |

| 4.1.9    | Operating Temperature Range                  | $T_{J}$      | -40          | 150  | °C   | 1)                                              |  |

| 4.1.10   | Storage Temperature Range                    | $T_{J}$      | -55          | 150  | °C   | 1)                                              |  |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

Figure 4 Energy Repetitive Pulse and Energy Single Pulse

<sup>2)</sup> ESD susceptibility, HBM according to EIA/JESD 22-A114B

#### **General Product Characteristics**

## 4.2 Functional Range

| Pos.  | Parameter                       | Symbol       | Limit Values |      | Unit | Conditions          |

|-------|---------------------------------|--------------|--------------|------|------|---------------------|

|       |                                 |              | Min.         | Max. |      |                     |

| 4.2.1 | Supply voltage                  | $V_{S}$      | 4.5          | 5.5  | V    | _                   |

| 4.2.2 | Junction temperature continuous | $T_{\rm j1}$ | -40          | 150  | °C   | Permanent operation |

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to <a href="https://www.jedec.org">www.jedec.org</a>.

| Pos.  | Parameter                      | Symbol     | Li   | Limit Values |      |     | Conditions |

|-------|--------------------------------|------------|------|--------------|------|-----|------------|

|       |                                |            | Min. | Тур.         | Max. |     |            |

| 4.3.1 | Junction to Case <sup>1)</sup> | $R_{thJC}$ | _    | _            | 2    | K/W | _          |

<sup>1)</sup> Not subject to production test, specified by design.

## TLE6270R Quad Low Side Injector Driver

**Functional Description**

## **5** Functional Description

#### 5.1 List of Functionalities

The device performs the following functionalities:

- Load control

- 4 low side power transistors driven by 4 parallel CMOS compatible inputs.

- · Output current control

- output current comparators and logic circuit to generate high side switches control signals NCTL2 and NCTL3.

- current thresholds programmable by external resistor.

- Diagnostic of defective or missing injector connections and overtemperature

- comparators and logic circuit to interpret unexpected current, voltages and HSDiag input status as short circuit or disconnection of the injector.

- 4 thermal sensors for independent overtemperature detection on the 4 channels.

- Protection

- all inputs/outputs: protection against ESD (all input and output pins)

- T1, T4, internal power transistors: protection against overvoltage and Transients (Schaffner test pulses)...

- external transistors connected via NCTL2 and CLT3: protection against overvoltage and Transients (Schaffner test pulses)...

- Reset

- external reset (reset pin)

- internal reset (undervoltage reset)

- Electro Magnetic Compatibility (EMC)

These functionalities are described in the next chapters.

#### 5.2 Load Control

Each output transistor is switched on and off by an individual control signal (NON input).

In normal operation, when NON is low, the transistor is ON and when NON is high the transistor is OFF. Also after power up, the outputs must have the status defined by the NON input.

The logic level of the input is CMOS compatible.

As there is an internal pull-up, the output transistor is switched off when the input is not connected.

It is possible to drive two separate loads simultaneously as far as they do not belong to the same bank.

Data Sheet 11 V1.3, 2008-12-23

## TLE6270R Quad Low Side Injector Driver

**Functional Description**

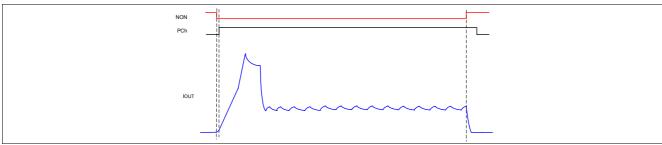

## 5.3 Output Current Control

From the output current comparators and inputs signals, a logic circuit controls the 4 current levels IPC, IP, IH and ID by commanding the high side drivers T2 and T3 via NCTL2 and NCTL3 (see **Chapter 8**). T2 and T3 are OFF when NCTL2 and NCTL3 are at high level.

- IPC level is controlled between high and low values

IPC value can be programmed through Pgr IPC pin

- IP level

the transition from IPC to IP is controlled by PCh pin

IP value can be programmed through Pgr IP pin

- IH level is controlled between high and low values the transition from IP to IH starts when peak level is reached IH value can be programmed through Pgr IH pin

- ID level is controlled between high and low values. ID is equal to IH.

the transition from IH to ID is controlled by NON1 or NON4 and PCh pins

the damp pulse is not present if there is no damp pulse command at NON1/4

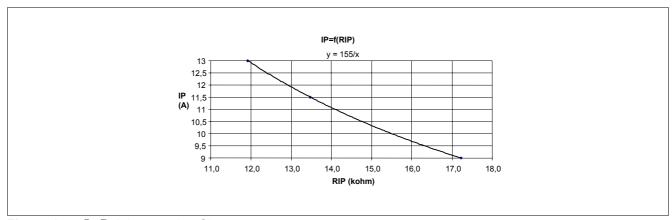

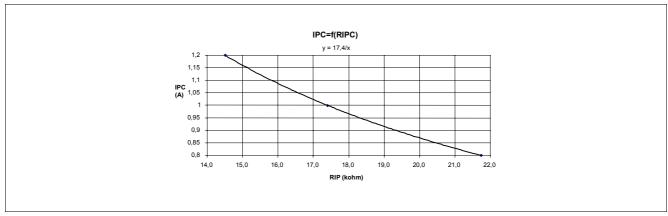

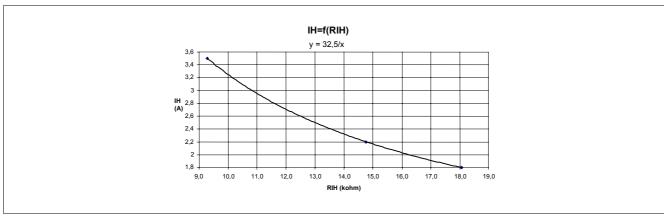

- Currents values according to programming resistors (see also graph in Chapter 7)

- $R_Pgr_IP = k_P / IP$

- R\_Pgr\_IPC =  $k_{PC}$  / IPC

- $R_pgr_IH = k_H / IH$

The theoretical Design calculation leads to  $k_{\rm P}$  = 140000 = 8 ×  $k_{\rm PC}$  = 4 ×  $k_{\rm H}$ .

Note: If  $Pgr\_IPC$  pin has no resistor and is connected to  $V_{CC}$  then there is no pre-charge and no damping. Then the Pch signal is not used and the output is controlled directly by the NON input.

## **Current Control Configurations according to NON and Pch Signals**

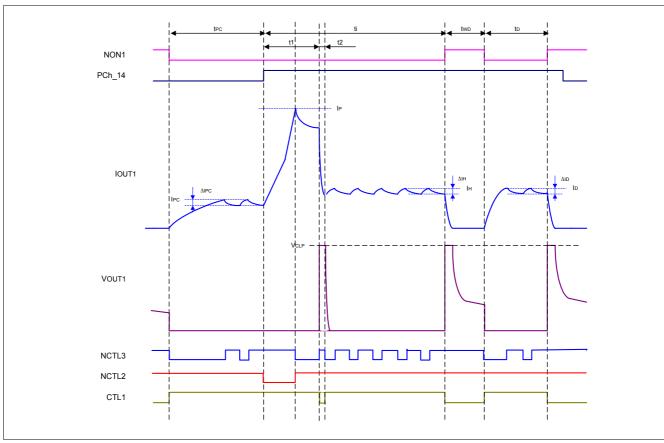

$\textbf{Figure 5} \qquad \textbf{Pre-charge} \rightarrow \textbf{Peak} \rightarrow \textbf{Hold} \rightarrow \textbf{Damp}$

Figure 6 Peak  $\rightarrow$  Hold  $\rightarrow$  Damp

Figure 7 Pre-charge  $\rightarrow$  Peak  $\rightarrow$  Hold

Figure 8 Peak - Hold

Figure 9 Peak - Hold, if Pgr\_IPC pin has no resistor and is connected to  $V_{

m CC}$

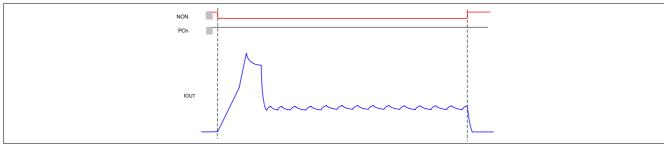

## 5.4 Diagnostic

The TLE6270R detects too high output current and too short or too long time to reach the peak current in ON state, too high output voltage in OFF state. It is also informed of too high current in the high side transistors via the HS\_Diag pin.

According to these comparator outputs and the NON signals, a logic circuit defines the failures (failure detection). When the failure is dangerous for the ECU, the engine management system, the vehicle or the car driver, all transistors T1, T2, T3, T4 are immediately switched off for protection (failure protection).

Then, for limp home and for repairing, the failures are read by the microcontroller via SPI (failure information).

Figure 10 Diagnostic Schematic

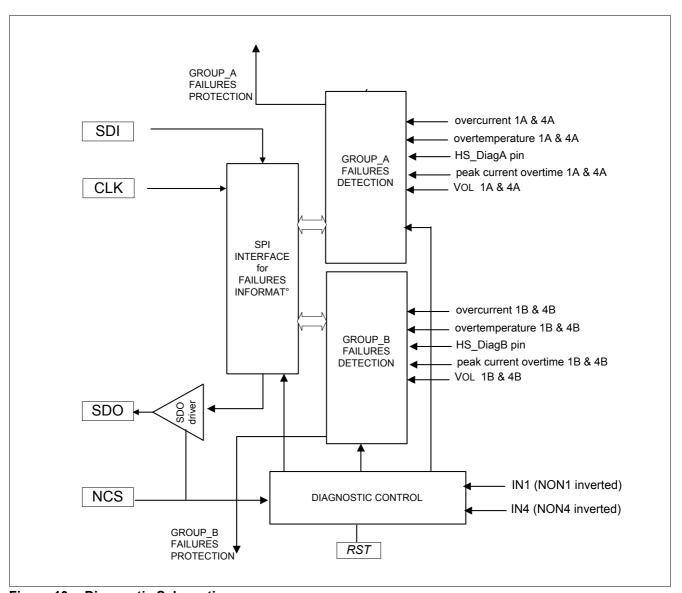

## 5.4.1 Failures Detection

For information only: Table 1 describes for each problem the detection mode and the failure detected (for exact detail, see Table 2).

Table 1 Failures Detection

| Connector<br>Point | Problem              | Failure Detection Mode                                             | Failures Detected   |

|--------------------|----------------------|--------------------------------------------------------------------|---------------------|

| HS                 | HS short to battery  | HS_Diag L → H or OUT1/4 peak current overtime                      | INJ1_SC and INJ4_SC |

|                    | HS short to ground   | $HS\_Diag L \rightarrow H \text{ or OUT1/4 peak current overtime}$ | INJ1_SC and INJ4_SC |

|                    | HS open circuit      | peak overtime and OUT1/4 OFF overvoltage                           | INJ1_OL and INJ4_OL |

| LS1                | LS1 short to battery | OUT1 overcurrent                                                   | INJ1_SC             |

|                    | T1 overtemperature   | OUT1 overtemperature                                               | INJ1_SC             |

|                    | LS1 short to ground  | $HS\_Diag L \rightarrow H \text{ or OUT1 peak current overtime}$   | INJ1_SC             |

|                    | LS1 short to HS      | OUT1 overcurrent or peak current undertime                         | INJ1_SC             |

|                    | LS1 open circuit     | peak overtime and OUT1 OFF overvoltage                             | INJ1_OL             |

| LS4                | LS4 short to battery | OUT4 overcurrent                                                   | INJ4_SC             |

|                    | T4 overtemp          | OUT4 overtemperature                                               | INJ4_SC             |

|                    | LS4 short to ground  | $HS\_Diag L \rightarrow H \text{ or OUT4 peak current overtime}$   | INJ4_SC             |

|                    | LS4 short to HS      | OUT4 overcurrent or peak current undertime                         | INJ4_SC             |

|                    | LS4 open circuit     | peak overtime and OUT4 OFF overvoltage                             | INJ4_OL             |

Figure 11 Diagram of INJ1 Failures Detection

#### **OFF State open load Functionality**

The TLE6270GR is able to detect a missing load in OFF-state using a pull-up resistor connected at the output when the both outputs of the correspoding bank are turned off.

For the correct functionality of this feature a  $5K\Omega$  resistor has to be connected in parallel with the freewheeling diode of each bank.

#### **OFF State Overvoltage Functionality:**

- Comparator:

- There is one comparator for two channels. A low level on the comparator output (called VOFF) means no failure.

- The voltage on OUT1 (resp. OUT4) is checked at the OFF state between OUT1 and OUT4 ON states (resp. between OUT4 and OUT1 ON states).

- Filter time: For OUT1 (resp. OUT4), the filter time starts:

- at H → L transition on IN1 (resp. IN4)

- if  $V_{\rm OFF}$  is high when this first filter time is finished

- at every L  $\rightarrow$  H transition on  $V_{OFF}$

#### **HS Diag Filter Functionality:**

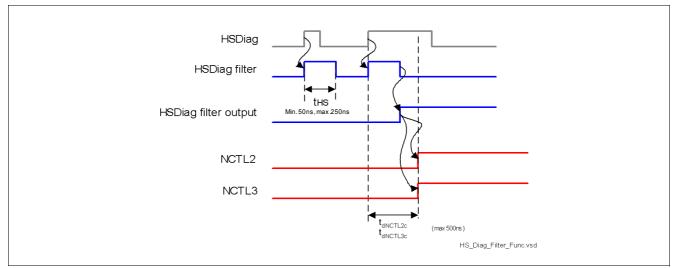

Figure 12 HS Diag Filter Functionality (optionally only one out of NCTL2 or NCTL3 can be on at the same time)

#### **Diagnostic Control Circuit Functionality:**

The SC1 (resp.4) and OL1 (resp.4) failures are transferred in the SPI on IN1 and IN4 positive edges. Just after, the X1, Y1, Z1 (resp. X4, Y4, Z4) problem memories are reset.

#### **SCn/OLn Definition Circuit Table:**

Table 2 SC/OL Definition Circuit

valid for n=1 or n=4

|    | Memor | ies | Failures |     |  |

|----|-------|-----|----------|-----|--|

| Xn | Yn    | Zn  | SCn      | OLn |  |

| 0  | 0     | 0   | 0        | 0   |  |

| 0  | 0     | 1   | 0        | 0   |  |

| 0  | 1     | 0   | 1        | 0   |  |

| 0  | 1     | 1   | 0        | 1   |  |

| 1  | 0     | 0   | 1        | 0   |  |

| 1  | 0     | 1   | 1        | 0   |  |

| 1  | 1     | 0   | 1        | 0   |  |

| 1  | 1     | 1   | 1        | 0   |  |

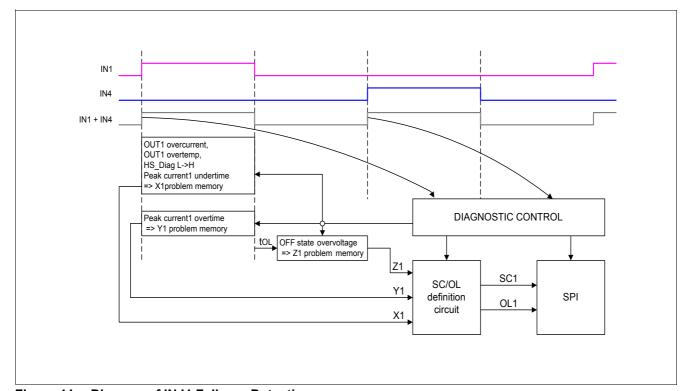

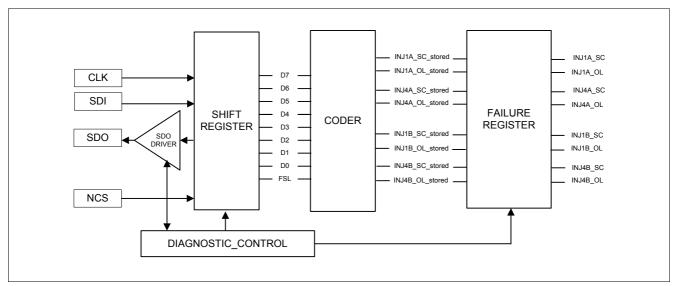

#### 5.4.2 Failures Information (via SPI)

The failures detected are communicated to the microcontroller via a Serial/Peripheral Interface (SPI) in order to minimize the pin number.

The SPI contains a failure register, a coder, a shift register, and a SDO driver:

Figure 13 Failures Information

#### **Failure Register**

Each failure is stored in an individual register (this cannot be done directly in the shift register because a failure can occur while the shift register is being read).

If the failure occurs, it remains until the SPI is read.

The failure register is cleared when the SPI is read (FR\_CLEAR signal).

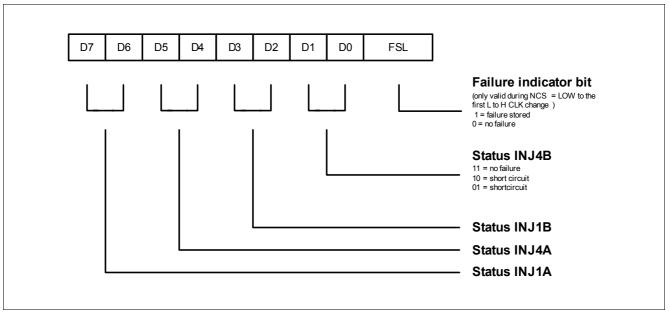

#### **Output Coder**

The SC and OL failures of the 4 outputs are coded on an 8 bit word described hereafter:

Figure 14 Output Coder

Table 3 Failures Coding and Priorities

valid for i=0 or i=2 or i=4 or i=6

|    | Failure |     | SPI Bits |    |  |  |

|----|---------|-----|----------|----|--|--|

| SC | OL      | FSL | Di+1     | Di |  |  |

| 0  | 0       | 0   | 1        | 1  |  |  |

| 0  | 1       | 1   | 0        | 1  |  |  |

| 1  | 0       | 1   | 1        | 0  |  |  |

| 1  | 1       | 1   | 1        | 0  |  |  |

The first bit of the shift register (FSL) is set to high level if there is a failure stored in the failure register.

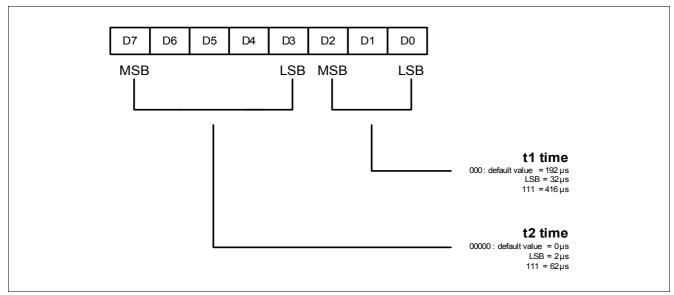

## **Input Coder**

$t_1$  and  $t_2$  times are coded on 3 bit and 5 bit respectively as described hereafter:

## TLE6270R Quad Low Side Injector Driver

**Functional Description**

Figure 15 Input Coder

Table 4 describes the time coding:

Table 4 Time Coding

|    |    | •  |    |    |    |    |    |                         |

|----|----|----|----|----|----|----|----|-------------------------|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Time                    |

| X  | Х  | Х  | Х  | Х  | 0  | 0  | 0  | t <sub>1</sub> = 192 μs |

| X  | Х  | Х  | Х  | Х  | 0  | 0  | 1  | $t_1 = 224 \ \mu s$     |

|    |    |    |    |    |    |    |    |                         |

| X  | Х  | Х  | Х  | Х  | 1  | 1  | 1  | t <sub>1</sub> = 416 μs |

| 0  | 0  | 0  | 0  | 0  | Х  | Х  | Х  | t <sub>2</sub> = 0 μs   |

| 0  | 0  | 0  | 0  | 1  | Х  | Х  | Х  | t <sub>2</sub> = 2 μs   |

|    |    |    |    |    |    |    |    |                         |

| 1  | 1  | 1  | 1  | 1  | Х  | Х  | Х  | t <sub>2</sub> = 62 μs  |

|    |    |    |    |    |    |    |    |                         |

#### **Shift Register**

The serial output of the diagnostic shift register is SDO. The serial input is SDI.

With the H/L change on NCS the first bit of the diagnostic shift register is transmitted to the SDO output.

The CLK pin clocks the diagnostic shift register. New SDO data will appear on every CLK's rising edge and new SDI data will be latched into the shift register on every CLK's falling edge.

With the first positive pulse of the CLK the failure register will be cleared by FR\_CLEAR.

There is no bus collision at a small spike at the NCS. The CLK is always LOW, while the NCS signal is changing.

#### **SPI Control**

The SPI control block monitors the data transfer from failure register to shift register and clear these register.

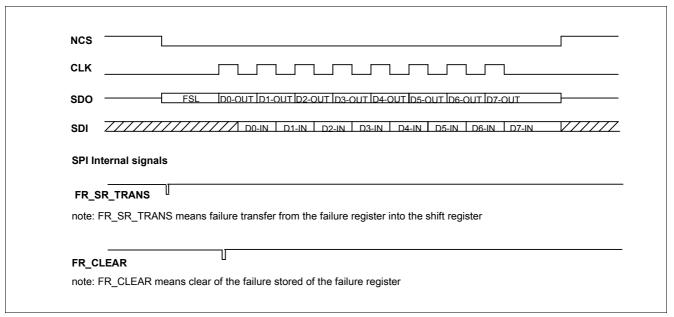

This is done with the FR\_SR\_TRANS and FR\_CLEAR signals as described in the following diagram:

# TLE6270R Quad Low Side Injector Driver

**Functional Description**

Figure 16 SPI Control

#### **SDO Driver**

The SDO driver drives the data on the diagnostic line.

SDO is tri-stated when NCS is high.

#### 5.5 Protections

### 5.5.1 All Inputs/Outputs

All pins are protected against ESD 2kV Human body model.

## 5.5.2 T1, T4 Power Transistors

· Protection against damaging failures

Table 5 Protection against Damaging Failures

| Problem detected                | Transistors switched off                                            |

|---------------------------------|---------------------------------------------------------------------|

| T1 or T4 overcurrent            | T1, T4 (internally) and T2, T3 (via NCTL2, NCTL3)                   |

| T1 or T4 overtemperature        | T1, T4 (internally) and T2, T3 (via NCTL2, NCTL3)                   |

| HS_Diag L → H                   | T1, T4 (internally) and T2, T3 (via NCTL2, NCTL3)                   |

| T1 or T4 peak current undertime | T1, T4 (internally) and T2, T3 (via NCTL2, NCTL3)                   |

| T1 or T4 peak current overtime  | T1, T4 (internally) and T2, T3 (via NCTL2, NCTL3) and $t_2$ starts. |

Note: The protection latches are reset when the NON input is at high level.

- · Protection against overvoltage

- A clamping circuit limits the output voltage to a defined value ( $V_{\rm clp}$ ) in order to avoid the breakdown of the output transistor when the solenoid load is switched off.

- · Protection against turn on due to fast voltage ramp on output.

A very fast voltage slope on the output can turn on the power transistor (capacitive effects) especially when the normal gate pull-down structure is not active (IC not supplied,  $V_{\rm CC}$  too low ...). In this case, the transistor is turned off immediately. This function is guaranteed for  $V_{\rm CC}$  between 0 and 5.5 V.

#### 5.6 Reset

There are two different reset functions:

- · Undervoltage reset

- NRES reset pin

If one or several of the following conditions are present:

- $V_{\rm CC}$  lower than  $V_{\rm CCRES}$ ,

- NRES pin at low level,

the low side T1, T4 are switched off, NCTL2 and NCTL3 set to high level, all diagnostic registers are reset and the SDO is tri-stated.

Data Sheet 21 V1.3, 2008-12-23

## **6** Electrical Characteristics

## 6.1 Supply Current

## **Electrical Characteristics: Supply Current**

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.  | Parameter                                 | Symbol                    |      | Limit Val | ues  | Unit | Conditions                                                                          |

|-------|-------------------------------------------|---------------------------|------|-----------|------|------|-------------------------------------------------------------------------------------|

|       |                                           |                           | Min. | Тур.      | Max. |      |                                                                                     |

| 6.1.1 | Standby current                           | $I_{CC\_STB}$             | _    | _         | 10   | mA   | without load                                                                        |

| 6.1.2 | Operating mode                            | $I_{\rm CC\_OM}$          | _    | _         | 20   | mA   | $I_{\text{out}}$ = 4 A on two outputs                                               |

| 6.1.3 | Operating mode and reverse output current | $I_{	exttt{CC\_OM\_REV}}$ | -    | _         | 20   | mA   | $I_{\text{outp}}$ = -1 A on one output, $I_{\text{out}}$ = 4 A on two other outputs |

## 6.2 Inputs

## Electrical Characteristics: Inputs (NONx, PChx, NRESx, NCS, CLK, SDI, HS\_Diag)

| Pos.    | Parameter                                              | Symbol             |                       | Limit Val | ues                   | Unit | Conditions                                       |  |

|---------|--------------------------------------------------------|--------------------|-----------------------|-----------|-----------------------|------|--------------------------------------------------|--|

|         |                                                        |                    | Min.                  | Тур.      | Max.                  |      |                                                  |  |

| 6.2.1   | Low level                                              | $V_{INL}$          | -0.3                  | -         | $V_{\rm CC}$          | V    | -                                                |  |

| High L  | evel                                                   |                    |                       | •         | ·                     |      |                                                  |  |

| 6.2.2   | All inputs except HS_Diag                              | $V_{INH}$          | $V_{\rm CC}$          | _         | V <sub>CC</sub> + 0.3 | V    | _                                                |  |

| 6.2.3   | HS_Diag                                                | $V_{ m HS\_DiagH}$ | $0.3 	imes V_{ m CC}$ | _         | 7                     | V    | -                                                |  |

| Hyster  | esis                                                   |                    |                       |           |                       |      |                                                  |  |

| 6.2.4   | NONx, Pchx, NRESx                                      | $V_{HYST}$         | 0.85                  | _         | _                     | V    | _                                                |  |

| 6.2.5   | NCS, CLK, SDI                                          | $V_{HYST\_SPI}$    | 0.2                   | _         | _                     | V    | _                                                |  |

| Input C | Current                                                |                    |                       | <u>'</u>  |                       |      |                                                  |  |

| 6.2.6   | All inputs except HS_Diag pull-up current              | $I_{IN}$           | -100                  | _         | -20                   | μΑ   | $0 < V_{\rm IN} < 0.9 \ V_{\rm CC}$              |  |

| 6.2.7   | HS_Diag pull-down current                              | $I_{IN}$           | 20                    | _         | 100                   | μΑ   | $500 \text{ mV} < V_{\text{IN}} < V_{\text{CC}}$ |  |

| 6.2.8   | $\Delta I_{\mathrm{IN}}$ during reverse output current | $I_{IN}$           | -200                  | -         | 200                   | μΑ   | $I_{\text{outp}}$ = -1 A on one output           |  |

## 6.3 Outputs

#### **Electrical Characteristics: Serial Data Output (SDO)**

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.  | Parameter                | Symbol     | ı                     | _imit Val | ues  | Unit | Conditions                               |

|-------|--------------------------|------------|-----------------------|-----------|------|------|------------------------------------------|

|       |                          |            | Min.                  | Тур.      | Max. |      |                                          |

| 6.3.1 | High output level        | $V_{SDOH}$ | V <sub>CC</sub> - 0.4 | _         | _    | V    | $I_{\rm SDO}$ = -2 mA                    |

| 6.3.2 | Low output level         | $V_{SDOL}$ | _                     | _         | 0.4  | V    | $I_{\rm SDO}$ = 3.2 mA                   |

| 6.3.3 | Tristate leakage current | $I_{SDOL}$ | -10                   | _         | 10   | μΑ   | NCS = HIGH;                              |

|       |                          |            |                       |           |      |      | $V_{\text{SDO}} = 0 \dots V_{\text{CC}}$ |

#### **Electrical Characteristics: Control HS Outputs (NCTLx)**

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.  | Parameter                                    | Symbol            | Limit Values        |      |      | Unit | Conditions                                      |  |

|-------|----------------------------------------------|-------------------|---------------------|------|------|------|-------------------------------------------------|--|

|       |                                              |                   | Min.                | Тур. | Max. |      |                                                 |  |

| 6.3.4 | High output level                            | $V_{NCTLH}$       | V <sub>CC</sub> - 1 | _    | _    | V    | $I_{\rm NCTL}$ = -10 mA                         |  |

| 6.3.5 | Low output level                             | $V_{NCTLL}$       | _                   | _    | 0.1  | V    | $I_{\rm NCTL}$ = 1 mA                           |  |

| 6.3.6 | Peak current at $L \rightarrow H$ transition | $I_{P\_NCTL\_LH}$ | _                   | _    | -35  | mA   | $V_{\text{NCTL}} = V_{\text{CC}} - 4 \text{ V}$ |  |

| 6.3.7 | Peak current at H → L transition             | $I_{P\_NCTL\_HL}$ | 40                  | _    | _    | mA   | $V_{\rm NCTL}$ = 4 V                            |  |

#### **Electrical Characteristics: Power Outputs (OUTx)**

| Pos.   | Parameter                                                                          | Symbol      | Li                   | imit Val | ues                | Unit | Conditions                      |

|--------|------------------------------------------------------------------------------------|-------------|----------------------|----------|--------------------|------|---------------------------------|

|        |                                                                                    |             | Min.                 | Тур.     | Max.               |      |                                 |

| 6.3.8  | ON resistance at $V_{\rm CC}$ = 5 V                                                | $R_{DSON1}$ | _                    | _        | 300                | mΩ   | 1)                              |

|        |                                                                                    |             |                      |          |                    |      | $I_{\text{out}} = 5 \text{ A};$ |

|        |                                                                                    |             |                      |          |                    |      | $V_{\rm CC}$ = 5 V;             |

|        |                                                                                    |             |                      |          |                    |      | $T_{\rm j}$ = 150 °C            |

| 6.3.9  | Clamp voltage                                                                      | $V_{CLP1}$  | 80                   | 87       | 94                 | V    | 1)                              |

|        |                                                                                    |             |                      |          |                    |      | $I_{OUT}$ = 4 A                 |

| 6.3.10 | Clamp voltage at -1 A on neighbor                                                  | $V_{CLPR}$  | _                    | _        | 94                 | V    | test current 100 mA             |

|        | output                                                                             |             |                      |          |                    |      |                                 |

| 6.3.11 | Matching clamp voltage                                                             | $V_{CLPM}$  | V <sub>CLP</sub> - 7 | _        | V <sub>CLP</sub> + | V    | -                               |

|        |                                                                                    |             |                      |          | 1                  |      |                                 |

| 6.3.12 | Leakage current                                                                    | $I_{OUTL}$  | _                    | _        | 10                 | μΑ   | $V_{OUT}$ = 18 V                |

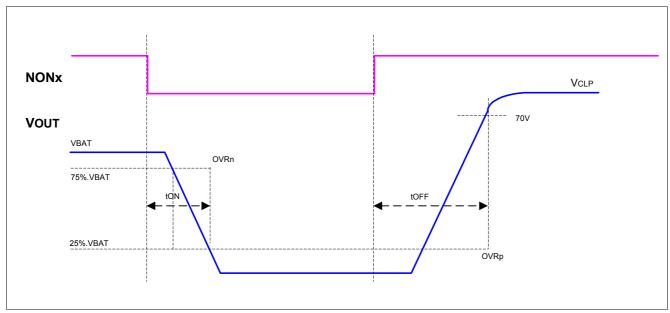

| 6.3.13 | Neg. output voltage ramp                                                           | $O_{VRn}$   | _                    | 20       | 100                | V/μs | see Chapter 7.2                 |

|        | $(75\% \times V_{\text{bat}} \dots 25\% \times V_{\text{bat}}, \text{ inductive})$ |             |                      |          |                    |      | 1)2)                            |

|        | load)                                                                              |             |                      |          |                    |      |                                 |

| 6.3.14 | Pos. output voltage ramp                                                           | $O_{VRp}$   | _                    | 100      | 200                | V/μs | see Chapter 7.2                 |

|        | (25% $\times$ $V_{\rm bat}$ 70 V, inductive load)                                  |             |                      |          |                    |      | 1)2)3)                          |

# TLE6270R Quad Low Side Injector Driver

**Electrical Characteristics**

### Electrical Characteristics: Power Outputs (OUTx) (cont'd)

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                                   | Symbol            | L    | imit Val | ues  | Unit | Conditions      |

|--------|-----------------------------------------------------------------------------|-------------------|------|----------|------|------|-----------------|

|        |                                                                             |                   | Min. | Тур.     | Max. |      |                 |

| 6.3.15 | Turn ON delay (NON 50%; $V_{\rm out}$ = 25% × $V_{\rm bat}$ inductive load) | td <sub>ON</sub>  |      |          | 1.5  | μS   | see Chapter 7.2 |

| 6.3.16 | Turn OFF delay (NON 50%; $V_{\rm out}$ = 70 V, inductive load)              | td <sub>OFF</sub> |      |          | 1.5  | μs   | see Chapter 7.2 |

- 1) Characteristics tested in different conditions than the specification and guaranteed by correlation.

- 2) Measured with resistive load.

- 3) The design is optimized for low EM emissions (no clamp overshoot).

## **Electrical Characteristics: Power Outputs Reverse Diode**

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter            | Symbol    | Limit Values |      |      | Unit | Conditions                                   |

|--------|----------------------|-----------|--------------|------|------|------|----------------------------------------------|

|        |                      |           | Min.         | Тур. | Max. |      |                                              |

| 6.3.17 | Reverse voltage drop | $V_{RDa}$ | 8.0          | _    | 1.5  | V    | for $I_{\text{out}}$ = -5.0 A (200 µs pulse) |

| 6.3.18 | Reverse voltage drop | $V_{RDb}$ | 0.6          | _    | 1.5  | V    | for $I_{\text{out}}$ = -2.5 A (200 µs pulse) |

Data Sheet 24 V1.3, 2008-12-23

#### 6.4 Current Control

## Electrical Characteristics: Current Control<sup>1)</sup>

| Pos.                 | Parameter                                    | Symbol                         | Li                 | mit Valu          | ies      | Unit | Conditions                               |

|----------------------|----------------------------------------------|--------------------------------|--------------------|-------------------|----------|------|------------------------------------------|

|                      |                                              |                                | Min.               | Тур.              | Max.     |      |                                          |

| I <sub>P</sub> Curre | ent (with $R_{\rm IP}$ = 13.5 k $\Omega$ )   |                                |                    |                   |          |      |                                          |

| 6.4.1                | Absolute value at -40 °C                     | $I_{P\_C}$                     | 8.5                | _                 | 13.0     | Α    | $I_{P} = k_{P} / R_{IP}$                 |

| 6.4.2                | Absolute value at 25 °C and 125 °C           |                                | 10                 | _                 | 13.0     | Α    | see Chapter 7.1                          |

| 6.4.3                | Matching at -40/25 °C                        | $I_{PX}$ - $I_{PY}$ C          | -17% ×             | _                 | +17%×    |      | _                                        |

|                      |                                              |                                | $I_{P}$            |                   | $I_{P}$  |      |                                          |

| 6.4.4                | Matching at 125 °C                           | $I_{PX}$ -                     | -13% ×             | _                 | +13%×    |      | _                                        |

|                      |                                              | $I_{PY\_RH}$                   | $I_{P}$            |                   | $I_{P}$  |      |                                          |

| 6.4.5                | Matching temp drift                          | $\Delta(I_{PX}\text{-}I_{PY})$ | -2% ×              | _                 | +2% ×    |      | 2)                                       |

|                      |                                              |                                | $I_{P}$            |                   | $I_{P}$  |      |                                          |

| $I_{H}$ Curr         | ent (with $R_{\rm IH}$ = 14.8 k $\Omega$ )   |                                |                    |                   |          |      |                                          |

| 6.4.6                | Absolute value at -40 °C                     | $I_{H\_C}$                     | 1.4                | _                 | 2.6      | Α    | $I_{\rm H}$ = $k_{\rm H}$ / $R_{\rm IH}$ |

| 6.4.7                | Absolute value at 25 °C and 125 °C           | $I_{H\_RH}$                    | 1.8                | _                 | 2.8      | Α    | see Chapter 7.1                          |

| 6.4.8                | Static hysteresis                            | $\Delta I_{H2}$                | $7\% \times I_{H}$ | _                 | 17% ×    |      | _                                        |

|                      |                                              |                                |                    |                   | $I_{H}$  |      |                                          |

| 6.4.9                | Matching at -40/25 °C                        | $I_{HX}$ - $I_{HY}$ C          | -17% ×             | _                 | +17%×    |      | _                                        |

|                      |                                              | _                              | $I_{H}$            |                   | $I_{H}$  |      |                                          |

| 6.4.10               | Matching at 125 °C                           | $I_{HX}$ -                     | -13% ×             | _                 | +13%×    |      | _                                        |

|                      |                                              | $I_{HY\_RH}$                   | $I_{H}$            |                   | $I_{H}$  |      |                                          |

| 6.4.11               | Matching temp drift                          | $\Delta (I_{HX}$ -             | -4% ×              | _                 | +4% ×    |      | 2)                                       |

|                      |                                              | $I_{HY}$ )                     | $I_{H}$            |                   | $I_{H}$  |      |                                          |

| $I_{PC}$ Cur         | rent (with $R_{\rm IPC}$ = 17.4 k $\Omega$ ) |                                |                    |                   |          |      |                                          |

| 6.4.12               | Absolute value at -40 °C                     | $I_{PC\_C}$                    | 0.6                | _                 | 1.25     | Α    | $I_{PC} = k_{PC} / R_{IPC}$              |

| 6.4.13               | Absolute value at 25 °C and 125 °C           | $I_{PC\_RH}$                   | 0.7                | _                 | 1.25     | Α    | see Chapter 7.1                          |

| 6.4.14               | Static hysteresis                            | $\Delta I_{PC2}$               | 7% ×               | 12.5%             | 15% ×    |      | _                                        |

|                      |                                              |                                | $I_{PC}$           | $	imes I_{ m PC}$ | $I_{PC}$ |      |                                          |

| 6.4.15               | Matching at -40/25 °C                        | $I_{PCX}$ -                    | -17% ×             | -                 | +17%×    |      | _                                        |

|                      |                                              | $I_{PCY\_C}$                   | $I_{PC}$           |                   | $I_{PC}$ |      |                                          |

| 6.4.16               | Matching at 125 °C                           | $I_{PCX}$ -                    | -13% ×             | _                 | +13%×    |      | _                                        |

|                      |                                              | $I_{PCY\_RH}$                  | $I_{PC}$           |                   | $I_{PC}$ |      |                                          |

| 6.4.17               | Matching temp drift                          | $\Delta (I_{PCX}$ -            | -4% ×              | _                 | +4% ×    |      | 2)                                       |

|                      |                                              | $I_{PCY}$ )                    | $I_{PC}$           |                   | $I_{PC}$ |      |                                          |

<sup>1)</sup> No reverse current on any outputs are allowed. External measures against reverse current must be applied.

<sup>2)</sup> Parameter specified by design, not subject to production test.

## 6.5 Current Control Timings

**Electrical Characteristics: Current Control Timings** (Load capacitor at NCTLx = 100 pF)

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.  | Parameter                                                                       | Symbol               | 1    | Limit Val | ues  | Unit | Conditions |

|-------|---------------------------------------------------------------------------------|----------------------|------|-----------|------|------|------------|

|       |                                                                                 |                      | Min. | Тур.      | Max. |      |            |

| NCTL2 | 2 Current Control Delay                                                         | "                    |      | "         |      |      | -          |

| 6.5.1 | delay from Pch14 50% $\times$ $V_{\rm CC}$ to NCTL2 50% $\times$ $V_{\rm CC}$   | td <sub>NCTL2a</sub> | _    | _         | 200  | ns   | -          |

| 6.5.2 | delay from HS_diag 50% $\times$ $V_{\rm CC}$ to NCTL2 50% $\times$ $V_{\rm CC}$ | td <sub>NCTL2c</sub> | _    | _         | 500  | ns   | -          |

| NCTL3 | Current Control Delay                                                           |                      |      |           |      |      |            |

| 6.5.3 | delay from HS_diag 50% $\times$ $V_{\rm CC}$ to NCTL3 50% $\times$ $V_{\rm CC}$ | td <sub>NCTL3c</sub> | _    | -         | 500  | ns   | _          |

## 6.6 Diagnostic and Protections

#### **Electrical Characteristics: Diagnostic and Protections**

| Pos.   | Parameter                                                                                                        | Symbol         | L                            | imit Valu          | Unit               | Conditions |      |

|--------|------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|--------------------|--------------------|------------|------|

|        |                                                                                                                  |                | Min.                         | Тур.               | Max.               |            |      |

| 6.6.1  | Overcurrent threshold                                                                                            | $I_{OFF}$      | 1.18 × <i>I</i> <sub>P</sub> | $1.4 \times I_{P}$ | 1.62 × $I_{\rm P}$ | А          | 1)   |

| 6.6.2  | Overtemperature threshold                                                                                        | $T_{OFF}$      | 155                          | _                  | 185                | °C         | 2)3) |

| 6.6.3  | HS diag input: filter and setup time                                                                             | $t_{HS}$       | 50                           | _                  | 250                | ns         | _    |

| 6.6.4  | Overcurrent / Overtemperature<br>Shutdown filter and delay time                                                  | $t_{OFF}$      | 8                            | _                  | 18                 | μS         | 1)   |

| 6.6.5  | Pull-up resistor                                                                                                 | $R_{PULL-UP}$  | 40                           | _                  | 150                | kΩ         | _    |

| 6.6.6  | OFF state overvoltage threshold                                                                                  | $V_{OL}$       | $V_{\rm CC}$                 | _                  | $V_{\rm CC}$       | V          | _    |

| 6.6.7  | OFF state overvoltage filter and delay time                                                                      | $t_{OL}$       | 3.5                          | _                  | 4.5                | ms         | _    |

| 6.6.8  | Peak current overtime threshold                                                                                  | $t_{Pmax}$     | _                            | $t_1$              | _                  | μS         | _    |

| 6.6.9  | Peak current undertime threshold                                                                                 | $t_{Pmin}$     | 10                           | _                  | 60                 | μS         | _    |

| 6.6.10 | $V_{ m CC}$ undervoltage                                                                                         | $V_{CCRES}$    | 3.35                         | _                  | 3.95               | ٧          | _    |

| 6.6.11 | Undervoltage protection Max ON-time after a output voltage ramp from: 0 V to 25 V at $V_{\rm CC}$ = 0 V to 5.5 V | $t_{\sf rpON}$ | _                            | _                  | 100                | μs         | -    |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Characteristics tested at wafer level only (with special testpads), not on packaged parts.

<sup>3)</sup> Characteristics tested in different conditions than the specification and guaranteed by correlation.

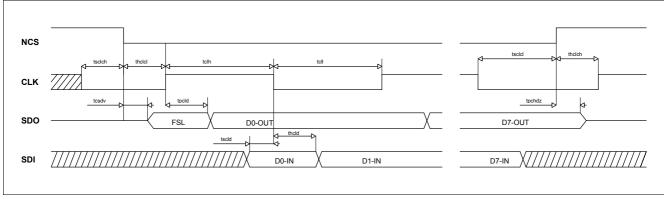

## 6.7 SPI Timings

Electrical Characteristics: SPI Timings (see Figure 17), Load capacitor at SDO = 100 pF

| Pos.   | Parameter                                                        | Symbol             |      | Limit Val | ues  | Unit | Conditions           |

|--------|------------------------------------------------------------------|--------------------|------|-----------|------|------|----------------------|

|        |                                                                  |                    | Min. | Тур.      | Max. |      |                      |

| 6.7.1  | Clock frequency (50% duty cycle)                                 | $f_{CLK}$          | _    | _         | 3    | MHz  | _                    |

| 6.7.2  | Minimum time CLK = HIGH                                          | $t_{CLH}$          | 100  | _         | _    | ns   | _                    |

| 6.7.3  | Minimum time CLK = LOW                                           | $t_{CLL}$          | 100  | _         | _    | ns   | _                    |

| 6.7.4  | Propagation delay CLK to data at SDO valid                       | $t_{PCLD}$         | _    | _         | 100  | ns   | 1)                   |

| 6.7.5  | NCS = LOW to data at SDO valid                                   | $t_{CSDV}$         | _    | _         | 100  | ns   | 1)                   |

| 6.7.6  | CLK low before NCS low<br>(setup time CLK to NCS change<br>H/L)  | t <sub>SCLCH</sub> | 100  | -         | -    | ns   | -                    |

| 6.7.7  | CLK change L/H after NCS = low                                   | $t_{HCLCL}$        | 100  | _         | _    | ns   | _                    |

| 6.7.8  | SDI input setup time<br>(CLK change H/L after SDI data<br>valid) | $t_{\sf SCLD}$     | 20   | -         | -    | ns   | -                    |

| 6.7.9  | SDI input hold time<br>(SDI data hold after CLK change<br>H/L)   | $t_{HCLD}$         | 20   | -         | -    | ns   | -                    |

| 6.7.10 | CLK low before NCS high                                          | $t_{\sf SCLCL}$    | 150  | _         | _    | ns   | _                    |

| 6.7.11 | CLK high after NCS high                                          | $t_{HCLCH}$        | 150  | _         | _    | ns   | _                    |

| 6.7.12 | NCS L/H to output data float                                     | $t_{PCHDZ}$        | _    | _         | 100  | ns   | 1)                   |

| 6.7.13 | Capacitance at SDI, SDO, CLK, NCS                                | $C_{x}$            | -    | -         | 15   | pF   | 1) Ceramic Capacitor |

| 6.7.14 | NCS filter time (pulses $\leq t_{\text{fNCS}}$ will be ignored)  | $t_{fNCS}$         | 10   | _         | 40   | ns   | 1)                   |

<sup>1)</sup> Not subject to production test, specified by design

Figure 17 SPI Timings

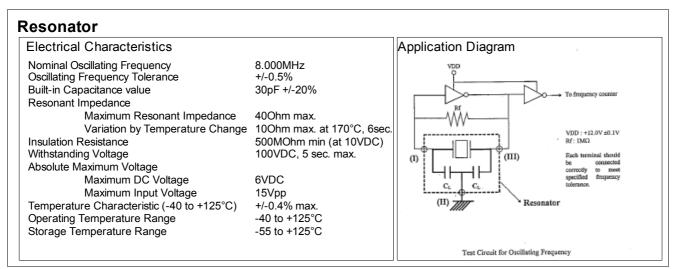

#### **Electrical Characteristics: Internal Clock**

(see SMD ceramic resonator specification n° S108 058 007 / 65 92 36.20.89, Figure 18)

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                    | Symbol               | Limit Values |      |      | Unit         | Conditions |

|--------|------------------------------|----------------------|--------------|------|------|--------------|------------|

|        |                              |                      | Min.         | Тур. | Max. |              |            |

| 6.7.15 | External resonator frequency | $f_{ m osc}$         | _            | 8    | _    | MHz          | _          |

| 6.7.16 | Internal frequency tolerance | $\Delta f_{\rm OSC}$ | -3%          | _    | +3%  | $f_{ m osc}$ | _          |

#### **Electrical Characteristics: Programmable Timings**

$V_{\rm CC}$  = 4.5 V to 5.5 V,  $T_{\rm CASE}$  = -40 °C to +125 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.                | Parameter                                  | Symbol        | Limit Values |      |      | Unit | Conditions      |

|---------------------|--------------------------------------------|---------------|--------------|------|------|------|-----------------|

|                     |                                            |               | Min.         | Тур. | Max. |      |                 |

| t <sub>1</sub> Time |                                            | -             | - 1          |      |      |      |                 |

| 6.7.17              | Number of coding bit via SPI               |               | _            | 3    | _    |      | _               |

| 6.7.18              | t <sub>1</sub> default value               | lue t1_0 – 19 |              | 192  | _    | μs   | (0, 0, 0)       |

| 6.7.19              | t <sub>1</sub> LSB (Least Significant Bit) | t1_lsb        | _            | 32   | _    | μs   | _               |

| 6.7.20              | t <sub>1</sub> max value                   | t1_max        | _            | 416  | _    | μs   | (1, 1, 1)       |

| t <sub>2</sub> Time |                                            |               |              |      |      |      |                 |

| 6.7.21              | Number of coding bit via SPI               |               | _            | 5    | _    |      | _               |

| 6.7.22              | t <sub>2</sub> default value               | t2_0          | _            | 0    | _    | μs   | (0, 0, 0, 0, 0) |

| 6.7.23              | t <sub>2</sub> LSB (Least Significant Bit) | t2_lsb        | _            | 2    | _    | μS   | _               |

| 6.7.24              | t <sub>2</sub> max value                   | t2_max        | _            | 62   | _    | μs   | (1, 1, 1, 1, 1) |

Attention: To avoid any unknown logic state,  $t_1$  and  $t_2$  values must be latched at the end of  $t_2$  time. Moreover, one latch is needed for each group (A and B) for overlapping reasons. At last, as  $t_1$  and  $t_2$  can be whenever changed,  $t_1$  and  $t_2$  should be stored in TLE6270R to release the SPI bus prior to being taken into account by the internal counters.

Figure 18 Application Hint: Example of Resonator

**Diagrams**

# 7 Diagrams

## 7.1 Typical Laws

Figure 19  $I_P(R_{IP})$  (temp = 25 °C)

Figure 20  $I_{PC}(R_{IPC})$  (temp = 25 °C)

Figure 21  $I_{H}(R_{IH})$  (temp = 25 °C)

**Diagrams**

# 7.2 Output Timings Diagram

Figure 22 Output Timing

**Application Information**

## 8 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

## 8.1 Principle Diagram of Injection System

Figure 23 Application Diagram

Note: All values mentioned are typical values.

Note: In order to program different t1 and t2 times the resonator frequency could be adjusted

**Application Information**

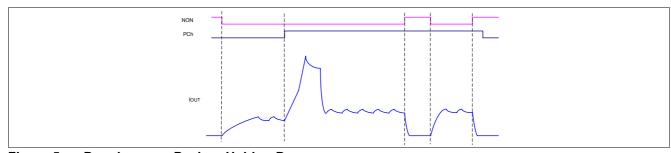

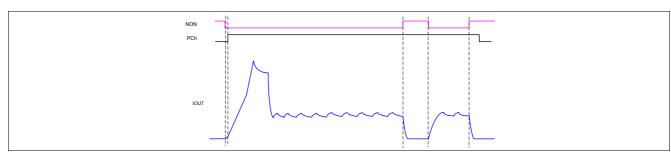

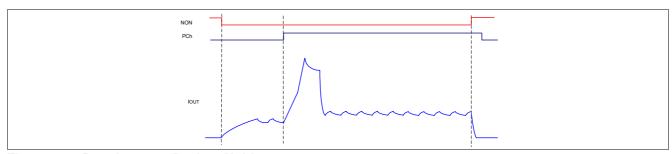

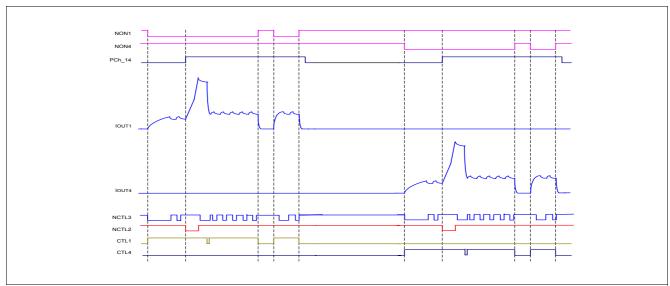

## 8.2 Typical Waveform Diagrams for One and Two Outputs Control

Figure 24 Waveform Diagram for One Output Control

- $t_{\rm pc}$  is typically 1 ms. It can be set to 100 ns minimum.

- $t_{wd}$  is typically 200  $\mu$ s.

- $t_d$  is typically 150  $\mu$ s.

Figure 25 Waveform Diagram for Two Outputs Control

Note: For each group (A or B), there is no overlapping between the channels 1 and 4.

**Package Outlines**

## 9 Package Outlines

Figure 26 P-DSO-36 (Plastic Dual Small Outline Package)

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

**Revision History**

# 10 Revision History

| Version | Date       | Changes                                                      |

|---------|------------|--------------------------------------------------------------|

| 1.3     | 2008-10-22 | Updated data sheet to newest template revision               |

|         |            | Figure 1: changed                                            |

|         |            | Chapter 5.2: added details                                   |

|         |            | Chapter 5.4.1: added paragraph regarding open load detection |

|         |            | Table 2: modified                                            |

|         |            | Table 3: modified                                            |

|         |            | Figure 15: modified                                          |

|         |            | Table 4: modified                                            |

|         |            | Chapter 8: application information chapter moved             |

|         |            | Figure 23: changed and second note added                     |

|         |            | All pages: editorial changes                                 |

| 1.1     | 2008-08-25 | Initial version of RoHS-compliant derivate of TLE6270R       |

|         |            | Datasheet converted to green                                 |

| 0.31    | 2007-01-30 | Updated Product Summary Page                                 |

|         |            | Parameter 4.1.3 removed                                      |

| 0.1     | 2006-05-06 | release for internal correction loop                         |

| 0.1a    | 2006.05.30 | corrections after internal correction loop                   |

| 0.2     | 2006-06    | release Target Datasheet                                     |

Edition 2008-12-23

Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.