# Rad Hard and SEE Hard 12A Synchronous Buck Regulator with Multi-Phase Current Sharing

#### ISL70002SEH

The ISL70002SEH is a radiation hardened and SEE hardened high efficiency monolithic synchronous buck regulator with integrated MOSFETs. This single chip power solution operates over an input voltage range of 3V to 5.5V and provides a tightly regulated output voltage that is externally adjustable from 0.8V to ~85% of the input voltage. Output load current capacity is 12A for  $T_J \leq +150\,^{\circ}\text{C}$ . Two ISL70002SEH devices configured to current share can provide 19A total output current, assuming  $\pm 27\%$  worst-case current share accuracy.

The ISL70002SEH utilizes peak current-mode control with integrated error amp compensation and pin selectable slope compensation. Switching frequency is also pin selectable to either 1MHz or 500kHz. Two ISL70002SEH devices can be synchronized 180° out-of-phase to reduce input RMS ripple current.

High integration makes the ISL70002SEH an ideal choice to power small form factor applications. Two devices can be synchronized to provide a complete power solution for large scale digital ICs, like field programmable gate arrays (FPGAs), that require separate core and I/O voltages.

### **Applications**

- FPGA, CPLD, DSP, CPU Core and I/O Voltages

- · Low-Voltage, High-Density Distributed Power Systems

#### **Features**

- DLA SMD#5962-12202

- 12A Output Current for a Single Device (at T<sub>J</sub> = +150°C)

- 19A Output Current for Two Paralleled Devices

- 1MHz or 500kHz Switching Frequency

- · 3V to 5.5V Supply Voltage Range

- ±1% Ref. Voltage (Line, Load, Temp. & Rad.)

- · Pre-Biased Load Compatible

- Redundancy/Junction Isolation: Exceptional SET Performance

- · Excellent Transient Response

- High Efficiency > 90%

- Two ISL70002SEH Synchronization, Inverted-Phase

- Comparator Input for Enable and Power-Good

- · Adjustable Analog Soft-Start

- Input Undervoltage, Output Undervoltage and Adjustable Output Overcurrent Protection

- QML Qualified per MIL-PRF-38535

- Full Mil-Temp Range Operation (-55°C to +125°C)

- Radiation Environment

- SEE Hardness

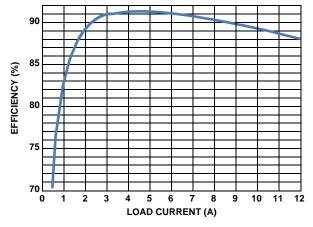

FIGURE 1. EFFICIENCY 5V INPUT TO 2.5V OUTPUT,  $T_{\Delta} = +25$  °C

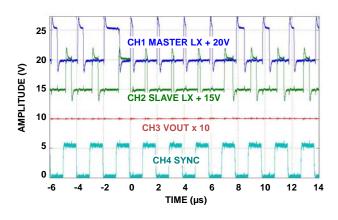

FIGURE 2. 2-PHASE SET PERFORMANCE at 86.4MeV/mg/cm<sup>2</sup>

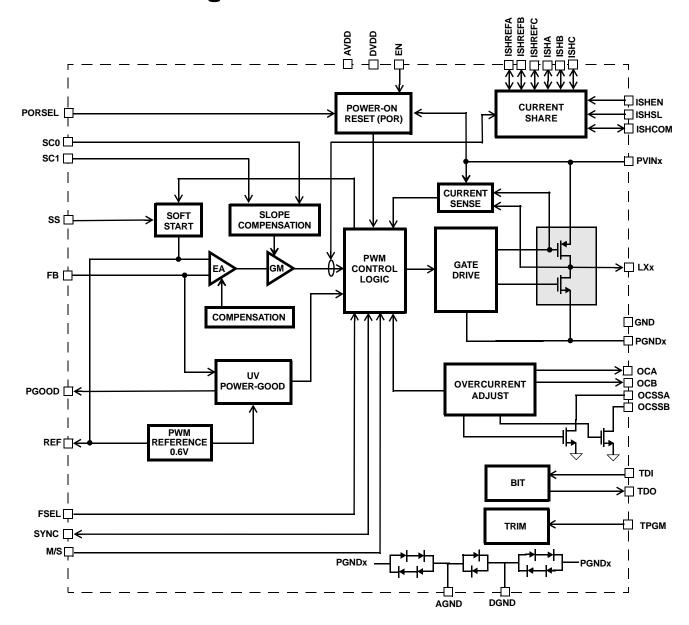

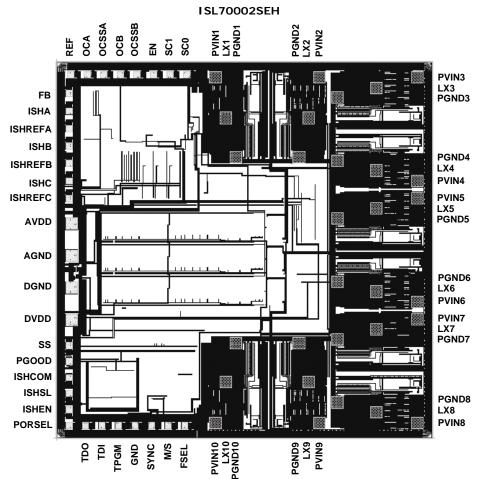

### **Functional Block Diagram**

### **Ordering Information**

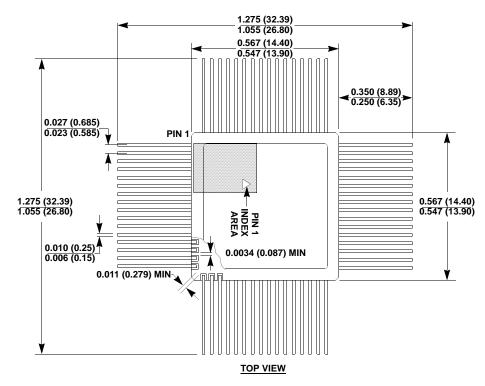

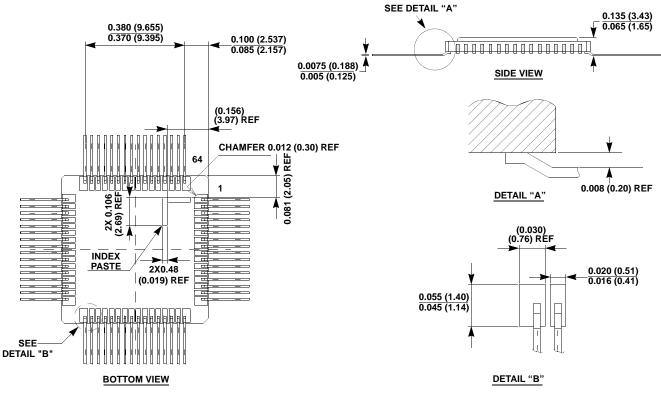

| ORDERING<br>NUMBER  | PART NUMBER<br>(Notes 1, 2) | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|---------------------|-----------------------------|---------------------|-----------------------------|----------------|

| 5962R1220201VXC     | ISL70002SEHVF               | -55 to +125         | 64 Ld CQFP                  | R64.A          |

| 5962R1220201V9A     | ISL70002SEHVX               | -55 to +125         | Die                         |                |

| ISL70002SEHF/PROTO  | ISL70002SEHF/PROTO          | -55 to +125         | 64 Ld CQFP                  | R64.A          |

| ISL70002SEHX/SAMPLE | ISL70002SEHX/SAMPLE         | -55 to +125         | Die                         |                |

| ISL70002SEHEVAL1Z   | Evaluation Board            |                     |                             |                |

#### NOTE:

- 1. These Intersil Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL70002SEH</u>. For more information on MSL please see techbrief <u>TB363</u>.

# **Pin Configuration**

### **Pin Descriptions**

| PIN NUMBER | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FB       | This pin is the voltage feedback input to the internal error amplifier. Connect a resistor from FB to VOUT and from FB to AGND to adjust the output voltage in accordance with Equation 1:                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            |          | $V_{OUT} = V_{REF} \cdot [1 + (R_T/R_B)] $ (EQ. 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |          | Where:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |          | V <sub>OUT</sub> = Output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |          | V <sub>REF</sub> = Reference voltage (0.6V typical)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            |          | $R_T$ = Top divider resistor (Must be 1k $\Omega$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            |          | R <sub>B</sub> = Bottom divider resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|            |          | The top divider resistor must be $1$ k $\Omega$ to mitigate SEE. Connect a 4.7nF ceramic capacitor across RT to mitigate SEE and to improve stability margins.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |          | If using current share, tie FB of the Master to FB of the Slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2, 4, 6    | ISHA/B/C | If configured as a current share Master (ISHSL = DGND, ISHEN = DVDD), the ISHA/B/C pins are outputs that provides a current equal to 25 times the redundant A/B/C error amp output currents plus ISHREFA/B/C (nominally 100µA each). If configured as a current share Slave (ISHSL = DVDD, ISHEN = DVDD), the ISHA/B/C pins are inputs that become the Slave's redundant A/B/C error amp output current. If using current share, tie ISHA/B/C of the Master to ISHA/B/C of the Slave. If not using current share, tie ISHA/B/C to DVDD. ISHA/B/C are tri-stated prior to a valid POR and when ISHEN = DGND. |

# Pin Descriptions (Continued)

| PIN NUMBER | PIN NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3, 5, 7    | ISHREFA/B/C | If configured as a current share Master (ISHSL = DGND, ISHEN = DVDD), the ISHREFA/B/C pins provide a reference output current equal to 100uA each. If configured as a current share Slave (ISHSL = DVDD, ISHEN = DVDD), the ISHREFA/B/C pins accept a reference input current. For a current share Slave, this input current is used together with the ISHA/B/C current to determine the Master's redundant A/B/C error amp output current. If using current share, tie ISHREFA/B/C of the MASTER to ISHREFA/B/C of the Slave. If not using current share, tie ISHREFA/B/C to DVDD. The purpose of the reference current is to reduce the impact of external noise coupling onto ISHA/B/C. ISHREFA/B/C are tri-stated prior to a valid POR and when ISHEN = DGND. |  |

| 8          | AVDD        | This pin is the bias supply input to the internal analog control circuitry. Locally filter this pin to AGND using a $1\Omega$ resistor and a $1\mu$ F ceramic capacitor. Locate both filter components as close as possible to the IC. AVDD should be the same voltage as DVDD and PVINx ( $\pm 200$ mV).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 9          | AGND        | This pin is the analog ground associated with the internal analog control circuitry. Connect this pin directly to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 10         | DGND        | This pin is the digital ground associated with the internal digital control circuitry. Connect this pin directly to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 11         | DVDD        | This pin is the bias supply input to the internal digital control circuitry. Locally filter this pin to DGND using a $1\Omega$ resistor and a $1\mu$ F ceramic capacitor. Locate both filter components as close as possible to the IC. DVDD should be the same voltage as AVDD and PVINx ( $\pm 200$ mV).                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

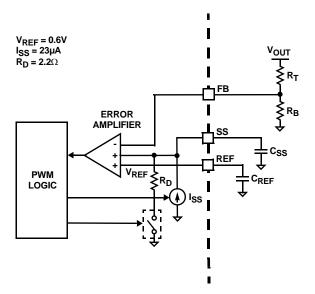

| 12         | SS          | This pin is the soft-start input. Connect a ceramic capacitor from this pin to DGND to set the soft-start output ramp time in accordance with Equation 2: $t_{SS} = C_{SS} \cdot V_{REF}/I_{SS} \tag{EQ. 2}$ Where: $t_{SS} = \text{Soft-start output ramp time}$ $C_{SS} = \text{Soft-start capacitor}$ $V_{REF} = \text{Reference voltage (0.6V typical)}$ $I_{SS} = \text{Soft-start charging current (23µA typical)}$ $\text{Soft-start time is adjustable from approximately 2ms to 200ms.}$ The range of the soft-start capacitor should be 82nF to 8.2µF, inclusive. If using current share, $C_{SS}$ of the Slave should be at least twice the $C_{SS}$ of the Master.                                                                                    |  |

| 13         | PGOOD       | This pin is the power-good output. This pin is an open drain logic output that is pulled to DGND when the output voltage is outside a $\pm 11\%$ typical regulation window. This pin can be pulled up to any voltage from 0V to 5.5V, independent of the supply voltage. A nominal $1 \text{k}\Omega$ to $10 \text{k}\Omega$ pull-up resistor is recommended. Bypass this pin to DGND with a 10nF ceramic capacitor to mitigate SEE. If using current share, tie PG00D of the Master to PG00D of the Slave.                                                                                                                                                                                                                                                       |  |

| 14         | ISHCOM      | ISHCOM is a bidirectional communication line between a current share Master and a current share Slave. If using current share, tie ISHCOM of the Master to ISHCOM of the Slave. The Master enables the Slave by resistively ( $\sim 8.5 \mathrm{k}\Omega$ ) pulling ISHCOM high. The Slave indicates an over-current fault condition to the Master by pulling ISHCOM low. To mitigate SET, connect a 47pF ceramic capacitor from ISHCOM to the PCB ground plane. If not using current share this pin should be floated or connected to the PCB ground plane. ISHCOM is tri-stated if ISHEN is low.                                                                                                                                                                |  |

| 15         | ISHSL       | This pin is a logic input that is used to configure the IC as a current share Master or Slave. Tie this pin to DVDD to configure the IC as a current share Slave. Tie this pin to the PCB ground plane to configure the IC as a current share Master, or if the current share feature is not being used.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 16         | ISHEN       | This pin is an input that enables/disables the current share feature. To enable the current share feature, tie this pin to DVDD. To disable the current share feature, tie this pin to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 17         | PORSEL      | This pin is the input for selecting the rising and falling POR (Power-On-Reset) thresholds. For a nominal 5V supply, connect this pin to DVDD. For a nominal 3.3V supply, connect this pin to DGND. For nominal supply voltages between 5V and 3.3V, connect this pin to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 18         | TD0         | This pin is the test data output of the internal BIT circuitry. Connect this pin to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 19         | TDI         | This pin is the test data input of the internal BIT circuitry. Connect this pin to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 20         | TPGM        | This pin is a trim input and is used to adjust various internal circuitry. Connect this pin to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 21         | GND         | This pin is connected to an internal metal die trace that serves as a sensitive node noise shield. Connect this pin to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

# Pin Descriptions (Continued)

| PIN NUMBER                                | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22                                        | SYNC     | When SYNC is configured as an output (clock Master Mode, M/S = DVDD), this pin drives the SYNC input of another ISL70002SEH with a square ware that is inverted (~180° out-of-phase) from the Master clockdriving the Master PWM circuits. When configured as an input (clock Slave Mode, M/S = DGND), this pin uses the SYNC output from another ISL70002SEH or an external clock to drive the clock Slave PWM circuitry. If synchronizing to an external clock, the clock must be SEE hardened and the frequency must be within the range of 400kHz to 1.2MHz. |

| 23, 28, 32, 37, 38,<br>43, 44, 49, 53, 58 | PVINx    | These pins are the power supply inputs to the corresponding internal power blocks. These pins must be connected to a common power supply rail, which must fall in the range of 3V to 5.5V. Bypass these pins directly to PGNDx with ceramic capacitors located as close as possible to the IC. PVINx should be the same voltage as DVDD and AVDD (±200mV).                                                                                                                                                                                                       |

| 24, 27, 33, 36, 39,<br>42, 45, 48, 54, 57 | LXx      | These pins are the outputs of the corresponding internal power blocks and should be connected to the output filter inductor. Internally, these pins are connected to the synchronous MOSFET power switches.                                                                                                                                                                                                                                                                                                                                                      |

| 25, 26, 34, 35, 40,<br>41, 46, 47, 55, 56 | PGNDx    | These pins are the power grounds associated with the corresponding internal power blocks. These pins also provide the ground path for the metal package lid. Connect these pins directly to the PCB ground plane. These pins should also connect to the negative terminals of the input and output capacitors. Locate the input and output capacitors as close as possible to the IC.                                                                                                                                                                            |

| 29                                        | M/S      | This pin is the clock Master/Slave input for selecting the direction of the bi-directional SYNC pin. For SYNC = Output (Master Mode), connect this pin to DVDD. For SYNC = Input (Slave Mode), connect this pin to the PCB ground plane.                                                                                                                                                                                                                                                                                                                         |

| 30                                        | FSEL     | This pin is the oscillator frequency select input. Tie this pin to DVDD to select a 1MHz nominal oscillator frequency. Tie this pin to the PCB ground plane to select a 500kHz nominal oscillator frequency.                                                                                                                                                                                                                                                                                                                                                     |

| 31, 50                                    | NC       | These are No Connect pins that are not connected to anything internally. They should be connected to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 51, 52                                    | SCO/1    | These pins are inputs that comprise a 2-bit code to select the slope compensation (SC) current ramp referred to the output as shown below.  SC1 = DVDD, SC0 = DVDD: SC = 6.6A/µs for FSEL = DGND  SC1 = DVDD, SC0 = DGND: SC = 3.3A/µs for FSEL = DGND  SC1 = DGND, SC0 = DVDD: SC = 1.6A/µs for FSEL = DGND  SC1 = DGND, SC0 = DGND: SC = 0.8A/µs for FSEL = DGND  SC1 = DVDD, SC0 = DVDD: SC = 13.4A/µs for FSEL = DVDD  SC1 = DVDD, SC0 = DGND: SC = 6.7A/µs for FSEL = DVDD                                                                                  |

|                                           |          | SC1 = DVDD; SC0 = DGND: SC = 3.4A/µs for FSEL = DVDD<br>SC1 = DGND, SC0 = DVDD: SC = 3.4A/µs for FSEL = DVDD<br>SC1 = DGND, SC0 = DGND: SC = 1.7A/µs for FSEL = DVDD                                                                                                                                                                                                                                                                                                                                                                                             |

|                                           |          | If using current share, SCO and SC1 of the Slave MUST match the Master SCO and SC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 59                                        | EN       | This pin is the enable input to the IC. This is a comparator type input with a rising threshold of 0.6V and programmable hysteresis. Driving this pin above 0.6V enables the IC. Bypass this pin to the PCB ground plane with a 10nF ceramic capacitor to mitigate SEE.                                                                                                                                                                                                                                                                                          |

| 60, 62                                    | OCSSB/A  | This pin is a switch to AGND that is active during the soft-start period. It is used to set the redundant A/B peak overcurrent limit threshold during soft-start. Connect a resistor from OCSSx to OCx in accordance with the following equation: ROCSSx 600mV / [(IOCSSx - IOCx) / 100,000] where IOCx is the desired peak overcurrent limit during normal operation and IOCSSx is the desired peak current limit threshold during soft-start.                                                                                                                  |

| 61, 63                                    | OCB/A    | This pin is a source follower output that is used to set the redundant A/B peak overcurrent limit threshold during normal operation. Connect a resistor from this pin to the PCB ground plane in accordance with the following equation: $ROCx = 600mV / (IOCx / 100,000)$ , where $IOCx$ is the desired peak current limit threshold during normal operation.                                                                                                                                                                                                   |

| 64                                        | REF      | This pin is the internal reference voltage output. Bypass this pin to the PCB ground plane with a 220nF ceramic capacitor located as close as possible to the IC. The bypass capacitor is needed to mitigate SEE. No current (sourcing or sinking) is available from this pin. If using current share, tie REF of the Master to REF of the Slave through a $10\Omega$ resistor.                                                                                                                                                                                  |

5 intersil

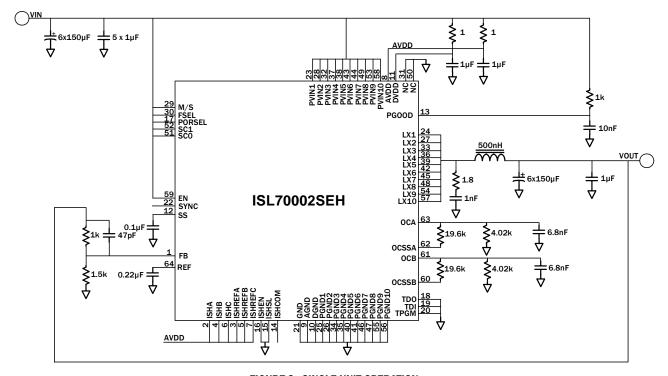

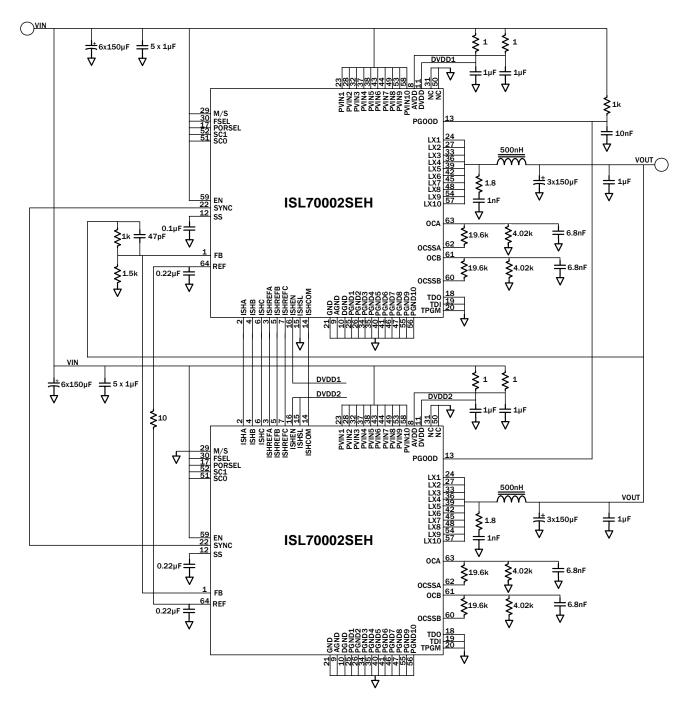

# **Typical Application Schematic**

FIGURE 3. SINGLE UNIT OPERATION

# Typical Application Schematic (Continued)

FIGURE 4. TWO PHASE OPERATION WITH CURRENT SHARING

#### Absolute Maximum Ratings (Note 3)

| AVDD                          | AGND - 0.3V to AGND + 6.2V   |

|-------------------------------|------------------------------|

| DVDD                          | DGND - 0.3V to DGND + 6.2V   |

| LXx, PVINx (Note 8)           | PGNDx - 0.3V to PGNDx + 6.2V |

| AVDD - AGND, DVDD - DGND      | PVINx - PGNDx ± 0.3V         |

| Signal pins (Note 6)          | AGND - 0.3V to AVDD + 0.3V   |

| Digital control pins (Note 7) | DGND - 0.3V to DVDD + 0.3V   |

| PG00D                         | DGND - 0.3V to DGND + 6.2V   |

| SS                            | DGND - 0.3V to DGND + 2.5V   |

#### **Thermal Information**

| Thermal Resistance             | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|--------------------------------|------------------------|------------------------|

| CQFP Package (Notes 4, 5)      | 34                     | 1.5                    |

| Operating Junction Temperature | Range                  | -55°C to +150°C        |

| Storage Temperature Range      |                        | -65°C to +150°C        |

| Pb-Free Reflow Profile         |                        | see link below         |

| http://www.intersil.com/pbfre  | e/Pb-FreeReflow.asp    |                        |

#### **Recommended Operating Conditions**

| AVDD                             | AGND + 3V to 5.5V    |

|----------------------------------|----------------------|

| DVDD                             | DGND + 3V to 5.5V    |

| PVINx                            | PGNDx + 3V to 5.5V   |

| AVDD - AGND, DVDD - DGND         | PVINx - PGNDx ± 0.1V |

| Signal pins (Note 6)             | AGND to AVDD         |

| Digital control pins (Note 7)    | DGND to DVDD         |

| REF, SS                          | Internally Set       |

| GND, TDI, TDO, TPGM              | DGND                 |

| $I_{L\chi\chi}(T_J \le +150$ °C) | 0A to 1.2A           |

| Ambient Temperature Range        | 55°C to +125°C       |

|                                  |                      |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 3. Absolute Maximum Ratings assume operation in a heavy ion environment.

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board. See Tech Brief TB379 for details.

- 5. For  $\theta_{\text{IC}}$ , the "case temp" location is the center of the package underside.

- 6. EN, FB, ISHx, ISHREFx, OCx, OCSSx, PORSEL and REF pins.

- 7. FSEL, GND, ISHCOM, ISHEN, ISHRSL, M/S, SYNC, SCO, SC1, TDI, TDO and TPGM pins.

- 8. The 6.2V absolute maximum rating must be met for a 20MHz bandwidth limited observation at the device pins. In addition, for a 600MHz bandwidth limited observation, the peak transient voltage on PVINx (measured to PGNDx) must be less than 7.1V with a duration above 6.2 V of less than 10ns, and the peak transient voltage on LXx (measured to PGNDx) must be less than 7.9V with a duration above 6.2 V of less than 10ns.

**Electrical Specifications** Unless otherwise noted,  $V_{IN} = AVDD = DVDD = PVINx = EN = FSEL = M/S = SC0 = SC1= 3V to 5.5V; GND = AGND = DGND = PGNDx = ISHx = ISHCOM = ISHEN = ISHREFx = ISHSL = TDI = TDO = TPGM = 0V; FB = 0.65V; PORSEL = <math>V_{IN}$  for 4.5V ≤  $V_{IN} \le 5.5V$  and GND for  $V_{IN} < 4.5V$ ; LXx = SYNC = Open Circuit; OCx is connected to OCSSx with a  $10k\Omega$  resistor; OCx is connected to GND with a 4.99kΩ resistor shunted by a 6.8nF capacitor; PG00D is pulled up to  $V_{IN}$  with a  $1k\Omega$  resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor;  $T_A = T_J = -55$ °C to +125°C; Post 100krad(Si). (Note 6).

| PARAMETER                                                                 | PARAMETER TEST CONDITIONS                                                                                                                                                                      |       | TYP | MAX<br>(Note 10) | UNITS |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------------------|-------|

| POWER SUPPLY                                                              |                                                                                                                                                                                                |       |     |                  |       |

| Operating Supply Current (Current Share                                   | V <sub>IN</sub> = 5.5V                                                                                                                                                                         |       | 70  | 105              | mA    |

| Disabled)                                                                 | V <sub>IN</sub> = 3.6V                                                                                                                                                                         |       | 43  | 65               | mA    |

| Standby Supply Current (Current Share                                     | V <sub>IN</sub> = 5.5V, EN = GND, ISHEN = GND                                                                                                                                                  |       | 2.5 | 6                | mA    |

| Disabled)                                                                 | V <sub>IN</sub> = 3.6V, EN = GND, ISHEN = GND                                                                                                                                                  |       | 2   | 4                | mA    |

| Operating Supply Current (Current Share<br>Enabled, Current Share Master) | V <sub>IN</sub> = ISHEN = 5.5V, ISHCOM = Open Circuit                                                                                                                                          |       | 70  | 120              | mA    |

| Operating Supply Current (Current Share<br>Enabled, Current Share Slave)  | $\begin{split} &V_{IN} = ISHEN = ISHSL = 5.5V, ISHCOM \ Pulled \ to \ V_{IN} \ with \\ &1 k\Omega, \ M/S = GND, \ ISHx = ISHREFx = -100 \mu A, \\ &SYNC = External \ 1MHz \ Clock \end{split}$ |       | 70  | 120              | mA    |

| Standby Supply Current (Current Share<br>Enabled, Current Share Slave)    | V <sub>IN</sub> = ISHEN = ISHSL = 5.5V, EN = M/S = GND,<br>SYNC = External 1MHz Clock                                                                                                          |       | 3.0 | 7                | mA    |

|                                                                           | V <sub>IN</sub> = ISHEN = ISHSL = 5.5V, M/S = GND,<br>SYNC = External 1MHz Clock, ISHCOM = GND                                                                                                 |       | 7.3 | 11               | mA    |

| OUTPUT VOLTAGE & CURRENT                                                  |                                                                                                                                                                                                | •     |     |                  | •     |

| eference Voltage                                                          |                                                                                                                                                                                                | 0.594 | 0.6 | 0.606            | ٧     |

intersil FN8264.1

**Electrical Specifications** Unless otherwise noted,  $V_{IN}$  = AVDD = DVDD = PVINx = EN = FSEL = M/S = SC0 = SC1= 3V to 5.5V; GND = AGND = DGND = PGNDx = ISHx = ISHCOM = ISHEN = ISHREFx = ISHSL = TDI = TDO = TPGM = 0V; FB = 0.65V; PORSEL =  $V_{IN}$  for 4.5V ≤  $V_{IN}$  ≤ 5.5V and GND for  $V_{IN}$  < 4.5V; LXx = SYNC = Open Circuit; OCx is connected to OCSSx with a 10kΩ resistor; OCx is connected to GND with a 4.99kΩ resistor shunted by a 6.8nF capacitor; PG00D is pulled up to  $V_{IN}$  with a 1kΩ resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor;  $T_A = T_J = -55$ °C to +125°C; Post 100krad(Si). (Note 6). (Continued)

| PARAMETER                                                                      | TEST CONDITIONS                                                                    | MIN<br>(Note 10)     | TYP | MAX<br>(Note 10) | UNITS |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------|-----|------------------|-------|

| Output Voltage Tolerance                                                       | V <sub>OUT</sub> = 0.8V to 2.5V, I <sub>OUT</sub> = 0A to 12A (Notes 11, 12)       | -2                   |     | 2                | %     |

| Error Amp Input Offset Voltage                                                 | V <sub>IN</sub> = 5.5V, V <sub>REF</sub> = 600mV, Test Mode                        |                      |     | 3                | mV    |

| Feedback (FB) Input Leakage Current                                            | V <sub>IN</sub> = 5.5V, V <sub>FB</sub> = 600mV                                    |                      |     | 1.5              | μΑ    |

| Sustained Output Current                                                       | V <sub>IN</sub> = 3V, V <sub>OUT</sub> = 1.8V, OCA = OCB = PVIN (Note 13)          | 16                   | 22  |                  | Α     |

| PWM CONTROL LOGIC                                                              |                                                                                    |                      |     |                  |       |

| Internal Oscillator Tolerance                                                  | FSEL = V <sub>IN</sub> or GND                                                      | -15                  |     | 15               | %     |

| External Oscillator Range                                                      | M/S = GND                                                                          | 0.4                  |     | 1.2              | MHz   |

| Minimum LXx On Time                                                            | V <sub>IN</sub> = 5.5V, Test Mode                                                  |                      | 200 | 275              | ns    |

| Minimum LXx Off Time                                                           | V <sub>IN</sub> = 5.5V, Test Mode                                                  |                      | 0   | 50               | ns    |

| Minimum LXx On Time                                                            | V <sub>IN</sub> = 3V, Test Mode                                                    |                      | 225 | 300              | ns    |

| Minimum LXx Off Time                                                           | V <sub>IN</sub> = 3V, Test Mode                                                    |                      | 0   | 50               | ns    |

| PORSEL, Master/Slave (M/S), SC1, SC0,                                          | Input High Threshold                                                               | V <sub>IN</sub> -0.5 | 1.3 |                  | ٧     |

| ISHSL, ISHEN, FSEL Input Voltage                                               | Input Low Threshold                                                                |                      | 1.2 | 0.5              | ٧     |

| PORSEL, Master/Slave (M/S), SC1, SC0, ISHSL, ISHEN, FSEL Input Leakage Current | V <sub>IN</sub> = 5.5V                                                             | -1                   |     | 1                | μΑ    |

| Synchronization (SYNC) Input Voltage                                           | Input High Threshold, M/S = GND                                                    | 2.3                  | 1.7 |                  | ٧     |

|                                                                                | Input Low Threshold, M/S = GND                                                     |                      | 1.5 | 1                | ٧     |

| Synchronization (SYNC) Input Leakage<br>Current                                | $V_{IN}$ = 5.5V, M/S = GND, SYNC = $V_{IN}$ or GND                                 | -1                   |     | 1                | μΑ    |

| Synchronization (SYNC) Output Voltage                                          | V <sub>IN</sub> - V <sub>OH</sub> @ I <sub>OH</sub> = -1mA                         |                      | 0.1 | 0.4              | ٧     |

|                                                                                | V <sub>0L</sub> @ I <sub>0L</sub> = 1mA                                            |                      | 0.1 | 0.4              | ٧     |

| POWER BLOCKS                                                                   |                                                                                    |                      |     |                  |       |

| Upper Device r <sub>DS(ON)</sub>                                               | V <sub>IN</sub> = 3V, 4A load, All Power Blocks in Parallel,<br>Test Mode (Note 9) |                      | 20  | 40               | mΩ    |

| Lower Device r <sub>DS(ON)</sub>                                               | V <sub>IN</sub> = 3V, 4A load, All Power Blocks in Parallel,<br>Test Mode (Note 9) |                      | 15  | 30               | mΩ    |

| LXx Output Leakage                                                             | V <sub>IN</sub> = 5.5V, EN = LXx = GND, Single LXx Output                          | -1                   |     |                  | μΑ    |

|                                                                                | V <sub>IN</sub> = LXx = 5.5V, EN = GND, Single LXx Output                          |                      |     | 10               | μΑ    |

| Deadtime (Note 12)                                                             | Within a Single Power Block or between Power Blocks                                | 2.2                  | 25  |                  | ns    |

| Efficiency (Note 12)                                                           | V <sub>IN</sub> = 3.3V, V <sub>OUT</sub> = 1.8V, I <sub>OUT</sub> = 6A, FSEL = GND |                      | 88  |                  | %     |

|                                                                                | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 2.5V, I <sub>OUT</sub> = 6A               |                      | 90  |                  | %     |

| POWER-ON RESET                                                                 |                                                                                    |                      |     |                  |       |

| VIN POR                                                                        | Rising Threshold, PORSEL = V <sub>IN</sub>                                         | 4.1                  | 4.3 | 4.45             | ٧     |

|                                                                                | Hysteresis, PORSEL = V <sub>IN</sub>                                               | 225                  | 325 | 425              | mV    |

|                                                                                | Rising Threshold, PORSEL = GND                                                     | 2.65                 | 2.8 | 2.95             | V     |

|                                                                                | Hysteresis, PORSEL = GND                                                           | 70                   | 140 | 240              | mV    |

| Enable (EN) Input Voltage                                                      | Rising/Falling Threshold                                                           | 0.56                 | 0.6 | 0.64             | ٧     |

| Enable (EN) Input Leakage Current                                              | V <sub>IN</sub> = 5.5V, EN = V <sub>IN</sub> or GND                                | -3                   |     | 3                | μA    |

**Electrical Specifications** Unless otherwise noted,  $V_{IN}$  = AVDD = DVDD = PVINx = EN = FSEL = M/S = SC0 = SC1= 3V to 5.5V; GND = AGND = DGND = PGNDx = ISHx = ISHCOM = ISHEN = ISHREFx = ISHSL = TDI = TDO = TPGM = 0V; FB = 0.65V; PORSEL =  $V_{IN}$  for 4.5V ≤  $V_{IN}$  ≤ 5.5V and GND for  $V_{IN}$  < 4.5V; LXx = SYNC = Open Circuit; OCx is connected to OCSSx with a 10kΩ resistor; OCx is connected to GND with a 4.99kΩ resistor shunted by a 6.8nF capacitor; PGOOD is pulled up to  $V_{IN}$  with a 1kΩ resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor;  $T_A = T_J = -55$ °C to +125°C; Post 100krad(Si). (Note 6). (Continued)

| PARAMETER                                | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                    | MIN<br>(Note 10) | TYP | MAX<br>(Note 10) | UNITS                |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|----------------------|

| Enable (EN) Sink Current                 | EN = 0.3V                                                                                                                                                                                                                                                                                                                                                          | 6.4              | 11  | 16.6             | μΑ                   |

| SOFT-START                               |                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  |                      |

| Soft-Start Source Current                | SS = GND                                                                                                                                                                                                                                                                                                                                                           | 20               | 23  | 27               | μΑ                   |

| Soft-Start Discharge ON-Resistance       |                                                                                                                                                                                                                                                                                                                                                                    |                  | 2.2 | 4.7              | Ω                    |

| Soft-Start Discharge Time                |                                                                                                                                                                                                                                                                                                                                                                    |                  | 256 |                  | Clock<br>Cycles      |

| POWER-GOOD SIGNAL                        |                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  | •                    |

| Rising Threshold                         | V <sub>FB</sub> as a % of V <sub>REF</sub> , Test Mode                                                                                                                                                                                                                                                                                                             | 107              | 111 | 115              | %                    |

| Rising Hysteresis                        | V <sub>FB</sub> as a % of V <sub>REF</sub> , Test Mode                                                                                                                                                                                                                                                                                                             | 2                | 3.5 | 5                | %                    |

| Falling Threshold                        | V <sub>FB</sub> as a % of V <sub>REF</sub> , Test Mode                                                                                                                                                                                                                                                                                                             | 85               | 89  | 93               | %                    |

| Falling Hysteresis                       | V <sub>FB</sub> as a % of V <sub>REF</sub> , Test Mode                                                                                                                                                                                                                                                                                                             | 2                | 3.5 | 5                | %                    |

| Power-Good Drive                         | V <sub>IN</sub> = 3V, PGOOD = 0.4V, EN = GND                                                                                                                                                                                                                                                                                                                       | 7.2              |     |                  | mA                   |

| Power-Good Leakage                       | V <sub>IN</sub> = PGOOD = 5.5V                                                                                                                                                                                                                                                                                                                                     |                  |     | 1                | μΑ                   |

| PROTECTION FEATURES                      |                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  | •                    |

| Undervoltage Monitor                     |                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  |                      |

| Undervoltage Trip Threshold              | V <sub>FB</sub> as a % of V <sub>REF</sub> , Test mode                                                                                                                                                                                                                                                                                                             | 71               | 75  | 79               | %                    |

| Undervoltage Recovery Threshold          | V <sub>FB</sub> as a % of V <sub>REF</sub> , Test mode                                                                                                                                                                                                                                                                                                             | 84               | 88  | 92               | %                    |

| Overcurrent Monitor                      |                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  | •                    |

| Overcurrent Trip Level                   | I <sub>OCx</sub> = 60μA, Test mode (Note 14)                                                                                                                                                                                                                                                                                                                       | 5.35             |     | 7.35             | Α                    |

|                                          | I <sub>OCx</sub> = 240μA, Test mode (Note 14)                                                                                                                                                                                                                                                                                                                      | 23               |     | 26               | Α                    |

| CURENT SHARE                             |                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  | •                    |

| Slave Load Current                       | $\begin{aligned} &\text{Master Load Current} = 12\text{A, V}_{\text{IN}} = 3.3\text{V, V}_{\text{OUT}} = 0.8\text{V,} \\ &\text{SC1} = \text{ISHSL} = \text{M/S} = 0, \text{SC0} = \text{ISHEN} = \text{FSEL} = 1, \\ &\text{SYNC} = 1\text{MHz External, 500nH inductor (Notes 12, 13)} \end{aligned}$                                                            | 7                | 12  | 17               | А                    |

|                                          | Master Load Current = 12A, $V_{\text{IN}}$ = 3.3V, $V_{\text{OUT}}$ = 1.8V, SC0 = ISHSL= M/S = 0, SC1 = ISHEN = FSEL = 1, SYNC = 1MHz External, 500nH inductor (Notes 12, 13)                                                                                                                                                                                      | 7                | 12  | 17               | А                    |

|                                          | $\begin{aligned} &\text{Master Load Current} = \textbf{12A},  \textbf{V}_{\text{IN}} = 5.0 \textbf{V},  \textbf{V}_{\text{OUT}} = \textbf{1.8V}, \\ &\text{SCO} = \text{ISHSL} = \textbf{M/S} = \textbf{0},  \text{SC1} = \text{ISHEN} = \text{FSEL} = \textbf{1}, \\ &\text{SYNC} = \textbf{1MHz External},  500 \text{nH inductor (Notes 12, 13)} \end{aligned}$ | 7                | 12  | 17               | А                    |

|                                          | Master Load Current = 12A, $V_{IN}$ = 5.0V, $V_{OUT}$ = 2.5V, ISHSL = M/S = 0, SC0 = SC1 = ISHEN = FSEL = 1, SYNC=1MHz External, 500nH inductor (Notes 12, 13)                                                                                                                                                                                                     | 7                | 12  | 17               | А                    |

| ISHx, ISHREFx, Tri-State Leakage Current | ent V <sub>IN</sub> = 5.5V, EN = GND                                                                                                                                                                                                                                                                                                                               |                  | 0   | 1                | μΑ                   |

| Master ISHCOM Pull-Up Resistance         | ISHCOM = -50μA                                                                                                                                                                                                                                                                                                                                                     | 6.5              | 10  | 13               | kΩ                   |

| Slave ISHCOM Input Leakage Current       | V <sub>IN</sub> = ISHSL = 5.5V                                                                                                                                                                                                                                                                                                                                     | -1               |     | 1                | μΑ                   |

| Slave ISHCOM Pull-Down Resistance        | ISHSL = V <sub>IN</sub> , EN = GND, ISHCOM = 7.2mA                                                                                                                                                                                                                                                                                                                 | 35               | 75  | 125              | Ω                    |

| Slave ISHCOM Input High Voltage          | ISHSL = V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                            | 42               | 52  | 62               | % of V <sub>IN</sub> |

| Slave ISHCOM Input Low Voltage           | ISHSL = V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                            | 26               | 36  | 46               | % of V <sub>IN</sub> |

| Slave ISHCOM Input Voltage Hysteresis    | ISHSL = V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                            | 7                | 16  | 24               | % of V <sub>IN</sub> |

**Electrical Specifications** Unless otherwise noted,  $V_{IN} = AVDD = DVDD = PVINx = EN = FSEL = M/S = SC0 = SC1= 3V to 5.5V; GND = AGND = DGND = PGNDx = ISHx = ISHCOM = ISHEN = ISHREFx = ISHSL = TDI = TDO = TPGM = 0V; FB = 0.65V; PORSEL = <math>V_{IN}$  for 4.5V ≤  $V_{IN} \le 5.5V$  and GND for  $V_{IN} < 4.5V$ ; LXx = SYNC = Open Circuit; OCx is connected to OCSSx with a  $10k\Omega$  resistor; OCx is connected to GND with a 4.99kΩ resistor shunted by a 6.8nF capacitor; PG00D is pulled up to  $V_{IN}$  with a  $1k\Omega$  resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor;  $T_A = T_I = -55$ °C to +125°C; Post 100krad(Si). (Note 6). (Continued)

| PARAMETER                   | TEST CONDITIONS                               | MIN<br>(Note 10)      | TYP  | MAX<br>(Note 10) | UNITS |

|-----------------------------|-----------------------------------------------|-----------------------|------|------------------|-------|

| ISHSL Input Leakage Current |                                               | -1                    |      | 1                | μΑ    |

| ISHSL Input High Voltage    |                                               | V <sub>IN</sub> - 0.5 | 1.3  |                  | ٧     |

| ISHSL Input Low Voltage     |                                               |                       | 1.2  | 0.5              | ٧     |

| SLOPE COMPENSATION          |                                               |                       |      | !                |       |

|                             | SC1 = SC0 = V <sub>IN</sub>                   | 5.9                   | 13.4 | 17.7             | A/µs  |

|                             | SC1 = V <sub>IN</sub> , SC0 = GND             | 3.0                   | 6.7  | 8.8              | A/µs  |

|                             | SC1 = GND, SC0 = V <sub>IN</sub>              | 1.5                   | 3.4  | 4.5              | A/µs  |

|                             | SC1 = SC0 = GND                               | 0.7                   | 1.7  | 2.2              | A/µs  |

|                             | FSEL = GND, SC1 = SC0 = V <sub>IN</sub>       | 2.9                   | 6.6  | 8.8              | A/µs  |

|                             | FSEL = GND, SC1 = V <sub>IN</sub> , SC0 = GND | 1.4                   | 3.3  | 4.5              | A/µs  |

|                             | FSEL = GND, SC1 = GND, SC0 = V <sub>IN</sub>  | 0.7                   | 1.6  | 2.2              | A/µs  |

|                             | FSEL = GND, SC1 = SC0 = GND                   | 0.3                   | 0.8  | 1.2              | A/µs  |

#### NOTES:

- 9. Typical values shown reflect  $T_A = T_J = +25$  °C operation and are not guaranteed.

- 10. Parameters with MIN and/or MAX limits are 100% tested at -55°C, +25°C and +125°C, unless otherwise specified.

- 11. Limits do not include tolerance of external feedback resistors. The OA to 12A output current range may be reduced by Minimum LXx On Time and Minimum LXx Off Time specifications.

- 12. Limits established by characterization or analysis and are not production tested.

- 13. Tested sequencially on LX2, LX6 and LX9.

- 14. Tested sequencially on LX2 and LX6 at 535mA to 735mA and 2.3A to 2.6A.

- 15. Tested in accordance with MIL-STD-883, method 1019, condition A.

# **Typical Performance Curves**

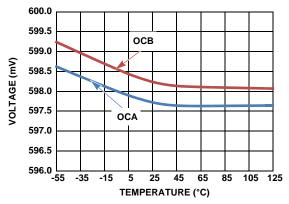

FIGURE 5. OVERCURRENT REFERENCE VOLTAGE

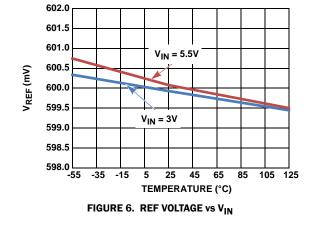

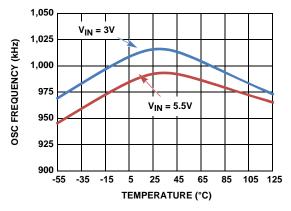

FIGURE 7. OSC FREQUENCY vs VIN

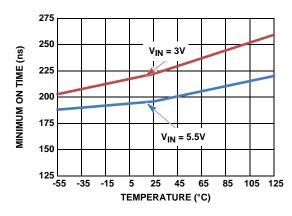

FIGURE 8. LXx MINIMUM ON TIME vs  $\mathbf{V}_{\mathbf{IN}}$

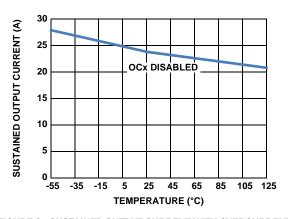

FIGURE 9. SUSTAINED OUTPUT CURRENT WITH OVERCURRENT DISABLED

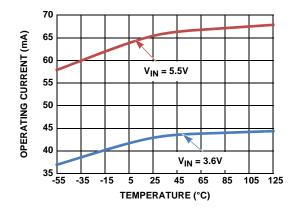

FIGURE 10. OPERATING CURRENT vs  $V_{\text{IN}}$

# Typical Performance Curves (Continued)

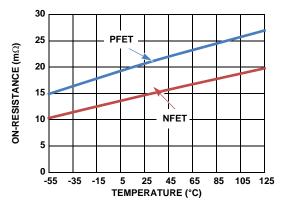

FIGURE 11. LX ON-RESISTANCE, ALL POWER BLOCKS IN PARALLEL,  $V_{\mbox{\scriptsize IN}}$  = 3V

### **Functional Description**

The ISL70002SEH is a monolithic, fixed frequency, current-mode synchronous buck regulator. Two ISL70002SEH devices can be used to provide a total DC/DC solution for FPGAs, CPLDs, DSPs and CPUs.

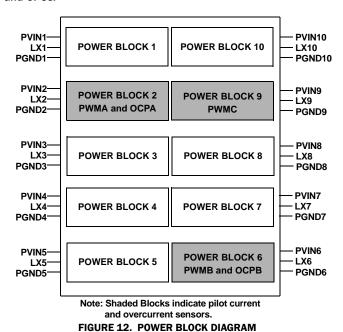

#### **Power Blocks**

The power output stage of the regulator consists of ten power blocks that are paralleled to provide full 12A output current capability. The block diagram in Figure 12 shows a top level view of the individual power blocks.

Each power block has a power supply input pin, PVINx, a phase output pin, LXx, and a power supply ground pin, PGNDx. All PVINx pins must be connected to a common power supply rail and all PGNDx pins must be connected to a common ground. LXx pins should be connected to the output inductor based on the required load current, but must include the LX2, LX6 and LX9 pins. For example, if 6A of output current is needed, any five LXx pins can be connected to the inductor as long as three of them are the LX2, LX6 and LX9 pins. The unused LXx pins should be left unconnected. Connecting all ten LXx pins to the output inductor provides a maximum 12A of output current at +150°C die temperature. See the "Typical Application Schematic" on page 6 for pin connection guidance.

Power blocks 2, 6 and 9 contain the master pilot devices, which provides current feedback and this is why they must be connected to the output inductor.

#### **Main Control Loop**

During normal operation, the internal top power switch is turned on at the beginning of each clock cycle. Current in the output inductor ramps up until the current comparator trips and turns off the top power MOSFET. Then the bottom power MOSFET turns on and the inductor current ramps down for the rest of the cycle.

The current comparator compares the output current at the current ripple peak to the scaled pilot current. The error amplifier monitors  $V_{OUT}$  and compares it with an internal reference voltage. The output voltage of the error amplifier creates a proportional current to the pilot. If  $V_{OUT}$  is low, the current level of the pilot is increased and the trip off current level of the output is increased. The increased output current raises  $V_{OUT}$  until it is in agreement with the reference voltage.

#### **Output Voltage Selection**

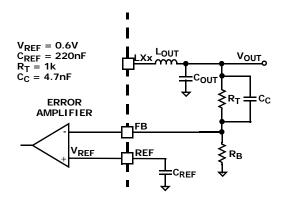

FIGURE 13. OUTPUT VOLTAGE SELECTION

The output voltage of the ISL70002SEH can be adjusted using an external resistor divider as shown in Figure 13.  $R_T$  should be selected as  $1 \mathrm{k}\Omega$  to mitigate SEE.  $R_T$  should be shunted by a 4.7nF ceramic capacitor,  $C_C$ , to mitigate SEE and to improve loop stability margins. The REF pin should be bypassed to AGND with a 220nF ceramic capacitor to mitigate SEE. It should be noted that no current (sourcing or sinking) is available from the REF pin.  $R_B$  can be determined from Equation 3. The designer can configure the output voltage from 0.8V to 85% of the input voltage.

$$R_{B} = R_{T} \cdot \frac{V_{REF}}{V_{OUT} - V_{REF}}$$

(EQ. 3)

The minimum on time determines the lowest output voltage, so when VIN = 5.5V and the switching frequency is 500kHz this parameter limits the regulated output voltage to about 0.8V or greater. It increases at the 1MHz switching frequency to about 1.6V or greater. The minimum on time increases by about 9% at  $V_{IN}$  = 3V, but the 500kHz output voltage is not limited by the minimum on time and the 1MHz minimum  $V_{OUT}$  is approximately 0.9V

#### **Switching Frequency/Synchronization**

The ISL70002SEH features an internal oscillator running at a fixed frequency of either 500kHz or 1MHz ±15% over recommended operating conditions. When the FSEL pin is grounded the oscillator operated at 500kHz, and if FSEL is connected to DVDD it operates at 1MHZ.

The regulator can be configured to run from the internal oscillator or can be synchronized to another ISL70002SEH or an SEE hardened external clock with a frequency range of 500kHz to 1MHz ( $\pm 20\%$ ).

To run the regulator from the internal oscillator, connect the M/S pin to DVDD. In this case the output of the internal oscillator

appears on the SYNC pin. To synchronize the regulator to the SYNC output of another ISL70002SEH regulator or to an SEE hardened external clock, connect the M/S pin to DGND. In this case the SYNC pin is an input that accepts an external synchronizing signal. When M/S is connected to DGND, the ISL70002SEH is synchronized 180° out-of-phase with respect to the SYNC input of a Master configured regulator SYNC output or to an external clock.

### Two Phase Operation

The ISL70002SEH is capable of operating 2 ICs as a single Two Phase regulator with nearly twice the load current capacity. In this mode, a redundant Current Sharing bus balances the load current between the two devices and communicates any fault conditions. One ISL70002SEH is designated the Master and the other the Slave. The Master ISHSL pin is connected to DGND and the Slave ISHSL pin is connected to DVDD. The ISHEN pins on both Master and Slave are connected to DVDD. The SYNC, ISHA, ISHB, ISHC, ISHREFA, ISHREFB, ISHREFC, ISHCOM and FB pins are connected from the Master to the Slave and the REF pins are tied with a  $10\Omega$  resistor. Configured this way, the two phase regulator nearly doubles the load current capacity, limited only by the Current Share Match tolerance.

The ISL70002SEH ICs operate 180° out-of-phase to minimize the input ripple current, effectively operating as a single IC at twice the switching frequency. The Master phase uses the falling edge of the SYNC clock to initiate the Master switching cycle with the non-overlap period before the rising edge of LX, while the Slave phase internally inverts the SYNC input and uses the falling edge of the inverted copy to start it's switching cycle. This is independent of whether the Master phase is configured for an external clock (Master M/S = DGND) or its internal clock (Master M/S = DVDD). The Master Error Amplifier and Compensation controls the two phase regulator while the Slave Error Amplifier is disabled. The schematic in Figure 3 shows the complete connections for the Master and Slave.

### **Operation Initialization**

The ISL70002SEH initializes based on the state of the power-on reset (POR) monitor of the PVINx inputs and the state of the EN input. Successful initialization prompts a soft-start interval and the regulator begins slowly ramping the output voltage. Once the commanded output voltage is within the proper window of operation, the power-good signal changes state from low to high indicating proper regulator operation.

#### **Power-On Reset**

The POR circuitry prevents the controller from attempting to softstart before sufficient bias is present at the PVINx pins.

The POR threshold of the PVINx pins is controlled by the PORSEL pin. For a nominal 5V supply voltage, PORSEL should be connected to DVDD. For a nominal 3.3V supply voltage, PORSEL should be connected to DGND. For nominal supply voltages between 5V and 3.3V, PORSEL should be connected to DGND. The POR rising and falling thresholds are shown in the "Electrical Specifications" table on page 9.

Hysteresis between the rising and falling thresholds insures that small perturbations on PVINx seen during turn-on/turn-off of the

regulator do not cause inadvertent turn-off/turn-on of the regulator. When the PVINx pins are below the POR rising threshold, the internal synchronous power MOSFET switches are turned off and the LXx pins are held in a high-impedance state.

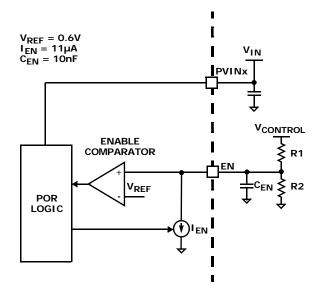

#### **Enable and Disable**