### INTEGRATED CIRCUITS

# DATA SHEET

## **SA2400A**

Single chip transceiver for 2.45 GHz ISM band

Product data 2002 Nov 04

### Single chip transceiver for 2.45 GHz ISM band

**SA2400A**

#### 1. DESCRIPTION

The SA2400A is a fully integrated single IC RF transceiver designed for 2.45 GHz wireless LAN (WLAN) applications. It is a direct conversion radio architecture that is fabricated on an advanced 30 GHz  $f_T$  BiCMOS process. The SA2400A combines a receiver, transmitter, and LO generation into a single IC. The receiver consists of a low-noise amplifier, down-conversion mixers, fully integrated channel filters, and an Automatic Gain Control (AGC) with an on-chip closed loop. The transmitter contains power ramping, filters, up-conversion, and pre-drivers. The LO generation is formed by an entirely on-chip VCO and a fractional-N synthesizer.

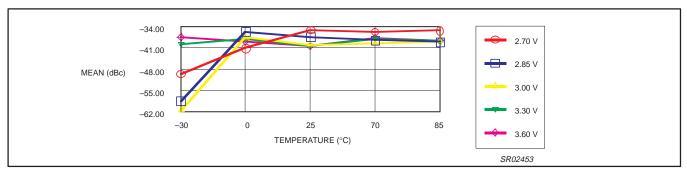

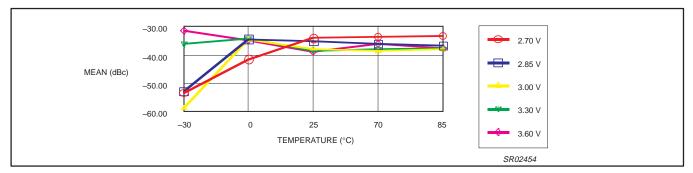

Typical system performance parameters for the receiver are 93 dB gain, 7.5 dB noise figure, input-referred third-order intercept point (IIP3) of +1 dBm, AGC settling time of 8  $\mu s$ , and Tx-to-Rx switching time of 3  $\mu s$ . The transmitter typical system performance parameters are an output power range from –7 dBm to +8 dBm in 1 dB steps, –40 dBc carrier leakage after calibration, 22 dB sideband suppression, in-band common mode rejection of 30 dB, and Rx-to-Tx switching time of 3  $\mu s$ .

### 2. FUNCTIONAL BLOCKS AND FEATURES

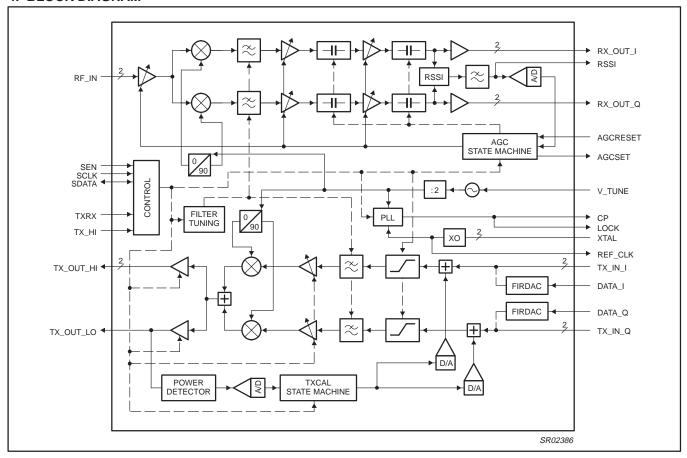

The block diagram of the SA2400A Direct Conversion transceiver is given in Figure 1. It consists of the following functional blocks:

- A 79 dB adjustable gain range direct conversion zero IF receiver with 3 μs (typical) Tx to Rx switching time, and comprising the following:

- Front-end LNA with two internal gain states

- A fast on-chip closed loop composite RF and IF AGC with zoomed analog RSSI output and 8 μs settling time

- Quadrature downconverters from 2.45 GHz RF directly to zero IF

- On-chip fast baseband DC cancellation with automatically stepped bandwidths of 10 MHz, 1 MHz, 100 kHz, and 10 kHz, settling within 8–13 µs for a DC error of 10% that decays to 1%.

- Fully integrated channel filters, appropriate for 11 Msymbols/s QPSK modulation RF bandwidth.

- An I/Q upconverter from baseband directly to 2.45 GHz, with +8 dBm output power, -40 dBc typical carrier leakage (calibrated) and 3 μs (typical) Rx to Tx switching time, and comprising the following:

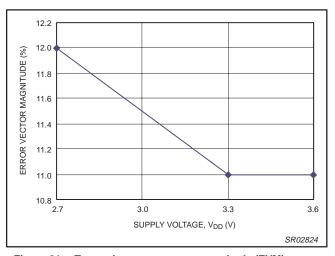

- Wide band IQ modulator producing better than 14% EVM for 11 Msymbols/s QPSK modulation

- Integrated reconstruction and spectral shaping filters at I and Q modulation input that is driven by an external D/A. High common mode rejection to input ground bounce.

- FIR-DACs for digital I/Q input feeding the analog signal path and including additional filtering for spectral shaping.

- 2.45 GHz power amplifier driver with +8 dBm maximum output,

15 dB adjustable gain in 1 dB steps and a second switched output at -1.5 dBm power level with similar gain adjustments that are set by a separate register.

- Completely on-chip calibration for Carrier Leakage compensation.

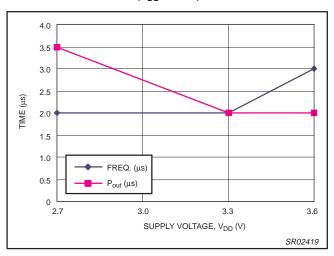

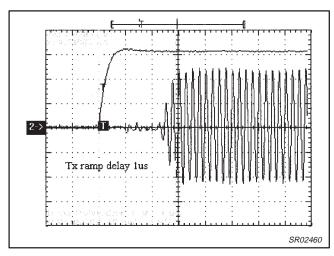

- Internal power ramping with 2  $\mu s$  delay and 0.5  $\mu s$  ramp-up time.

- A fractional-N frequency synthesizer with on-chip VCO and XO

- A 3-wire bus for control of most blocks

- An additional high speed 3-wire bus for full control of Rx-Gain and DC-offset compensation parameters with 44Mbits/s.

- Fast Tx-Rx switching based on a single digital input pin.

- Reference currents and voltage for supply of Baseband Processor and PA-chip.

### 3. APPLICATIONS

- IEEE 802.11 and 802.11b radios

- Supports DSSS and CCK modulation

- Supports data rates: 1, 2, 5.5, and 11 Mbps

- 2.45 GHz ISM band wireless communication devices

### Table 1. Ordering Information

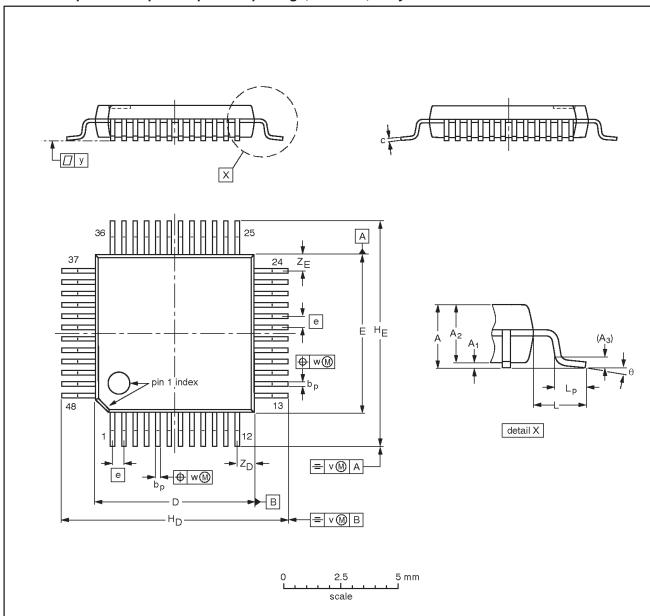

| TYPE NUMBER   | PACKAGE | CKAGE                                                                |          |  |  |  |  |

|---------------|---------|----------------------------------------------------------------------|----------|--|--|--|--|

| I TPE NOWIBER | NAME    | DESCRIPTION                                                          | VERSION  |  |  |  |  |

| SA2400ABE     | LQFP48  | plastic low profile quad flat package; 48 leads; body 7 x 7 x 1.4 mm | SOT313-2 |  |  |  |  |

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

### 4. BLOCK DIAGRAM

Figure 1. SA2400A functional block diagram.

2002 Nov 04

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

### 5. PINNING INFORMATION

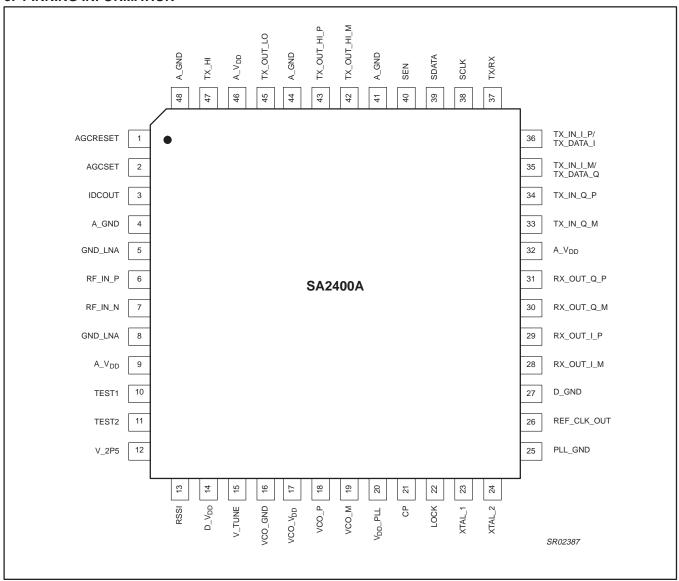

Figure 2. Pin configuration.

2002 Nov 04

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

Table 2. Pin description

PIN type is designated by A = Analog, D = Digital, I = Input, O = Output

| SYMBOL               | PIN | DESCRIPTION                       | TYPE |

|----------------------|-----|-----------------------------------|------|

| AGCRESET             | 1   | AGC start input                   | DI   |

| AGCSET               | 2   | AGC settled output                | DO   |

| IDCOUT               | 3   | Tx-mode:                          | AO   |

| IDCOOT               |     | DC reference current              |      |

| A_GND                | 4   | Analog Ground                     |      |

| GND_LNA              | 5   | Analog Ground                     |      |

| RF_IN_P              | 6   | RF input (positive)               | Al   |

| RF_IN_N              | 7   | RF input (negative)               | Al   |

| GND_LNA              | 8   | Analog Ground                     |      |

| A_V <sub>DD</sub>    | 9   | Analog Supply                     |      |

| TEST_1               | 10  | Test pin                          |      |

| TEST_2               | 11  | Test pin                          |      |

| V_2P5                | 12  | DC reference voltage              | AO   |

| RSSI                 | 13  | RSSI output signal                | AO   |

| D_V <sub>DD</sub>    | 14  | Digital Supply                    |      |

| V_TUNE               | 15  | VCO tuning voltage                | Al   |

| VCO_GND              | 16  | VCO ground                        |      |

| VCO_V <sub>DD</sub>  | 17  | VCO Supply                        |      |

| VCO_P                | 18  | VCO output/<br>External VCO input | AI/O |

| VCO_M                | 19  | VCO output/<br>External VCO input | AI/O |

| V <sub>DD</sub> _PLL | 20  | Synthesizer Supply                |      |

| СР                   | 21  | Charge pump output                | AO   |

| LOCK                 | 22  | Synthesizer lock indicator        | AO   |

| XTAL_1               | 23  | Crystal input                     | Al   |

| XTAL_2               | 24  | Crystal input                     | Al   |

| SYMBOL                  | PIN | DESCRIPTION                        | TYPE  |

|-------------------------|-----|------------------------------------|-------|

| PLL_GND                 | 25  | Synthesizer Ground                 |       |

| REF_CLK_OUT             | 26  | Reference clock output             | AO    |

| D_GND                   | 27  | Digital and Analog Ground          |       |

| RX_OUT_I_M              | 28  | Receive output                     | AO    |

| RX_OUT_I_P              | 29  | Receive output                     | AO    |

| RX_OUT_Q_M              | 30  | Receive output                     | AO    |

| RX_OUT_Q_P              | 31  | Receive output                     | AO    |

| A_V <sub>DD</sub>       | 32  | Analog Supply                      |       |

| TX_IN_Q_M               | 33  | Transmit input                     | Al    |

| TX_IN_Q_P               | 34  | Transmit input                     | Al    |

| TX_IN_I_M/<br>TX_DATA_Q | 35  | Transmit input                     | AI/DI |

| TX_IN_I_P/<br>TX_DATA_I | 36  | Transmit input                     | AI/DI |

| TX/RX                   | 37  | Tx/Rx mode select                  | DI    |

| SCLK                    | 38  | Three-wire bus clock               | DI    |

| SDATA                   | 39  | Three wire bus data                | DI/O  |

| SEN                     | 40  | Three wire bus enable              | DI    |

| A_GND                   | 41  | Analog Ground                      |       |

| TX_OUT_HI_M             | 42  | Transmit output, high power        | AO    |

| TX_OUT_HI_P             | 43  | Transmit output, high power        | AO    |

| A_GND                   | 44  | Analog Ground                      |       |

| TX_OUT_LO               | 45  | Transmit output, low power         | AO    |

| A_V <sub>DD</sub>       | 46  | Analog Supply                      |       |

| TX_HI                   | 47  | Transmit output power level select | DI    |

| A_GND                   | 48  | Analog Ground                      |       |

### Single chip transceiver for 2.45 GHz ISM band

SA2400A

### 6. FUNCTIONAL DESCRIPTION

The SA2400A transceiver is intended for operation in the 2.45 GHz band, specifically for IEEE 802.11b 1 and 2 Mbits/s DSSS, and 5.5 and 11 Mbits/s CCK standards. Throughout this document, the operating RF frequency refers to the ISM band between 2.4 GHz and 2.5 GHz.

### 6.1 RF VCO

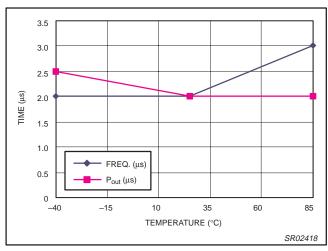

The local oscillator is common to both the transmitter and the receiver. The RF VCO is a differential 4.8 GHz oscillator with the frequency determining components internal to the IC. The VCO is connected internally to a frequency divider and a quadrature generator circuit which produces the LO for the IQ up- and downmixer. The divider output is also internally connected to the synthesizer, which can be programmed in order to produce steps of 0.5 MHz for the desired LO frequency.

At the time of power-up, the VCO must be calibrated by invoking the VCOCALIB mode by means of the three-wire bus. This operation will select an appropriate frequency band in the VCO, thus compensating for process tolerances. The calibration takes up to 2.2 ms, after which the IC automatically enters the SLEEP mode. The synthesizer registers 0x00 through 0x03 must be re-programmed after completing the VCOCALIB.

The 2.45 GHz LO can also be injected externally.

### 6.2 RF Low Noise Amplifier

The RF LNA has differential inputs and an external balun is needed in the case of single-ended operation. It has two gain states which are controlled internally by the on-chip automatic gain control, or manually via the 3-wire bus.

#### 6.3 Downconversion mixers

The RF signal is converted down directly to baseband by quadrature image-reject mixers.

### 6.4 Receiver low-pass filter, baseband amplifiers

The I and Q low-pass filters are fully integrated Chebychev active filters. The I and Q pass band extends from DC to a -3 dB corner at 7 MHz.

Additional adjustable gain is provided in baseband amplifiers to achieve a total adjustable gain range of 79 dB. The Rx output is provided in the form of differential I and Q signals, which must be DC coupled to the ADC inputs on a base band IC.

### 6.5 DC cancellation

The Rx chain also integrates a high-pass filter (DC notch) for cancellation of the DC offset inherent to zero-IF operation. The high-pass filter has a programmable lower 3 dB cutoff frequency of 10 MHz, 1 MHz, 100 kHz or 10 kHz. The DC offset cancellation occurs simultaneously with the AGC settling process. During the AGC settling phase (see below) the cutoff frequency is dynamically selected between 10 MHz and 1 MHz to quickly reduce DC offset values from +50 dBc to below –20 dBc relative to a –76 dBm antenna input signal before the RSSI (see below) is internally sampled. After the AGC settling, the high pass is configured for 100 kHz for 5  $\mu s$  before switching to a final 10 kHz cutoff frequency. The low value of 10 kHz is required for minimizing the signal distortion created by a high-pass function at zero frequency. The

high-pass will then remain set to the 10 kHz cutoff frequency until a new AGC cycle is started.

Whenever there is a frequency change in the high-pass filter lower cutoff, the DC offset can change from a very low value to about 50% (1 MHz  $\geq$  100 kHz step) or 10% (100 kHz  $\geq$  10 kHz step) of the signal level. This DC offset then decays according to the high-pass response of the filter.

The cutoff frequency of the high-pass filter can also be selected manually by using the RXMGC mode.

### **6.6 AGC**

The receiver contains a fully integrated Automatic Gain Control loop. It works by adjusting the internal gain such that the Rx output amplitude, as measured by the RSSI (see below), meets a predefined target value.

By default, the AGC is always set to a default maximum gain (adjustable by register value GMAX) whenever the SA2400A enters the RECEIVE mode of operation from another operational mode. It takes 5  $\mu s$  for the receiver to settle when it enters this mode, which includes the time for DC offsets to be removed with a 1 MHz lower cut-off frequency of the high-pass filtering. This lower cut-off frequency of 1 MHz remains unchanged as long as the AGC remains in the default maximum gain state.

The AGC must be invoked by providing a 0-to-1 transition on the AGCRESET pin, and keeping the signal on that pin to 1 for at least  $5~\mu s$ .

By successively reducing the gain from its initial maximum value, the loop searches for the correct gain value to provide a nominal output amplitude of 500 mV  $_{\rm peak,\ differential}$  for a QPSK signal (within  $\pm 3$  dB dynamic error) at the output pins. This is achieved after a maximum of 8  $\mu s$ . This time is defined by wait periods necessary to settle the receiver after gain switching actions. The individual wait periods can be adjusted by means of register settings.

After completing the AGC settling process, the AGCSET pin is set to 1 by the algorithm. The receiver gain then will not change again until another pulse is issued on the AGCRESET pin.

For a subsequent AGC operation, the receiver needs to enter its maximum gain state again. If another AGCRESET signal (as described above) is issued, the settling period will take an extra 3  $\mu s$ , up to a total of 11  $\mu s$ , since the first 3  $\mu s$  will be spent on entering maximum gain mode and settling the receiver thereafter. To shorten this operation, the receiver can be forced to maximum gain (e.g., at a time when no signal is present) by issuing a 0–1–0 pulse of maximum 1  $\mu s$  pulse width on the AGCRESET pin. The receiver will then enter maximum gain mode (the AGCSET signal will **not** be set to 1 after this), and a following 0-to-1 transition on the AGCRESET pin will start the settling sequence from maximum gain, which will then take a maximum of 8  $\mu s$ .

The receiver gain can also be selected manually by using the RXMGC mode.

The settling target can be adjusted by  $\pm 7$  dB from the nominal level of 500 mV  $_{peak,\ differential}$  by means of register settings.

**Note:** When doing measurements with a single-tone RF signal, the amplitude at the Rx outputs after settling the AGC will be lower, at about 300 mV  $_{\rm peak,\ differential}$

2002 Nov 04

### Single chip transceiver for 2.45 GHz ISM band

SA2400A

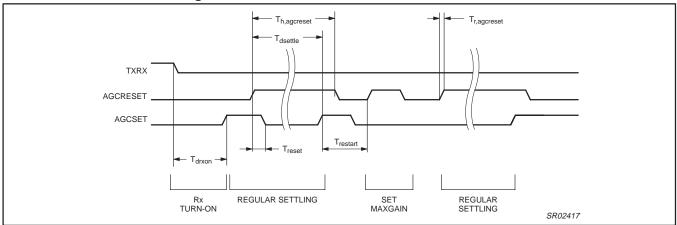

#### 6.7 AGC Handshake

On the digital input pin AGCRESET, a 0-to-1 transition clears AGCSET output to logic 0 and starts the AGC cycle. At the end of the AGC settling, the AGCSET output is asserted to logic 1. The AGCRESET input can then be reset to logic 0. At any time in the RECEIVE mode the AGC can be forced to the maximum gain by giving the AGCRESET signal as described, but by additionally re-setting it to logic 0 within 1  $\mu s$ . The AGCSET indication is not given in this case and the receiver settling time is 3  $\mu s$ . The channel filters will be set to have a lower cut-off of 1 MHz. For a timing diagram, please see the receiver parameters section.

### **6.8 RSSI**

The Receive Signal Strength Indicator (RSSI) is implemented as an error signal comparing the signal level at the Rx output to the nominal value of 500 mV  $_{\rm peak, differential}$ . It has a -10 dBc to +10 dBc operational range relative to the nominal signal level. Since the RSSI acts on the modulated RF signal envelope that is extracted from the baseband I and Q signals, it includes DC offsets, and will therefore show transient decaying errors when the AC coupling lower cut-off frequency is changed.

The RSSI signal reflects on a logarithmic scale the amplitude of the instantaneous modulated RF signal (envelope). The RSSI signal is filtered by a low-pass filter with 0.5 MHz upper cut-off frequency.

The SA2400A receiver is designed to give at least –10 dBc RSSI at maximum gain, when there is no signal present, i.e., with only thermal noise. However, due to process spreads (e.g., gain, noise figure, IQ low-pass filter bandwidth, etc.), the RSSI may show higher than –10 dBc. In case a calibration is required for setting this noise power to –10 dBc, the AGC's maximum gain (GMAX) can be changed in the range of 85 to 54 dB in steps of 1 dB via register settings. The programmed value of maximum gain is never altered by the AGC settling or by forcing the AGC to maximum gain. Only the RXMGC mode can set the AGC gain to values higher than GMAX. The RXMGC mode does not change the value of GMAX.

### 6.9 Receiver blocking immunity

The receiver is designed to exceed the IEEE802.11 specifications for the blocking and intermodulation. It can accept continuous or randomly pulsed interfering single- or multi-tone signals that are more than 35 dB stronger than the wanted signal, and up to -10 dBm of interference level. The spurious I and Q outputs are maintained to smaller than -20 dBc of the wanted signal level.

### 6.10 Transmitter and IQ upconverter

The transmitter inputs are designed to be driven from a Baseband IC in one of two modes: a) in analog mode, differential I and Q inputs expect current signals driven by DACs in the Baseband IC; or b) in digital mode, single-ended inputs expect two binary data

streams. In this case, integrated FIR–DACS provide additional filtering. The data streams are sampled with the reference clock. For timing specifications, please see the transmitter parameters section.

The wide band IQ upconverter includes spectral shaping reconstruction filters (4<sup>th</sup> order low-pass Butterworth with 9.75 MHz 3 dB upper cut-off frequency).

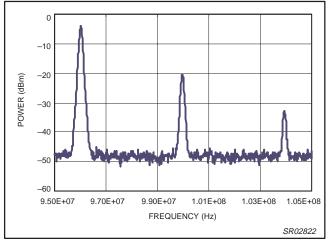

At +8 dBm maximum transmitter output level the out-of-band (FCC forbidden band) spurious signal power is less than –77 dBc (integrated over 1 MHz with a 100 kHz resolution bandwidth) for the 11 Msymbols/sec CCK modulation (footnote <sup>1</sup>). This implies that the spectral regrowth is dominated by any external PA that may be used to boost the transmission power level.

In analog mode, it is assumed that the input baseband IQ signals as delivered from the Baseband IC are pulse shaped.

By using the on-chip calibration loop, the transmitter Carrier Leakage can be reduced to levels far less than required by the standard. An RF power meter detects the LO level, converts it into a digital signal and a state machine determines the compensation values which are fed through a DAC directly to the IQ inputs. This mode is activated by setting the IC into the DCALIB mode by means of 3-wire bus programming. This calibration is designed to compensate for any DC offsets delivered by the ADCs on the Baseband IC. The DCALIB cannot be used when the IC is using the digital-input Tx mode.

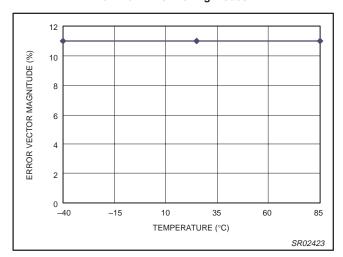

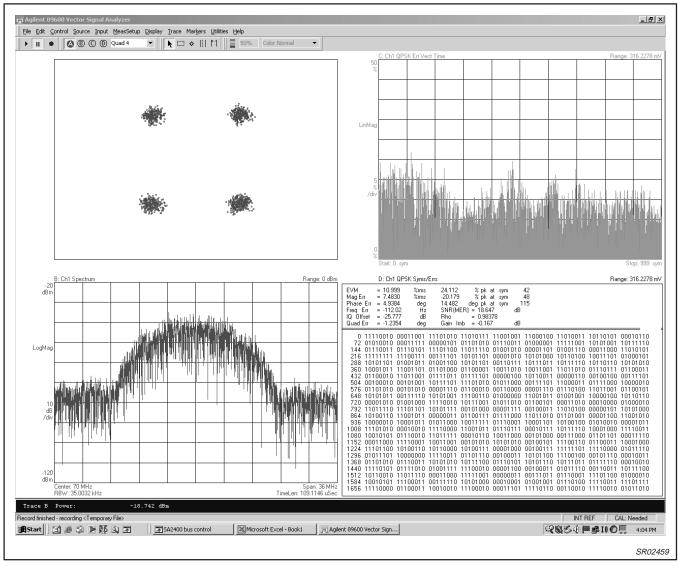

The IQ gain and phase imbalance, reconstruction filter roll-off and in-channel noise produce a modulation EVM of less than 12% for 11 Msymbols/sec QPSK. The transmitter has two switched outputs, one with –1.5 dBm output power and the other one with +8 dBm output power. The input pin TX\_HI is used to select between the two RF output ports.

The 8 dBm output port is differential and is designed to work seamlessly (no external filtering required) with the SA2411 power amplifier.

Upon entering the Tx mode, the ramping up of the RF Tx signal is delayed by an internal power ramping circuit. The ramping up time is fixed, while the delay prior to ramping up can be programmed by register settings.

**Note:** When switching out of the Transmit mode (either into Receive mode by transition on TXRX pin, or into another mode by 3-wire programming), the reference clock input (pins XTAL\_1 and XTAL\_2) needs to be active since a digital timer is being used.

### 6.11 Reference current and voltage outputs

The IC provides a temperature-constant reference current of 1 mA or 300  $\mu$ A (selectable), active in Tx mode, as well as a 2.5 V reference voltage.

2002 Nov 04

<sup>1.</sup> For a CCK signal, the peak signal power is 21.7 dB lower than the total power integrated over the 22 MHz band. The SA2400A guarantees better than 56 dBc suppression of the second sidelobe (greater than 22 MHz frequency offset). Consequently, the power level in the forbidden bands is at least 77 dBc below the transmitted integrated power.

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

### 7. OPERATING CONDITIONS

**Table 3. Absolute Maximum Ratings**

| Symbol           | Parameter                                         | Min         | Max                  | Unit   |

|------------------|---------------------------------------------------|-------------|----------------------|--------|

| T <sub>stg</sub> | Storage temperature                               | <b>-</b> 55 | +150                 | °C     |

| $V_{DD}$         | Supply voltage                                    | -0.5        | +3.85                | V      |

|                  | Voltage applied to inputs                         | -0.5        | V <sub>DD</sub> +0.5 | ٧      |

|                  | Short circuit duration, to GND or V <sub>DD</sub> | _           | 1                    | second |

### **Table 4. Recommended Operating Conditions**

| Symbol           | Parameter                              | Min  | Nom | Max | Units |

|------------------|----------------------------------------|------|-----|-----|-------|

| T <sub>amb</sub> | Ambient operating temperature (Note 1) | -30  | _   | +85 | °C    |

| $V_{DD}$         | Supply voltage                         | 2.85 | 3.3 | 3.6 | V     |

#### NOTE:

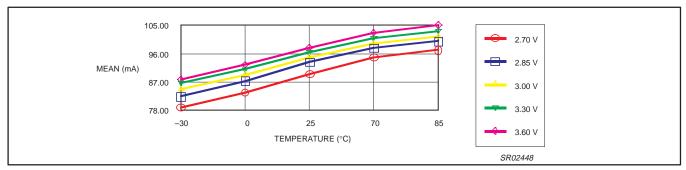

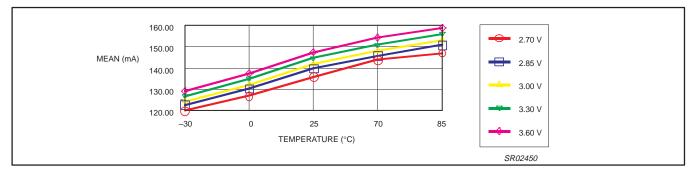

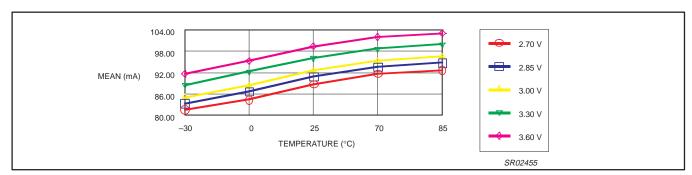

### 8. OPERATIONAL MODES AND CURRENT CONSUMPTION

(See also Table 18).

Table 5. Operational modes and current consumption

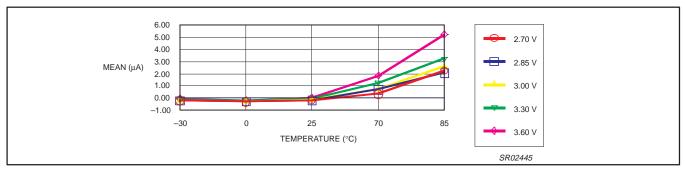

$T_{amb} = 25 \, ^{\circ}C; \, V_{CC} = 3.3 \, V.$

|            | Main mode                           |                                                                                                 |                                                                                                                   | Duration | Cı  | urrent (mA) |      |

|------------|-------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------|-----|-------------|------|

| Chip state | (register 0x04)                     | Other conditions                                                                                | Description                                                                                                       | (max.)   | Min | Тур         | Max  |

| POWER-UP   | SLEEP                               | XO on, clock output on                                                                          |                                                                                                                   | n/a      | 1.8 | 2.2         | 2.7  |

| SLEEP      | SLEEP                               | XO off                                                                                          | Note 1.                                                                                                           | n/a      | -   | -           | 0.05 |

| TX HI      | TX/RX or<br>FASTTXRXMGC             | TXRX = HIGH;<br>TX_HI = HIGH                                                                    | Synthesizer ON.<br>Transmitter ON with 8 dBm driver.<br>Maximum gain.                                             | n/a      | 120 | 143         | 170  |

| TX LO      | TX/RX or<br>FASTTXRXMGC             | TXRX = HIGH;<br>TX_HI = LOW                                                                     | Synthesizer ON. Transmitter ON with –1.5 dBm driver. Maximum gain.                                                | n/a      | 81  | 95          | 105  |

| RX         | TX/RX or<br>RXMGC or<br>FASTTXRXMGC | TXRX = LOW                                                                                      | Synthesizer ON. Receiver ON. Receiver gain control by:  ■ TX/RX ⇒ internal AGC  ■ RXMGC ⇒ 3-wire bus programming  | n/a      | 81  | 95          | 105  |

|            |                                     |                                                                                                 | <ul> <li>FASTTXRXMGC ⇒ fast 3-wire bus</li> </ul>                                                                 |          |     |             |      |

| WAIT       | WAIT                                |                                                                                                 | Only Synthesizer and Xtal oscillator ON                                                                           | n/a      | 27  | 31          | 34   |

| FCALIB     | FCALIB                              |                                                                                                 | Calibrates cut-off frequency of Tx and Rx filters internally. Automatic transition to SLEEP mode upon completion. | 3 μs     | -   | n/a         | _    |

| DCALIB     | DCALIB                              | Maintain TX mode<br>for 5 μs before<br>calibration.<br>Quiescent IQ input.<br>Analog mode used. | Calibration to reduce transmitter carrier leakage. Automatic transition to SLEEP mode upon completion.            | 20 μs    | _   | n/a         | _    |

| VCOCALIB   | VCOCALIB                            |                                                                                                 | Calibrates internal VCO.                                                                                          | 2200 μs  | -   | n/a         | _    |

| RESET      | RESET                               |                                                                                                 | Resets IC into power-up state (SLEEP mode and all registers at default values)                                    | n/a      | -   | n/a         | _    |

#### NOTE:

<sup>1.</sup> When the digital input mode is used, the lower limit of the ambient operating temperature is higher than -30 °C. Preliminary characterization results suggest a limit of -20 °C. This does not apply if the analog input mode is used.

<sup>1.</sup> All digital inputs connected to GND or  $V_{\mbox{\scriptsize DD}}$ .

### Single chip transceiver for 2.45 GHz ISM band

SA2400A

#### 8.1 RESET

Shuts down all blocks except the 3-wire digital section, and programs internal registers to known default values that are described in section 13. This ensures that the SA2400A transmitter, receiver, synthesizer and other blocks enter a known state when made active. The SA2400A enters the SLEEP state automatically after the RESET state. Before entering either the TXRX or RXMGC active states, the internal registers can be reprogrammed to change their values from the default values. A power-up of the digital supply also forces the SA2400A to the RESET mode.

### 8.2 SLEEP

All blocks (except the xtal osc) are OFF. The xtal osc can be separately shut down. Note that the 3-wire bus will remain operational in all modes as long as the digital supply is ON. The SA2400A retains programmed values of all active modes when it comes out of the sleep mode. This includes the synthesizer operation. Programmed via 3-wire bus.

### **8.3 WAIT**

The PLL is on. Receiver and the transmitter are both OFF. This mode is useful for a quick turn-around to either TXRX or RXMGC modes. Transition to or from this mode is done via the 3-wire bus.

#### 8.4 RXMGC

Only the PLL and Receiver are operating. The AGC gain is manually set by the value of a register field.

### **8.5 TXRX**

In this mode the logic level on the TX/RX input pin determines the operational mode: 1 = TRANSMIT, 0 = RECEIVE. This way, no 3-wire bus programming is necessary to switch between Tx and Tx, resulting in faster switching. When entering the RECEIVE mode (either via 3-wire programming to TXRX mode with TX/RX pin at logic zero, or by a 1-to-0 transition of TX/RX pin when already in the TXRX mode), the Receiver is set to maximum gain. An AGC cycle is

initiated by a 0-to-1 change on the AGC\_RESET digital input pin. At any time in the RECEIVE mode, the AGC can be forced to the maximum gain setting by giving a 1  $\mu$ s pulse on the AGC\_RESET input while the TX/RX input is held at logic 0.

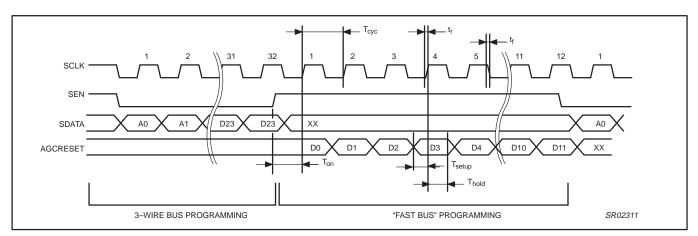

### 8.6 FASTTXRXMGC

It is similar to the RXMGC mode, except that the manual AGC gain programming can be done faster, as described in Section 14.5.

### 8.7 FCALIB

This mode needs to be programmed after power ON in order to internally calibrate the cut-off frequency of the on-chip transmit and receive active filters. Upon completion of the calibration, the IC will automatically switch to Main Mode = SLEEP. This calibration takes a maximum of 3  $\mu s$  measured from the end of the programming sequence. The result of this calibration can be read out from register word 0x04.

#### 8.8 DCALIB

If the analog Tx inputs are used, this mode needs to be programmed at least once after power ON in order to reduce the transmitter carrier leakage. This mode should be programmed after being in TX mode for at least 5  $\mu s$ . Upon completion of the calibration, the IC will automatically switch to Main Mode = SLEEP. This calibration takes a maximum of 20  $\mu s$  measured from the end of the programming sequence. The result of this calibration can be read out from register 0.007

#### 8.9 VCOCALIB

This mode needs to be programmed at least once after power ON in order to calibrate the internal VCO. Upon completion of the calibration, the IC will automatically switch to Main Mode = SLEEP. This calibration takes a maximum of 2.2 ms from the end of the programming sequence. After this calibration, the synthesizer must be re-programmed by writing the register words 0x00 through 0x03. The result of this calibration can be read out from register 0x08.

2002 Nov 04

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

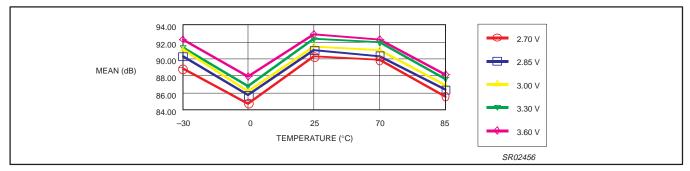

### 9. SA2400A RECEIVER

The baseband output signal extends from DC to 8 MHz, and the out-of-band frequency begins from 11 MHz. The modulated test signal used is 11 Msymbols/sec QPSK with raised cosine filtering (50% excess bandwidth for 11 Msymbols/sec). The LO frequency is the same as the Receiver channel center frequency, as the IF output is at 0 Hz.

Table 6. SA2400A Receiver properties

$T_{amb} = 25 \, ^{\circ}\text{C}; \, V_{CC} = 3.3 \, \text{V}; \, f_{LO} = 2.45 \, \text{GHz}.$

| Specification                                                 | Conditions                                                                                                                                                                                                                                   | Min                     | Тур                                              | Max                | Units                |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------|--------------------|----------------------|

| RF input frequency range                                      | Typical                                                                                                                                                                                                                                      | 2.4                     |                                                  | 2.5                | GHz                  |

| S11 (RF input)                                                | Incl balun+matching. 50 $\Omega$ unbalanced. Note 3. LNA in high gain (see reg. description 0x06) LNA in low gain                                                                                                                            |                         | -10<br>-7                                        | -                  | dB<br>dB             |

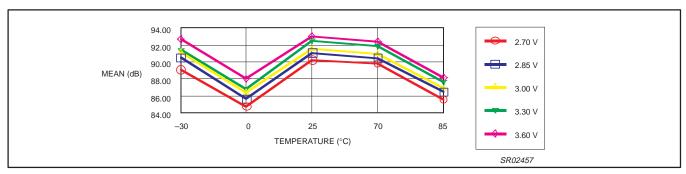

| Maximum Rx voltage gain                                       | RF input to I or Q outputs                                                                                                                                                                                                                   | 90                      | 93                                               | _                  | dB                   |

| Max RF input level                                            | Including application, AGCTARGET = +5. Note 1.                                                                                                                                                                                               | -10                     | -                                                | _                  | dBm                  |

|                                                               | To maintain nominal IQ output levels as defined below ("nominal I and Q output voltage")                                                                                                                                                     | -20                     | -                                                | -                  | dBm                  |

| IQ Output DC error (relative to signal, 5 μs after AGC set)   | -80 dBm < P <sub>input</sub> < -20 dBm, 1 MHz sinewave output. Note 3.                                                                                                                                                                       | -                       | -                                                | -20                | dBc                  |

| AGC settling time<br>(indicated by AGC_SET digital<br>output) | Initiated by AGC_RESET input. Constant RF input within this settling time. Begins after TX to RX switching time. Measured from AGC_RESET 0–1 transition. AGC delay registers (0x05) at default or smaller values. Note 2.  a) First instance | _                       | _                                                | 8                  | μs                   |

|                                                               | b) 2 <sup>nd</sup> or subsequent instances                                                                                                                                                                                                   | _                       | _                                                | 11                 | μs                   |

| AGC Max Gain settling time                                    | AGC forced to GMAX by:                                                                                                                                                                                                                       |                         |                                                  |                    | 1                    |

|                                                               | a) TX to RX mode transition. (measured after 5 μs TX–RX settling time).                                                                                                                                                                      | _                       | _                                                | 0                  | μs                   |

|                                                               | b) Pulse on AGC_RESET pin (measured from end of programming) Note 2.                                                                                                                                                                         | _                       | _                                                | 3                  | μs                   |

| AGC Max Gain adjustment range                                 | Note 2.                                                                                                                                                                                                                                      | 54 to 85, in steps of 1 |                                                  |                    | dB                   |

| AGC error (I, Q signal levels)                                | RF input between –75 to –20 dBm. AGC_RESET used. AGC delay registers (0x05) at default values.                                                                                                                                               |                         |                                                  |                    |                      |

|                                                               | <ul> <li>a) Random (varies each AGC cycle)</li> <li>b) Slow (varies with V<sub>CC</sub>, Temperature).</li> <li>c) Static (fixed, part to part)</li> </ul>                                                                                   | -3<br>-1<br>-1          | _<br>_<br>_                                      | 3 1 1              | dB<br>dB<br>dB       |

| DC cancellation time                                          | With constant RF input during this time. Note 3.                                                                                                                                                                                             | · ·                     | <del>                                     </del> | <del> </del>       | +                    |

| (after AGCRESET)                                              | a) DC offset < 50% of output signal level                                                                                                                                                                                                    | _                       | _                                                | 8                  | μs                   |

|                                                               | b) DC offset <10% of output signal level                                                                                                                                                                                                     | _                       | -                                                | 13                 | μs                   |

| TX to RX switching time                                       | Output signal within 1 dB of final value, frequency error within 25 ppm of final value. Note 3.                                                                                                                                              | -                       | 3                                                | 3.5                | μs                   |

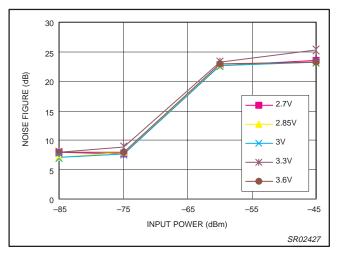

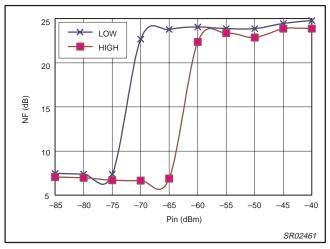

| Noise Figure<br>(Incl balun+matching)                         | Less than the piece-wise linear interpolation. Note 3.  Pinput = -85 dBm (LNA in high gain mode) -75 dBm -60 dBm (LNA in low gain mode) -45 dBm                                                                                              | -<br>-<br>-             | 7.5<br>7.5<br>24<br>24                           | 9<br>9<br>25<br>25 | dB<br>dB<br>dB<br>dB |

| Input IP3 (50 $\Omega$ source resistance)                     | 2 interfering tones of power P <sub>interferer</sub> each, at 13 and 23 MHz offsets from LO. IP3 to be more than the piece-wise linear interpolation: P <sub>interferer</sub> = -39 dBm                                                      | -5                      | 1                                                | -                  | dBm                  |

| 1 dB compression of wanted signal                             | Including matching, receiver at minimum gain.                                                                                                                                                                                                | -10                     | 0                                                | _                  | dBm                  |

| Desens by jammer                                              | -45 dBm wanted signal at 1 MHz offset, +40 dBc                                                                                                                                                                                               | _                       | _                                                | 1                  | dB                   |

### Single chip transceiver for 2.45 GHz ISM band

SA2400A

| Specification                                             | Conditions                                                                                                                                                                                                         | Min                     | Тур                        | Max                            | Units             |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|--------------------------------|-------------------|

| LO leakage to antenna                                     | All gain modes. Incl balun                                                                                                                                                                                         | -                       | -75                        | -57                            | dBm               |

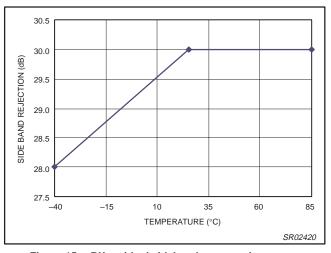

| Residual sideband Rejection                               | Measured with single tone at 2 MHz offset from carrier. Includes both IQ gain and phase error. Notes 3, 7.                                                                                                         | 22                      | 29                         | -                              | dB                |

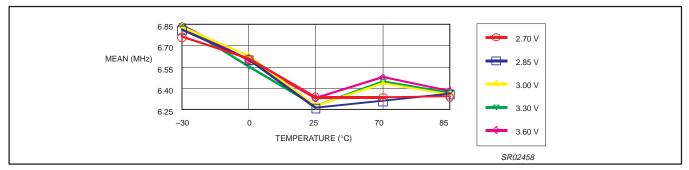

| Ripple band width of filter                               | Note 4.                                                                                                                                                                                                            | 5.6                     | 6.3                        | 7.0                            | MHz               |

| 3 dB band width of filter                                 | Indicative, not tested. Note 4.                                                                                                                                                                                    | _                       | 7                          | _                              | MHz               |

| In-band amplitude ripple                                  | DC to ripple band width edge. Note 3.                                                                                                                                                                              | _                       | -                          | 0.6                            | dB peak           |

| Out-of-band attenuation                                   | Relative to minimum in-band gain > 11 MHz > 22 MHz                                                                                                                                                                 | 25<br>55                | _<br>_                     | -                              | dB<br>dB          |

| Lower 3 dB cut-off frequency of AC coupling               | Cascade of two 1st order high-pass filters. a) NARROW BAND b) INTERMEDIATE BAND c) WIDE BAND                                                                                                                       | -<br>-<br>-             | 10<br>100<br>1000          | -<br>-<br>-                    | kHz<br>kHz<br>kHz |

| Output load resistance                                    | Pin to GND, differential. Note 5.                                                                                                                                                                                  | 15                      | -                          | _                              | kΩ                |

| Output load capacitance                                   | Pin to GND                                                                                                                                                                                                         | _                       | _                          | 6                              | pF                |

| Nominal I & Q output voltage                              | Differential at the load specified. Note 6.                                                                                                                                                                        | _                       | 0.5                        | -                              | V peak            |

| Maximum I & Q output voltage                              | Saturated, differential                                                                                                                                                                                            | _                       | _                          | 1.5                            | V peak            |

| Common mode IQ voltage                                    | Programmable (see 0x04)  Mode 1  Mode 2                                                                                                                                                                            | V <sub>CC</sub> /2-0.25 | V <sub>CC</sub> /2<br>1.25 | V <sub>CC</sub> /2+0.25<br>1.5 | V<br>V            |

| 1 dB compression level at output                          | 1 MHz tone, differential. Maximum gain.                                                                                                                                                                            | 1                       | -                          | Ī-                             | V peak            |

| Total Harmonic Distortion (measured at max and min gains) | Input 1 – 5 MHz signal, 1 V peak differential sinusoidal at output, output spurs measured differential up to 100 MHz. Ratio of rms total spurious distortion to rms fundamental. Receiver in minimum gain. Note 3. | -                       | 2                          | 4                              | %                 |

|                                                           | Receiver in maximum gain. Note 3.                                                                                                                                                                                  | _                       | 5                          | 10                             | %                 |

| Phase Imbalance                                           | Signal tone input at 2 MHz offset from carrier. Indicative, not tested.                                                                                                                                            | -                       | 4                          | -                              | deg               |

| I, /I to Q, /Q amplitude imbalance                        | ratio of signal at I pin to /I pin;<br>Same for Q and /Q pins.                                                                                                                                                     | _                       | 0.1                        | _                              | dB                |

| RSSI voltage in settled state (internal AGC)              | Corresponds to I, Q output signal levels when AGC_RESET is used, with RF input between –10 and –80 dBm.  1 MHz tone, 0.5 V peak differential. ACGTARGET = 0                                                        | 1.25                    | 1.55                       | 1.95                           | V                 |

| RSSI voltage difference                                   | 1 dB change in input power compared to settled state                                                                                                                                                               | -                       | 64.5                       | -                              | mV                |

| RSSI minimum voltage                                      | Signal power = -10 dBc                                                                                                                                                                                             | -                       | 0.9                        | -                              | V                 |

| RSSI maximum output voltage                               | Signal power = +10 dBc                                                                                                                                                                                             | -                       | 2.2                        | -                              | V                 |

| RSSI error                                                | -10 dBc < signal power < +10 dBc                                                                                                                                                                                   | <b>-</b>                | ±1                         | -                              | dB                |

### NOTES:

- Corresponds to -15 dBm input level at IC input, assuming typical 5 dB loss from the antenna to the IC input. The AGCTARGET register should be set to "+5" which causes the AGC to settle to an output amplitude greater than the specified nominal value. A resistive divider network at the output can be used to adjust the actual IQ output levels to the BB ADC range.

- 2. Guaranteed by design.

- 3. Verified by bench characterization and found to have sufficient margin for production.

- 4. At power-up time, the filter bandwidth is undefined. It needs to be calibrated with the internal tuner (FCALIB mode).

- 5. For unsymmetrical loading, attach the same load impedance to the unused pin; condition: for 80% of nominal output voltage swing.

- 6. Nominal I/Q output levels are understood as the levels the SA2400A will settle to after an AGCRESET action is performed with an RF input signal modulated by a Barker sequence, and with AGCTARGET = 0.

- 7.  $RSB = 20^* \log(\sqrt{1+K^2 + 2K\cos\phi})/[1+K^2 2K\cos\phi]$ ), where K = linear gain imbalance, and  $\phi$  = phase imbalance.

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

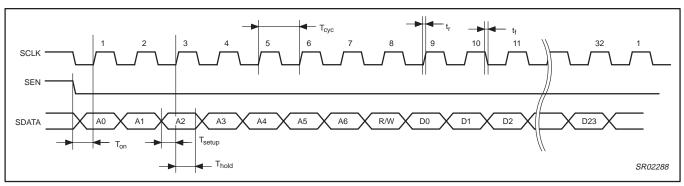

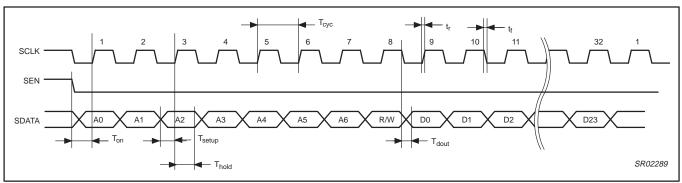

### 9.1 AGC handshake and timing

Figure 3. AGC handshake and timing.

### Table 7. AGC timing

| Symbol                  | Parameter                           | Condition               | Min                 | Тур | Max                  | Units |

|-------------------------|-------------------------------------|-------------------------|---------------------|-----|----------------------|-------|

| AGC logic               | evel requirements                   |                         | •                   |     |                      |       |

| V <sub>IH</sub>         | HIGH-level logic input voltage      |                         | 0.5×V <sub>DD</sub> | -   | V <sub>DD</sub> +0.3 | V     |

| V <sub>IL</sub>         | LOW-level logic input voltage       |                         | -0.3                | -   | 0.2×V <sub>DD</sub>  | V     |

| AGCRESE <sup>-</sup>    | Γ timing                            |                         |                     |     |                      |       |

| T <sub>r,agcreset</sub> | Input rise time                     |                         | -                   | 10  | 40                   | ns    |

| T <sub>h,agcreset</sub> | Input hold time                     | To execute AGC settling | 5                   | 8   | -                    | μs    |

|                         |                                     | To set AGC to max. Gain | -                   | 0.5 | 1                    | μs    |

| T <sub>restart</sub>    | Time between AGC cycles (Note 1)    |                         | 1                   |     | -                    | μs    |

| AGCSET ti               | ming                                |                         |                     |     |                      |       |

| T <sub>drxon</sub>      | Settling time after switching to Rx |                         | -                   | -   | 5                    | μs    |

| T <sub>reset</sub>      | Clearing time after AGCRESET        |                         | _                   | _   | 180                  | ns    |

| T <sub>dsettle</sub>    | AGC settling time                   |                         | Ī-                  | _   | 11                   | μs    |

### NOTES:

<sup>1.</sup> In certain time interval further AGCRESET rising edges will not be detected. This applies for  $4.3 \,\mu s < T_{restart} < 4.8 \,\mu s$ .

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

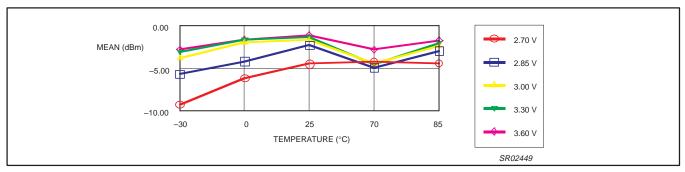

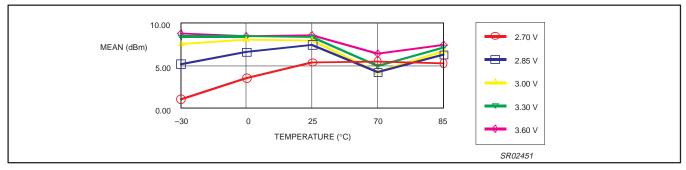

### 10. SA2400A TRANSMITTER

The IQ baseband input signal used is 11 Msymbols/sec QPSK with pulse shaping and 44 MHz D/A sampling rate. The source EVM is less than 3%. The LO frequency is the same as the Transmitter channel center frequency, as the transmit IF input is at 0 Hz.

Table 8. SA2400A Transmitter properties

$T_{amb} = 25 \, ^{\circ}C; \, V_{CC} = 3.3 \, V.$

| Specification                                 | Conditions                                                                                                                                |                                                                                            | Min                | Тур              | Max                | Units      |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|------------------|--------------------|------------|

| RF output frequency                           | Typical                                                                                                                                   |                                                                                            | 2.4                | -                | 2.5                | GHz        |

| RF output power incl balun,                   | Output1, maximum                                                                                                                          |                                                                                            | 4.5                | 8.0              | -                  | dBm        |

| for a CCK modulated signal                    | Output2, maximum                                                                                                                          |                                                                                            | <b>-</b> 5         | -1.5             | -                  | dBm        |

| Gain step size                                | Output1 and Output2                                                                                                                       |                                                                                            | -                  | 1                | -                  | dB         |

| # gain steps                                  | Output1 and Output2                                                                                                                       |                                                                                            | -                  | 15               | -                  |            |

| Spectral Mask (Output1)                       | -11 to + 11 MHz, 100 kHz band                                                                                                             |                                                                                            | -                  | -                | 0                  | dBc        |

| Note 1.                                       | -22 to -11 and 11 to 22 MHz, 100 kHz band                                                                                                 |                                                                                            | -                  | -40              | -36                | dBc        |

|                                               | < –22, > 22 MHz, 100 kHz band                                                                                                             |                                                                                            | -                  | -60              | <del>-56</del>     | dBc        |

| Spectral Mask (Output2)<br>Note 1.            | -11 to + 11 MHz, 100 kHz band<br>-22 to -11 and 11 to 22 MHz, 100 kHz band                                                                |                                                                                            | -                  | -                | 0                  | dBc<br>dBc |

| Note 1.                                       | <-22, > 22 MHz, 100 kHz band                                                                                                              |                                                                                            | _                  | _                | -30<br>-50         | dBc        |

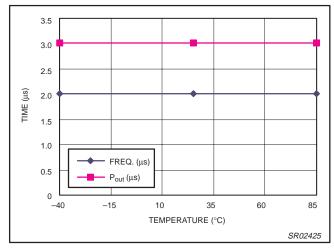

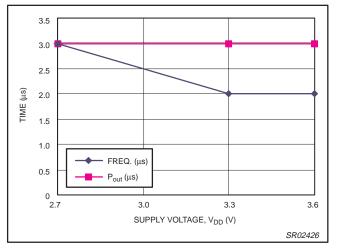

| Power ramping up time                         | 10% to 90% ramp up. Note 2.                                                                                                               |                                                                                            | _                  | 0.5              | _                  | μs         |

| Power ramping up delay                        | From programming to TRANSMIT mode (TXRX mo                                                                                                | ode, or 0-to-1                                                                             | <del> </del> _     | 2                | <del> </del>       | μs         |

| (Note 3)                                      | change of TX/RX pin). Note 2.                                                                                                             | 740, 01 0 10 1                                                                             |                    | -                |                    | ا          |

| Power ramping down                            | Note 2.                                                                                                                                   |                                                                                            |                    |                  |                    |            |

|                                               | a) 90% to 10% ramp down                                                                                                                   |                                                                                            | _                  | 0.5              | -                  | μs         |

|                                               | b) 10% to carrier leakage level                                                                                                           |                                                                                            |                    | 0.5              | -                  | μs         |

| Carrier Leakage                               | Analog input mode selected. No signal input, only of                                                                                      | quiescent current.                                                                         |                    |                  |                    |            |

|                                               | a) Uncalibrated b) Calibrated                                                                                                             |                                                                                            | _                  | -<br> -40        | -25<br>-30         | dBc<br>dBc |

|                                               | Digital input mode selected.                                                                                                              |                                                                                            | _                  | -40<br>-40       | -30<br>-28         | dBc        |

| Carrier Leakage Adjustment                    | Adjustment range of input current offset                                                                                                  |                                                                                            | -<br>-10           | _ <del>4</del> 0 | +10                | μА         |

|                                               | , , ,                                                                                                                                     |                                                                                            | 22                 | _                | -                  | dΒ         |

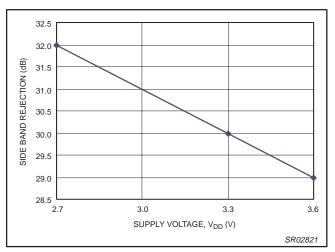

| Residual Sideband Rejection                   | Includes both IQ phase and gain imbalance                                                                                                 | ith an authorise                                                                           | <b></b>            |                  |                    | -          |

| Error Vector Magnitude                        | 11 Msymbols/s QPSK. Both RF outputs. Measured gain. Note 2.                                                                               | with maximum                                                                               | _                  | 12               | 14                 | %          |

| RX to TX switching time                       | Note 2. a) Output power within 1 dB of final value. Includes power-up delay and ramping.                                                  | 2.5 μs for                                                                                 | -                  | 3                | 3.5                | μs         |

|                                               | b) Frequency step settles to within 25 ppm of final v                                                                                     | /alue                                                                                      | _                  | 3                | 3.5                | μs         |

| IQ filter bandwidth                           | Upper 3 dB cut off frequency, after calibration. No                                                                                       | te 2.                                                                                      | 9.25               | 9.75             | 10.25              | MHz        |

| In-band IQ Common Mode<br>Rejection Ratio     | 1–6 MHz common mode signal at –30 dBc relative signal. Measured at upconverted transmitter output                                         |                                                                                            | 30                 | -                | -                  | dB         |

| Out-of-band IQ Common<br>Mode Rejection Ratio | 22–100 MHz common mode signal at –10 dBc rela differential signal. Measured at upconverted transm relative to in-band 1 MHz tone. Note 2. |                                                                                            | 40                 | _                | -                  | dB         |

| IQ input signal current range                 | Into each arm of differential inputs that sink current Analog input selected. Note 4.                                                     | Into each arm of differential inputs that sink current to ground.                          |                    | -                | 550                | μА         |

| IQ input quiescent current                    | Into each arm of differential inputs that sink current to ground.  Analog input selected.                                                 |                                                                                            | -                  | 300              | _                  | μА         |

| Resulting I/Q bias voltage                    | With 300 $\mu\text{A}$ quiescent current into each arm of diff Analog input selected.                                                     | With 300 μA quiescent current into each arm of differential inputs. Analog input selected. |                    | 0.7              | 0.8                | ٧          |

| IQ AC input impedance                         | Analog input selected.                                                                                                                    |                                                                                            | -                  | 320              | -                  | Ω          |

| IQ input voltage                              | Digital input selected                                                                                                                    | Logic LOW                                                                                  | _                  | -                | 0.2V <sub>DD</sub> | V          |

| _                                             |                                                                                                                                           | Logic HIGH                                                                                 | 0.8V <sub>DD</sub> | _                | <u> </u>           | V          |

### Single chip transceiver for 2.45 GHz ISM band

SA2400A

| Specification   | Conditions              |             | Min | Тур | Max | Units |

|-----------------|-------------------------|-------------|-----|-----|-----|-------|

| IQ input timing | 3                       | Set-up time | _   | 4   | _   | ns    |

|                 | relative to REF_CLK_OUT | Hold time   | _   | 4   | _   | ns    |

### NOTES:

- 1. The 44 MHz common mode digital ground bounce on the I and Q inputs is assumed to be less than -30 dBc relative to signal level.

- 2. Verified by bench characterization and found to have sufficient margin for production.

- 3. The power ramping-up delay can be programmed to 2, 3, 4, 5 µs. See the 3-wire bus control register map. The default is 2 µs.

- 4. The differential input signal current is the difference between the I and /I (Q and /Q) instantaneous currents. The peak differential current is therefore  $(I_{max}-I_{min})/2 = 500 \mu A$ .

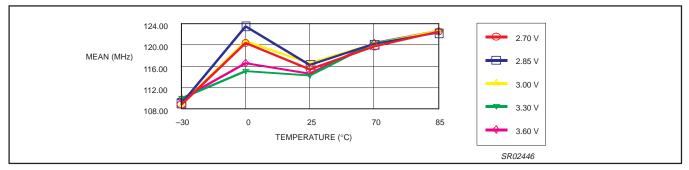

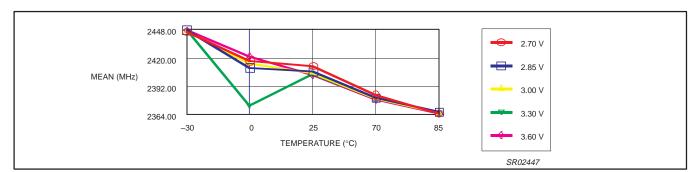

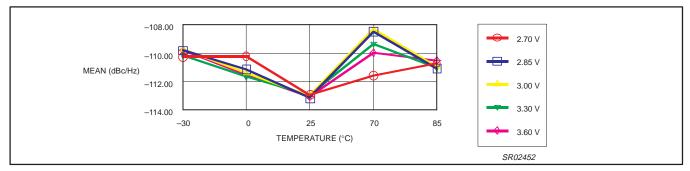

#### 11. VCO AND SYNTHESIZER

Table 9 lists the synthesizer specifications. The synthesizer has the same specification as the SA8027 fractional PLL main loop without the PHI speed-up mode. The phase comparator frequency used is typically 4 MHz (in fractional mode). The charge pump current is internally programmed using the 3-wire bus (Synthesizer Register C). The recommended charge pump current is 480  $\mu$ A. An external reference input of 44 MHz or 22 MHz is supported.

### Table 9. Synthesizer and VCO Specifications

$T_{amb} = 25 \, ^{\circ}C; \, V_{CC} = +3 \, V$

| DADAMETED                                             | TEST SOMBITIONS                                          | LIMITS     |          |                       |           |  |

|-------------------------------------------------------|----------------------------------------------------------|------------|----------|-----------------------|-----------|--|

| PARAMETER                                             | TEST CONDITIONS                                          | Min        | Тур      | Max                   | UNITS     |  |

| VCO                                                   | <u> </u>                                                 | •          |          | <u> </u>              |           |  |

| VCO output frequency range                            |                                                          | 2.4        | <b></b>  | 2.5                   | GHz       |  |

| VCO gain (K <sub>VCO</sub> )                          | V <sub>tune</sub> = 1.2 V                                | 70         | 85       | 100                   | MHz/V     |  |

| Open Loop VCO Phase Noise                             | Note 1. 1/f <sup>2</sup> roll off region; 0.5 MHz offset | Ī-         | -113     | -107                  | dBc/Hz    |  |

| External VCO input levels                             | Differential; when device configured for external VCO    | -10        | -        | 0                     | dBm       |  |

| Main divider                                          | •                                                        |            |          | •                     |           |  |

| N divider range                                       |                                                          | 512        | -        | 65535                 |           |  |

| Reference divider                                     | •                                                        |            | •        |                       |           |  |

| Fixed reference input (XTAL_1 and XTAL_2)             |                                                          | 1-         | 22       | -                     | MHz       |  |

| frequency                                             |                                                          |            | 44       | _                     | MHz       |  |

| R divider range (non-fractional)                      | SM = '000'                                               | 4          | _        | 1023                  |           |  |

| Reference input level                                 | XTAL_1 input                                             | 350        | _        | 1300                  | $mV_{pp}$ |  |

| Input parallel resistance (XTAL_1, XTAL_2)            | f = 44 MHz; indicative, not tested                       | 10         | <b>-</b> | -                     | kΩ        |  |

| Input parallel capacitance (XTAL_1, XTAL_2)           | f = 44 MHz; indicative, not tested                       | T-         | T-       | 1.5                   | pF        |  |

| Phase detector                                        |                                                          |            |          |                       |           |  |

| Phase detector frequency                              |                                                          | T-         | T-       | 4.0                   | MHz       |  |

| Charge pump                                           |                                                          |            |          |                       |           |  |

| Charge pump current accuracy                          | $V_{cp} = 0.5 V_{CC}$                                    | -20        | T-       | +20                   | %         |  |

| Charge pump compliance voltage                        |                                                          | 0.6        | T-       | V <sub>DD</sub> – 0.7 | V         |  |

| Output current variation vs. V <sub>cp</sub> (Note 2) | V <sub>cp</sub> in compliance range                      | <b>-</b> 5 | -        | +5                    | %         |  |

| Charge pump sink to source current<br>Matching        | $V_{cp} = 0.5 V_{CC}$                                    | -10        | -        | +10                   | %         |  |

| Charge pump "off" current leakage                     | $V_{CD} = 0.5 V_{CC}$                                    | <b>-</b> 5 | ±1       | 5                     | nA        |  |

#### NOTES:

- 1. This is measured at the Output1 RF port with the SA2400A in transmit mode, with static DC offset signals to the transmitter I and Q inputs. The phase detector and divide-by-N phase noise is such that when configured as a phase locked loop with a 30 kHz loop band width, the phase noise at frequencies between 1 kHz and 30 kHz will be no worse than –80 dBc/Hz. The total closed loop spur power within a 22 MHz band around the carrier is less than –30 dBc.

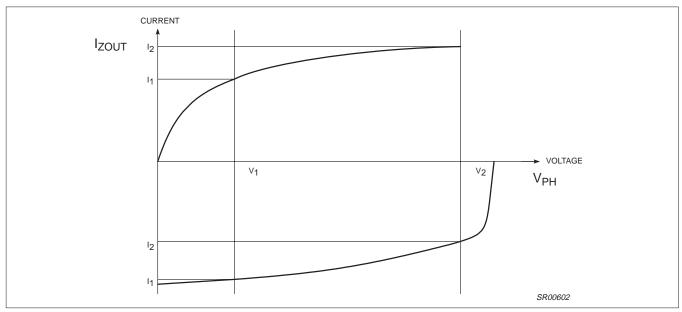

- 2. The relative output current variation is defined as:  $\frac{\Delta I_{ZOUT}}{I_{OUT}} = 2 \times \frac{(I_2 I_1)}{|I_2 + I_1|}$  with  $I_1 @ V_1 = 0.6 \text{ V}, I_2 @ V_2 = V_{CC} 0.7 \text{ V}$  (see Figure 4).

### Single chip transceiver for 2.45 GHz ISM band

SA2400A

Figure 4.

### 12. FUNCTIONAL DESCRIPTION

### 12.1 Main Fractional-N divider

The divider consists of a fully programmable bipolar prescaler followed by a CMOS counter. Total divide ratios range from 512 to 65535.

At the completion of a main divider cycle, a main divider output pulse is generated which will drive the main phase comparator. Also, the fractional accumulator is incremented by the value of NF. The accumulator works with modulo Q set by FM (Synthesizer Register A). When the accumulator overflows, the overall division ratio N will be increased by 1 to N + 1, the average division ratio over Q main divider cycles (either 5 or 8) will be

$$Nfrac = N + \frac{NF}{Q}$$

The output of the main divider will be modulated with a fractional phase ripple. The phase ripple is proportional to the contents of the fractional accumulator and is nulled by the fractional compensation charge pump.

The reloading of a new main divider ratio is synchronized to the state of the main divider to avoid introducing a phase disturbance.

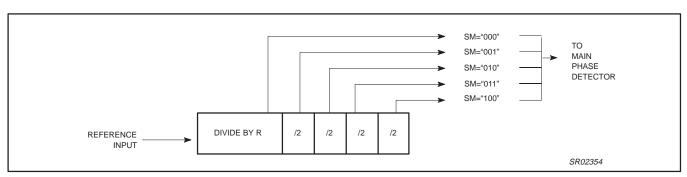

### 12.2 Reference divider

The reference divider consists of a divider with programmable values between 4 and 1023 followed by a 3-bit binary counter. The 3-bit SM register (see Figure 5) determines which of the five output pulses are selected as the main phase detector input.

Figure 5. Reference Divider

## Single chip transceiver for 2.45 GHz ISM band

SA2400A

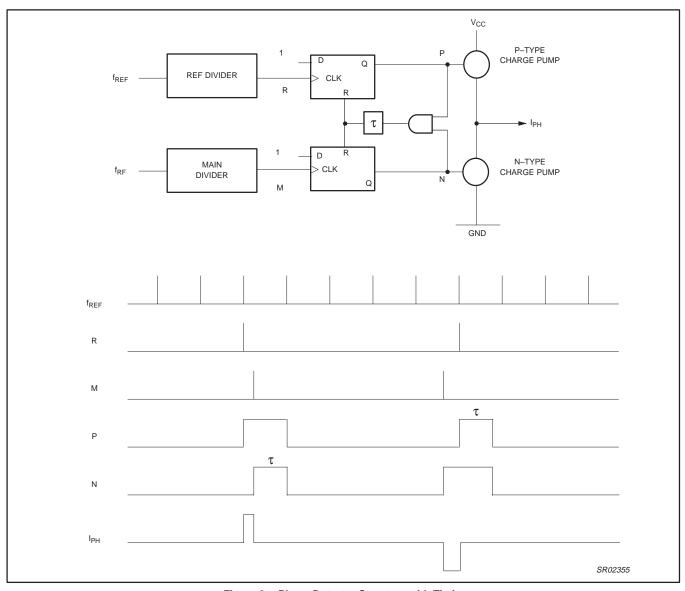

### 12.3 Phase detector (see Figure 6)

The reference and main divider outputs are connected to a phase/frequency detector that controls the charge pump. The pump current is set by the control bit CP (Synthesizer Register C). The

dead zone (caused by finite time taken to switch the current sources on or off) is cancelled by forcing the pumps ON for a minimum time  $(\tau)$  at every cycle (backlash time) providing improved linearity.

Figure 6. Phase Detector Structure with Timing

### Single chip transceiver for 2.45 GHz ISM band

SA2400A

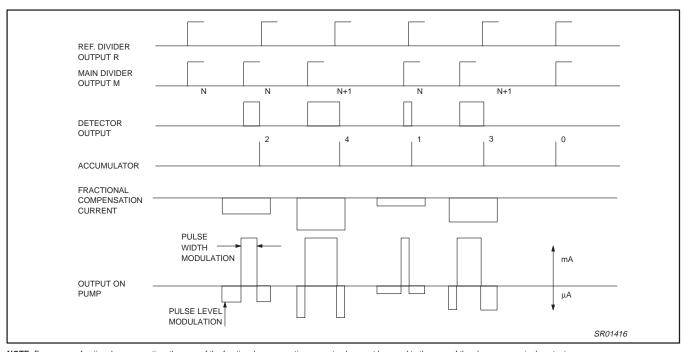

## 12.4 Main output charge pumps and fractional compensation currents (see Figure 7)

The main charge pumps on pin CP are driven by the main phase detector and the charge pump current value is determined by bit CP (Synthesizer Register C). The fractional compensation is derived from the contents of the fractional accumulator FRD and by the program value of the FDAC. The timing for the fractional compensation is derived from the main divider. The charge pumps will enter speed-up mode after sending a Synthesizer Register A word and stays active until a different word is sent.

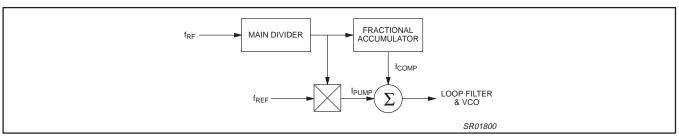

### 12.5 Principle of fractional compensation

The fractional compensation is designed into the circuit as a means of reducing or eliminating fractional spurs that are caused by the fractional phase ripple of the main divider. If  $I_{COMP}$  is the compensation current and  $I_{PLJMP}$  is the pump current:

The compensation is done by sourcing a small current, I<sub>COMP</sub>, see Figure 8, that is proportional to the fractional error phase. For proper fractional compensation, the area of the fractional compensation current pulse must be equal to the area of the fractional charge pump ripple. The width of the fractional compensation pulse is fixed to 128 VCO cycles, the amplitude is proportional to the fractional

accumulator value and is adjusted by FDAC values (bits FC7–0 in Synthesizer B). The fractional compensation current is derived from the main charge pump in that it follows all the current scaling through programming or speed-up operation. For a given charge pump,

$$I_{COMP} = (I_{PUMP} / 128) * (FDAC / 5*128) * FRD$$