# HT16525 5x8 Dot Character VFD Controller & Driver

### Feature

- Logic voltage : 2.7V~5.5V

- High voltage: 60V (max.)

- 3-line serial interface

- Alphanumeric and symbolic display using integrated ROM

- 24 x 8-bit display data RAM (DDRAM)

- Integrated 5x8 dot ROM containing 248 character set

- 8 user-defined characters stored in character data RAM (CGRAM)

- Additional symbol display data stored in 24 x 8-bit RAM (ADRAM)

- Display content: 24 columns by 1 row + 48 symbols - each column has 1 digit character with 2 symbols

- Supports display output: 40-segment & 24-grid

- Supports symbol output: 2-symbol & 24-grid

- Supports 2-pin general output port static operation

- · Fully integrated oscillator circuit

**Ordering Information**

• 80-pin LQFP package

# Applications

- · Consumer products panel function control

- Industrial measuring instrument panel function control

- Other similar application panel function control

- · Suitable for POS terminals or message displays

### **General Description**

The HT16525 device is a dot matrix Vacuum Fluorescent Display, VFD, controller/driver which displays characters, numerics and symbols. Dot matrix VFD driving signals are received via a 3-line serial interface driven by an externally connected microcontroller. The display data is stored in the internal ROM and RAM for character and symbol display.

| ĺ | Part Number | Information                           |

|---|-------------|---------------------------------------|

|   | HT16525-001 | 80-pin LQFP package with ROM code 001 |

|   | HT16525-002 | 80-pin LQFP package with ROM code 002 |

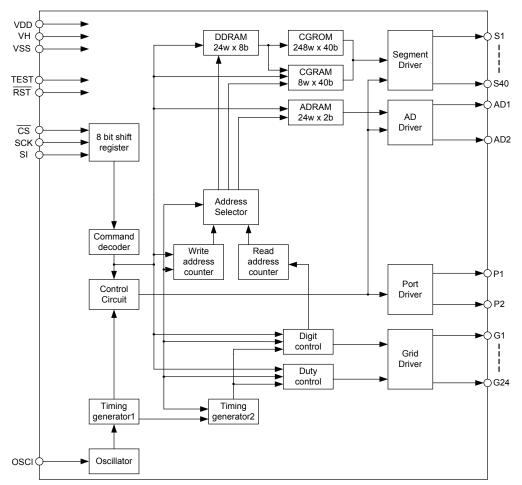

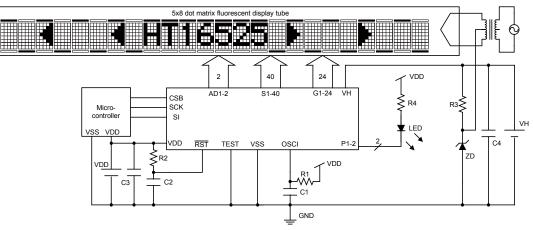

### **Block Diagram**

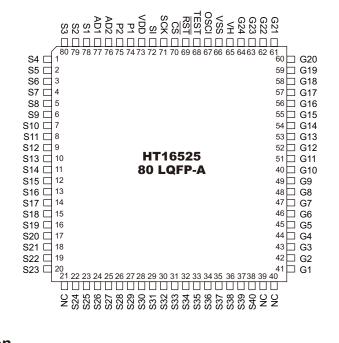

### **Pin Assignment**

### **Pin Description**

| Pin Name              | I/O       | Description                                                                                                       |  |  |  |  |  |  |

|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Power Supply Pins     |           |                                                                                                                   |  |  |  |  |  |  |

| VDD                   | _         | Positive power supply for logic circuits                                                                          |  |  |  |  |  |  |

| VH                    | —         | Power supply for VFD driver circuits                                                                              |  |  |  |  |  |  |

| VSS                   | _         | VSS - ground pin                                                                                                  |  |  |  |  |  |  |

| Microcontroller Inter | face Pins |                                                                                                                   |  |  |  |  |  |  |

| CS                    | I         | Chip select pin<br>When "Low", the device is active.                                                              |  |  |  |  |  |  |

| SCK                   | I         | Serial clock input<br>Shift clock input with data written on the SCK rising edge.                                 |  |  |  |  |  |  |

| SI                    | I         | Serial data input.<br>The serial data is first shifted from LSB.                                                  |  |  |  |  |  |  |

| RST                   | I         | Initialize all the internal registers and commands.<br>All segments and digits are fixed at "Low" level.          |  |  |  |  |  |  |

| TEST                  | I         | When "Low" or open, the device is in normal mode.<br>When "High", the device is in test mode.                     |  |  |  |  |  |  |

| Output Pins           |           |                                                                                                                   |  |  |  |  |  |  |

| S1~S40                | 0         | High-voltage segment output pins.                                                                                 |  |  |  |  |  |  |

| G1~G24                | 0         | High-voltage grid output pins.                                                                                    |  |  |  |  |  |  |

| AD1, AD2              | 0         | High-voltage additional data segment output pins.                                                                 |  |  |  |  |  |  |

| P1, P2                | 0         | General port output.<br>Static operation output - can drive LEDs                                                  |  |  |  |  |  |  |

| Oscillator Pin        |           |                                                                                                                   |  |  |  |  |  |  |

| OSCI                  | I         | Oscillator input pin<br>Connected to an external resistor and capacitor to generate the oscillation<br>frequency. |  |  |  |  |  |  |

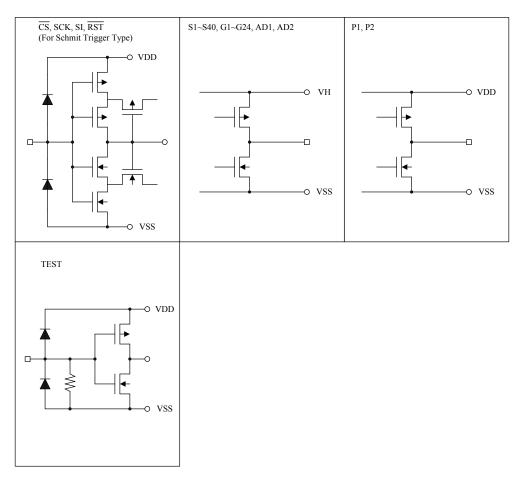

### **Approximate Internal Connections**

## **Absolute Maximum Ratings**

| Logic Supply Voltage  | . Vss-0.3V to Vss+6.0V       |

|-----------------------|------------------------------|

| Driver Supply Voltage | Vss-0.3V to Vss+66V          |

| Input Voltage         | . Vss-0.3V to $V_{DD}$ +0.3V |

| Output Voltage        | . Vss-0.3V to $V_{DD}$ +0.3V |

| Grid output current   | -20mA to 4mA                 |

| Segment output current      | 10mA to 4mA   |

|-----------------------------|---------------|

| AD output current           | 15mA to 4mA   |

| General port output current | 20mA to 40mA  |

| Storage Temperature         | 55°C to 125°C |

| Operation Temperature       | 40°C to 85°C  |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# **D.C. Characteristics**

$V_{H}$ =50V,  $V_{SS}$ =0V, Ta=-40°C ~ 85°C

|                                   |                             |                                    | Test Conditi                                                                            | on                                               |                    | , • 55 • • | , 1a40             |    |

|-----------------------------------|-----------------------------|------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------|--------------------|------------|--------------------|----|

| Symbol                            | Parameter                   | V <sub>DD</sub>                    | Condit                                                                                  | Min.                                             | Тур.               | Max.       | Unit               |    |

| V <sub>DD</sub>                   | Logic Supply Voltage        | ♥ DD                               |                                                                                         | 2.7                                              | 5.0                | 5.5        | V                  |    |

| V <sub>DD</sub><br>V <sub>H</sub> | VFD Supply Voltage          |                                    |                                                                                         |                                                  |                    |            | 60                 | V  |

|                                   |                             | 5V                                 | f <sub>osc</sub> =2MHz, no loa<br>Digit=1 to 24, All                                    |                                                  | 20<br>—            | _          | 2                  |    |

| I <sub>DD1</sub>                  | VDD Operating Current       | 3V                                 | ON, MCU no w<br>command, P2 and                                                         | rite data or                                     | _                  | _          | 1                  | mA |

| I <sub>DD2</sub>                  | VDD Operating Current       | 5V                                 | f <sub>osc</sub> =2MHz, no loa<br>Digit=1 to 24, Sto                                    |                                                  |                    | _          | 2                  | mA |

| DD2                               | VDD Operating Current       | 3V                                 | no write data or<br>and P1=high                                                         | command, P2                                      | _                  | _          | 1                  |    |

| I <sub>STB</sub>                  | VDD Standby Current         | 5V                                 | Standby mode                                                                            |                                                  |                    | 2          | —                  | μA |

| 'STB                              |                             | 3V                                 |                                                                                         |                                                  | —                  | 2          |                    | μΛ |

| I <sub>H1</sub>                   | VH Operating Current        |                                    | f <sub>osc</sub> =2MHz, no loa<br>Digit=1 to 24, All<br>ON, MCU no w<br>command, P2 and | output lights                                    | _                  | _          | 1                  | mA |

| I <sub>H2</sub>                   | VH Operating Current        |                                    | f <sub>osc</sub> =2MHz, no loa<br>Digit=1 to 24, Sto<br>no write data or<br>and P1=high | op scan, MCU                                     | _                  |            | 20                 | μA |

| I <sub>H_STB</sub>                | VH Standby Current          | _                                  | Standby mode                                                                            |                                                  | _                  | _          | 20                 | μA |

| V <sub>IH</sub>                   | High Level Input Voltage    | 5V<br>3V                           | CS, SCK, SI, RST                                                                        |                                                  | 0.8V <sub>DD</sub> | _          | _                  | V  |

| V <sub>IL</sub>                   | Low Level Input Voltage     | 5V<br>3V                           | CS, SCK, SI, RST                                                                        |                                                  | _                  | _          | $0.2V_{\text{DD}}$ | V  |

| I <sub>IH</sub>                   | High Level Input Current    | 5V<br>3V                           | $V_{IH} = V_{DD}, \overline{CS}, SCK$                                                   | , SI, <del>RST</del>                             | _                  | _          | 1                  | μA |

| I                                 | Low Level Input Current     | 5V<br>3V                           | V <sub>IL</sub> =0V, CS, SCK,                                                           | SI, RST                                          | -1                 | _          | _                  | μA |

| V <sub>OH1</sub>                  |                             | 5V<br>3V                           | G1~G24, I <sub>OH1</sub> =-15                                                           | mA                                               | 45                 | _          | _                  | V  |

| V <sub>OH2</sub>                  |                             | 5V<br>3V                           | AD1, AD2, I <sub>OH2</sub> =-7                                                          | mA                                               | 46                 | _          | _                  | V  |

| V <sub>OH3</sub>                  | - High Level Output Voltage | 5V<br>3V                           | S1~S40, I <sub>онз</sub> =-1m                                                           | A                                                | 46                 | _          | _                  | V  |

| .,                                |                             | 5V                                 | D4 D0                                                                                   | I <sub>OH4</sub> =-2mA                           | 0.9V <sub>DD</sub> | _          | _                  |    |

| $V_{OH4}$                         |                             | 3V                                 | P1, P2                                                                                  | I <sub>OH4</sub> =-1mA                           | 0.9V <sub>DD</sub> | _          |                    | V  |

| V <sub>OL1</sub>                  |                             | 5V<br>3V<br>G1~G24, I <sub>c</sub> |                                                                                         |                                                  | _                  | _          | 5                  | V  |

| V <sub>OL2</sub>                  |                             | 5V<br>3V                           | AD1, AD2, I <sub>OL2</sub> =1n                                                          | _                                                | _                  | 5          | V                  |    |

| V <sub>ol3</sub>                  | - Low Level Output Voltage  | 5V<br>3V                           | S1~S40, I <sub>oL3</sub> =1mA                                                           | l.                                               | _                  | _          | 5                  | V  |

| V <sub>OL4</sub>                  |                             | 5V<br>3V                           | P1, P2                                                                                  | I <sub>OL4</sub> =20mA<br>I <sub>OL4</sub> =10mA | _                  | _          | 1                  | V  |

|                                   |                             |                                    | -0L4                                                                                    |                                                  |                    |            |                    |    |

| R <sub>PD</sub>                   | Pull Down Resistor          | 5V                                 | TEST Pin                                                                                |                                                  |                    | 50         | 100                | kΩ |

# A.C. Characteristics

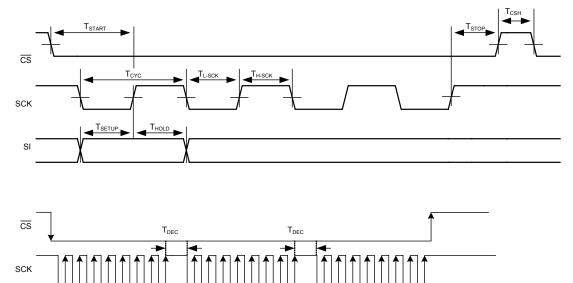

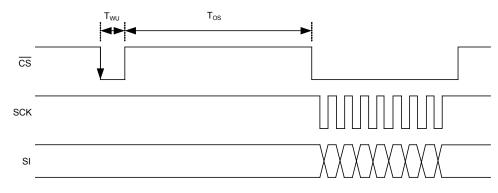

### **Serial Interface Timing**

B0 B1

B2 B3 B4

3rd byte

B5 B6 B7

B0 B1 B2 B3 B4 B5 B6 B7

2nd byte

SI

B0 B1 B2

B3 B4

B4 B5 B6 B7

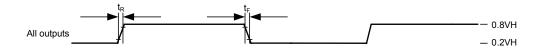

### **Output Timing**

$V_{\rm H}\text{=}50\text{V},\,V_{\rm SS}\text{=}0\text{V},\,\text{Ta}=\text{-}40^{\circ}\text{C}\sim85^{\circ}\text{C}$

| Symbol             | Parameter                |                 | Test Condition                        | Min.       | Turn | Max.  | Unit |

|--------------------|--------------------------|-----------------|---------------------------------------|------------|------|-------|------|

| Symbol             | Parameter                | V <sub>DD</sub> | Condition                             | wiin.      | Тур. | WidA. | Onit |

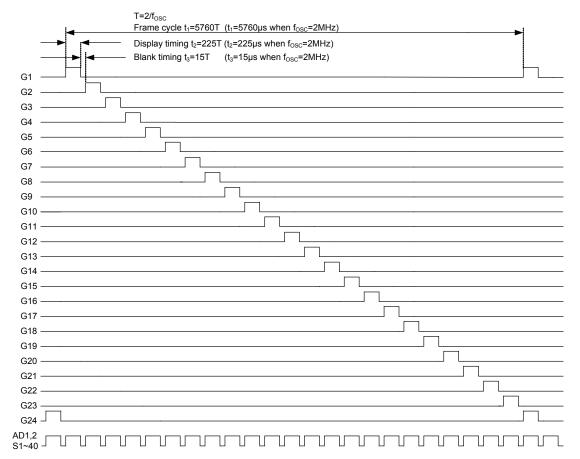

| f <sub>osc</sub>   | Oscillation Frequency    | 5V<br>3V        | R1=120kΩ, C1=0.1μF                    | 1.5        | 2    | 2.5   | MHz  |

| f <sub>FR</sub>    | Frame Frequency          | 5V<br>3V        | Digit=1 to 24, R1=120kΩ,<br>C1=0.1μF  | 130        | 175  | 220   | Hz   |

| T <sub>CYC</sub>   | Write Cycle Time         | 5V<br>3V        | SCK                                   |            | _    | 2     | MHz  |

| T <sub>L-SCK</sub> | Low Pulse of SCK         | 5V<br>3V        | зск                                   | 250<br>250 |      | _     | ns   |

| Т <sub>н-scк</sub> | High Pulse of SCK        |                 | зск                                   | 250<br>250 |      |       | ns   |

| T <sub>SETUP</sub> | Data Setup Time          | 3V<br>5V<br>3V  | SCK, SI                               | 250<br>250 |      |       | ns   |

| T <sub>HOLD</sub>  | Data Hold Time           | 5V<br>3V        | SCK, SI                               | 250<br>250 |      |       | ns   |

| T <sub>start</sub> | Command Start Wait Time  | 5V<br>3V        | SCK, SI                               | 250<br>250 |      |       | ns   |

| T <sub>STOP</sub>  | Command Stop Wait Time   | 5V<br>3V        | SCK, CS                               | 16<br>16   |      |       | μs   |

| Т <sub>сsн</sub>   | CS Off Time              | 5V<br>3V        |                                       | 250<br>250 |      |       | ns   |

| T <sub>DEC</sub>   | Command/Data Decode Time | 5V<br>3V        |                                       | 8          |      |       | μs   |

| t <sub>R</sub>     |                          | 5V<br>3V        | - Ci=100pF, t <sub>R</sub> =20 to 80% | _          |      | 2     | μs   |

| t <sub>F</sub>     | All Output Slew Rate     | 5V<br>3V        | −Ci=100pF, t <sub>F</sub> =80 to 20%  | _          | _    | 2     | μs   |

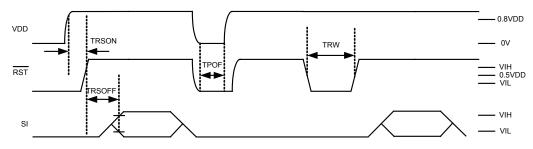

### **Reset and Wake-up Timing**

Hardware Reset

| Symbol             | Parameter              |    | Test Condition                   | Min.    | Tun  | Max. | Unit |

|--------------------|------------------------|----|----------------------------------|---------|------|------|------|

| Symbol             | Arameter               |    | Condition                        | IVIIII. | Тур. | Wax. | Unit |

|                    |                        | 5V | RST signal is an external input  | 250     | —    | —    | 20   |

| -                  | Oscillator Stable Time | 3V | from a microcontroller etc.      | 250     | _    | _    | ns   |

| T <sub>RSON</sub>  |                        | 5V | R2=1kΩ、C2=0.1μF                  | _       | 1000 | _    |      |

|                    |                        | 3V | $R_2 = 1R_2$ , $C_2 = 0.1 \mu F$ | _       | 1000 | _    | μs   |

| -                  | VDD Off Time           | 5V | VDD drag down to 0)/             | 40      | —    | —    | μs   |

| T <sub>POF</sub>   |                        | 3V | VDD drop down to 0V              | 10      | —    | —    | ms   |

| -                  |                        | 5V | RST signal is an external input  | 400     | _    | _    |      |

| T <sub>RW</sub>    | RST Pulse Width        | 3V | from a microcontroller etc.      | 400     | —    | _    | ns   |

| -                  | SI Wait Time           | 5V |                                  | 3       | _    | _    | μs   |

| I <sub>RSOFF</sub> |                        | 3V |                                  | 3       | —    | _    |      |

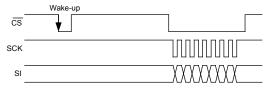

#### Wake-up Timing

Ta=-40°C ~ 85°C

| Symbol | Parameter                 |                 | Test Condition | Min.   | Тур. | Max. | Unit |

|--------|---------------------------|-----------------|----------------|--------|------|------|------|

| Symbol | Fardineter                | $V_{\text{dd}}$ | Condition      | IVIII. |      |      |      |

| -      | Mala an Ting              |                 |                | 200    |      |      |      |

| I WU   | Wake-up Time              | 3V              |                | 200    | _    | _    | ns   |

| -      | Os sillation Otable Times | 5V              |                | 1000   |      |      |      |

| Los    | Oscillation Stable Time   | 3V              |                | 1000   |      |      | μs   |

### **Digit Output Timing**

#### For 24-digits display, at a duty of 15/16

### Segment and AD Position

Positional relationship between S1~S40 and AD1 ~ AD2 - single digit

# **Command Table**

| Function                      | Byte | R/W | Bit7<br>(MSB) | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0<br>(LSB) | Note                                                                                                                          | Default |

|-------------------------------|------|-----|---------------|------|------|------|------|------|------|---------------|-------------------------------------------------------------------------------------------------------------------------------|---------|

|                               |      |     | 1             |      |      |      |      |      |      |               | 1                                                                                                                             |         |

| DDRAM<br>data write           | 1st  | W   | 0             | 0    | 0    | X4   | Х3   | X2   | X1   | X0            | Xn: Address specification<br>for each RAM                                                                                     | 00H     |

| DDRAM<br>data                 | 2nd  | W   | C7            | C6   | C5   | C4   | C3   | C2   | C1   | C0            | Cn: character code specification for each RAM                                                                                 | _       |

| CGRAM<br>data write           | 1st  | W   | 0             | 0    | 1    | *    | *    | X2   | X1   | X0            | Xn: Address specification<br>for each RAM                                                                                     | 20H     |

| CGRAM<br>Data                 | 2nd  | W   | C35           | C30  | C25  | C20  | C15  | C10  | C5   | C0            |                                                                                                                               | _       |

| CGRAM<br>Data                 | 3rd  | W   | C36           | C31  | C26  | C21  | C16  | C11  | C6   | C1            |                                                                                                                               |         |

| CGRAM<br>Data                 | 4th  | W   | C37           | C32  | C27  | C22  | C17  | C12  | C7   | C2            | Cn: character code specification for each RAM                                                                                 |         |

| CGRAM<br>Data                 | 5th  | W   | C38           | C33  | C28  | C23  | C18  | C13  | C8   | СЗ            |                                                                                                                               | _       |

| CGRAM<br>Data                 | 6th  | W   | C39           | C34  | C29  | C24  | C19  | C14  | C9   | C4            |                                                                                                                               | _       |

| ADRAM<br>data write           | 1st  | W   | 0             | 1    | 0    | X4   | X3   | X2   | X1   | X0            | Xn: Address specification for each RAM                                                                                        | 40H     |

| ADRAM<br>Data                 | 2nd  | W   | *             | *    | *    | *    | *    | *    | C1   | C0            | Cn: character code specification for each RAM                                                                                 |         |

|                               |      |     |               |      |      | 1    |      |      | 1    |               | 1                                                                                                                             |         |

| General<br>output<br>port set | 1st  | W   | 0             | 1    | 1    | *    | *    | *    | P2   | P1            | Pn: General output port<br>status specification                                                                               | 63H     |

|                               |      |     |               |      |      |      |      |      |      |               |                                                                                                                               |         |

| Display<br>duty set           | 1st  | W   | 1             | 0    | 0    | *    | *    | D2   | D1   | D0            | Dn: display duty<br>specification                                                                                             | 80H     |

|                               |      |     |               |      |      |      |      |      |      |               |                                                                                                                               |         |

| Number<br>of digits<br>set    | 1st  | W   | 1             | 0    | 1    | *    | K3   | K2   | K1   | К0            | Kn: Number of digits specification                                                                                            | A0H     |

|                               |      |     |               |      |      |      |      |      |      |               |                                                                                                                               |         |

| All lights<br>ON/OFF          | 1st  | W   | 1             | 1    | 0    | *    | D    | S    | Н    | L             | D: display on/off instruction<br>S: standby mode instruction<br>H: all lights ON instruction<br>L: all lights OFF instruction | С0Н     |

|                               | ·    |     |               |      | 1    | r    | 1    | 1    | r    |               | 1                                                                                                                             |         |

| TEST<br>mode                  | 1st  | W   | 1             | 1    | 1    | 0    | 0    | 0    | 0    | 0             | For HOLTEK internal<br>testing                                                                                                | E0H     |

#### **Command and Data Transfer Methods**

Complete access to the VFD driver consists of display commands and the display data. The number of the transmitted data bytes for a complete access depends upon the command and memory type as the Command Table shows. The display control commands and data are transmitted using a 3-wire serial interface from the host MCU. The following steps show how the operation of the serial interface circuitry.

- Setting the  $\overline{\text{CS}}$  pin to a "Low" level will enable a data transfer.

- Data is 8-bits wide and is sequentially shifted-in on the SI pin from LSB to MSB (LSB first)

- Data shifted into the register is ready at the rising edge of the serial shift clock SCK. If the 8-bit data is to be written in, then internal signals are automatically generated and the data will be written into the corresponding register and RAM.

- Setting the  $\overline{CS}$  pin to "High" will disable the command and data transfer

- When data is written into the RAM area including DDRAM, ADRAM and CGRAM continuously, the command used to specify the RAM area is contained in the first shifted-in command byte together with the start address. Then the RAM address will be internally incremented by 1 automatically. Therefore, it is not necessary to specify the start address of the data to be written after the command byte.

#### **Reset Function**

When the  $\overline{\text{RST}}$  pin is set to "Low", the module is initialized to the following conditions:

- Address will be reset to 00H for each RAM including DDRAM, ADRAM and CGRAM

- The contents of the RAM including DDRAM, ADRAM and CGRAM are undefined.

- All general output ports go "High".

- Display duty setting will be reset to 8/16 duty (register value D2, D1, D0=0, 0, 0).

- Number of digits setting will be reset to 24 digits (register value K3, K2, K1, K0=0, 0, 0, 0).

- All display lights ON/OFF settings will be switched to the "display off" mode (register value D,S,H,L=0,0,0)

- All segment outputs go "Low".

- · All AD outputs go "Low".

- · All grid outputs go "Low".

- Note: After a power on reset, all the RAM including DDRAM, ADRAM and CGRAM will be cleared.

### **Functional Description**

#### **Timing Generation Circuit**

A timing generation circuit generates timing signals for the operation of internal circuits such as the DDRAM, CGRAM, CGROM and ADRAM.

#### **VFD Driver Circuit**

The VFD driver circuit consists of 24 grid signal drivers and 40 segment signal drivers. When the number of digits are selected by a corresponding command, the required grid signal drivers automatically output drive waveforms, while the other grid signal drivers continue to output non-selection waveforms. Sending serial data is latched when the display data character pattern corresponds to the last address of the display data RAM (DDRAM).

#### Data Display RAM - DDRAM

The Display Data RAM (DDRAM) stores the display data in 8-bit character codes. Its extended capacity is 24x8 bits or 24 characters.

#### **DDRAM Data Write Command**

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|-----|------|------|------|------|------|------|------|------|

| 1st  | W   | 0    | 0    | 0    | X4   | X3   | X2   | X1   | X0   |

| 2nd  | W   | C7   | C6   | C5   | C4   | C3   | C2   | C1   | C0   |

| 3rd  | W   | C7   | C6   | C5   | C4   | C3   | C2   | C1   | C0   |

| 4th  | W   | C7   | C6   | C5   | C4   | C3   | C2   | C1   | C0   |

| :    | :   | :    | :    | :    | :    | :    | :    | :    | :    |

The DDRAM data write command descriptions are shown in the following:

- X4~X0: DDRAM address is for 24 characters addressed from 00H to 17H. The addresses ranged from 18H to 1FH are unused and unavailable addresses.

- C7~C0: character code of the CGROM (internal 248 characters) or CGRAM (user-defined 8 characters)

- To specify the character code of the CGROM or CGRAM continuously, only the character code needs to be specified

- The addresses of the DDRAM are automatically incremented by 1.

- The address will be wrapped around to the start address when the DDRAM data write function is successively executed and the DDRAM address is greater than the maximum available address

| • | Grid positions and set DDRAM addresse | es |

|---|---------------------------------------|----|

|---|---------------------------------------|----|

| HEX | X4 | X3 | X2 | X1 | X0 | Grid Position |

|-----|----|----|----|----|----|---------------|

| 0   | 0  | 0  | 0  | 0  | 0  | G1            |

| 1   | 0  | 0  | 0  | 0  | 1  | G2            |

| 2   | 0  | 0  | 0  | 1  | 0  | G3            |

| 3   | 0  | 0  | 0  | 1  | 1  | G4            |

| 4   | 0  | 0  | 1  | 0  | 0  | G5            |

| 5   | 0  | 0  | 1  | 0  | 1  | G6            |

| 6   | 0  | 0  | 1  | 1  | 0  | G7            |

| 7   | 0  | 0  | 1  | 1  | 1  | G8            |

| 8   | 0  | 1  | 0  | 0  | 0  | G9            |

| 9   | 0  | 1  | 0  | 0  | 1  | G10           |

| A   | 0  | 1  | 0  | 1  | 0  | G11           |

| В   | 0  | 1  | 0  | 1  | 1  | G12           |

| С   | 0  | 1  | 1  | 0  | 0  | G13           |

| D   | 0  | 1  | 1  | 0  | 1  | G14           |

| E   | 0  | 1  | 1  | 1  | 0  | G15           |

| F   | 0  | 1  | 1  | 1  | 1  | G16           |

| 10  | 1  | 0  | 0  | 0  | 0  | G17           |

| 11  | 1  | 0  | 0  | 0  | 1  | G18           |

| 12  | 1  | 0  | 0  | 1  | 0  | G19           |

| 13  | 1  | 0  | 0  | 1  | 1  | G20           |

| 14  | 1  | 0  | 1  | 0  | 0  | G21           |

| 15  | 1  | 0  | 1  | 0  | 1  | G22           |

| 16  | 1  | 0  | 1  | 1  | 0  | G23           |

| 17  | 1  | 0  | 1  | 1  | 1  | G24           |

Note: If the specified address in this command is not defined (X4~X0=18H~1FH), the function will not be changed.

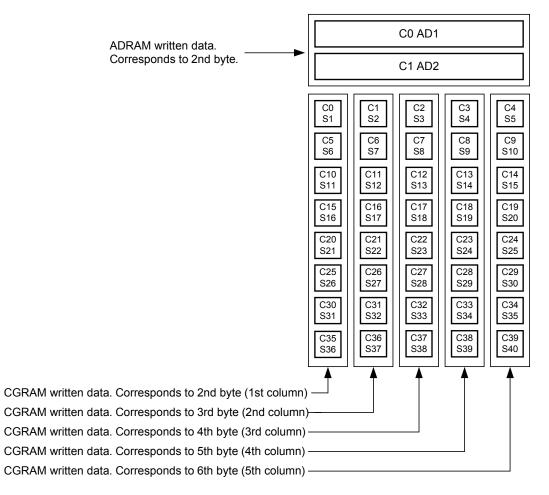

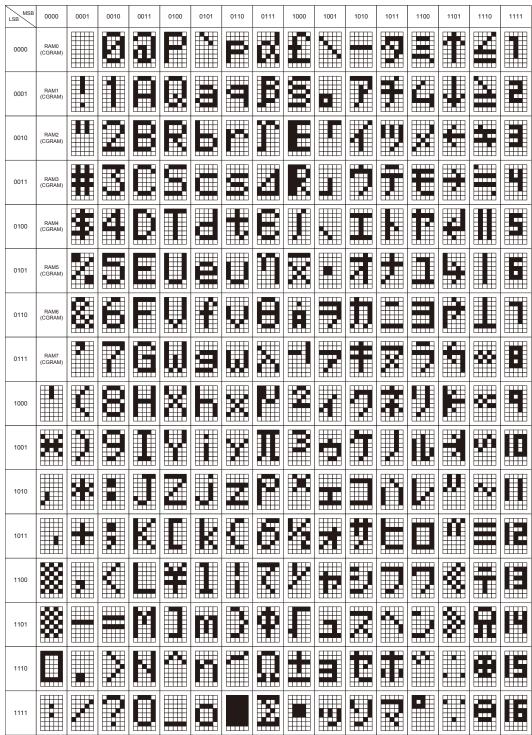

#### **Character Generator ROM - CGROM**

- The CGROM for generating character patterns of 5x8 dots from 8-bit character codes generates 248 types of character patterns

- The character codes are shown on the following page

- · Character codes 00H to 07H are allocated to the CGRAM

Character Code Table for ROM Code 001

Character Code Table for ROM Code 002

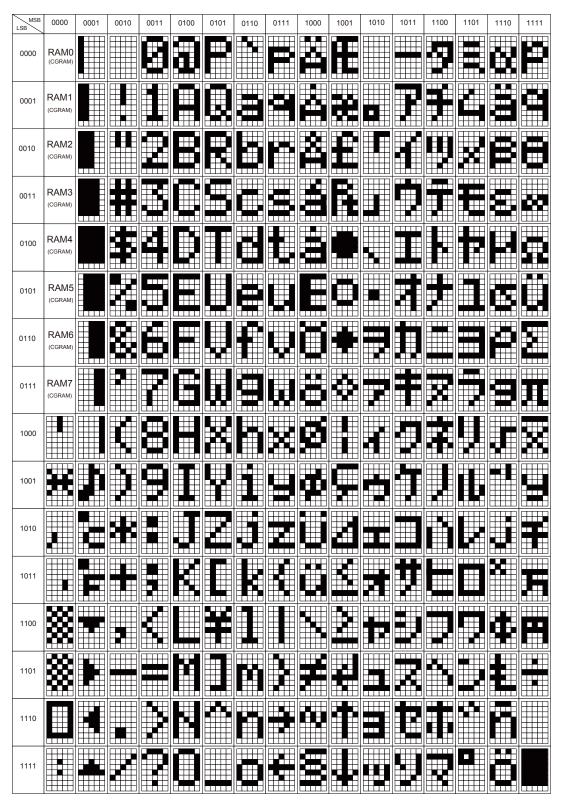

#### **Character Generator RAM - CGRAM**

The CGRAM stores the pixel information (1=pixel on, 0=pixel off) for the eight user-defined 5x7 characters. Valid CGRAM addresses are 00H to 07H. Character codes 00H~07H are assigned to the user-defined characters.

#### **CGRAM Data Write Command**

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|-----|------|------|------|------|------|------|------|------|

| 1st  | W   | 0    | 0    | 1    | *    | *    | X2   | X1   | X0   |

| 2nd  | W   | C35  | C30  | C25  | C20  | C15  | C10  | C5   | C0   |

| 3rd  | W   | C36  | C31  | C26  | C21  | C16  | C11  | C6   | C1   |

| 4th  | W   | C374 | C32  | C27  | C22  | C17  | C12  | C7   | C2   |

| 5th  | W   | C38  | C33  | C28  | C23  | C18  | C13  | C8   | C3   |

| 6th  | W   | C39  | C34  | C29  | C24  | C19  | C14  | C9   | C4   |

\*: Don't care

The CGRAM data write command descriptions are described by the following:

- X2~X0: CGRAM addresses for 8 user-defined characters

- C39~C0: character pattern data, 40-bit outputs per digit. The relationship between the 40-bit character pattern data and the dot positions for each digit is shown in the accompanying diagram.

- A character pattern stored in the CGRAM can be displayed and addressed by the character code specified in the DDRAM

- To specify character pattern data continuously, only the character pattern data needs to be specified

- The addresses of the CGRAM are automatically incremented by 1

- The address will be wrapped around to the start address when the CGRAM data write function is successively executed and the CGRAM address is greater than the maximum available address

- · CGROM addresses and set CGRAM addresses

| HEX | X2 | X1 | X0 | CGRAM | Mapping to<br>CGROM Address |

|-----|----|----|----|-------|-----------------------------|

| 00  | 0  | 0  | 0  | RAM00 | 0000000B                    |

| 01  | 0  | 0  | 1  | RAM01 | 0000001B                    |

| 02  | 0  | 1  | 0  | RAM02 | 00000010B                   |

| 03  | 0  | 1  | 1  | RAM03 | 00000011B                   |

| 04  | 1  | 0  | 0  | RAM04 | 00000100B                   |

| 05  | 1  | 0  | 1  | RAM05 | 00000101B                   |

| 06  | 1  | 1  | 0  | RAM06 | 00000110B                   |

| 07  | 1  | 1  | 1  | RAM07 | 00000111B                   |

• Relationship between the CGRAM output data and the character dot position

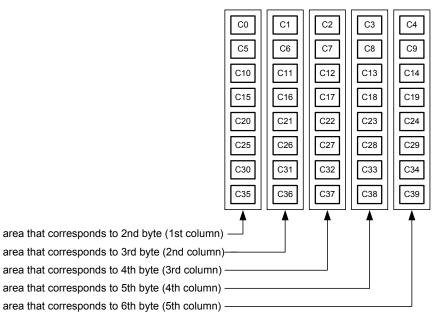

#### Additional Symbol Display RAM - ADRAM

The ADRAM stores the additional symbol information (1=symbol on, 0=symbol off) for the 24 digits. For each 5x8 digit there are two symbols displayed together with the character. The positional relationship is shown in the accompanying diagram.

#### ADRAM Data Write Command

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|-----|------|------|------|------|------|------|------|------|

| 1st  | W   | 0    | 1    | 0    | X4   | X3   | X2   | X1   | X0   |

| 2nd  | W   | *    | *    | *    | *    | *    | *    | C1   | C0   |

| 3rd  | W   | *    | *    | *    | *    | *    | *    | C1   | C0   |

| 4th  | W   | *    | *    | *    | *    | *    | *    | C1   | C0   |

| :    | :   | :    | :    | :    | :    | :    | :    | :    | :    |

\*: Don't care

The ADRAM data write command descriptions are described by the following:

- X4~X0: ADRAM addresses for 24 digits

- C1~C0: 2 bits Symbol data for each digit

- Symbol data specified by the ADRAM is directly output regardless of the CGRAM data and the CGROM code

- The ADRAM can store 2 types of symbol pattern for each digit

- The ADRAM contents output to the terminal can be used as a cursor for each digit

- The address of the ADRAM is automatically incremented by 1

- The address will be wrapped around to the start address when the ADRAM data write function is successively executed and the ADRAM address is greater than the maximum available address

- Grid positions and ADRAM addresses

| HEX | X4 | X3 | X2 | X1 | X0 | <b>Grid Position</b> |

|-----|----|----|----|----|----|----------------------|

| 0   | 0  | 0  | 0  | 0  | 0  | G1                   |

| 1   | 0  | 0  | 0  | 0  | 1  | G2                   |

| 2   | 0  | 0  | 0  | 1  | 0  | G3                   |

| 3   | 0  | 0  | 0  | 1  | 1  | G4                   |

| 4   | 0  | 0  | 1  | 0  | 0  | G5                   |

| 5   | 0  | 0  | 1  | 0  | 1  | G6                   |

| 6   | 0  | 0  | 1  | 1  | 0  | G7                   |

| 7   | 0  | 0  | 1  | 1  | 1  | G8                   |

| 8   | 0  | 1  | 0  | 0  | 0  | G9                   |

| 9   | 0  | 1  | 0  | 0  | 1  | G10                  |

| HEX | X4 | X3 | X2 | X1 | X0 | <b>Grid Position</b> |

|-----|----|----|----|----|----|----------------------|

| Α   | 0  | 1  | 0  | 1  | 0  | G11                  |

| В   | 0  | 1  | 0  | 1  | 1  | G12                  |

| С   | 0  | 1  | 1  | 0  | 0  | G13                  |

| D   | 0  | 1  | 1  | 0  | 1  | G14                  |

| E   | 0  | 1  | 1  | 1  | 0  | G15                  |

| F   | 0  | 1  | 1  | 1  | 1  | G16                  |

| 10  | 1  | 0  | 0  | 0  | 0  | G17                  |

| 11  | 1  | 0  | 0  | 0  | 1  | G18                  |

| 12  | 1  | 0  | 0  | 1  | 0  | G19                  |

| 13  | 1  | 0  | 0  | 1  | 1  | G20                  |

| 14  | 1  | 0  | 1  | 0  | 0  | G21                  |

| 15  | 1  | 0  | 1  | 0  | 1  | G22                  |

| 16  | 1  | 0  | 1  | 1  | 0  | G23                  |

| 17  | 1  | 0  | 1  | 1  | 1  | G24                  |

Note: If the specified address in this command is not defined (X4~X0=18H~1FH), the function will not be changed.

#### **General Output Port Command**

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1  | Bit0     |

|------|-----|------|------|------|------|------|------|-------|----------|

| 1st  | W   | 0    | 1    | 1    | *    | *    | *    | P2    | P1       |

|      |     |      |      |      |      |      |      | *· Do | n't care |

The general output port command descriptions are described by the following:

- P2, P1: general output port data

- The general output port supports 2-bit static output operation

- Used to control other I/O devices or controls the LEDs

- When the general output port data is set to a high level, the related pin will output a VDD level while the related pin will output a GND level when the general output port data is cleared to a low level

- Relationship between the general output port data and the output pin status

| P2 | P1 | Display State of<br>General Output Port | Comment                                                                                                |

|----|----|-----------------------------------------|--------------------------------------------------------------------------------------------------------|

| 0  | 0  | Sets P2 to low; Sets P1 to low          | _                                                                                                      |

| 0  | 1  | Sets P2 to low; Sets P1 to high         | _                                                                                                      |

| 1  | 0  | Sets P2 to high; Sets P1 to low         | _                                                                                                      |

| 1  | 1  | Sets P2 to high; Sets P1 to high        | Default state when power is applied or when the $\overrightarrow{\text{RST}}$ input is at a low level. |

#### **Display Duty Set Command**

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1  | Bit0     |

|------|-----|------|------|------|------|------|------|-------|----------|

| 1st  | W   | 1    | 0    | 0    | *    | *    | D2   | D1    | D0       |

|      |     |      |      |      |      |      |      | *: Do | n't care |

The display duty set command descriptions are described by the following:

- D2~D0: Display duty selections

- The display duty adjusts the contrast in 8 stages using 3 selection bits to adjust the pulse width of the segment output

- The relationship between the setup data and the grid duty is shown in the table.

| HEX | D2 | D1 | D0 | Grid Duty | Comment                                                                                      |

|-----|----|----|----|-----------|----------------------------------------------------------------------------------------------|

| 0   | 0  | 0  | 0  | 8/16      | Default state when power is applied or when $\overline{\text{RST}}$ input is at a low level. |

| 1   | 0  | 0  | 1  | 9/16      | —                                                                                            |

| 2   | 0  | 1  | 0  | 10/16     | _                                                                                            |

| 3   | 0  | 1  | 1  | 11/16     | —                                                                                            |

| 4   | 1  | 0  | 0  | 12/16     | —                                                                                            |

| 5   | 1  | 0  | 1  | 13/16     | —                                                                                            |

| 6   | 1  | 1  | 0  | 14/16     | _                                                                                            |

| 7   | 1  | 1  | 1  | 15/16     | _                                                                                            |

#### Number of Digits Set Command

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1  | Bit0     |

|------|-----|------|------|------|------|------|------|-------|----------|

| 1st  | W   | 1    | 0    | 1    | *    | K3   | K2   | K1    | K0       |

|      |     |      |      |      |      |      |      | *: Do | n't care |

The number of digits set command descriptions is are described by the following:

- K3~K0: number of digit selections

- The number of display digits can be from 9 to 24 digits using the 4 selection bits.

- The relationship between setup data and the displayed grid is shown in the table.

| HEX | КЗ | К2 | К1 | к0 | Number of<br>Digits of Grid | Comment                                                                                          |

|-----|----|----|----|----|-----------------------------|--------------------------------------------------------------------------------------------------|

| 0   | 0  | 0  | 0  | 0  | G1 to G24                   | Default state when power is applied or when the $\overline{\text{RST}}$ input is at a low level. |

| 1   | 0  | 0  | 0  | 1  | G1 to G9                    | —                                                                                                |

| 2   | 0  | 0  | 1  | 0  | G1 to G10                   | —                                                                                                |

| 3   | 0  | 0  | 1  | 1  | G1 to G11                   | —                                                                                                |

| 4   | 0  | 1  | 0  | 0  | G1 to G12                   | —                                                                                                |

| 5   | 0  | 1  | 0  | 1  | G1 to G13                   | _                                                                                                |

| 6   | 0  | 1  | 1  | 0  | G1 to G14                   | —                                                                                                |

| 7   | 0  | 1  | 1  | 1  | G1 to G15                   | _                                                                                                |

| 8   | 1  | 0  | 0  | 0  | G1 to G16                   | —                                                                                                |

| 9   | 1  | 0  | 0  | 1  | G1 to G17                   | —                                                                                                |

| А   | 1  | 0  | 1  | 0  | G1 to G18                   | —                                                                                                |

| В   | 1  | 0  | 1  | 1  | G1 to G19                   | —                                                                                                |

| С   | 1  | 1  | 0  | 0  | G1 to G20                   | _                                                                                                |

| D   | 1  | 1  | 0  | 1  | G1 to G21                   | _                                                                                                |

| E   | 1  | 1  | 1  | 0  | G1 to G22                   | —                                                                                                |

| F   | 1  | 1  | 1  | 1  | G1 to G23                   | —                                                                                                |

#### All Display Lights On/Off Set Command

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1  | Bit0     |

|------|-----|------|------|------|------|------|------|-------|----------|

| 1st  | W   | 1    | 1    | 0    | *    | D    | S    | Н     | L        |

|      |     |      |      |      |      |      |      | *: Do | n't care |

The display ON/OFF set command descriptions are described by the following:

- S bit: S="1" is standby mode; S="0" is normal mode

- D bit: D="1" is display ON; D="0" is display OFF

- H bit: set all lights ON

- L bit: set all lights OFF

- When S bit = "1", the internal oscillator stops and all outputs are set to low and the general port is set to high (P2 and P1 are all at high levels)

- When S bit = "1", all registers will keep their original value

- After being woken up, the device will set the S and D bits to "0"

- The "All display lights ON" command is used primarily for display testing

- The "All display lights OFF" command is primarily used for display flashing

- The command bits, including D, H and L bits, can not control the general output port

- The relationship between the control bits and display state of G1~G24, S1~S40 and AD1~AD2 pins is shown in the table.

| D | s | Н | L | Driver Output Status                                                                  | Comment                                                                                                     |

|---|---|---|---|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 1 | 0 | 0 | 0 | Normal display                                                                        | —                                                                                                           |

| 1 | 0 | 0 | 1 | Sets all segments and AD to Low<br>All grids keep scan<br>General ports active        | —                                                                                                           |

| 1 | 0 | 1 | * | Sets all segments and AD to High<br>All grids keep scan<br>General ports active       | _                                                                                                           |

| 0 | 0 | * | * | Sets all segments and AD to Low<br>Sets all grids to Low<br>General ports active      | Display off mode<br>(Default state when<br>power is applied or<br>when the RST input<br>is at a low level.) |

| * | 1 | * | * | Sets all segments and AD to Low<br>Sets all grids to Low<br>Set General ports to high | Standby mode                                                                                                |

\*: Don't care

#### Wake-up Setting

The wake-up behavior is described by the following:

- The device is woken up when a  $\overline{\text{CS}}$  low pulse is asserted i.e. when a  $\overline{\text{CS}}$  signal falling edge occurs.

- The D and S control bits described in the preceding section will be set to "0" display off mode

- The oscillator starts to oscillate after wake-up

- The VFD driver does not display until the host MCU transmits commands to it.

#### **TEST Command**

| Byte | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|-----|------|------|------|------|------|------|------|------|

| 1st  | W   | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0    |

The TEST command is described by the following:

- Only when the TEST pin is high is the TEST command "EOH" is valid

- This command is used by HOLTEK for internal testing.

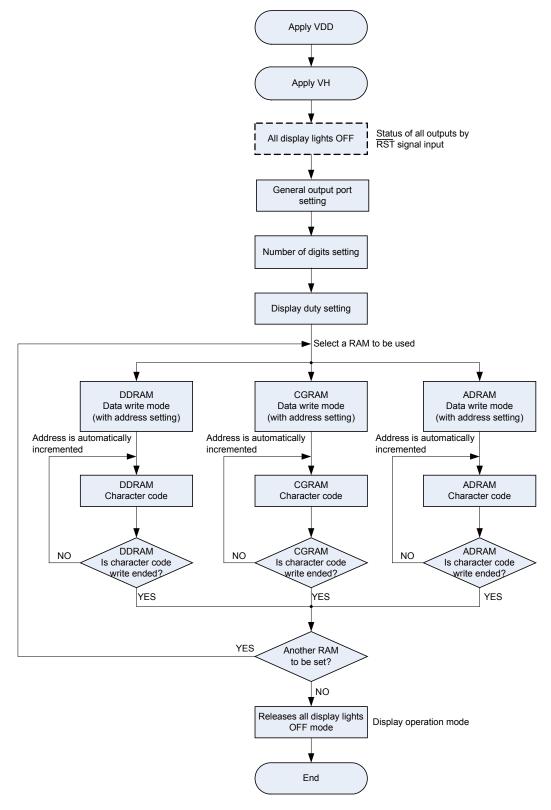

#### **Setting Flowchart**

**Power Applied Included**

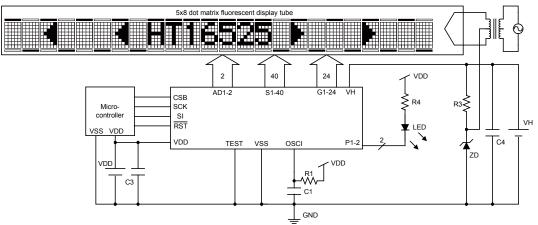

# **Application Circuit**

RST Pin is Connected to a MCU

### **RST** Pin is Connected to External Resistor and Capacitor

- Note: 1. The VDD value depends on the power supply voltage of the microcontroller used. Adjust the values of the components R2, R4, C2, C3 and C4 according to the power supply voltage used.

- 2. The VH value depends on the fluorescent display tube used. Adjust the values of the components R3 and ZD according to the power supply voltage used.

- 3. R1=120kΩ, C1=0.1µF.

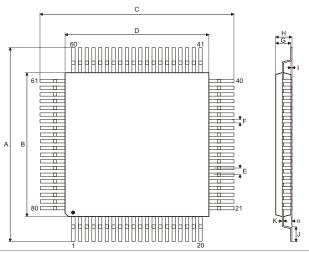

# Package Information

# 80-pin LQFP (10mmx10mm) Outline Dimensions

| Symbol | Dimensions in inch |       |       |  |  |  |

|--------|--------------------|-------|-------|--|--|--|

| Symbol | Min.               | Nom.  | Max.  |  |  |  |

| A      | 0.469              | —     | 0.476 |  |  |  |

| В      | 0.390              | —     | 0.398 |  |  |  |

| С      | 0.469              | —     | 0.476 |  |  |  |

| D      | 0.390              | —     | 0.398 |  |  |  |

| E      | _                  | 0.016 | —     |  |  |  |

| F      | _                  | 0.006 | —     |  |  |  |

| G      | 0.053              | —     | 0.057 |  |  |  |

| Н      | _                  | —     | 0.063 |  |  |  |

| I      | —                  | 0.004 | —     |  |  |  |

| J      | 0.018              | —     | 0.030 |  |  |  |

| К      | 0.004              | —     | 0.008 |  |  |  |

| α      | 0°                 | _     | 7°    |  |  |  |

| Symbol | Dimensions in mm |      |       |  |  |  |

|--------|------------------|------|-------|--|--|--|

| Symbol | Min.             | Nom. | Max.  |  |  |  |

| A      | 11.90            | _    | 12.10 |  |  |  |

| В      | 9.90             | _    | 10.10 |  |  |  |

| С      | 11.90            | _    | 12.10 |  |  |  |

| D      | 9.90             | _    | 10.10 |  |  |  |

| E      | _                | 0.40 | —     |  |  |  |

| F      | _                | 0.16 | —     |  |  |  |

| G      | 1.35             | _    | 1.45  |  |  |  |

| Н      | _                | _    | 1.60  |  |  |  |

| I      | _                | 0.10 | —     |  |  |  |

| J      | 0.45             | _    | 0.75  |  |  |  |

| K      | 0.10             | _    | 0.20  |  |  |  |

| α      | 0°               | —    | 7°    |  |  |  |

#### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan Tel: 886-2-2655-7070 Fax: 886-2-2655-7373 Fax: 886-2-2655-7383 (International sales hotline)

#### Holtek Semiconductor Inc. (Shenzhen Sales Office)

5F, Unit A, Productivity Building, No.5 Gaoxin M 2nd Road, Nanshan District, Shenzhen, China 518057 Tel: 86-755-8616-9908, 86-755-8616-9308 Fax: 86-755-8616-9722

#### Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538, USA Tel: 1-510-252-9880 Fax: 1-510-252-9885 http://www.holtek.com

#### Copyright © 2012 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.