# SANYO Semiconductors DATA SHEET

# Monolithic Digital IC For Office Automation Equipment **3-phase Brushless Motor Driver**

## Overview

The LB1928 is a 3-phase brushless motor driver well suited for drum and paper feed motors in laser printers, plain-paper copiers and other office automation equipment. Direct PWM drive allows control with low power losses. Peripheral circuitry including speed control circuit and FG amplifier is integrated, thus allows drive circuit to be constructed with a single chip.

## Features

- 3-phase bipolar drive (30V, 3.1A)

- Direct PWM drive technique

- Built-in diode for absorbing output lower-side kickback

- Speed discriminator and PLL speed control

- Speed lock detection output

- Built-in forward/reverse switching circuit

- Built-in protection circuitry includes current limiter, overheat protection, motor restraint protection, etc.

## **Specifications**

### Absolute Maximum Ratings at Ta = 25°C

| Parameter                              | Symbol              | Conditions                        | Ratings     | Unit |

|----------------------------------------|---------------------|-----------------------------------|-------------|------|

| Maximum supply voltage                 | V <sub>CC</sub> max |                                   | 30          | V    |

| Maximum output current                 | I <sub>O</sub> max  | $T \leq 500 ms$                   | 3.1         | А    |

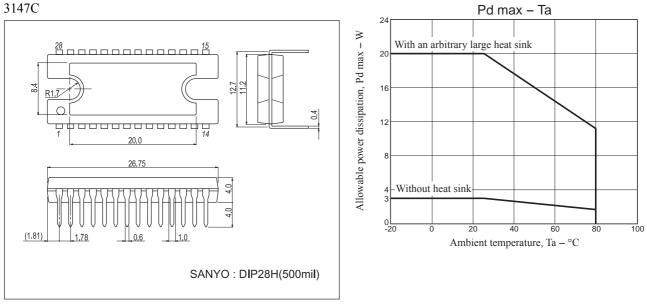

| Allowable power dissipation 1          | Pd max 1            | Independent IC                    | 3           | W    |

| Allowable power dissipation 2 Pd max 2 |                     | With an arbitrary large heat sink | 20          | W    |

| Operating temperature                  | Topr                |                                   | -20 to +80  | °C   |

| Storage temperature                    | Tstg                |                                   | -55 to +150 | °C   |

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

## Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter                        | Symbol           | Conditions | Ratings   | Unit |

|----------------------------------|------------------|------------|-----------|------|

| Power supply voltage range 1     | V <sub>CC</sub>  |            | 9.5 to 28 | V    |

| Regulator voltage output current | I <sub>REG</sub> |            | -30 to 0  | mA   |

| LD output current                | I <sub>LD</sub>  |            | 0 to 15   | mA   |

# **Electrical Characteristics** at Ta = 25°C, $V_{CC} = VM = 24V$

| Parameter                              | Symbol Conditions     |                                                   | Ratings  |          | Unit                  |       |

|----------------------------------------|-----------------------|---------------------------------------------------|----------|----------|-----------------------|-------|

| T drameter                             |                       |                                                   | min      | typ      |                       | max   |

| Power supply current 1                 | I <sub>CC</sub> 1     |                                                   |          | 23       | 30                    | mA    |

| Power supply current 2                 | I <sub>CC</sub> 2     | In STOP mode                                      |          | 3.5      | 5.0                   | mA    |

| Output                                 |                       |                                                   |          |          |                       |       |

| Output saturation voltage 1            | V <sub>O</sub> sat1   | $I_{O} = 1.0A, V_{O} (SINK) + V_{O} (SOURCE)$     |          | 2.0      | 2.5                   | V     |

| Output saturation voltage 2            | V <sub>O</sub> sat2   | $I_{O}$ = 2.0A, $V_{O}$ (SINK) + $V_{O}$ (SOURCE) |          | 2.6      | 3.2                   | V     |

| Output leak current                    | l <sub>O</sub> leak   |                                                   |          |          | 100                   | μΑ    |

| Lower-side diode forward voltage 1     | V <sub>D</sub> 1      | ID = -1.0A                                        |          | 1.2      | 1.5                   | V     |

| Lower-side diode forward voltage 2     | V <sub>D</sub> 2      | ID = -2.0A                                        |          | 1.5      | 2.0                   | V     |

| 5V regulator voltage output            |                       |                                                   |          |          |                       |       |

| Output voltage                         | V <sub>REG</sub>      | I <sub>O</sub> = -5mA                             | 4.65     | 5.00     | 5.35                  | V     |

| Voltage fluctuation                    | ∆V <sub>REG</sub> 1   | V <sub>CC</sub> = 9.5 to 28V                      |          | 30       | 100                   | mV    |

| Load fluctuation                       | $\Delta V_{REG}^2$    | I <sub>O</sub> = -5 to -20mA                      |          | 20       | 100                   | mV    |

| Hall amplifier                         |                       |                                                   | •        |          |                       |       |

| Input bias current                     | I <sub>HB</sub>       |                                                   | -2       | -0.5     |                       | μA    |

| Common mode input voltage range        | VICM                  |                                                   | 1.5      |          | V <sub>REG</sub> -1.5 | V     |

| Hall input sensitivity                 |                       |                                                   | 80       |          | -                     | mVp-p |

| Hysteresis width                       | ΔVIN                  |                                                   | 15       | 24       | 42                    | mV    |

| Input voltage L→H                      | VSLH                  |                                                   |          | 12       |                       | mV    |

| Input voltage H→L                      | VSHL                  |                                                   |          | -12      |                       | mV    |

| PWM oscillator                         |                       |                                                   |          |          |                       |       |

| Output High level voltage              | V <sub>OH</sub> (PWM) |                                                   | 2.5      | 2.8      | 3.1                   | V     |

| Output Low level voltage               | V <sub>OL</sub> (PWM) |                                                   | 1.2      | 1.5      | 1.8                   | V     |

| Oscillator frequency                   | F (PWM)               | C = 3900pF                                        |          | 18       |                       | kHz   |

| Amplitude                              | V (PWM)               |                                                   | 1.05     | 1.30     | 1.55                  | Vp-p  |

| CSD circuit                            | . ()                  |                                                   |          |          |                       | • • • |

| Operating voltage                      | V <sub>OH</sub> (CSD) |                                                   | 3.6      | 3.9      | 4.2                   | V     |

| External capacitance charge            | ICHG                  |                                                   | -17      | -12      | -9                    | μA    |

| current                                |                       |                                                   |          |          | 0                     | μι    |

| Operating time                         | T (CSD)               | C = 10µF Design target value                      |          | 3.3      |                       | S     |

| Current limiter operation              |                       |                                                   |          |          |                       |       |

| Limiter                                | VRF                   | V <sub>CC</sub> -VM                               | 0.45     | 0.5      | 0.55                  | V     |

| Thermal shutdown operation             |                       |                                                   |          |          |                       |       |

| Thermal shutdown operating temperature | TSD                   | Design target value (junction temperature)        | 150      | 180      |                       | °C    |

| Hysteresis width                       | ∆TSD                  | Design target value (junction temperature)        |          | 50       |                       | °C    |

| FG amplifier                           |                       |                                                   |          |          |                       |       |

| Input offset voltage                   | V <sub>IO</sub> (FG)  |                                                   | -10      |          | +10                   | mV    |

| Input bias current                     | I <sub>B</sub> (FG)   |                                                   | -1       |          | +1                    | μA    |

| Output High level voltage              | V <sub>OH</sub> (FG)  | IFGO = -0.2mA                                     | VREG-1.2 | VREG-0.8 |                       | V     |

| Output Low level voltage               | V <sub>OL</sub> (FG)  | IFGO = 0.2mA                                      |          | 0.8      | 1.2                   | V     |

| FG input sensitivity                   |                       | GAIN 100 times                                    | 3        | 0.0      |                       | mV    |

| Next-stage Schmitt comparator<br>width |                       | Design target value                               | 100      | 180      | 250                   | mV    |

| Operation frequency range              |                       |                                                   |          |          | 2                     | kHz   |

| Open-loop gain                         |                       | f (FG) = 2kHz                                     | 45       | 51       |                       | dB    |

Continued on next page.

| Parameter                      | Symbol                | Conditions                                 |          | Ratings  |          |      |  |

|--------------------------------|-----------------------|--------------------------------------------|----------|----------|----------|------|--|

| Falameter                      | Symbol                | Conditions                                 | min      | typ max  |          | Unit |  |

| Speed discriminator            |                       |                                            |          |          |          |      |  |

| Output High level voltage      | V <sub>OH</sub> (D)   | IDO = -0.1mA                               | VREG-1.0 | VREG-0.7 |          | V    |  |

| Output Low level voltage       | V <sub>OL</sub> (D)   | IDO = 0.1mA                                |          | 0.8      | 1.1      | V    |  |

| Count number                   |                       |                                            |          | 512      |          |      |  |

| PLL output                     |                       |                                            |          |          |          |      |  |

| Output High level voltage      | V <sub>OH</sub> (P)   | IPO = -0.1mA                               | VREG-1.8 | VREG-1.5 | VREG-1.2 | V    |  |

| Output Low level voltage       | V <sub>OL</sub> (P)   | IPO = 0.1mA                                | 1.2      | 1.5      | 1.8      | V    |  |

| Lock detection                 |                       |                                            |          |          |          |      |  |

| Output Low level voltage       | V <sub>OL</sub> (LD)  | ILD = 10mA                                 |          | 0.15     | 0.5      | V    |  |

| Lock range                     |                       |                                            |          | 6.25     |          | %    |  |

| Integrator                     |                       |                                            |          |          |          |      |  |

| Input bias current             | IB (INT)              |                                            | -0.4     |          | +0.4     | μΑ   |  |

| Output High level voltage      | V <sub>OH</sub> (INT) | I <sub>INTO</sub> = -0.2mA                 | VREG-1.2 | VREG-0.8 |          | V    |  |

| Output Low level voltage       | V <sub>OL</sub> (INT) | I <sub>INTO</sub> = 0.2mA                  |          | 0.8      | 1.2      | V    |  |

| Open-loop gain                 |                       | f (INT) = 1kHZ                             | 45       | 51       |          | dB   |  |

| Gain bandwidth product         |                       | Design target value                        |          | 450      |          | kHz  |  |

| Reference voltage              |                       | Design target value                        | -5%      | VREG/2   | 5%       | V    |  |

| Crystal oscillator             |                       |                                            |          |          |          |      |  |

| Operating frequency range      | fosc                  |                                            | 3        |          | 10       | MHz  |  |

| Low level pin voltage          | VOSCL                 | I <sub>OSC</sub> = -0.5mA                  |          | 1.65     |          | V    |  |

| High level pin current         | IOSCH                 | V <sub>OSC</sub> = V <sub>OSC</sub> L+0.3V |          | 0.4      |          | mA   |  |

| Start/stop pin                 |                       |                                            |          |          |          |      |  |

| High level input voltage range | V <sub>IH</sub> (S/S) |                                            | 3.5      |          | VREG     | V    |  |

| Low level input voltage range  | V <sub>IL</sub> (S/S) |                                            | 0        |          | 1.5      | V    |  |

| Input open voltage             | V <sub>IO</sub> (S/S) |                                            | VREG-0.5 |          | VREG     | V    |  |

| Hysteresis width               | ΔVIN                  |                                            | 0.35     | 0.50     | 0.65     | V    |  |

| High level input current       | I <sub>IH</sub> (S/S) | V (S/S) = VREG                             | -10      | 0        | 10       | μA   |  |

| Low level input current        | I <sub>IL</sub> (S/S) | V (S/S) = 0V                               | -280     | -210     |          | μΑ   |  |

| Forward/reverse pin            |                       |                                            |          |          |          |      |  |

| High level input voltage range | V <sub>IH</sub> (F/R) |                                            | 3.5      |          | VREG     | V    |  |

| Low level input voltage range  | V <sub>IL</sub> (F/R) |                                            | 0        |          | 1.5      | V    |  |

| Input open voltage             | V <sub>IO</sub> (F/R) |                                            | VREG-0.5 |          | VREG     | V    |  |

| Hysteresis width               | ΔVIN                  |                                            | 0.35     | 0.50     | 0.65     | V    |  |

| High level input current       | I <sub>IH</sub> (F/R) | V (F/R) = VREG                             | -10      | 0        | +10      | μA   |  |

| Low level input current        | I <sub>IL</sub> (F/R) | V (F/R) = 0V                               | -280     | -210     |          | μA   |  |

## Package Dimensions

unit : mm (typ)

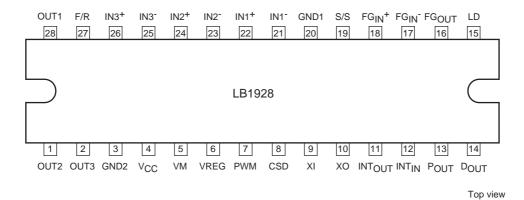

# **Pin Assignment**

Relationship between crystal oscillator frequency  $f_{OSC}$  and FG frequency  $f_{FG}$  is as follows.  $f_{FG}$  (servo) =  $f_{OSC}$ / (ECL divide-by-16×count number) =  $f_{OSC}$ /8192

# **Truth Table**

|   | Source    |     | F/R = "L" |     | F/R = "H" |     |     |

|---|-----------|-----|-----------|-----|-----------|-----|-----|

|   | Sink      | IN1 | IN2       | IN3 | IN1       | IN2 | IN3 |

| 1 | OUT2→OUT1 | Н   | L         | Н   | L         | Н   | L   |

| 2 | OUT3→OUT1 | Н   | L         | L   | L         | Н   | Н   |

| 3 | OUT3→OUT2 | н   | Н         | L   | L         | L   | Н   |

| 4 | OUT1→OUT2 | L   | н         | L   | н         | L   | Н   |

| 5 | OUT1→OUT3 | L   | н         | н   | н         | L   | L   |

| 6 | OUT2→OUT3 | L   | L         | Н   | Н         | Н   | L   |

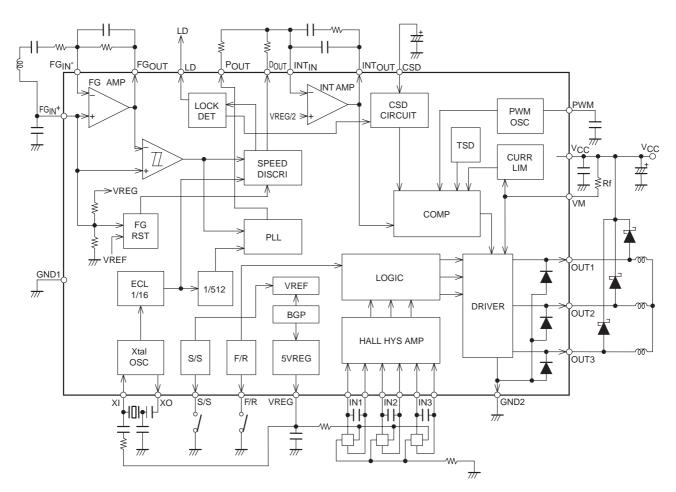

# **Block Diagram and Sample Application Circuit**

# **Pin Description**

| FIII Des | -        |                                                                                                                             |                                       |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Pin No.  | Pin name | Pin function                                                                                                                | Equivalent circuit                    |

| 28       | OUT1     | Motor drive output pins.                                                                                                    | Vcc                                   |

| 1        | OUT2     | Connect a Schottky diode between these outputs and $V_{CC}.$                                                                | 300Ω VM (5)                           |

| 2        | OUT3     |                                                                                                                             |                                       |

| 3        | GND2     | Output ground pin.                                                                                                          |                                       |

| 5        | VM       | Output block power supply and output current detection pin.                                                                 |                                       |

|          |          | Connect a resistor (Rf) between this pin and $V_{CC}$ to detect the                                                         |                                       |

|          |          | output current as a voltage.                                                                                                |                                       |

|          |          | The output current is limited according to the equation $I_{OUT}$ =                                                         |                                       |

|          |          | V <sub>RF</sub> /R <sub>f</sub> .                                                                                           |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             | $\bigcirc$                            |

| 4        | VCC      | Power supply pin (except for output block).                                                                                 |                                       |

| 6        | VREG     | Regulated power supply output pin (5V output).                                                                              | V <sub>CC</sub>                       |

|          |          | Connect a capacitor (approx. $0.1\mu F$ ) between this pin and                                                              |                                       |

|          |          | ground to stabilize the output.                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             | ↓ \$                                  |

|          |          |                                                                                                                             | (6)                                   |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             | $\Psi$                                |

|          |          |                                                                                                                             |                                       |

| 7        |          | DW/M fraguency actting pin                                                                                                  |                                       |

| /        | PWM      | PWM frequency setting pin.<br>Connect a capacitor between this pin and ground.                                              | VREG                                  |

|          |          | C = 3900 pF results in a frequency of about 18kHz.                                                                          |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

| 8        | CSD      | Lock protection circuit operation time setting pin.                                                                         |                                       |

| 0        | COD      | Connecting a capacitor of about $10\mu$ F between this pin and                                                              |                                       |

|          |          | ground results in a protection circuit operation time of about                                                              |                                       |

|          |          | 3.3 seconds.                                                                                                                |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             | 1 $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

| 0        | XI       | Crustal oscillator pine                                                                                                     |                                       |

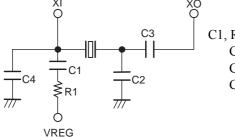

| 9<br>10  | XO       | Crystal oscillator pins.                                                                                                    | VREG                                  |

| 10       | 70       | Connect to quartz oscillator to generate the reference clock.<br>When an external clock (of several MHz) is used, the clock |                                       |

|          |          | signal should be input via a resistor of about 5.1k $\Omega$ connected                                                      |                                       |

|          |          | in series with the XI pin. In this case, the XO pin must be left                                                            |                                       |

|          |          | open.                                                                                                                       |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

|          |          |                                                                                                                             |                                       |

Continued on next page.

| Continued | from preced       | ling page.                                                                                                           |                                                              |

|-----------|-------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Pin No.   | Pin name          | Pin function                                                                                                         | Equivalent circuit                                           |

| 11        | INTOUT            | Integrator output pin (speed control pin).                                                                           | VREG                                                         |

| 12        | INT <sub>IN</sub> | Integrator input pin.                                                                                                | VREG                                                         |

| 13        | POUT              | PLL output pin.                                                                                                      | VREG<br>300Ω<br>13                                           |

| 14        | DOUT              | Speed discriminator output pin.<br>Acceleration : High, Deceleration : Low                                           | VREG<br>300Ω<br>14<br>77<br>77<br>77<br>77<br>77<br>77<br>77 |

| 15        | LD                | Speed lock detection pin.<br>When motor rotation is within lock range (±6.25%) : Low<br>Withstand voltage : 30V max. | Continued on next page                                       |

Continued on next page.

|          | n preceding pag                         | -                                                                                                                                                          | <b>-</b>                                                                      |

|----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Pin No.  | Pin name                                | Pin function                                                                                                                                               | Equivalent circuit                                                            |

| 16       | FGOUT                                   | FG amplifier output pin.                                                                                                                                   | VREG<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()              |

| 17<br>18 | FGIN <sup>-</sup><br>FG <sub>IN</sub> + | FG amplifier input pin.<br>By connecting a capacitor (approx. 0.1µF)<br>between FG <sub>IN</sub> <sup>+</sup> and ground, the logic circuitry is<br>reset. | VREG<br>FG reset circuit<br>18<br>300Ω<br>18<br>300Ω<br>18<br>300Ω<br>17<br>7 |

| 19       | S/S                                     | Start/stop control pin.<br>Start (Low) : 0V to 1.5V<br>Stop (High) : 3.5V to VREG<br>High when open.<br>Hysteresis width : approx. 0.5V.                   | VREG                                                                          |

| 20       | GND1                                    | Ground pin (except for output block).                                                                                                                      |                                                                               |

| 22       | IN1+                                    | Hall input pins.                                                                                                                                           | VREG                                                                          |

| 21       | IN1 <sup>-</sup>                        | High when $IN^+ > IN^-$ , Low when $IN^+ < IN^-$ .                                                                                                         |                                                                               |

| 24       | IN2 <sup>+</sup>                        | Hall signal should have an amplitude of at least                                                                                                           |                                                                               |

| 23       | IN2 <sup>-</sup>                        | 100mVp-p (differential operation). When Hall                                                                                                               |                                                                               |

| 26       | IN3 <sup>+</sup>                        | signal noise is a problem, connect a capacitor                                                                                                             | 21 23 25 W 22 24 26                                                           |

| 25       | IN3 <sup>-</sup>                        | between IN <sup>+</sup> and IN <sup>-</sup> .                                                                                                              |                                                                               |

| 27       | F/R                                     | Forward/reverse control pin.<br>Forward (Low) : 0V to 1.5V<br>Reverse (High) : 3.5V to VREG<br>High when open.<br>Hysteresis width : approx. 0.5V.         | VREG                                                                          |

## **Description of the LB1928**

## 1. Speed control circuit

The IC performs speed control through combined use of a speed discrimination circuit and PLL circuit. The speed control circuit counts FG cycles and outputs a deviation signal every 2FG cycles. The PLL circuit outputs a phase deviation signal every FG cycle.

The FG servo frequency is determined by the following equation. The motor rotation speed is set by the number of FG pulses and the crystal oscillator frequency.

fFG (servo) = fOSC/8192

fOSC : Crystal oscillator frequency

2. Output drive circuit

In order to reduce power loss at the output, the LB1927 uses the PWM drive technique. While ON, the output transistors are always saturated, and motor drive power is adjusted by varying the output ON duty ratio. Because output PWM switching is performed by the lower-side output transistor, a Schottky diode must be connected between OUT and V<sub>CC</sub>. (If the reverse recovery time of the diode is too long, a feedthrough current will flow at the instant when the lower-side transistor goes ON.) An internal diode is provided between OUT and GND. If large output current causes a problem (waveform distortion during lower-side kickback, etc.), an external rectifying diode or Schottky diode should be connected.

The output diode is integrated only on the lower side.

3. Current limiting circuit

The current limiting circuit limits the peak current to the value I = VRF/Rf (VRF = 0.5V typ., Rf : current detector resistance). Current limiting is achieved by reducing the ON duty ratio of the output, which reduces the current.

4. Power save circuit

In order to reduce current drain in the STOP condition, the IC goes into power save mode. In this condition, bias current to most circuits is cut off, but the 5V regulator output remains active.

5. Reference clock

The reference clock for speed control can be input using one of the following two methods.

(1) Using a crystal oscillator

When a crystal is used for oscillation, connect the crystal, capacitors, and a resistor as shown in the figure below.

C1, R1 : For stable oscillationC3 : For oscillator couplingC2 : For stabilization and to prevent oscillation at upper harmonic frequencies

C4 : Prevents oscillation at upper harmonic frequencies

| (Reference value           |         |         |         |         |        |  |  |

|----------------------------|---------|---------|---------|---------|--------|--|--|

| Oscillator frequency (MHz) | C1 (µF) | C2 (pF) | C3 (pF) | C4 (pF) | R1 (Ω) |  |  |

| 3 to 5                     | 0.1     | 15      | 47      | 10      | 330k   |  |  |

| 5 to 8                     | 0.1     | 10      | 47      | None    | 330k   |  |  |

| 8 to 10                    | 0.1     | 10      | 22      | None    | 330k   |  |  |

The circuit configuration and values are for reference only. The crystal oscillator's characteristics as well as the possibility of floating capacitance and noise due to layout factors must be taken into consideration when designing an actual application.

[Precautions for wiring layout design]

Since the crystal oscillator circuit operates at high frequencies, it is susceptible to the influence of floating capacitance from the circuit board. Wiring should be kept as short as possible and traces should be kept narrow. When designing the external circuitry, pay special attention to the wiring layout between the oscillator and C3 (C2), to minimize the influence of floating capacitance. The capacitor C4 is quite effective at reducing the negative resistance (gain) at high frequencies. However, care is required to avoid excessive reduction in the negative resistance at the fundamental frequency.

(2) External clock input (equivalent to crystal oscillator, several MHz)

When using an external signal source instead of a crystal oscillator, the clock signal should be input from the XI pin through a resistor of about  $5.1 \text{k}\Omega$  connected to the pin in series. The XO pin should be left open. Signal input level Low : 0 to 0.8 VHigh : 2.5 to 5.0V

6. Speed lock range

The speed clock range is  $\pm 6.25\%$  of the rated speed. When the motor rotation is within the lock range, the LD pin becomes Low (open collector output). When the motor rotation goes out of the lock range, the ON duty ratio of the motor drive output is varied according to the amount of deviation to bring the rotation back into the lock range.

7. PWM frequency

The PWM frequency is determined by the capacitance connected to the PWM pin.

$f PWM \approx 1/(14400 \times C)$

PWM frequency in the range 15 to 25kHz is desirable. The ground side of the connected capacitor must be connected to the GND1 pin with a lead that is as short as possible.

8. Hall input signal

The Hall input requires a signal with an amplitude of at least the hysteresis width (42mV max.). Taking possible noise influences into consideration, an amplitude of at least 100mV is desirable. If noise during output phase switching disrupts the output waveform, insert capacitors across the Hall signal inputs (between the + and - inputs), and position those capacitors as close as possible to the pins.

## 9. Forward/reverse switching

Forward/reverse switching of motor rotation is carried out with the F/R pin. If this is performed while the motor is running, the following points must be observed :

- Feedthrough current during switching is handled by proper circuit design. However, the V<sub>CC</sub> voltage rise during switching (caused by momentary return of motor current to power supply) must not exceed the rated voltage (30V). If problems occur, the capacitance between V<sub>CC</sub> and GND must be increased.

- If the motor current after switching exceeds the current limiter value, the lower-side transistors go OFF but the upper-side transistors go into the short brake state, which causes a current flow. The magnitude of the current is determined by the motor counterelectromotive voltage and the coil resistance. This current may not exceed the rated current (3.1A). (Forward/reverse switching at high speed therefore is not safe.)

## 10. Motor restraint protection circuit

To protect the IC and the motor itself when rotation is inhibited, a restraint protection circuit is provided. If the LD output is High (unlocked) for a certain interval in the start condition, the lower-side transistors are turned off. The length of the interval is determined by the capacitance at the CSD pin. A capacitance of  $10\mu$ F results in a set interval of about 3.3 seconds. (Tolerance approx.  $\pm 30\%$ )

### Set interval (s) $\approx 0.33 \times C (\mu F)$

If the capacitor arrangement is subject to leak current, possible adverse effects such as setting time tolerances must be taken into consideration.

When the restraint protection circuit has been activated, the condition can only be canceled by setting the system to the stop condition or by turning the power off and on again (in the stop condition). When wishing not to use the restraint protection circuit, connect the CSD pin to ground.

If the stop time when releasing the restraint protection is short, the capacitor charge will not be fully dissipated. This in turn will cause a shorter restraint protection activation time after the motor has been restarted. The stop time should therefore be designed to be sufficiently long, using the equation shown below (also when restarting in the motor start transient state).

Stop time (ms)  $\geq 15 \times C (\mu F)$

## 11. Power supply stabilization

Because this IC provides a high output current and uses a switching drive technique, power supply line fluctuations can occur easily. Therefore, a capacitor of sufficient capacitance (several ten  $\mu$ F or higher) must be connected between the V<sub>CC</sub> pin and ground to assure stable operation. The ground connection of this capacitor must be connected to the GND2 pin, which is the power block ground, at a point as close as possible to the IC. If, due to problems associated with the heat sink, the (electrolytic) capacitor cannot be connected near the this pin, a ceramic capacitor of about 0.1 $\mu$ F must be connected near the pin.

Since the likelihood of power line fluctuation increases if diodes are inserted in the power supply lines to prevent destruction of the IC if power is connected with reverse polarity, a larger capacitance will be required.

### 12. VREG stabilization

A capacitor (about  $0.1\mu$ F) must be connected to the VREG pin (the 5V regulator output), which functions as the control circuit power supply, for stabilization. The ground side of this capacitor must be connected to the GND1 pin with a lead that is as short as possible.

#### 13. Integrating amplifier related component values

The external components used in the integrating amplifier must be located as close as possible to the IC to minimize the circuit's susceptibility to noise. These components must be located as far as possible from the motor.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of December, 2008. Specifications and information herein are subject to change without notice.