# PLL FOR DIGITAL TUNING SYSTEM(DTS)

#### **DESCRIPTION**

The SC72131 is phase-locked loop (PLL) LSI for digital turning systems (DTS).

The LSI is use to configure high-performance digital tuning systems, such as radio/cassette players. They allow high-performance AM/FM tuners to be implemented easily.

## **FEATURES**

- \* Built-in prescalers. Operate at input frequency ranging from 10~160MHz during FMIN input and at 0.5~40MHz during AMIN input.

- \* 12 possible reference frequencies (with 4.5 or 7.2 MHz crystal) 1, 3, 5, 9, 10, 3.125, 6.25, 12.5, 15, 25, 50 and 100 kHz

- \* Built-in 20bit general-purpose counter for such as measuring intermediate frequency (IF), IF input frequency ranging from 0.4M~12MHz.

- \* Has an unlock detector circuit, an dead zone control circuit and an deadlock clear circuit

- \* Built-in MOS transistor for forming an active low-pass filter

- \* 4 N-channel open-drain output ports (OFF withstanding Voltage: 13V) and 2 input or output ports.

- \* Serial data I/O

- All functions controlled through 4 serial bus lines

- \* Operating ranges

- Supply voltage......5.0  $\pm$  0.5 V

- Operating temperature.....-40 to +85° C

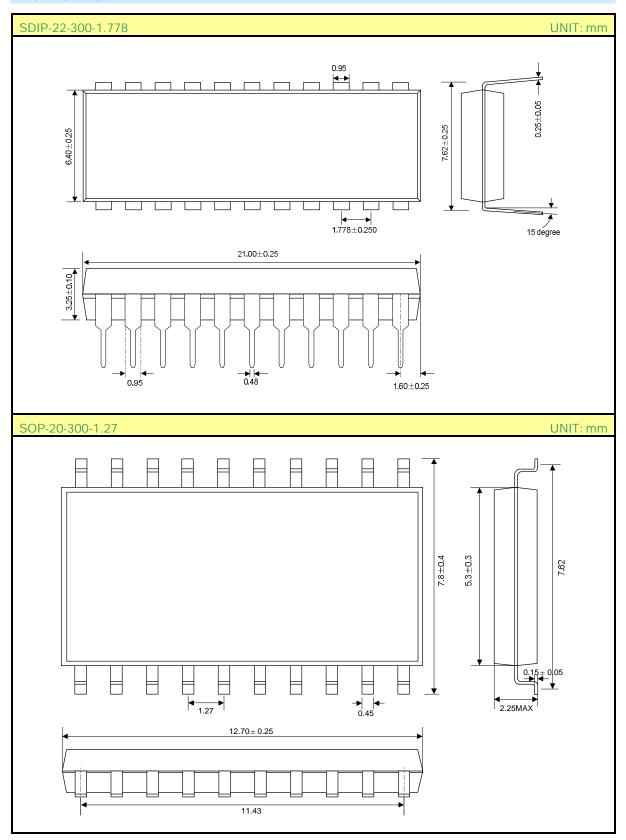

- \* Packages

- -SDIP-22-300-1.78

- -SOP-20-300-1.27

## ORDERING INFORMATION

| Part No. | Package           |

|----------|-------------------|

| SC72131  | SDIP-22-300-1.778 |

| SC72131S | SOP-20-300-1.27   |

### **APPLICATIONS**

\* Digital Tuning Systems

REV:2.0 2004.08.03

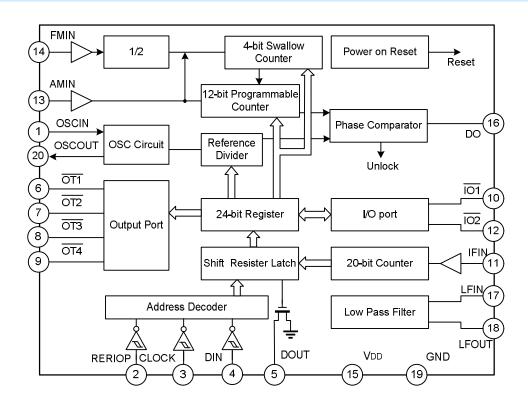

## **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (Tamb=25°C, VSS=0V)

| Characteristics                          | Symbol            | Ratings     | Unit |

|------------------------------------------|-------------------|-------------|------|

| Supply Voltage                           | VDDmax            | -0.3 to 7.0 | V    |

| Allowable Power Dissipation              | P <sub>dmax</sub> | 350         | mW   |

| N-ch Open-Drain OFF Withstanding Voltage | Voff              | 13          | V    |

| Operating Temperature                    | Topr              | -40 to +85  | °C   |

## ELECTRICAL CHARACTERISTICS (Tamb=-40 to 85°C, VSS=0V)

| Characteristics              | Symbol           | Test Condition | Min.                 | Тур.               | Max. | Unit |

|------------------------------|------------------|----------------|----------------------|--------------------|------|------|

|                              | R <sub>f</sub> 1 |                |                      | 1.0                |      | ΜΩ   |

| Duilt in Foodback Desistance | Rf2              |                |                      | 500                |      | kΩ   |

| Built-in Feedback Resistance | Rf3              |                |                      | 500                |      | kΩ   |

|                              | Rf4              |                |                      | 250                |      | kΩ   |

| D With D III In a Decision   | Rpd1             |                |                      | 200                |      | kΩ   |

| Built-in Pull-down Resistor  | Rpd2             |                |                      | 200                |      | kΩ   |

| Hysteresis                   | VHIS             |                |                      | 0.1V <sub>DD</sub> |      | V    |

| Output High Level Voltage    | VOH1             | Io=-1mA        | V <sub>DD</sub> -1.0 |                    |      | V    |

(To be continued)

| (Continued)                                   |                  |                                            |      |      |      |      |

|-----------------------------------------------|------------------|--------------------------------------------|------|------|------|------|

| Characteristics                               | Symbol           | Test Condition                             | Min. | Тур. | Max. | Unit |

|                                               | VOL1             | Io=1mA                                     |      |      | 1.0  | V    |

|                                               | VOL2             | Io=0.5mA                                   |      |      | 0.5  | V    |

|                                               | VOLZ             | IO=1mA                                     |      |      | 1.0  | V    |

|                                               | Vol3             | IO=1mA                                     |      |      | 0.2  | V    |

| Output Low Level Voltage                      | VOLS             | Io=5mA                                     |      |      | 1.0  | V    |

|                                               |                  | Io=1mA                                     |      |      | 0.2  | V    |

|                                               | VOL4             | IO=5mA                                     |      |      | 1.0  | V    |

|                                               |                  | Io=8mA                                     |      |      | 1.6  | V    |

|                                               | VOL5             | Io=1mA, Ain=1.3V                           |      |      | 0.5  | V    |

|                                               | lih1             | Vi=6.5V                                    |      |      | 5.0  | μΑ   |

|                                               | I <sub>IH2</sub> | V <sub>I</sub> =13V                        |      |      | 5.0  | μΑ   |

| Input High Level Current                      | Іінз             | VI=VDD                                     | 2.0  |      | 11   | μΑ   |

| Imput riigh Level Current                     | IIH4             | VI=VDD                                     | 4.0  |      | 22   | μΑ   |

|                                               | lih5             | VI=VDD                                     | 8.0  |      | 44   | μΑ   |

|                                               | IIH6             | VI=6.5V                                    |      |      | 200  | nA   |

| Input Low Level Current                       | IIL1             | VI=0                                       |      |      | 5.0  | μΑ   |

| Imput Low Level Current                       | l <sub>IL2</sub> | V <sub>I</sub> =0                          |      |      | 5.0  | μΑ   |

|                                               | IIL3             | V <sub>I</sub> =0                          | 2.0  |      | 11   | μΑ   |

| Input Low Level Current                       | lıL4             | V <sub>I</sub> =0                          | 4.0  |      | 22   | μΑ   |

| Imput Low Level Current                       | IIL5             | VI=0                                       | 8.0  |      | 44   | μΑ   |

|                                               | IIL6             | VI=0                                       |      |      | 200  | μΑ   |

| Output Off Lookage Current                    | IOFF1            | Vo=13                                      |      |      | 5.0  | μΑ   |

| Output Off Leakage Current                    | IOFF2            | Vo=6.5V                                    |      |      | 5.0  | μΑ   |

| High Level Three-state Off Leakage<br>Current | IOFFH            | VO=VDD                                     |      | 0.01 | 200  | nA   |

| Low Level Three-state Off Leakage<br>Current  | loffl            | Vo=0V                                      |      | 0.01 | 200  | nA   |

| Input Capacitance                             | Cin              |                                            |      | 6    | _    | pF   |

|                                               |                  | Xtal=7.2MHz,                               |      |      |      |      |

|                                               | IDD1             | fin2=130MHz,                               |      | 5    | 10   | mA   |

|                                               |                  | V <sub>IN2</sub> =40mVrms                  |      |      |      |      |

| Current Drain                                 |                  | PLL block stopped (PLL                     |      |      |      |      |

| Oundit Dialli                                 | IDD2             | INHIBIT), Xtal oscillator                  |      | 0.5  |      | mA   |

|                                               |                  | operating (Xtal=7.2MHz)                    |      |      |      |      |

|                                               | I <sub>DD3</sub> | PLL block stopped, Xtal oscillator stopped |      |      | 10   | μΑ   |

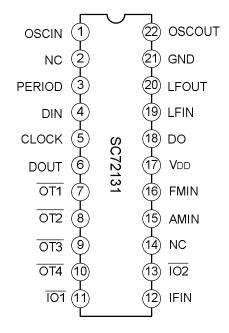

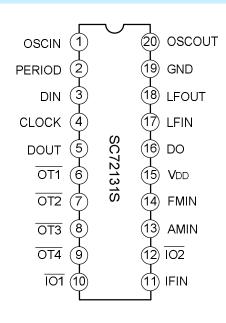

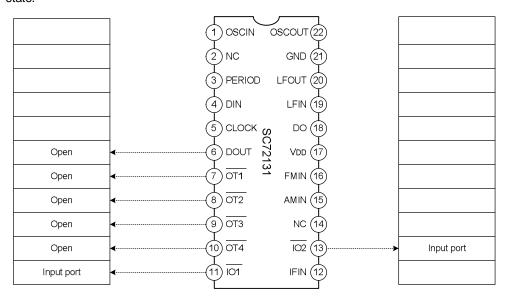

# PIN CONFIGURATION (SDIP22, SOP20)

# PIN DESCRIPTION

| Pin     | Pin NO. |          | David Maria                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|---------|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SDIP-22 | SOP-20  | Pin Name | Description                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| 1       | 1       | OSCIN    | Connects 4.5M or 7.2M crystal oscillator to supply reference                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| 22      | 20      | OSCOUT   | frequency and internal clock.                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 2       |         | NC       |                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 3       | 2       | PERIOD   | Serial I/O ports, These pins transfer data to and from the controller                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| 4       | 3       | DIN      | to set divisors and dividing modes, and to control the general-                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 5       | 4       | CLOCK    | purpose counter and general-purpose I/O ports.                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| 6       | 5       | DOUT     |                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 7       | 6       | OT1      | N channel open drain port pins.                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 8       | 7       | OT2      | • The output states are determined by OT1 to OT4 bits in the serial                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 9       | 8       | OT3      | data.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| 10      | 9       | OT4      | <ul> <li>If the serial data TBC bit is set to 1, a time base signal (8Hz) can be output from the OT1 pin.</li> <li>These pins are set to the OFF state when power is turn on.</li> </ul>                                                                   |  |  |  |  |  |  |  |  |

| 11      | 10      | ĪŌ1      | CMOS structure allows free use of these ports for input or output.                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| 13      | 12      | ĪO2      | Ports are set for input when the power is turned on.                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| 12      | 11      | IFIN     | <ul> <li>Input pin for measure general-purpose counter frequencies. The frequency measurement function has such uses as measuring intermediate frequencies (IF)</li> <li>These pin feature built-in amps, Data are input by capacitor coupling.</li> </ul> |  |  |  |  |  |  |  |  |

(To be continued)

REV:2.0 2004.08.03

## (Continued)

| Pin     | NO.    | D. N.    |                                                             |

|---------|--------|----------|-------------------------------------------------------------|

| SDIP-22 | SOP-20 | Pin Name | Description                                                 |

| 14      |        | NC       |                                                             |

| 15      | 13     | AMIN     | These pins input AM and FM band local oscillator signals by |

| 16      | 14     | FMIN     | capacitor coupling.                                         |

|         |        |          | These pins feature built-in amps.                           |

| 17      | 15     | VDD      | • power supply pin (Applies 5.0V ± 10%)                     |

| 18      | 16     | DO       | This pin is for phase comparator tristate output.           |

| 19      | 17     | LFIN     | - · · · · · · · · · · · · · · · · · · ·                     |

| 20      | 18     | LFOUT    | These pins for low-pass filter input pin and output pin.    |

| 21      | 19     | GND      | The SC72131 ground.                                         |

## **FUNCTION DESCRIPTION**

#### Serial Data I/O Methods

The SC72131 inputs and outputs data using the 4 serial bus lines, the serial data I/O methods are selected by an 8bit address

## Register assignments

| P0   | P1    | P2            | Ь3    | P4 | P5 | 9d | P7 | P8 | P9 | P10 | P11 | P12 | P13 | P14 | P15 | AODE | ΕM | CTE | oso | RO | R1 | R2 | R3 |

|------|-------|---------------|-------|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|------|----|-----|-----|----|----|----|----|

| Addr | ess = | = 92 <i>l</i> | H(IN) |    |    |    |    |    |    |     |     |     |     |     |     |      |    |     |     |    |    |    |    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | то о | G1 T | G1 | G1 | G1 | €0 | G0 | G | DZ<br>1 | <b>,</b> | ٨ | UL<br>1 |  | Co | _ | _ |  |  | OT3 | <br>OT2 |  | IO2 | ĪŌ1 |  |  |  |

|---------------------------------------------------------|------|------|----|----|----|----|----|---|---------|----------|---|---------|--|----|---|---|--|--|-----|---------|--|-----|-----|--|--|--|

|---------------------------------------------------------|------|------|----|----|----|----|----|---|---------|----------|---|---------|--|----|---|---|--|--|-----|---------|--|-----|-----|--|--|--|

# Address = A2H (OUT)

|    |    |   |    | IF1 |     |     |     |     |     |     |     |     |     |     |

|----|----|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 11 | 12 | * | UL | _   | _   | _   | _   | _   |     | _   | _   |     | _   | IF9 | IF8 | IF7 | IF6 | IF5 | IF4 | IF3 | IF2 | IF1 | IF0 |

|    |    |   |    | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |     |     |     |     |     |     |     |     |     | i   |

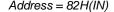

# Programmable divider structure

Swallow counter and programmable counter circuit configuration

HANGZHOU SILAN MICROELECTRONICS CO.,LTD

REV:2.0 2004.08.03

Http: www.silan.com.cn

| FM | MODE | Input pin | Set divisor  | Actual divisor: N   | Input frequency range (MHz) |

|----|------|-----------|--------------|---------------------|-----------------------------|

| 1  | *    | FMIN      | 272 to 65535 | Twice the set value | 10 to 160                   |

| 0  | 1    | AMIN      | 272 to 65535 | The set value       | 2 to 40                     |

| 0  | 0    | AMIN      | 4 to 4095    | The set value       | 0.5 to 10                   |

Note: \* Don't care.

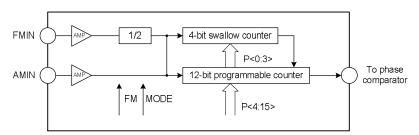

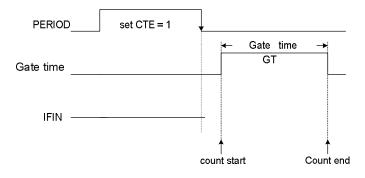

#### 1.IF Counter Structure

The SC72131 IF counter section consists of input amp, a gate time control circuit and a 20bit binary counter. The result, i.e., the counter's msb, can be read serially from the Dout pin.

| G1 | G0 | Gate time (GT) (ms) | Wait time (ms) |

|----|----|---------------------|----------------|

| 0  | 0  | 4                   | 3 ~ 4          |

| 0  | 1  | 8                   | 3 ~ 4          |

| 1  | 0  | 32                  | 7 ~ 8          |

| 1  | 1  | 64                  | 7~8            |

## 2. IF Counter Operation

Note: 1. IFIN input have built-in amp. Data are input by capacitor coupling.

- 2. Before starting the IF count, the IF counter must be reset in advance by setting CTE in the serial data to 0.

- 3. The IF count is started by changing the CTE bit in the serial data from 0 to 1. The serial data is latched by the SC72131 when the CE pin is dropped from high to low.

- 4.The IF signal must be supplied to the IFIN pin in the period between the point the CE pin goes low and the end of the wait time at the latest.

- 5. The value of the IF counter at the end of the Gate-Time must be read out during the period that CTE is 1. This is because the IF counter is reset when CTE is set to 0.

- 6. When operating the IF counter, the control microprocessor must first check the state of the IF-IC SD (station detect) signal and only after determining that the SD signal is present turn on IF buffer output

and execute an IF count operation. Auto search techniques that use only the IF counter are not recommended, since it is possible for IF buffer leakage output to cause incorrect stops at points where there is no station.

## 3. Power Supply Pins

A capacitor of at least 2000 pF must be inserted between the power supply VDD and GND pins for noise exclusion. This capacitor must be placed as close as possible to the VDD and GND pins.

## PIN STATES AFTER THE POWER ON RESET

After power-on reset, the pins (DOUT OT1  $\overline{OT2}$   $\overline{OT3}$   $\overline{OT4}$ ) are set to OPEN state and the pins ( $\overline{IO1}$ ,  $\overline{IO2}$ ) set to INPUT state.

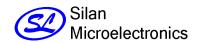

Note: this circuit according to SDIP-22 package, and the circuit of SOP-20 removed two NC pins, and others are the same as the above circuit.

HANGZHOU SILAN MICROELECTRONICS CO.,LTD Http: www.silan.com.cn Page 7 of 11

## TYPICAL APPLICATION CIRCUIT

Note: this circuit according to SDIP-22 package, and the circuit of SOP-20 removed two NC pins, and others are the same as the above circuit.

# PACKAGE OUTLINE

## HANDLING MOS DEVICES:

Electrostatic charges can exist in many things. All of our MOS devices are internally protected against electrostatic discharge but they can be damaged if the following precautions are not taken:

- Persons at a work bench should be earthed via a wrist strap.

- Equipment cases should be earthed.

- All tools used during assembly, including soldering tools and solder baths, must be earthed.

- MOS devices should be packed for dispatch in antistatic/conductive containers.

Http: www.silan.com.cn