#### **Features**

- Transparent RF Receiver ICs for 315 MHz (ATA5746) and 433.92 MHz (ATA5745) With High Receiving Sensitivity

- . Fully Integrated PLL With Low Phase Noise VCO, PLL, and Loop Filter

- High FSK/ASK Sensitivity:-105 dBm (ATA5746, FSK, 9.6 Kbits/s, Manchester, BER 10<sup>-3</sup>)

- -114 dBm (ATA5746, ASK, 2.4 Kbits/s, Manchester, BER 10<sup>-3</sup>)

- -104 dBm (ATA5745, FSK, 9.6 Kbits/s, Manchester, BER 10<sup>-3</sup>)

- -113 dBm (ATA5745, ASK, 2.4 Kbits/s, Manchester, BER 10<sup>-3</sup>)

- Supply Current: 6.5 mA in Active Mode (3V, 25°C, ASK Mode)

- Data Rate: 1 Kbit/s to 10 Kbits/s Manchester ASK, 1 Kbit/s to 20 Kbits/s Manchester FSK With Four Programmable Bit Rate Ranges

- Switching Between Modulation Types ASK/FSK and Different Data Rates Possible in

≤1 ms Typically, Without Hardware Modification on Board to Allow Different Modulation

Schemes for RKE, TPMS

- Low Standby Current: 50 μA at 3V, 25°C

- ASK/FSK Receiver Uses a Low-IF Architecture With High Selectivity, Blocking, and Low Intermodulation (Typical 3-dB Blocking 68.0 dBC at ±3 MHz/74.0 dBC at ±20.0 MHz, System I1dBCP = -31 dBm/System IIP3 = -24 dBm)

- Telegram Pause Up to 52 ms Supported in ASK Mode

- Wide Bandwidth AGC to Handle Large Out-of-band Blockers above the System I1dBCP

- 440-kHz IF Frequency With 30-dB Image Rejection and 420-kHz IF Bandwidth to Support PLL Transmitters With Standard Crystals or SAW-based Transmitters

- RSSI (Received Signal Strength Indicator) With Output Signal Dynamic Range of 65 dB

- Low In-band Sensitivity Change of Typically ±2.0 dB Within ±160-kHz Center

Frequency Change in the Complete Temperature and Supply Voltage Range

- Sophisticated Threshold Control and Quasi-peak Detector Circuit in the Data Slicer

- Fast and Stable XTO Start-up Circuit (> −1.4 kΩ Worst-case Start Impedance)

- Clock Generation for Microcontroller

- ESD Protection at all Pins (±4 kV HBM, ±200V MM, ±500V FCDM)

- Dual Supply Voltage Range: 2.7V to 3.3V or 4.5V to 5.5V

- Temperature Range: -40°C to +105°C

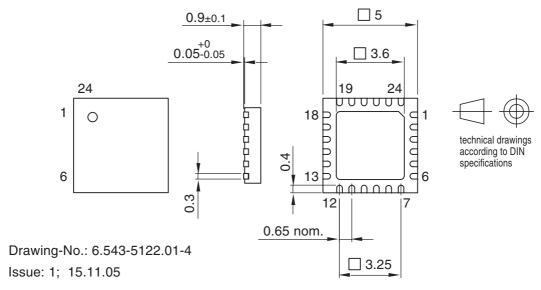

- Small 5 mm × 5 mm QFN24 Package

## **Applications**

- Automotive Keyless Entry and Tire Pressure Monitoring Systems

- Alarm, Telemetering and Energy Metering Systems

#### **Benefits**

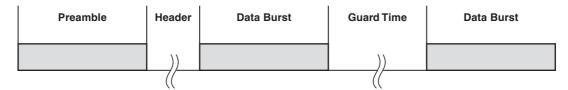

- Supports Header and Blanking Periods of Protocols Common in RKE and TPM Systems (Up to 52 ms in ASK Mode)

- All RF Relevant Functions are Integrated. The Single-ended RF Input is Suited for Easy Adaptation to  $\lambda$  / 4 or Printed-loop Antennas

- Allows a Low-cost Application With Only 8 Passive Components

- Suitable for use in a Receiver for Joint RKE and TPMS

- Optimal Bandwidth Maximizes Sensitivity while Maintaining SAW Transmitter Compatibility

- Clock Output Provides an External Microcontroller Crystal-precision Time Reference

- Well Suited for Use With PLL Transmitter ATA5756/ATA5757

# UHF ASK/FSK Receiver

ATA5745 ATA5746

**Preliminary**

## 1. General Description

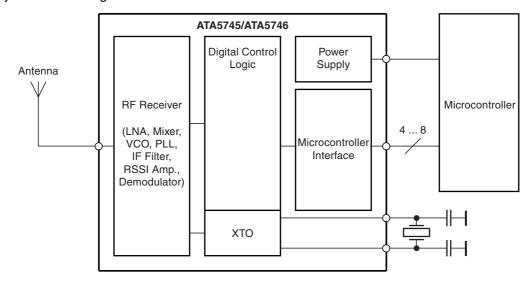

The ATA5745/ATA5746 is a UHF ASK/FSK transparent receiver IC with low power consumption supplied in a small QFN24 package (body 5 mm  $\times$  5 mm, pitch 0.65 mm). ATA5745 is used in the 433 MHz to 435 MHz band of operation, and ATA5746 in 313 MHz to 317 MHz. The IC combines the functionality of remote keyless entry (RKE - typically low bit rate ASK) and tire pressure monitoring (TPM - typically high bit rate FSK) into one receiver under the control of an external microcontroller such as an ATmega48 (AVR®).

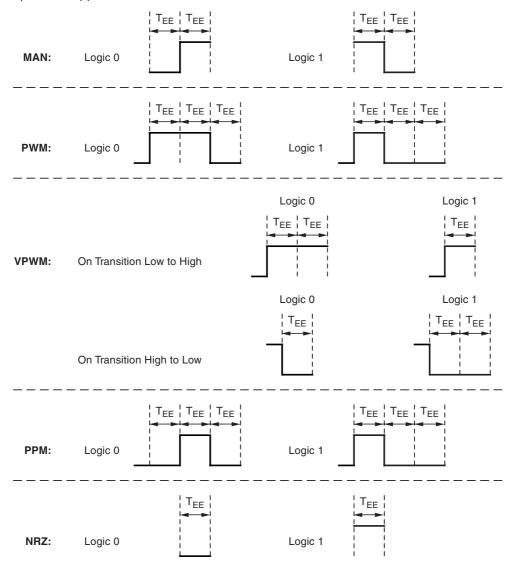

For improved image rejection and selectivity, the IF frequency is fixed to 440 kHz. The IF block uses an 8th-order band pass yielding a receive bandwidth of 420 kHz. This enables the use of the receiver in both SAW- and PLL-based transmitter systems utilizing various types of data-bit encoding such as pulse width modulation, Manchester modulation, variable pulse modulation, pulse position modulation, and NRZ. Prevailing encryption protocols such as Keeloq® are easily supported due to the receiver's ability to hold the current data slicer threshold for up to 52 ms when incoming RF telegrams contain a blanking interval. This feature eliminates erroneous noise from appearing on the demodulated data output pin, and simplifies software decoding algorithms. The decoding of the data stream must be carried out by a connected microcontroller device. Because of the highly integrated design, the only required RF components are for the purpose of receiver antenna matching.

ATA5745 and ATA5746 support Manchester bit rates of 1 Kbit/s to 10 Kbits/s in ASK and 1 Kbit/s to 20 Kbits/s in FSK mode. The four discrete bit rate passbands are selectable and cover 1.0 Kbit/s to 2.5 Kbits/s, 2.0 Kbits/s to 5.0 Kbits/s, 4.0 Kbits/s to 10.0 Kbits/s, and 8.0 Kbits/s to 10.0 Kbits/s or 20.0 Kbits/s (for ASK or FSK, respectively). The receiver contains an RSSI output to provide an indication of received signal strength and a SENSE input to allow the customer to select a threshold below which the DATA signal is gated off. ASK/FSK and bit rate ranges are selected by the connected microcontroller device via pins ASK\_NFSK, BR0, and BR1.

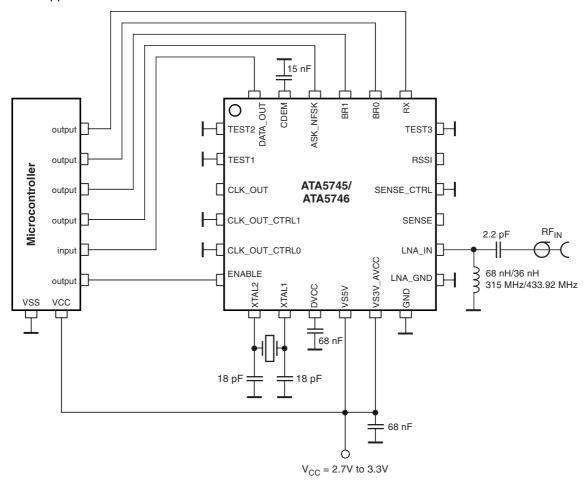

Figure 1-1. System Block Diagram

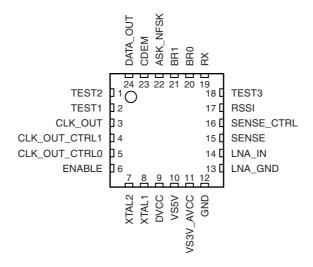

Figure 1-2. Pinning QFN24

Table 1-1. Pin Description

| Table 1-1. | i iii bescription |                                                                          |  |  |

|------------|-------------------|--------------------------------------------------------------------------|--|--|

| Pin        | Symbol            | Function                                                                 |  |  |

| 1          | TEST2             | Test pin, during operation at GND                                        |  |  |

| 2          | TEST1             | Test pin, during operation at GND                                        |  |  |

| 3          | CLK_OUT           | Output to clock a connected microcontroller                              |  |  |

| 4          | CLK_OUT_CTRL1     | Input to control CLK_OUT (MSB)                                           |  |  |

| 5          | CLK_OUT_CTRL0     | Input to control CLK_OUT (LSB)                                           |  |  |

| 6          | ENABLE            | Input to enable the XTO                                                  |  |  |

| 7          | XTAL2             | Reference crystal                                                        |  |  |

| 8          | XTAL1             | Reference crystal                                                        |  |  |

| 9          | DVCC              | Digital voltage supply blocking                                          |  |  |

| 10         | VS5V              | Power supply input for voltage range 4.5V to 5.5V                        |  |  |

| 11         | VS3V_AVCC         | Power supply input for voltage range 2.7V to 3.3V                        |  |  |

| 12         | GND               | Ground                                                                   |  |  |

| 13         | LNA_GND           | RF ground                                                                |  |  |

| 14         | LNA_IN            | RF input                                                                 |  |  |

| 15         | SENSE             | Sensitivity control resistor                                             |  |  |

| 16         | SENSE_CTRL        | Sensitivity selection Low: Normal sensitivity, High: Reduced sensitivity |  |  |

| 17         | RSSI              | Output of the RSSI amplifier                                             |  |  |

| 18         | TEST3             | Test pin, during operation at GND                                        |  |  |

| 19         | RX                | Input to activate the receiver                                           |  |  |

| 20         | BR0               | Bit rate selection, LSB                                                  |  |  |

| 21         | BR1               | Bit rate selection, MSB                                                  |  |  |

| 22         | ASK_NFSK          | FSK/ASK selection<br>Low: FSK, High: ASK                                 |  |  |

| 23         | CDEM              | Capacitor to adjust the lower cut-off frequency data filter              |  |  |

| 24         | DATA_OUT          | Data output                                                              |  |  |

|            | GND               | Ground/backplane (exposed die pad)                                       |  |  |

|            | and               | Ground/backplaire (exposed die pad)                                      |  |  |

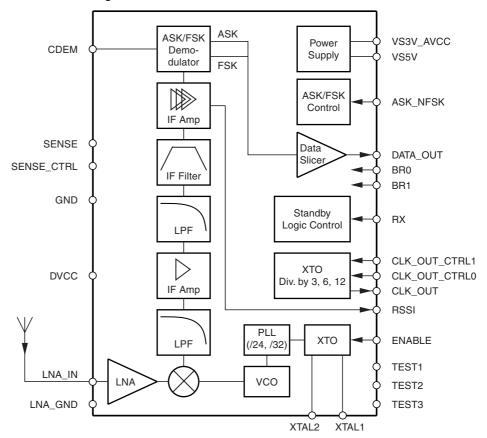

Figure 1-3. Block Diagram

#### 2. RF Receiver

As seen in Figure 1-3 on page 4, the RF receiver consists of a low-noise amplifier (LNA), a local oscillator, and the signal processing part with mixer, IF filter, IF amplifier with analog RSSI, FSK/ASK demodulator, data filter, and data slicer.

In receive mode, the LNA pre-amplifies the received signal which is converted down to a 440-kHz intermediate frequency (IF), then filtered and amplified before it is fed into an FSK/ASK demodulator, data filter, and data slicer. The received signal strength indicator (RSSI) signal is available at the pin RSSI.

#### 2.1 Low-IF Receiver

The receive path consists of a fully integrated low-IF receiver. It fulfills the sensitivity, blocking, selectivity, supply voltage, and supply current specification needed to design an automotive integrated receiver for RKE and TPM systems. A benefit of the integrated receive filter is that no external components needed.

At 315 MHz, the ATA5745 receiver (433.92 MHz for the ATA5746 receiver) has a typical system noise figure of 6.0 dB (7.0 dB), a system I1dBCP of -31 dBm (-30 dBm), and a system IIP3 of -24 dBm (-23 dBm). The signal path is linear for out-of-band disturbers up to the I1dBCP and hence there is no AGC or switching of the LNA needed, and a better blocking performance is achieved. This receiver uses an IF (intermediate frequency) of 440 kHz, the typical image rejection is 30 dB and the typical 3-dB IF filter bandwidth is 420 kHz ( $f_{\rm IF} = 440$  kHz  $\pm 210$  kHz,  $f_{\rm Io\_IF} = 230$  kHz and  $f_{\rm hi\_IF} = 650$  kHz). The demodulator needs a signal-to-noise ratio of 8.5 dB for 10 Kbits/s Manchester with  $\pm 38$  kHz frequency deviation in FSK mode, thus, the resulting sensitivity at 315 MHz (433.92 MHz) is typically -105 dBm (-104 dBm).

Due to the low phase noise and spurs of the synthesizer together with the 8th-order integrated IF filter, the receiver has a better selectivity and blocking performance than more complex double superhet receivers, without using external components and without numerous spurious receiving frequencies.

A low-IF architecture is also less sensitive to second-order intermodulation (IIP2) than direct conversion receivers where every pulse or amplitude modulated signal (especially the signals from TDMA systems like GSM) demodulates to the receiving signal band at second-order non-linearities.

## 2.2 Input Matching at LNA\_IN

The measured input impedances as well as the values of a parallel equivalent circuit of these impedances can be seen in Table 2-1. The highest sensitivity is achieved with power matching of these impedances to the source impedance.

Table 2-1. Measured Input Impedances of the LNA\_IN Pin

| f <sub>RF</sub> [MHz] | Z <sub>In</sub> (RF_IN) [Ω] | $R_{ln_p}/\!/C_{ln_p}$ [pF] |

|-----------------------|-----------------------------|-----------------------------|

| 315                   | (72.4 – j298)               | 1300Ω//1.60                 |

| 433.92                | (55 – j216)                 | 900Ω//1.60                  |

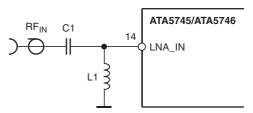

The matching of the LNA input to  $50\Omega$  is done using the circuit shown in Figure 2-1 and the values of the matching elements given in Table 2-2. The reflection coefficients were always  $\leq$  -10 dB. Note that value changes of C1 and L1 may be necessary to compensate individual board layout parasitics. The measured typical FSK and ASK Manchester-code sensitivities with a bit error rate (BER) of  $10^{-3}$  are shown in Table 2-3 and Table 2-4 on page 7. These measurements were done with wire-wound inductors having quality factors reported in Table 2-2, resulting in estimated matching losses of 0.8 dB at 315 MHz and 433.92 MHz. These losses can be estimated when calculating the parallel equivalent resistance of the inductor with  $R_{loss} = 2 \times \pi \times f \times L \times Q_L$  and the matching loss with  $10 \log(1 + R_{ln~p} / R_{loss})$ .

**Figure 2-1.** Input Matching to  $50\Omega$

**Table 2-2.** Input Matching to  $50\Omega$

| f <sub>RF</sub> [MHz] | C <sub>1</sub> [pF] | L <sub>1</sub> [nH] | Q <sub>L1</sub> |

|-----------------------|---------------------|---------------------|-----------------|

| 315                   | 2.2                 | 68                  | 20              |

| 433.92                | 2.2                 | 36                  | 15              |

**Table 2-3.** Measured Typical Sensitivity FSK,  $\pm 38$  kHz, Manchester, BER =  $10^{-3}$

| RF Frequency | BR_Range_0<br>1.0 Kbit/s | BR_Range_0<br>2.5 Kbits/s | BR_Range_1<br>5 Kbits/s | BR_Range_2<br>10 Kbits/s | BR_Range_3<br>10 Kbits/s | BR_Range_3<br>20 Kbits/s |

|--------------|--------------------------|---------------------------|-------------------------|--------------------------|--------------------------|--------------------------|

| 315 MHz      | –108 dBm                 | –108 dBm                  | –107 dBm                | −105 dBm                 | -104 dBm                 | –104 dBm                 |

| 433.92 MHz   | –107 dBm                 | –107 dBm                  | –106 dBm                | -104 dBm                 | –103 dBm                 | –103 dBm                 |

**Table 2-4.** Measured Typical Sensitivity 100% ASK, Manchester, BER =  $10^{-3}$

| RF Frequency | BR_Range_0<br>1.0 Kbit/s | BR_Range_0<br>2.5 Kbits/s | BR_Range_1<br>5 Kbits/s | BR_Range_2<br>10 Kbits/s | BR_Range_3<br>10 Kbits/s |

|--------------|--------------------------|---------------------------|-------------------------|--------------------------|--------------------------|

| 315 MHz      | –114 dBm                 | –114 dBm                  | –113 dBm                | –111 dBm                 | −109 dBm                 |

| 433.92 MHz   | –113 dBm                 | –113 dBm                  | –112 dBm                | –110 dBm                 | –108 dBm                 |

Conditions for the sensitivity measurement:

The given sensitivity values are valid for Manchester-modulated signals. For the sensitivity measurement the distance from edge to edge must be evaluated. As can be seen in Figure 6-1 on page 24, in a Manchester-modulated data stream, the time segments  $T_{FF}$  and  $2 \times T_{FF}$  occur.

To reach the specified sensitivity for the evaluation of  $T_{EE}$  and  $2 \times T_{EE}$  in the data stream, the following limits should be used ( $T_{EE}$  min,  $T_{EE}$  max,  $2 \times T_{EE}$  min,  $2 \times T_{EE}$  max).

Table 2-5. Limits for Sensitivity Measurements

| Bit Rate    | T <sub>EE</sub> Min | T <sub>EE</sub> Typ | T <sub>EE</sub> Max | 2× T <sub>EE</sub> Min | 2 × T <sub>EE</sub> Typ | $2 \times \mathbf{T}_{\mathbf{EE}}  \mathbf{Max}$ |

|-------------|---------------------|---------------------|---------------------|------------------------|-------------------------|---------------------------------------------------|

| 1.0 Kbit/s  | 260 μs              | 500 μs              | 790 µs              | 800 µs                 | 1000 µs                 | 1340 µs                                           |

| 2.4 Kbits/s | 110 µs              | 208 μs              | 310 µs              | 320 µs                 | 416 µs                  | 525 µs                                            |

| 5.0 Kbits/s | 55 µs               | 100 μs              | 155 µs              | 160 µs                 | 200 μs                  | 260 µs                                            |

| 9.6 Kbits/s | 27 μs               | 52 µs               | 78 µs               | 81 µs                  | 104 µs                  | 131 µs                                            |

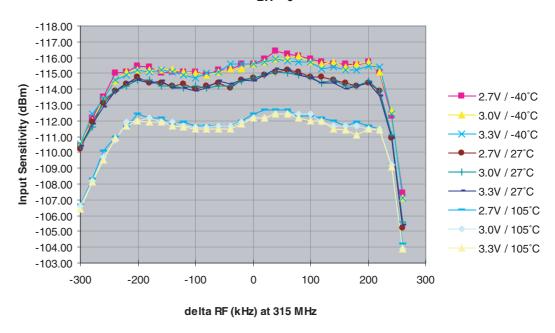

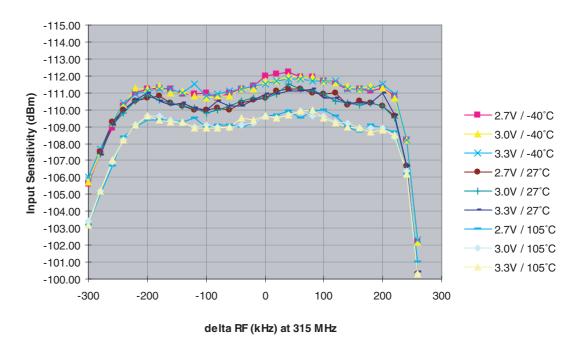

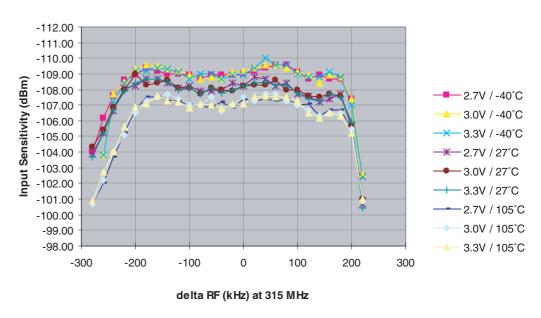

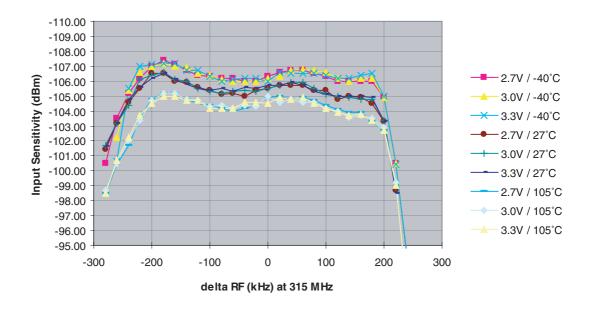

## 2.3 Sensitivity Versus Supply Voltage, Temperature and Frequency Offset

To calculate the behavior of a transmission system, it is important to know the reduction of the sensitivity due to several influences. The most important are frequency offset due to crystal oscillator (XTO) and crystal frequency (XTAL) errors, temperature and supply voltage dependency of the noise figure, and IF-filter bandwidth of the receiver. Figure 2-2 and Figure 2-3 on page 8 show the typical sensitivity at 315 MHz, ASK, 2.4 Kbits/s and 9.6 Kbits/s, Manchester, Figure 2-4 and Figure 2-5 on page 9 show a typical sensitivity at 315 MHz, FSK, 2.4 Kbits/s and 9.6 Kbits/s,  $\pm$ 38 kHz, Manchester versus the frequency offset between transmitter and receiver at  $T_{amb} = -40^{\circ}\text{C}$ ,  $\pm$ 25°C, and  $\pm$ 105°C and supply voltage VS = VS3V\_AVCC = VS5V = 2.7V, 3.0V and 3.3V.

**Figure 2-2.** Measured Sensitivity (315 MHz, ASK, 2.4 Kbits/s, Manchester) Versus Frequency Offset

Input Sensitivity (dBm) at BER < 1e-3, ATA5746, ASK, 2.4 Kbits/s (Manchester), BR = 0

**Figure 2-3.** Measured Sensitivity (315 MHz, ASK, 9.6 Kbits/s, Manchester) Versus Frequency Offset

Input Sensitivity (dBm) at BER < 1e-3, ATA5746, ASK, 9.6 Kbits/s (Manchester), BR = 2

**Figure 2-4.** Measured Sensitivity (315 MHz, FSK, 2.4 Kbits/s, ±38 kHz, Manchester) Versus Frequency Offset

Input Sensitivity (dBm) at BER < 1e-3, ATA5746, FSK, 2.4 Kbits/s (Manchester), BR0

**Figure 2-5.** Measured Sensitivity (315 MHz, FSK, 9.6 Kbits/s, ±38 kHz, Manchester) Versus Frequency Offset

Input Sensitivity (dBm) at BER < 1e-3, ATA5746, FSK, 9.6 Kbits/s (Manchester), BR = 2

As can be seen in Figure 2-5 on page 9, the supply voltage has almost no influence. The temperature has an influence of about  $\pm 1.0$  dB, and a frequency offset of  $\pm 160$  kHz also influences by about  $\pm 1$  dB. All these influences, combined with the sensitivity of a typical IC (-105 dB), are then within a range of -103.0 dBm and -107.0 dBm over temperature, supply voltage, and frequency offset. The integrated IF filter has an additional production tolerance of  $\pm 10$  kHz, hence, a frequency offset between the receiver and the transmitter of  $\pm 160$  kHz can be accepted for XTAL and XTO tolerances.

Note: For the demodulator used in the ATA5745/ATA5746, the tolerable frequency offset does not change with the data frequency. Hence, the value of ±160 kHz is valid for 1 Kbit/s to 10 Kbits/s.

This small sensitivity change over supply voltage, frequency offset, and temperature is very unusual in such a receiver. It is achieved by an internal, very fast, and automatic frequency correction in the FSK demodulator after the IF filter, which leads to a higher system margin. This frequency correction tracks the input frequency very quickly. If, however, the input frequency makes a larger step (for example, if the system changes between different communication partners), the receiver has to be restarted. This can be done by switching back to Standby mode and then again to Active mode (pin RX 1  $\rightarrow$ 0  $\rightarrow$ 1) or by generating a positive pulse on pin ASK\_NFSK (0  $\rightarrow$ 1  $\rightarrow$ 0).

#### 2.4 Frequency Accuracy of the Crystals in a Combined RKE and TPM System

In a tire pressure measurement system working at 315 MHz and using an ATA5756 as transmitter and an ATA5746 is receiver, the higher frequency tolerances and the tolerance of the frequency deviation of the transmitter has to be considered.

In the TPM transmitter, the crystal has a frequency error over temperature  $-40^{\circ}$ C to  $125^{\circ}$ C, aging, and tolerance of  $\pm 80$  ppm ( $\pm 25.2$  kHz at 315 MHz). The tolerances of the XTO, the capacitors used for FSK modulation, and the stray capacitances cause an additional frequency error of  $\pm 30$  ppm ( $\pm 9.45$  kHz at 315 MHz). The frequency deviation of such a transmitter varies between  $\pm 16$  kHz and  $\pm 24$  kHz, since a higher frequency deviation is equivalent to a frequency error this has to be considered as an additional  $\pm 24$  kHz –  $\pm 19.5$  kHz =  $\pm 4.5$ kHz frequency tolerance (19.5 kHz is constant). All tolerances added, these transmitters have a worst-case frequency offset of  $\pm 39.15$  kHz.

For the receiver in the car, a tolerance of  $\pm 160$  kHz  $-\pm 39.15$  kHz  $=\pm 120.85$  kHz ( $\pm 383.6$  ppm) remains. The needed frequency stability of the crystals over temperature and aging is  $\pm 383.6$  ppm  $-\pm 5$  ppm  $=\pm 378.6$  ppm. The aging of such a crystal is  $\pm 10$  ppm, leaving a reasonable  $\pm 368.6$  ppm for the temperature dependency of the crystal frequency in the car.

Since the receiver in the car is able to receive these TPM transmitter signals with high frequency offsets, the component specification in the key can be largely relaxed.

This system calculation is based on worst-case tolerances of all the components; this leads in practice to a system with margin.

For a 433.92 MHz TPM system using ATA5757 as transmitter and ATA5745 as receiver, the same calculation must be done, but since the RF frequency is higher, every ppm of crystal tolerances results in higher frequency offset and either the system must have lower tolerances or a lower margin at this frequency.

#### 2.5 RX Supply Current Versus Temperature and Supply Voltage

Table 2-7 shows the typical supply current of the receiver in Active mode versus supply voltage and temperature with VS = VS3V\_AVCC = VS5V.

**Table 2-6.** Measured Current in Active Mode ASK

| VS = VS3V_AVCC = VS5V    | 2.7V   | 3.0V   | 3.3V   |

|--------------------------|--------|--------|--------|

| $T_{amb} = -40$ °C       | 5.4 mA | 5.5 mA | 5.6 mA |

| T <sub>amb</sub> = 25°C  | 6.4 mA | 6.5 mA | 6.6 mA |

| T <sub>amb</sub> = 105°C | 7.4 mA | 7.5 mA | 7.6 mA |

Table 2-7. Measured Current in Active Mode FSK

| VS = VS3V_AVCC = VS5V    | 2.7V   | 3.0V   | 3.3V   |

|--------------------------|--------|--------|--------|

| $T_{amb} = -40$ °C       | 5.6 mA | 5.7 mA | 5.8 mA |

| $T_{amb} = 25^{\circ}C$  | 6.6 mA | 6.7 mA | 6.8 mA |

| T <sub>amb</sub> = 105°C | 7.6 mA | 7.7 mA | 7.8 mA |

#### 2.6 Blocking, Selectivity

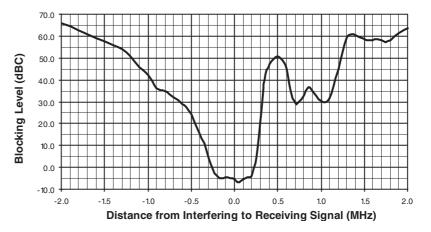

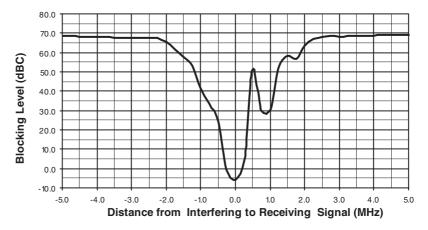

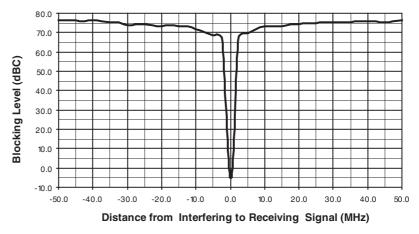

As can be seen in Figure 2-6 on page 11, and Figure 2-7 and Figure 2-8 on page 12, the receiver can receive signals 3 dB higher than the sensitivity level in the presence of large blockers of –34.5 dBm or –28 dBm with small frequency offsets of ±3 MHz or ±20 MHz.

Figure 2-6, and Figure 2-7 on page 12 show the narrow-band blocking, and Figure 2-8 on page 12 shows the wide-band blocking characteristic. The measurements were done with a useful signal of 315 MHz, FSK, 10 Kbits/s,  $\pm 38$  kHz, Manchester, BR\_Range2 with a level of -105 dBm + 3 dB = -102 dBm, which is 3 dB above the sensitivity level. The figures show how much larger than -102 dBm a continuous wave signal can be, until the BER is higher than  $10^{-3}$ . The measurements were done at the  $50\Omega$  input shown in Figure 2-1 on page 6. At 3 MHz, for example, the blocker can be 67.5 dBC higher than -102 dBm, or -102 dBm + 67.5 dBC = -34.5 dBm.

Figure 2-6. Close-in 3-dB Blocking Characteristic and Image Response at 315 MHz

Figure 2-7. Narrow-band 3-dB Blocking Characteristic at 315 MHz

Figure 2-8. Wide-band 3-dB Blocking Characteristic at 315 MHz

Table 2-8 shows the blocking performance measured relative to -102 dBm for some frequencies. Note that sometimes the blocking is measured relative to the sensitivity level 104 dBm (denoted dBS), instead of the carrier -102 dBm (denoted dBC)

**Table 2-8.** Blocking 3 dB Above Sensitivity Level With BER  $< 10^{-3}$

| Frequency Offset | Blocking Level | Blocking           |

|------------------|----------------|--------------------|

| +1.5 MHz         | −44.5 dBm      | 57.5 dBC, 60.5 dBS |

| −1.5 MHz         | −44.5 dBm      | 57.5 dBC, 60.5 dBS |

| +2 MHz           | −39.0 dBm      | 63 dBC, 66 dBS     |

| –2 MHz           | −36.0 dBm      | 66 dBC, 69 dBS     |

| +3 MHz           | −34.5 dBm      | 67.5 dBC, 70.5 dBS |

| –3 MHz           | −34.5 dBm      | 67.5 dBC, 70.5 dBS |

| +20 MHz          | −28.0 dBm      | 74 dBC, 77 dBS     |

| –20 MHz          | −28.0 dBm      | 74 dBC, 77 dBS     |

The ATA5745/ATA5746 can also receive FSK and ASK modulated signals if they are much higher than the I1dBCP. It can typically receive useful signals at –10 dBm. This is often referred to as the nonlinear dynamic range (that is, the maximum to minimum receiving signal), and is 95 dB for 10 Kbits/s Manchester (FSK). This value is useful if the transmitter and receiver are very close to each other.

#### 2.7 In-band Disturbers, Data Filter, Quasi-peak Detector, Data Slicer

If a disturbing signal falls into the received band, or if a blocker is not a continuous wave, the performance of a receiver strongly depends on the circuits after the IF filter. Hence, the demodulator, data filter, and data slicer are important.

The data filter of the ATA5745/ATA5746 functions also as a quasi-peak detector. This results in a good suppression of above mentioned disturbers and exhibits a good carrier-to-noise performance. The required useful-signal-to-disturbing-signal ratio, at a BER of  $10^{-3}$ , is less than 14 dB in ASK mode and less than 3 dB (BR\_Range\_0 to BR\_Range\_2) and 6 dB (BR\_Range\_3) in FSK mode. Due to the many different possible waveforms, these numbers are measured for the signal, as well as for disturbers, with peak amplitude values. Note that these values are worst-case values and are valid for any type of modulation and modulating frequency of the disturbing signal, as well as for the receiving signal. For many combinations, lower carrier-to-disturbing-signal ratios are needed.

#### 2.8 RSSI Output

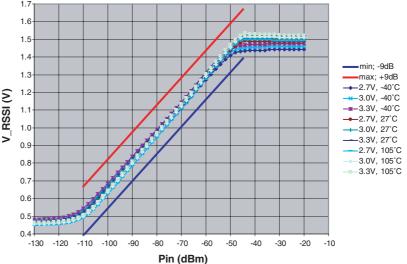

The output voltage of the pin RSSI is an analog voltage, proportional to the input power level. Using the RSSI output signal, the signal strength of different transmitters can be distinguished. The usable dynamic range of the RSSI amplifier is 65 dB, the input power range P(RF $_{\rm IN}$ ) is -110 dBm to -45 dBm, and the gain is 15 mV/dB. Figure 2-9 shows the RSSI characteristic of a typical device at 315 MHz with VS3V\_AVCC = VS5V = 2.7V to 3.3V and  $T_{\rm amb}$  =  $-40\,^{\circ}$ C to  $+105\,^{\circ}$ C with a matched input as shown in Table 2-2 and Figure 2-1 on page 6. At 433.92 MHz, 1 dB more signal level is needed for the same RSSI results.

As can be seen in Figure 2-9 on page 13, for single devices there is a variance over temperature and supply voltage range of  $\pm 3$  dB. The total variance over production, temperature, and supply voltage range is  $\pm 9$  dB.

#### 2.9 Frequency Synthesizer

The LO generates the carrier frequency for the mixer via a PLL synthesizer. The XTO (crystal oscillator) generates the reference frequency  $f_{\rm XTO}$ . The VCO (voltage-controlled oscillator) generates the drive voltage frequency  $f_{\rm LO}$  for the mixer.  $f_{\rm LO}$  is divided by the factor 24 (ATA5746) or 32 (ATA5745). The divided frequency is compared to  $f_{\rm XTO}$  by the phase frequency detector. The current output of the phase frequency detector is connected to the fully integrated loop filter, and thereby generates the control voltage for the VCO. By means of that configuration, the VCO is controlled in a way, such that  $f_{\rm LO}$  / 24 ( $f_{\rm LO}$  / 32) is equal to  $f_{\rm XTO}$ . If  $f_{\rm LO}$  is determined,  $f_{\rm XTO}$  can be calculated using the following formula:  $f_{\rm XTO} = f_{\rm LO}$  / 24 ( $f_{\rm XTO} = f_{\rm LO}$  / 32). The synthesizer has a phase noise of –130 dBC/Hz at 3 MHz and spurs of –75 dBC.

Care must be taken with the harmonics of the CLK output signal, as well as with the harmonics produced by a microprocessor clocked using the signal, as these harmonics can disturb the reception of signals.

#### 3. XTO

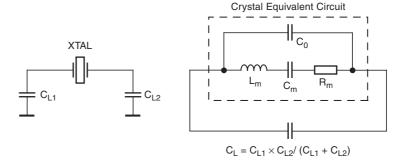

The XTO is an amplitude-regulated Pierce oscillator type with external load capacitances  $(2 \times 16 \text{ pF})$ . Due to additional internal and board parasitics  $(C_P)$  of approximately 2 pF on each side, the load capacitance amounts to  $2 \times 18 \text{ pF}$  (9 pF total).

The XTO oscillation frequency  $f_{XTO}$  is the reference frequency for the integer-N synthesizer. When designing the system in terms of receiving and transmitting frequency offset, the accuracy of the crystal and XTO have to be considered.

The XTO's additional pulling (including the  $R_M$  tolerance) is only ±5 ppm. The XTAL versus temperature, aging, and tolerances is then the main source of frequency error in the local oscillator.

The XTO frequency depends on XTAL properties and the load capacitances  $C_{L1,2}$  at pin XTAL1 and XTAL2. The pulling (p) of  $f_{XTO}$  from the nominal  $f_{XTAL}$  is calculated using the following formula:

$$p = \frac{C_{m}}{2} \times \frac{C_{LN} - C_{L}}{(C_{O} + C_{LN}) \times (C_{O} + C_{L})} \times 10^{-6} ppm$$

$C_m$ , the crystal's motional capacitance;  $C_0$ , the shunt capacitance; and  $C_{LN}$ , the nominal load capacitance of the XTAL, are found in the datasheet.  $C_L$  is the total actual load capacitance of the crystal in the circuit, and consists of  $C_{L1}$  and  $C_{L2}$  connected in series.

Figure 3-1. Crystal Equivalent Circuit

With  $C_m \le 10$  fF,  $C_0 \ge 1.0$  pF,  $C_{LN} = 9$  pF and  $C_{L1,2} = 16$  pF  $\pm 1\%$ , the pulling amounts to P  $\le \pm 1$  ppm.

The  $C_0$  of the XTAL has to be lower than  $C_{Lmin}$  / 2 = 7.9 pF for a Pierce oscillator type in order to not enter the steep region of pulling versus load capacitance where there is risk of an unstable oscillation.

To ensure proper start-up behavior, the small signal gain and the negative resistance provided by this XTO at start is very large. For example, oscillation starts up even in the worst case with a crystal series resistance of 1.5 k $\Omega$  at  $C_0 \le 2.2$  pF with this XTO. The negative resistance is approximately given by

$$\text{Re}\{\text{Zxtocore}\} = \text{Re}\left\{\frac{\text{Z}_1 \times \text{Z}_3 + \text{Z}_2 \times \text{Z}_3 + \text{Z}_1 \times \text{Z}_3 \times \text{gm}}{\text{Z}_1 + \text{Z}_2 + \text{Z}_3 + \text{Z}_1 \times \text{Z}_2 \times \text{gm}}\right\}$$

with Z<sub>1</sub> and Z<sub>2</sub> as complex impedances at pins XTAL1 and XTAL2, hence Z<sub>1</sub> = -j /  $(2 \times p \times f_{XTO} \times C_{L1}) + 5\Omega$  and Z<sub>2</sub> = -j /  $(2 \times p \times f_{XTO} \times C_{L2}) + 5\Omega$  Z<sub>3</sub> consists of crystal C<sub>0</sub> in parallel with an internal 110-k $\Omega$  resistor, hence Z<sub>3</sub> = -j /  $(2 \times p \times f_{XTO} \times C_0)$  / 110 k $\Omega$ , gm is the internal transconductance between XTAL1 and XTAL2, with typically 20 mS at 25°C.

With  $f_{XTO}$  = 13.5 MHz, gm = 20 mS,  $C_L$  = 9 pF, and  $C_0$  = 2.2 pF, this results in a negative resistance of about 2 k $\Omega$ . The worst case for technology, supply voltage, and temperature variations is then always higher than 1.4 k $\Omega$  for  $C_0 \le 2.2$  pF.

Due to the large gain at start, the XTO is able to meet a very low start-up time. The oscillation start-up time can be estimated with the time constant  $\tau$ .

$$\tau \ = \ \frac{2}{4 \times \pi^2 \times \left( f_{XTAL}^2 \times C_m \times \left( Re(Z_{xtocore}) + R_m \right) \right)}$$

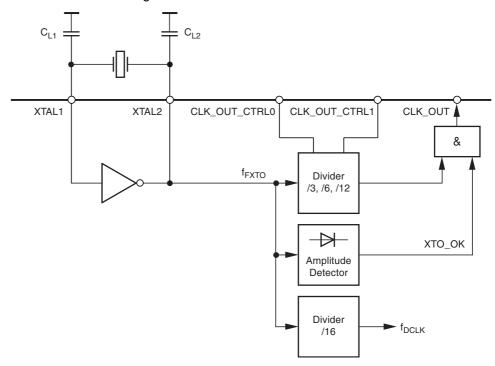

After  $10\tau$  to  $20\tau$ , an amplitude detector detects the oscillation amplitude and sets XTO\_OK to High if the amplitude is large enough; this activates the CLK\_OUT output if it is enabled via the pins CLK\_OUT\_CTRL0 and CLK\_OUT\_CTRL1. Note that the necessary conditions of the DVCC voltage also have to be fulfilled.

It is recommended to use a crystal with  $C_m$  = 3.0 fF to 10 fF,  $C_{LN}$  = 9 pF,  $R_m$  < 120 $\Omega$  and  $C_0$  = 1.0 pF to 2.2 pF.

Lower values of  $C_m$  can be used, slightly increasing the start-up time. Lower values of  $C_0$  or higher values of  $C_m$  (up to 15 fF) can also be used, with only little influence on pulling.

Figure 3-2. XTO Block Diagram

The relationship between  $f_{XTO}$  and the  $f_{RF}$  is shown in Table 3-1.

**Table 3-1.** Calculation of f<sub>RF</sub>

| Frequency [MHz]  | f <sub>XTO</sub> [MHz] | f <sub>RF</sub>                 |

|------------------|------------------------|---------------------------------|

| 433.92 (ATA5745) | 13.57375               | f <sub>XTO</sub> x 32 – 440 kHz |

| 315.0 (ATA5746)  | 13.1433                | f <sub>XTO</sub> x 24 – 440 kHz |

Attention must be paid to the harmonics of the CLK\_OUT output signal  $f_{\text{CLK}\_\text{OUT}}$  as well as to the harmonics produced by an microprocessor clocked with it, since these harmonics can disturb the reception of signals if they get to the RF input. If the CLK\_OUT signal is used, it must be carefully laid out on the application PCB. The supply voltage of the microcontroller must also be carefully blocked.

#### 3.1 Pin CLK\_OUT

Pin CLK\_OUT is an output to clock a connected microcontroller. The clock is available in Standby and Active modes. The frequency f<sub>CLK\_OUT</sub> can be adjusted via the pins CLK\_OUT\_CTRL0 and CLK\_OUT\_CTRL1, and is calculated as follows:

**Table 3-2.** Setting of f<sub>CLK OUT</sub>

| CLK_OUT_CTRL1 | CLK_OUT_CTRL0 | Function                                                        |

|---------------|---------------|-----------------------------------------------------------------|

| 0             | 0             | Clock on pin CLK_OUT is switched off (Low level on pin CLK_OUT) |

| 0             | 1             | $f_{CLK\_OUT} = f_{XTO} / 3$                                    |

| 1             | 0             | $f_{CLK\_OUT} = f_{XTO} / 6$                                    |

| 1             | 1             | $f_{CLK\_OUT} = f_{XTO} / 12$                                   |

The signal at CLK\_OUT output has a nominal 50% duty cycle. To save current, it is recommended that CLK\_OUT be switched off during Standby mode.

## 3.2 Basic Clock Cycle of the Digital Circuitry

The complete timing of the digital circuitry is derived from one clock. As seen in Figure 3-2 on page 16, this clock cycle,  $T_{DCLK}$ , is derived from the crystal oscillator (XTO) in combination with a divider.

$$f_{DCLK} = \frac{f_{XTO}}{16}$$

$T_{DCLK}$  controls the following application relevant parameters:

- Debouncing of the data signal stream

- Start-up time of the RX signal path

The start-up time and the debounce characteristic depend on the selected bit rate range (BR\_Range) which is defined by pins BR0 and BR1. The clock cycle  $T_{XDCLK}$  is defined by the following formulas for further reference:

$$\begin{split} \text{BR\_Range} \Rightarrow & \text{BR\_Range} \ 0: \ T_{\text{XDCLK}} = 8 \times \ T_{\text{DCLK}} \\ \text{BR\_Range} \ 1: \ T_{\text{XDCLK}} = 4 \times \ T_{\text{DCLK}} \\ \text{BR\_Range} \ 2: \ T_{\text{XDCLK}} = 2 \times \ T_{\text{DCLK}} \\ \text{BR\_Range} \ 3: \ T_{\text{XDCLK}} = 1 \times \ T_{\text{DCLK}} \end{split}$$

## 4. Sensitivity Reduction

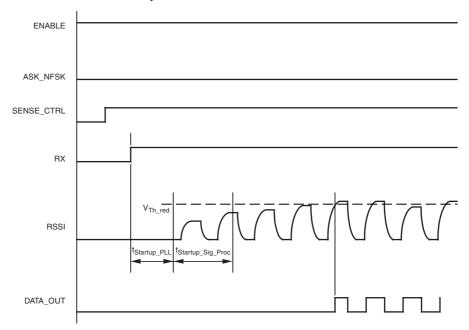

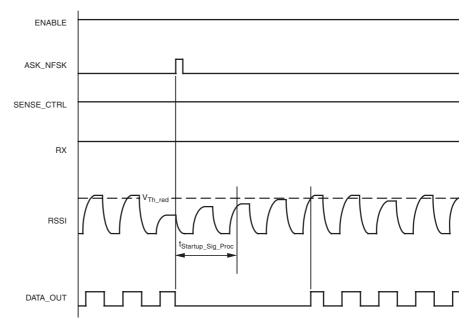

The output voltage of the RSSI amplifier is internally compared to a threshold voltage  $V_{Th\_red}$ .  $V_{Th\_red}$  is determined by the value of the external resistor  $R_{Sense}$ .  $R_{Sense}$  is connected between the pins SENSE and VS3V\_AVCC (see Figure 10-1 on page 28). The output of the comparator is fed into the digital control logic. By this means, it is possible to operate the receiver at a lower sensitivity.

If the level on input pin SENSE\_CTRL is low, the receiver operates at full sensitivity.

If the level on input pin SENSE\_CTRL is high, the receiver operates at a lower sensitivity. The reduced sensitivity is defined by the value of  $R_{Sense}$ , the maximum sensitivity by the signal-to-noise ratio of the LNA input. The reduced sensitivity depends on the signal strength at the output of the RSSI amplifier.

Since different RF input networks may exhibit slightly different values for the LNA gain, the sensitivity values given in the electrical characteristics refer to a specific input matching. This matching is illustrated in Figure 2-1 on page 6 and exhibits the best possible sensitivity.

If the sensitivity reduction feature is not used, pin SENSE can be left open, pin SENSE\_CTRL must be set to GND.

To operate with reduced sensitivity, pin SENSE\_CTRL must be set to high before the RX signal path will be enabled by setting pin RX to high (see Figure 4-1 on page 19). As long as the RSSI level is lower than  $V_{Th\_red}$  (defined by the external resistor  $R_{Sense}$ ) no data stream is available on pin DATA\_OUT (low level on pin DATA\_OUT). An internal RS flip-flop will be set to high the first time the RSSI voltage crosses  $V_{Th\_red}$ , and from then on the data stream will be available on pin DATA\_OUT. From then on the receiver also works with full sensitivity. This makes sure that a telegram will not be interrupted if the RSSI level varies during the transmission. The RS flip-flop can be set back, and thus the receiver switched back to reduced sensitivity, by generating a positive pulse on pin ASK\_NFSK (see Figure 4-2 on page 19). In FSK mode, operating with reduced sensitivity follows the same way.

Figure 4-1. Reduced Sensitivity Active

Figure 4-2. Restart Reduced Sensitivity

## 5. Power Supply

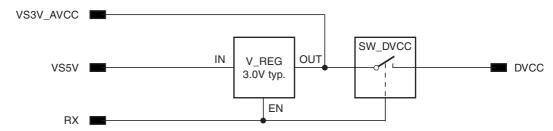

**Figure 5-1.** Power Supply

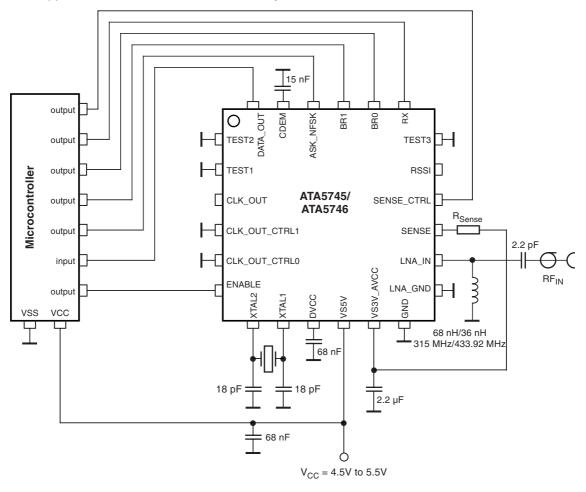

The supply voltage range of the ATA5745/ATA5746 is 2.7V to 3.3V or 4.5V to 5.5V.

Pin VS3V\_AVCC is the supply voltage input for the range 2.7V to 3.3V, and is used in battery applications using a single lithium 3V cell. Pin VS5V is the voltage input for the range 4.5V to 5.5V (car applications) in this case the voltage regulator V\_REG regulates VS3V\_AVCC to typically 3.0V. If the voltage regulator is active, a blocking capacitor of 2.2  $\mu$ F has to be connected to VS3V\_AVCC (see Figure 10-1 on page 28).

DVCC is the internal operating voltage of the digital control logic and is fed via the switch SW\_DVCC by VS3V\_AVCC. DVCC must be blocked on pin DVCC with 68 nF (see Figure 9-1 on page 27 and Figure 10-1 on page 28).

Pin RX is the input to activate the RX signal processing and set the receiver to Active mode.

#### 5.1 OFF Mode

A low level on pin RX and ENABLE will set the receiver to OFF mode (low power mode). In this mode, the crystal oscillator is shut down and no clock is available on pin CLK\_OUT. The receiver is not sensitive to a transmitter signal in this mode.

Table 5-1. Standby Mode

| RX | ENABLE | Function |

|----|--------|----------|

| 0  | 0      | OFF mode |

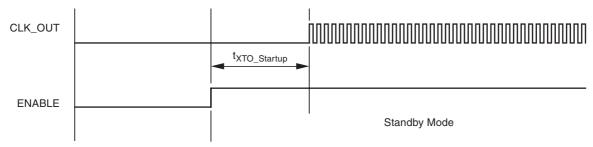

#### 5.2 Standby Mode

The receiver activates the Standby mode if pin ENABLE is set to "1".

In Standby mode, the XTO is running and the clock on pin CLK\_OUT is available after the start-up time of the XTO has elapsed (dependent on pin CLK\_OUT\_CTRL0 and CLK\_OUT\_CTRL1). During Standby mode, the receiver is not sensitive to a transmitter signal.

In Standby mode, the RX signal path is disabled and the power consumption  $I_{Standby}$  is typically 50  $\mu$ A (CLK\_OUT output off, VS3V\_AVCC = VS5V = 3V). The exact value of this current is strongly dependent on the application and the exact operation mode, therefore check the section "Electrical Characteristics: General" on page 29 for the appropriate application case.

**Table 5-2.** Standby Mode

| RX | ENABLE | Function     |

|----|--------|--------------|

| 0  | 1      | Standby mode |

Figure 5-2. Standby Mode (CLK\_OUT\_CTRL0 or CLK\_OUT\_CTRL1 = 1)

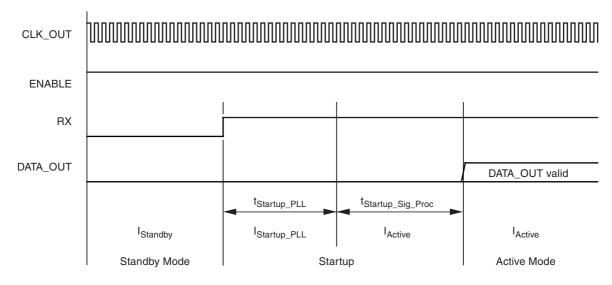

#### 5.3 Active Mode

The Active mode is enabled by setting the level on pin RX to high. In Active mode, the RX signal path is enabled and if a valid signal is present it will be transferred to the connected microcontroller.

**Table 5-3.** Active Mode

| RX | ENABLE | Function    |

|----|--------|-------------|

| 1  | 1      | Active mode |

During  $T_{Startup\_PLL}$  the PLL is enabled and starts up. If the PLL is locked, the signal processing circuit starts up ( $T_{Startup\_Sig\_Proc}$ ). After the start-up time, all circuits are in stable condition and ready to receive. The duration of the start-up sequence depends on the selected bit rate range.

Figure 5-3. Active Mode

Table 5-4. Start-up Time

|     |     | ATA5745 (433.92 MHz)     |                               | ATA5746 (315 MHz)        |                               |  |

|-----|-----|--------------------------|-------------------------------|--------------------------|-------------------------------|--|

| BR1 | BR0 | T <sub>Startup_PLL</sub> | T <sub>Startup_Sig_Proc</sub> | T <sub>Startup_PLL</sub> | T <sub>Startup_Sig_Proc</sub> |  |

| 0   | 0   |                          | 1096 µs                       |                          | 1132 µs                       |  |

| 0   | 1   | 061 up                   | 644 µs                        | 000                      | 665 µs                        |  |

| 1   | 0   | 261 µs                   | 417 µs                        | - 269 μs                 | 431 µs                        |  |

| 1   | 1   |                          | 304 μs                        |                          | 324 µs                        |  |

Table 5-5.Modulation Scheme

| ASK_NFSK | RF <sub>IN</sub> at Pin LNA_IN | Level at Pin DATA_OUT |

|----------|--------------------------------|-----------------------|

| 0        | f <sub>FSK_H</sub>             | 1                     |

|          | f <sub>FSK_L</sub>             | 0                     |

| 4        | f <sub>ASK</sub> on            | 1                     |

| 1        | f <sub>ASK</sub> off           | 0                     |

## 6. Bit Rate Ranges

Configuration of the bit rate ranges is carried out via the two pins BR0 and BR1. The microcontroller uses these two interface lines to set the corner frequencies of the band-pass data filter. Switching the bit rate ranges while the RF front end is in Active mode can be done on the fly and will not take longer than 100  $\mu$ s if done while remaining in either ASK or FSK mode. If the modulation scheme is changed at the same time, the switching time is ( $T_{Startup\_Sig\_Proc}$ , see Figure 7-1 on page 25). Each BR\_Range is defined by a minimum edge-to-edge time. To maintain full sensitivity of the receiver, edge-to-edge transition times of incoming data should not be less than the minimum for the selected BR\_Range.

Table 6-1. BR Ranges ASK

| BR1 | BR0 | BR_Range  | Recommended Bit Rate<br>(Manchester) <sup>(1)</sup> | Minimum Edge-to-edge<br>Time Period T <sub>EE</sub> of the Data<br>Signal <sup>(2)</sup> | Edge-to-edge Time Period T <sub>EE</sub> of<br>the Data Signal During the Start-up<br>Period <sup>(3)</sup> |

|-----|-----|-----------|-----------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 0   | 0   | BR_Range0 | 1.0 Kbit/s to 2.5 Kbits/s                           | 200 μs                                                                                   | 200 μs to 500 μs                                                                                            |

| 0   | 1   | BR_Range1 | 2.0 Kbits/s to 5.0 Kbits/s                          | 100 µs                                                                                   | 100 µs to 250 µs                                                                                            |

| 1   | 0   | BR_Range2 | 4.0 Kbits/s to 10.0 Kbits/s                         | 50 μs                                                                                    | 50 μs to 125 μs                                                                                             |

| 1   | 1   | BR_Range3 | 8.0 Kbits/s to 10.0 Kbits/s                         | 50 μs                                                                                    | 50 μs to 62.5 μs                                                                                            |

Table 6-2. BR Ranges FSK

| BR1 | BR0 | BR_Range  | Recommended Bit Rate<br>(Manchester) <sup>(1)</sup> | Minimum Edge-to-edge<br>Time Period T <sub>EE</sub> of the Data<br>Signal <sup>(2)</sup> | Edge-to-edge Time Period T <sub>EE</sub> of<br>the Data Signal During the Start-up<br>Period <sup>(3)</sup> |

|-----|-----|-----------|-----------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 0   | 0   | BR_Range0 | 1.0 Kbit/s to 2.5 Kbits/s                           | 200 µs                                                                                   | 200 μs to 500 μs                                                                                            |

| 0   | 1   | BR_Range1 | 2.0 Kbits/s to 5.0 Kbits/s                          | 100 µs                                                                                   | 100 μs to 250 μs                                                                                            |

| 1   | 0   | BR_Range2 | 4.0 Kbits/s to 10.0 Kbits/s                         | 50 μs                                                                                    | 50 μs to 125 μs                                                                                             |

| 1   | 1   | BR_Range3 | 8.0 Kbits/s to 20.0 Kbits/s                         | 25 µs                                                                                    | 25 μs to 62.5 μs                                                                                            |

Note: If during the start-up period (T<sub>Startup\_PLL</sub> + T<sub>Startup\_Sig\_Proc</sub>) there is no RF signal, the data filter settles to the noise floor, leading to noise on pin DATA\_OUT.

Notes:

- 1. As can be seen, a bit stream of, for example, 2.5 Kbits/s can be received in BR\_Range0 and BR\_Range1 (overlapping BR\_Ranges). To get the full sensitivity, always use the lowest possible BR\_Range (here, BR\_Range0). The advantage in the next higher BR\_Range (BR\_Range1) is the shorter start-up period, meaning lower current consumption during Polling mode. Thus, it is a decision between sensitivity and current consumption.

- 2. The receiver is also capable of receiving non-Manchester-modulated signals, such as PWM, PPM, VPWM, NRZ. In ASK mode, the header and blanking periods occurring in Keeloq-like protocols (up to 52 ms) are supported.

- 3. To ensure an accurate settling of the data filter during the start-up period ( $T_{Startup\_PLL} + T_{Startup\_Sig\_Proc}$ ), the edge-to-edge time  $T_{EE}$  of the data signal (preamble) must be inside the given limits during this period.

Figure 6-1. Examples of Supported Modulation Formats

Figure 6-2. Supported Header and Blanking Periods

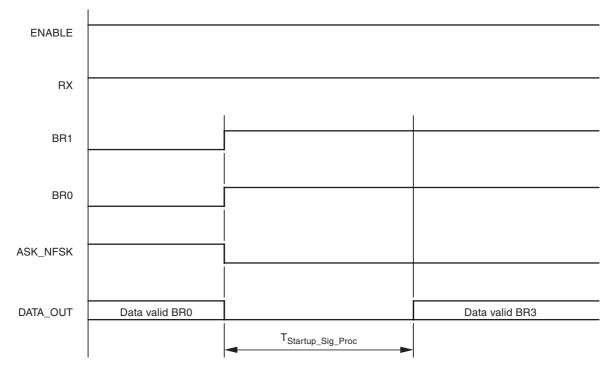

## 7. ASK NFSK

The ASK\_NFSK pin allows the microcontroller to rapidly switch the RF front end between demodulation modes. A logic 1 on this pin selects ASK mode, and a logic 0 FSK mode. The time to change modes ( $T_{Startup\_Sig\_Proc}$ ) depends on the bit rate range being selected (not current bit rate range) and is given in Table 5-4 on page 22. This response time is specified for applications that require an ASK preamble followed by FSK data (for typical TPM applications). During  $T_{Startup\_Sig\_Proc}$ , the level on pin DATA\_OUT is low.

Figure 7-1. ASK Preamble 2.4 Kbits/s followed by FSK Data 9.6 Kbits/s

## 8. Polling Current Calculation

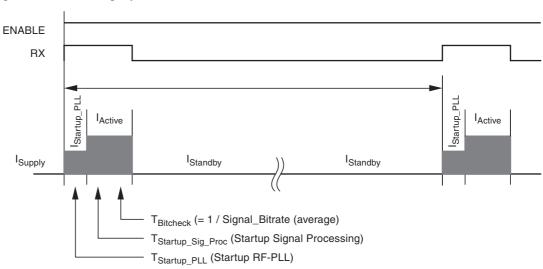

Figure 8-1. Polling Cycle

In an RKE and TPM system, the average chip current in Polling mode, I<sub>Polling</sub>, is an important parameter. The polling period must be controlled by the connected microcontroller via the pins ENABLE and RX. The polling current can be calculated as follows:

$$\begin{split} I_{Polling} &= (T_{Startup\_PLL} \ / \ T_{Polling\_Period}) \times I_{Startup\_PLL} + (T_{Startup\_Sig\_Proc} \ / \ T_{Polling\_Period}) \times I_{Active} + \\ &(T_{Bitcheck} \ / \ T_{Polling\_Period}) \times I_{Active} + (T_{Polling\_Period} - T_{Startup\_PLL} - T_{Startup\_Sig\_Proc} - T_{Bitcheck}) \ / \\ &T_{Polling\_Period} \times I_{Standby} \end{split}$$

T<sub>Startup PLL</sub>: depends on 315 MHz/433.92 MHz application.

T<sub>Startup\_Sig\_Proc</sub>: depends on 315 MHz/433.92 MHz application and the selected bit

rate range.

T<sub>Bitcheck</sub>: depends on the signal bit rate (1 / Signal\_Bit\_Rate).

T<sub>Polling Period</sub>: depends on the transmitter telegram (preburst).

I<sub>Startup\_PLL</sub>: depends on 3V or 5V application and the setting of pin CLK\_OUT.

I<sub>Active</sub>: depends on 3V or 5V application, ASK or FSK mode and the setting of

pin CLK OUT.

I<sub>Standby</sub>: depends on 3V or 5V application and the setting of pin CLK\_OUT.

Example:- 315-MHz application (ATA5746), bit rate: 9.6 Kbits/s, T<sub>Polling Period</sub> = 8 ms

$--> T_{Startup PLL} = 269 \mu s$

$--> T_{Startup Sig Proc} = 324 \,\mu s$  (Bit Rate Range 3)

$--> T_{Bitcheck}$  = 104 µs

3V application; ASK mode, CLK OUT disabled

$--> I_{Startup\_PLL}$  = 4.5 mA  $--> I_{Active}$  = 6.5 mA  $--> I_{Standby}$  = 0.05 mA

$--> I_{Polling} = 0.545 \text{ mA}$

# 9. 3V Application

Figure 9-1. 3V Application

Note: Paddle (backplane) must be connected to GND

# 10. 5V Application

Figure 10-1. 5V Application With Reduced/Full Sensitivity

Note: Paddle (backplane) must be connected to GND

## 11. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                                           | Symbol              | Min.        | Max. | Unit |

|----------------------------------------------------------------------|---------------------|-------------|------|------|

| Junction temperature                                                 | T <sub>j</sub>      |             | +150 | °C   |

| Storage temperature                                                  | T <sub>stg</sub>    | <b>-</b> 55 | +125 | °C   |

| Ambient temperature                                                  | T <sub>amb</sub>    | -40         | +105 | °C   |

| Supply voltage VS5V                                                  | V <sub>S</sub>      |             | +6   | V    |

| ESD (Human Body Model ESD S 5.1) every pin                           | НВМ                 | -4          | +4   | kV   |

| ESD (Machine Model JEDEC A115A) every pin                            | MM                  | -200        | +200 | V    |

| ESD (Field Induced Charge Device Model ESD STM 5.3.1-1999) every pin | FCDM                | -500        | +500 | V    |

| Maximum input level, input matched to $50\Omega$                     | P <sub>in_max</sub> |             | 0    | dBm  |

#### 12. Thermal Resistance

| Parameters       | Symbol     | Value | Unit |

|------------------|------------|-------|------|

| Junction ambient | $R_{thJA}$ | 25    | K/W  |

## 13. Electrical Characteristics: General

All parameters refer to GND and are valid for  $T_{amb} = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ ,  $V_{VS3V\_AVCC} = V_{VS5V} = 2.7\text{V}$  to 3.3V, and  $V_{VS5V} = 4.5\text{V}$  to 5.5V. Typical values are given at  $V_{VS3V\_AVCC} = V_{VS5V} = 3\text{V}$ ,  $T_{amb} = 25^{\circ}\text{C}$ , and  $f_{RF} = 315$  MHz unless otherwise specified. Details about current consumption, timing, and digital pin properties can be found in the specific sections of the "Electrical Characteristics".

| No. | Parameters                     | Test Conditions                                                                      | Pin <sup>(1)</sup> | Symbol                   | Min. | Тур. | Max.   | Unit     | Type*  |

|-----|--------------------------------|--------------------------------------------------------------------------------------|--------------------|--------------------------|------|------|--------|----------|--------|

| 1   | OFF Mode                       |                                                                                      |                    |                          |      |      |        |          |        |

| 1.1 | Supply current in OFF mode     | $V_{VS3V\_AVCC} = V_{VS5V} \le 3V$<br>$V_{VS5V} = 5V$<br>CLK_OUT disabled            | 10, 11<br>10       | I <sub>SOFF</sub>        |      |      | 2<br>2 | μA<br>μA | A<br>A |

| 2   | Standby Mode                   |                                                                                      |                    |                          |      |      |        |          |        |

| 2.1 | RF operating frequency         | ATA5746                                                                              | 14                 | f <sub>RF</sub>          | 313  |      | 317    | MHz      | Α      |

| 2.1 | range                          | ATA5745                                                                              | 14                 | f <sub>RF</sub>          | 433  |      | 435    | MHz      | Α      |

| 2.2 | Supply current<br>Standby mode | XTO running<br>V <sub>VS3V_AVCC</sub> = V <sub>VS5V</sub> ≤3V<br>CLK_OUT disabled    | 10,11              | Standby                  |      | 50   | 100    | μΑ       | А      |

| 2.2 |                                | XTO running<br>V <sub>VS5V</sub> = 5V<br>CLK_OUT disabled                            | 10,11              | I <sub>Standby</sub>     |      | 50   | 100    | μA       | А      |

| 2.3 | System start-up time           | XTO startup<br>XTAL: $C_m = 5 \text{ fF},$<br>$C_0 = 1.8 \text{ pF}, R_m = 15\Omega$ |                    | T <sub>XTO_Startup</sub> |      | 0.3  | 0.8    | ms       | А      |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Pin numbers in parenthesis were measured with RF\_IN matched to  $50\Omega$  according to Figure 2-1 on page 6 with component values as in Table 2-2 on page 6 (RF<sub>IN</sub>).

All parameters refer to GND and are valid for  $T_{amb} = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ ,  $V_{VS3V\_AVCC} = V_{VS5V} = 2.7\text{V}$  to 3.3V, and  $V_{VS5V} = 4.5\text{V}$  to 5.5V. Typical values are given at  $V_{VS3V\_AVCC} = V_{VS5V} = 3\text{V}$ ,  $T_{amb} = 25^{\circ}\text{C}$ , and  $f_{RF} = 315$  MHz unless otherwise specified. Details about current consumption, timing, and digital pin properties can be found in the specific sections of the "Electrical Characteristics".

| No. | Parameters                                         | Test Conditions                                                                                                                                               | Pin <sup>(1)</sup> | Symbol                                                   | Min. | Тур.     | Max.       | Unit     | Type* |

|-----|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------|------|----------|------------|----------|-------|

| 2.4 | Active mode start-up time                          | From Standby mode to<br>Active mode<br>BR_Range_3<br>ATA5745<br>ATA5746                                                                                       |                    | T <sub>Startup_PLL</sub> + T <sub>Startup_Sig_Proc</sub> |      |          | 565<br>593 | μs<br>μs | А     |

| 3   | Active Mode                                        |                                                                                                                                                               |                    |                                                          |      | <u> </u> |            |          |       |

|     |                                                    | V <sub>VS3V_AVCC</sub> = V <sub>VS5V</sub> = 3V<br>ASK mode<br>CLK_OUT disabled<br>SENSE_CTRL = 0                                                             | 10,11              | I <sub>Active</sub>                                      |      | 6.5      |            | mA       | А     |

| 3.1 | Supply current Active                              | $V_{VS3V\_AVCC} = V_{VS5V} = 3V$<br>FSK mode<br>CLK_OUT disabled<br>SENSE_CTRL = 0                                                                            | 10,11              | I <sub>Active</sub>                                      |      | 6.7      |            | mA       | А     |

| 0.1 | mode                                               | V <sub>VS5V</sub> = 5V<br>ASK mode<br>CLK_OUT disabled<br>SENSE_CTRL = 0                                                                                      | 10                 | I <sub>Active</sub>                                      |      | 6.7      |            | mA       | Α     |

|     |                                                    | V <sub>VS5V</sub> = 5V<br>FSK mode<br>CLK_OUT disabled<br>SENSE_CTRL = 0                                                                                      | 10                 | I <sub>Active</sub>                                      |      | 6.9      |            | mA       | А     |

| 3.2 | Supply current Polling mode                        | V <sub>VS3V_AVCC</sub> = V <sub>VS5V</sub> = 3V<br>T <sub>Polling_Period</sub> = 8 ms<br>BR_Range_3, ASK mode,<br>CLK_OUT disabled<br>Data rate = 9.6 Kbits/s | 10,11              | I <sub>Polling</sub>                                     |      | 545      |            | μΑ       | С     |

|     |                                                    | FSK deviation<br>$f_{DEV} = \pm 38 \text{ kHz}$<br>BER = $10^{-3}$<br>$T_{amb} = 25^{\circ}\text{C}$                                                          |                    |                                                          |      |          |            |          |       |

|     | Input sensitivity FSK                              | Bit rate 9.6 Kbits/s BR2                                                                                                                                      | (14)               | P <sub>REF_FSK</sub>                                     | -103 | -105     | -106.5     | dBm      | В     |

| 3.3 | f <sub>RF</sub> = 315 MHz                          | Bit rate 2.4 Kbits/s BR0                                                                                                                                      | (14)               | P <sub>REF_FSK</sub>                                     | -106 | -108     | -109.5     | dBm      | В     |

|     |                                                    | FSK deviation ±18 kHz to ±50 kHz                                                                                                                              |                    |                                                          |      |          |            |          |       |

|     |                                                    | Bit rate 9.6 Kbits/s BR2                                                                                                                                      | (14)               | P <sub>REF_FSK</sub>                                     | -101 |          |            | dBm      | В     |

|     |                                                    | Bit rate 2.4 Kbits/s BR0                                                                                                                                      | (14)               | P <sub>REF_FSK</sub>                                     | -104 |          |            | dBm      | В     |

|     | Input consitiuity ACK                              | ASK 100% level of carrier,<br>BER = 10 <sup>-3</sup>                                                                                                          |                    |                                                          |      |          |            |          |       |

| 3.4 | Input sensitivity ASK<br>f <sub>BF</sub> = 315 MHz | $T_{amb} = 25^{\circ}C$                                                                                                                                       |                    |                                                          |      |          |            |          |       |

|     | nr                                                 | Bit rate 9.6 Kbits/s BR2                                                                                                                                      | (14)               | P <sub>REF_ASK</sub>                                     | -109 | -111     | -112.5     | dBm      | В     |

|     |                                                    | Bit rate 2.4 Kbits/s BR0                                                                                                                                      | (14)               | P <sub>REF_ASK</sub>                                     | -112 | -114     | -115.5     | dBm      | В     |

$<sup>^{\</sup>star}$ ) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Pin numbers in parenthesis were measured with RF\_IN matched to  $50\Omega$  according to Figure 2-1 on page 6 with component values as in Table 2-2 on page 6 (RF<sub>IN</sub>).

All parameters refer to GND and are valid for  $T_{amb} = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ ,  $V_{VS3V\_AVCC} = V_{VS5V} = 2.7\text{V}$  to 3.3V, and  $V_{VS5V} = 4.5\text{V}$  to 5.5V. Typical values are given at  $V_{VS3V\_AVCC} = V_{VS5V} = 3\text{V}$ ,  $T_{amb} = 25^{\circ}\text{C}$ , and  $f_{RF} = 315$  MHz unless otherwise specified. Details about current consumption, timing, and digital pin properties can be found in the specific sections of the "Electrical Characteristics".

| No.  | Parameters                                                                          | Test Conditions                                                                                                                                                                                                                                                                                                                                                                              | Pin <sup>(1)</sup> | Symbol               | Min. | Тур. | Max. | Unit                   | Type* |

|------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|------|------|------|------------------------|-------|

| 3.5  | Sensitivity change at $f_{RF} = 433.92$ MHz compared to $f_{RF} = 315$ MHz          | $\begin{split} f_{RF} &= 315 \text{ MHz to} \\ f_{RF} &= 433.92 \text{ MHz} \\ P &= P_{REF\_ASK} + \Delta P_{REF1} \\ P &= P_{REF\_FSK} + \Delta P_{REF1} \end{split}$                                                                                                                                                                                                                       | (14)               | $\Delta P_{REF1}$    |      | +1   |      | dB                     | В     |

| 3.6  | Sensitivity change versus<br>temperature, supply<br>voltage and frequency<br>offset | $\begin{aligned} & \text{FSK f}_{\text{DEV}} = \pm 38 \text{ kHz} \\ & \Delta f_{\text{OFFSET}} \leq \pm 160 \text{ kHz} \\ & \text{ASK 100\%} \\ & \Delta f_{\text{OFFSET}} \leq \pm 160 \text{ kHz} \\ & P = P_{\text{REF}\_ASK} + \Delta P_{\text{REF1}} + \\ & \Delta P_{\text{REF2}} \\ & P = P_{\text{REF}\_FSK} + \Delta P_{\text{REF1}} + \\ & \Delta P_{\text{REF2}} \end{aligned}$ | (14)               | $\Delta P_{REF2}$    | +4.5 |      | -1.5 |                        | В     |

|      |                                                                                     | R <sub>Sense</sub> connected from<br>pin SENSE to<br>pin VS3V_AVCC                                                                                                                                                                                                                                                                                                                           |                    | P <sub>Ref_Red</sub> |      |      |      | dBm<br>(peak<br>level) |       |

|      |                                                                                     | $R_{Sense} = 62 \text{ k}\Omega$<br>$f_{in} = 433.92 \text{ MHz}$                                                                                                                                                                                                                                                                                                                            |                    |                      |      | -76  |      | dBm                    | С     |

| 3.7  | Reduced sensitivity                                                                 | $R_{Sense} = 82 \text{ k}\Omega$<br>$f_{in} = 433.92 \text{ MHz}$                                                                                                                                                                                                                                                                                                                            |                    |                      |      | -88  |      | dBm                    | С     |

| 0.7  |                                                                                     | $R_{Sense} = 62 \text{ k}\Omega$<br>$f_{in} = 315 \text{ MHz}$                                                                                                                                                                                                                                                                                                                               |                    |                      |      | -76  |      | dBm                    | С     |

|      |                                                                                     | $R_{Sense} = 82 \text{ k}\Omega$<br>$f_{in} = 315 \text{ MHz}$                                                                                                                                                                                                                                                                                                                               |                    |                      |      | -88  |      | dBm                    | С     |

|      | Reduced sensitivity variation over full operating range                             | $\begin{aligned} &R_{Sense} = 62 \; k\Omega \\ &R_{Sense} = 82 \; k\Omega \\ &P_{Red} = P_{Ref\_Red} + P_{\DeltaRed} \end{aligned}$                                                                                                                                                                                                                                                          |                    | $\Delta P_Red$       | -10  |      | +10  | dB                     |       |

| 3.8  | Maximum frequency offset in FSK mode                                                | Maximum frequency difference of $f_{RF}$ between receiver and transmitter in FSK mode ( $f_{RF}$ is the center frequency of the FSK signal with $f_{BIT} = 10$ Kbits/s $f_{DEV} = \pm 38$ kHz                                                                                                                                                                                                | (14)               | $\Delta f_{OFFSET}$  | -160 |      | +160 | kHz                    | В     |

| 3.9  | Supported FSK frequency deviation                                                   | With up to 2 dB loss of sensitivity. Note that the tolerable frequency offset is 12 kHz lower for $f_{DEV} = \pm 50$ kHz than for $f_{DEV} = \pm 38$ kHz, hence, $\Delta f_{OFFSET} \leq \pm 148$ kHz                                                                                                                                                                                        | (14)               | f <sub>DEV</sub>     | ±18  | ±38  | ±50  | kHz                    | В     |

| 3.10 | System noise figure                                                                 | f <sub>RF</sub> = 315 MHz                                                                                                                                                                                                                                                                                                                                                                    | (14)               | NF                   |      | 6.0  | 9    | dB                     | В     |

|      | - ,ga. c                                                                            | f <sub>RF</sub> = 433.92 MHz                                                                                                                                                                                                                                                                                                                                                                 | (14)               | NF                   |      | 7.0  | 10   | dB                     | В     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Pin numbers in parenthesis were measured with RF\_IN matched to 50Ω according to Figure 2-1 on page 6 with component values as in Table 2-2 on page 6 (RF<sub>IN</sub>).

All parameters refer to GND and are valid for  $T_{amb} = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ ,  $V_{VS3V\_AVCC} = V_{VS5V} = 2.7\text{V}$  to 3.3V, and  $V_{VS5V} = 4.5\text{V}$  to 5.5V. Typical values are given at  $V_{VS3V\_AVCC} = V_{VS5V} = 3\text{V}$ ,  $T_{amb} = 25^{\circ}\text{C}$ , and  $f_{RF} = 315$  MHz unless otherwise specified. Details about current consumption, timing, and digital pin properties can be found in the specific sections of the "Electrical Characteristics".

| No.  | Parameters                                            | Test Conditions                                                                                                                                         | Pin <sup>(1)</sup> | Symbol                | Min. | Тур.              | Max.            | Unit | Type* |

|------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|------|-------------------|-----------------|------|-------|

| 0.11 | Intermediate frequency                                | f <sub>RF</sub> = 433.92 MHz                                                                                                                            |                    | f <sub>IF</sub>       |      | 440               |                 | kHz  | Α     |

| 3.11 | Intermediate frequency                                | f <sub>RF</sub> = 315 MHz                                                                                                                               |                    | f <sub>IF</sub>       |      | 440               |                 | kHz  | Α     |

| 3.12 | System bandwidth                                      | 3 dB bandwidth  This value is for information only!  Note that for crystal and system frequency offset calculations, Δf <sub>OFFSET</sub> must be used. | (14)               | SBW                   |      | 435               |                 | kHz  | А     |

| 3.13 | System out-band<br>3rd-order input intercept<br>point | $\Delta f_{meas1} = 1.8 \text{ MHz}$<br>$\Delta f_{meas2} = 3.6 \text{ MHz}$<br>$f_{RF} = 315 \text{ MHz}$                                              | (14)               | IIP3                  |      | -24               |                 | dBm  | С     |

|      | point                                                 | f <sub>RF</sub> = 433.92 MHz                                                                                                                            | (14)               | IIP3                  |      | -23               |                 | dBm  | С     |

| 3.14 | System outband input 1-dB compression point           | $\Delta f_{meas1} = 1 \text{ MHz}$<br>$f_{RF} = 315 \text{ MHz}$                                                                                        | (14)               | I1dBCP                |      | -31               | -36             | dBm  | С     |

|      | 1-db compression point                                | f <sub>RF</sub> = 433.92 MHz                                                                                                                            | (14)               | I1dBCP                |      | -30               | -35             | dBm  | С     |

| 2 15 | LNA input impedance                                   | f <sub>RF</sub> = 315 MHz                                                                                                                               | 14                 | Z <sub>in_LNA</sub>   |      | (72.4 – j298)     |                 | Ω    | С     |

| 3.13 | LIVA input impedance                                  | f <sub>RF</sub> = 433.92 MHz                                                                                                                            | 14                 | Z <sub>in_LNA</sub>   |      | (55 – j216)       |                 | Ω    | С     |

| 3.16 | Maximum peak RF input                                 | BER < 10 <sup>-3</sup> , ASK: 100%                                                                                                                      | (14)               | P <sub>IN_max</sub>   |      | +5                | -10             | dBm  | С     |

| 3.10 | level, ASK and FSK                                    | FSK: f <sub>DEV</sub> = ±38 kHz                                                                                                                         | (14)               | P <sub>IN_max</sub>   |      | +5                | -10             | dBm  | С     |

|      |                                                       | f < 1 GHz                                                                                                                                               | (14)               |                       |      |                   | <b>–</b> 57     | dBm  | С     |

|      |                                                       | f >1 GHz                                                                                                                                                | (14)               |                       |      |                   | <del>-4</del> 7 | dBm  | С     |

| 3.17 | LO spurs at LNA_IN                                    | $\begin{aligned} &f_{LO} = 315.44 \text{ MHz} \\ &2 \times f_{LO} \\ &4 \times f_{LO} \end{aligned}$                                                    | (14)               |                       |      | -90<br>-94<br>-68 |                 | dBm  | С     |

|      |                                                       | $f_{LO} = 434.36 \text{ MHz}$ $2 \times f_{LO}$ $4 \times f_{LO}$                                                                                       | (14)               |                       |      | -92<br>-88<br>-58 |                 | dBm  | С     |

| 3.18 | Image rejection                                       | With the complete image band $f_{\rm RF} = 315~{\rm MHz}$                                                                                               | (14)               |                       | 24   | 30                |                 | dB   | Α     |

|      |                                                       | f <sub>RF</sub> = 433.92 MHz                                                                                                                            | (14)               |                       | 24   | 30                |                 | dB   | Α     |