www.DataSheet4U.com

## 4096 X 1 BIT DYNAMIC RAM

# MK4096 (P/N)-6/16/11

#### **FEATURES**

- Industry standard 16-pin DIP configuration (available in plastic (N) and ceramic (P) packages)

- All inputs are low capacitance and TTL compatible

- Input latches for address, chip select and data in

- □ Inputs protected against static charge

- Three-state TTL compatible output, latched and valid into next cycle

□ Proven reliability with high performance

| Part Number | Access Time | Cycle Time | Max Power* |

|-------------|-------------|------------|------------|

| MK 40966    | 250 ns      | 375 ns     | 450mW      |

| MK 4096-16  | 300 ns      | 425 ns     | 385mW      |

| MK 4096-11  | 350 ns      | 500 ns     | 320mW      |

<sup>\*</sup>Standby power for all parts < 19mW

#### **DESCRIPTION**

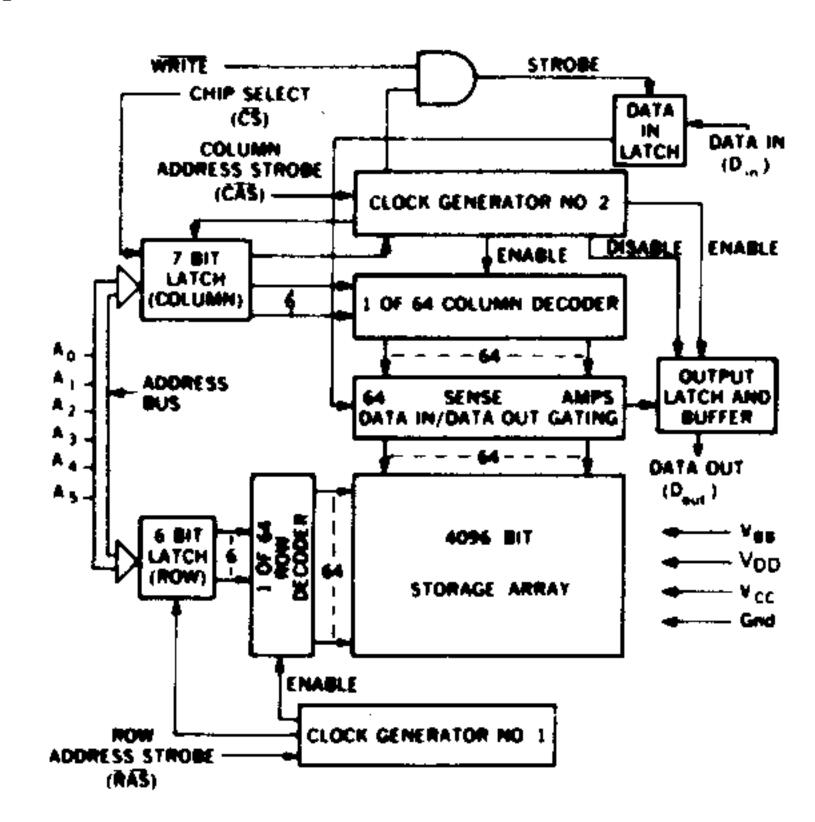

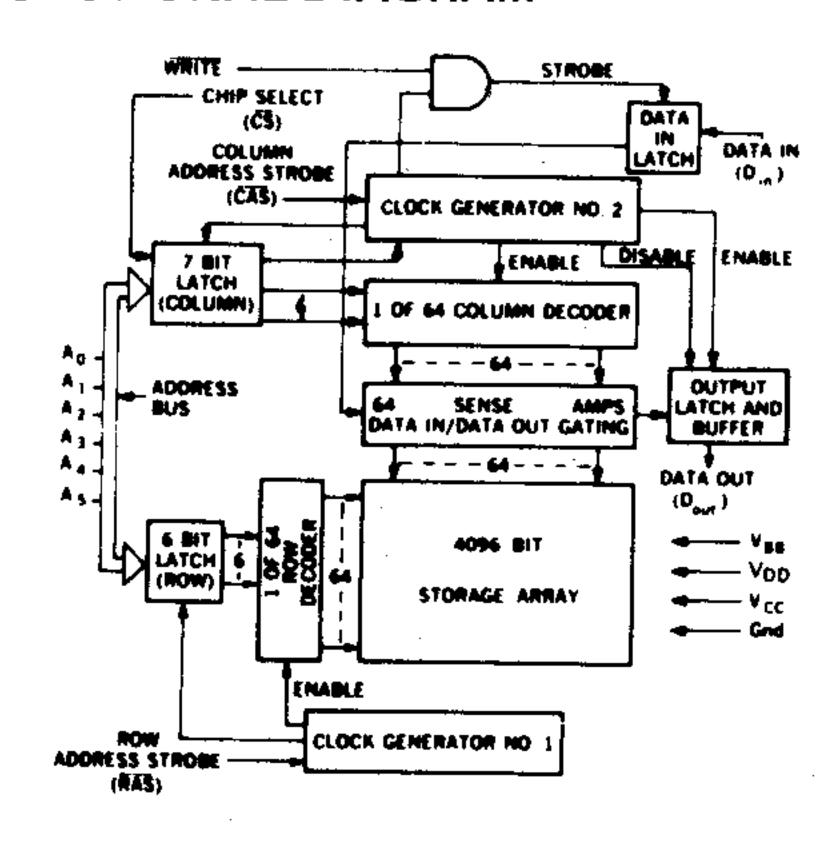

The MK 4096 is the recognized industry standard 4096 word by 1 bit MOS Random Access Memory circuit packaged in a standard 16-pin DIP on 0.3 inch centers. This package configuration is made possible by a unique multiplexing and latching technique for the address inputs. The use of the 16-pin DIP for the MK 4096 provides high system bit densities and is compatible with widely available automated testing and insertion equipment.

The MK 4096 is fabricated with MOSTEK's standard Self-Aligned, Poly-Interconnect, N-Channel (SPIN) process. The SPIN process allows the MK 4096 to be a highly manufacturable, state-of-the-art memory circuit that exhibits the reliability and performance

standards necessary for today's (and tomorrow's) data processing applications. The MK 4096 employs a single transistor storage cell, utilizing a dynamic storage technique and dynamic control circuitry to achieve optimum performance with low power dissipation.

System oriented features incorporated within the MK 4096 include direct interfacing capability with TTL, 6 instead of 12 address lines to drive, on-chip registers which can eliminate the need for interface registers, input logic levels selected to optimize the noise immunity, and two chip select methods to allow the user to determine the speed/power characteristics of his memory system.

#### **FUNCTIONAL DIAGRAM**

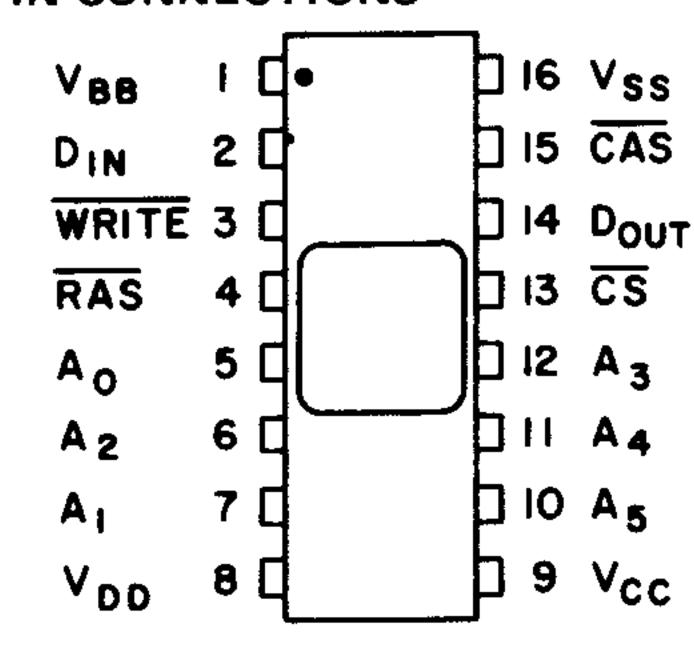

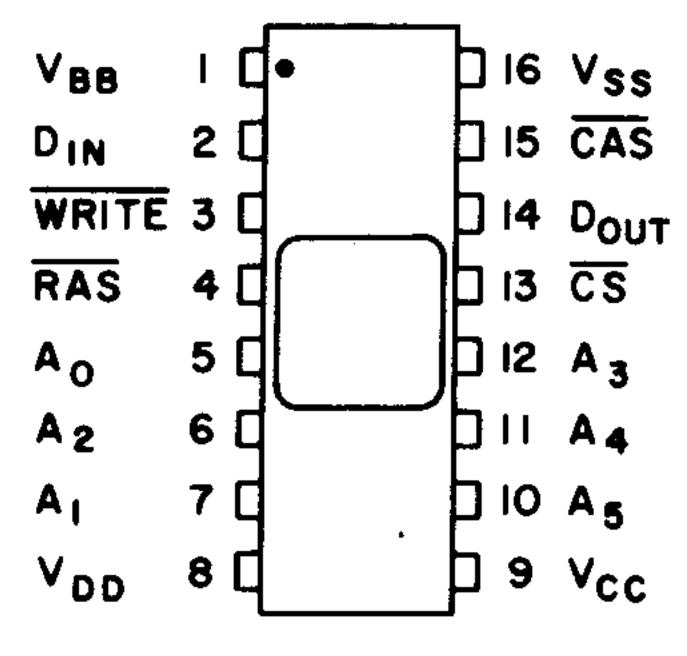

#### **PIN CONNECTIONS**

PIN NAMES

An - A5 A CAS CC CS C RAS R

WRITE

ADDRESS INPUTS

COLUMN ADDRESS STROBE

CHIP SELECT

ROW ADDRESS STROBE

READ/WRITE INPUT

DIN DOUT VBB VCC VDD VSS DATA IN DATA OUT POWER (-5V) POWER (+5V) POWER (+12V) GROUND

#### **ABSOLUTE MAXIMUM RATINGS\***

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# RECOMMENDED DC OPERATING CONDITIONS (17) ( $0^{\circ}$ C $\leq$ TA $\leq$ +70 $^{\circ}$ C)

|                 |                                                    | MK 40           | 966      | MK 40           | 96-16    | MK 40           | 96-11           |       |       |

|-----------------|----------------------------------------------------|-----------------|----------|-----------------|----------|-----------------|-----------------|-------|-------|

|                 | PARAMETER                                          | MIN             | MAX      | MIN             | MAX      | MIN             | MAX             | UNITS | NOTES |

| $V_{DD}$        | Supply Voltage                                     | 11.4            | 12.6     | 11.4            | 12.6     | 11.4            | 12.6            | Volts | 1     |

| V <sub>CC</sub> | Supply Voltage                                     | V <sub>SS</sub> | $V_{DD}$ | V <sub>SS</sub> | $V_{DD}$ | V <sub>SS</sub> | V <sub>DD</sub> | Volts | 1,2   |

| V <sub>SS</sub> | Supply Voltage                                     | 0               | 0        | 0               | 0        | 0               | 0               | Volts | 1     |

| V <sub>BB</sub> | Supply Voltage                                     | -4.5            | -5.5     | -4.5            | -5.5     | -4.5            | -5.5            | Volts | 1     |

| Чнс             | Logic 1 Voltage – RAS,<br>CAS, WRITE               | 2.7             | 7.0      | 2.7             | 7.0      | 3.0             | 7.0             | Volts | 1,3   |

| V <sub>H</sub>  | Logic 1 Voltage, all inputs except RAS, CAS, WRITE | 2.4             | 7.0      | 2.4             | 7.0      | 2.4             | 7.0             | Volts | 1,3   |

| VIL             | Logic 0 Voltage, all inputs                        | -1.0            | 0.8      | -1.0            | 0.8      | -1.0            | 0.8             | Volts | 1,3   |

DC ELECTRICAL CHARACTERISTICS (17)  $(0^{\circ}C \le T_A \le 70^{\circ}C)(V_{DD} = 12.0V \pm 5\%; V_{CC} = 5.0V \pm 10\%; V_{SS} = 0V; V_{BB} = -5.0V \pm 10\%)$

| · · · · · · · · · · · · · · · · · · · |                                                     |         | MK4096-6 |     | MK4096-16 |     | 096-11 |       |       |

|---------------------------------------|-----------------------------------------------------|---------|----------|-----|-----------|-----|--------|-------|-------|

|                                       | PARAMETER                                           | MIN     | MAX      | MIN | MAX       | MIN | MAX    | UNITS | NOTES |

| I <sub>DD1</sub>                      | Average V <sub>DD</sub> Power Supply Current        |         | 35       |     | 30        |     | 25     | mA    | 4     |

| 1 <sub>CC</sub>                       | V <sub>CC</sub> Power Supply Current                |         |          |     |           |     |        | mA    | 5     |

| IBB                                   | Average V <sub>BB</sub> Power Supply Current        |         | 75       |     | 75        |     | 75     | μΑ    |       |

| IDD2                                  | Standby V <sub>DD</sub> Power Supply Current        | <u></u> | 1.5      |     | 1.5       |     | 1.5    | mA    | 7     |

| IDD3                                  | Average VDD Supply Current during "RAS-only" cycles |         | 25       |     | 22        |     | 18     | mA    | 4     |

| l(L)                                  | Input Leakage Current (any input)                   |         | 5        |     | 5         |     | 5      | μΑ    | 6     |

| 0(L)                                  | Output Leakage Current                              |         | 10       |     | 10        |     | 10     | μΑ    | 7,8   |

| V <sub>OH</sub>                       | Output Logic 1 Voltage @ I <sub>OUT</sub> = -5mA    | 2.4     |          | 2.4 |           | 2.4 |        | Volts | 2     |

| V <sub>OL</sub>                       | Output Logic 0 Voltage @ IOUT= 2mA                  |         | 0.4      |     | 0.4       |     | 0.4    | Volts |       |

#### **NOTES**

- All voltages referenced to VSS. VBB must be applied to and removed from the device within 5 seconds of VDD.

- Output voltage will swing from V<sub>SS</sub> to V<sub>CC</sub> if V<sub>CC</sub> ≤ V<sub>DD</sub> -4 volts. If V<sub>CC</sub> ≥ V<sub>DD</sub> -4 volts, the output will swing from V<sub>SS</sub> to a voltage somewhat less than V<sub>DD</sub>.

- Device speed is not guaranteed at input voltages greater than TTL. levels (0 to 5V).

- 4. Current is proportional to cycle rate; maximum current is measured at the fastest cycle rate.

- 5. ICC depends upon output loading. The VCC supply is connected to the output buffer only.

- 6. All device pins at 0 volts except VBB which is at -5 volts and the pin under test which is at +10 volts.

- 7. Output is disabled (open-circuit) and RAS and CAS are both at a logic 1.

- 8.  $0V \leq V_{OUT} \leq +10V$ .

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (10, 15,17) (0°C $\leq$ TA $\leq$ 70°C) (VDD = 12.0V ± 5%, VCC = 5.0V ± 10%, VSS = 0V, VBB = -5.0V ± 10%)

|                   |                                             | MK 40                                            | 96-6        | MK 40 | 96-16  | MK 409 | 6-11   |          |          |

|-------------------|---------------------------------------------|--------------------------------------------------|-------------|-------|--------|--------|--------|----------|----------|

|                   | PARAMETER  Random Read or Write Cycle Time  |                                                  | MAX         | MIN   | MAX    | MIN    | MAX    | UNITS    | NOTES    |

| t <sub>RC</sub>   | Random Read or Write Cycle Time             | 375                                              |             | 425   |        | 500    |        | nsec     | 11       |

| t <sub>RAC</sub>  | Access time from Row Address Strobe         |                                                  | 250         |       | 300    |        | 350    | <u></u>  | 11,13    |

| t CAC             | Access Time from Column Address<br>Strobe   |                                                  | 140         |       | 165    |        | 200    |          | 12,13    |

| t OFF             | Output Buffer Turn-Off Delay                | 0                                                | 65          | 0     | 80     | 0      | 100    |          |          |

| t RP              | Row Address Strobe Precharge Time           | 115                                              |             | 125   |        | 150    |        |          |          |

| t RAS             | Row Address Strobe Pulse Width              | 250                                              | 10,000      | 300   | 10,000 | 350    | 10,000 |          | <u> </u> |

| t RCL             | Row To Column Strobe Lead Time              | 60                                               | 110         | 80    | 135    | 100    | 150    |          | 14       |

| t cas             | Column Address Strobe Pulse Width           | 140                                              |             | 165   | · · ·  | 200    |        |          | 12       |

| t ÀS              | Address Set-Up Time                         | 0                                                |             | 0     |        | 0      |        |          |          |

| t <sub>AH</sub>   | Address Hold Time                           | 60                                               |             | 80    |        | 100    |        |          |          |

| t CH              | Chip Select Hold Time                       | 100                                              |             | 100   | _      | 100    |        |          |          |

| t <sub>T</sub>    | Rise and Fall Times                         | 3                                                | 50          | 3     | 50     | 3      | 50     |          | 15       |

| t <sub>RCS</sub>  | Read Command Set-Up Time                    | 0                                                |             | 0     |        | 0      |        |          |          |

| t <sub>RCH</sub>  | Read Command Hold Time                      | 0                                                |             | 0     |        | 0      |        | <u>.</u> |          |

| t wch             | Write Command Hold Time                     | 110                                              |             | 130   |        | 150    |        |          |          |

| t <sub>WP</sub>   | Write Command Pulse Width                   | 110                                              |             | 130   |        | 150    |        |          |          |

| t <sub>CRL</sub>  | Column to Row Strobe Lead Time              | -40                                              | +40         | -50   | +50    | -50    | +50    |          |          |

| <sup>t</sup> cwl. | Write Command to Column Strobe<br>Lead Time | 110                                              |             | 130   |        | 150    |        |          |          |

| t <sub>DS</sub>   | Data In Set-Up Time                         | 0                                                |             | 0     |        | 0      |        | •        | 16       |

| t <sub>DH</sub>   | Data In Hold Time                           | 110                                              |             | 130   |        | 150    |        |          | 16       |

| t RFSH            | Refresh Period                              |                                                  | 2           |       | 2      |        | 2      | msec     |          |

| t <sub>MOD</sub>  | Modify Time                                 | <del>                                     </del> | 10          |       | 10     |        | 10     | μsec     |          |

| t DOH             | Data Out Hold Time                          | 10                                               | <del></del> | 10    |        | 10     |        | μsec     |          |

#### **NOTES Continued**

www.DataSheet4U.com

- 9. Capacitance measured with Boonton Meter or effective capacitance calculated from the equation:  $C = \frac{1 \triangle t}{\triangle V}$  with current equal to a constant 20mA.

- 10. A C measurements assume t<sub>T</sub> = 5ns.

- 11. Assumes that tRCL + tT ≤ tRCL (max).

- 12. Assumes that t<sub>RCL</sub> + t<sub>T</sub> ≥t<sub>RCL</sub> (max).

- 13. Measured with a load circuit equivalent to 1 TTL load and C<sub>L</sub> = 100pF.

- 14. Operation within the t<sub>RCL</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met. t<sub>RCL</sub> (max) is specified as a reference point only; if t<sub>RCL</sub> is greater than the specified t<sub>RCL</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub> and t<sub>RAS</sub>, t<sub>RAC</sub> and t<sub>RCL</sub> will be longer by the amount t<sub>RCL</sub> + t<sub>T</sub> exceeds t<sub>RCL</sub> (max).

15. VIHC (min) or VIH (min) and VIL (max) are reference levels for measuring timing of input signals. Also, transition times are measured between VIHC or VIH and VIL.

www.DataSheet4U.com

- 16. These parameters are referenced to CAS leading edge in random write cycles and to WRITE leading edge in delayed write or readmodify-write cycles.

- 17. After the application of supply voltages or after extended periods of operation without clocks, the device must perform a minimum of one initialization cycle (any valid memory cycle containing both RAS and CAS) prior to normal operation.

# AC ELECTRICAL CHARACTERISTICS $(0^{\circ}\text{C} \leq \text{T}_{A} \leq +70^{\circ}\text{C}) \text{ (VDD} = 12.0V ±5\%, VCC =5.0V ±10\%, VSS = 0V, VBB = -5.0V ± 10%)}$

| PA                                         | RAMETER                                  | TYP | MAX | UNITS | NOTES |

|--------------------------------------------|------------------------------------------|-----|-----|-------|-------|

| C 1 Input Capaci                           | tance (A <sub>0</sub> – A <sub>5</sub> ) | 7   | 10  | pF    | 9     |

| C <sub>12</sub> Input Capaci<br>WRITE, CS) | tance (RAS, CAS, DIN,                    | 5   | 7   | pF    | 9     |

| C <sub>0</sub> Output Capa                 | citance (DOUT)                           | 5   | 8   | pF    | 7,9   |

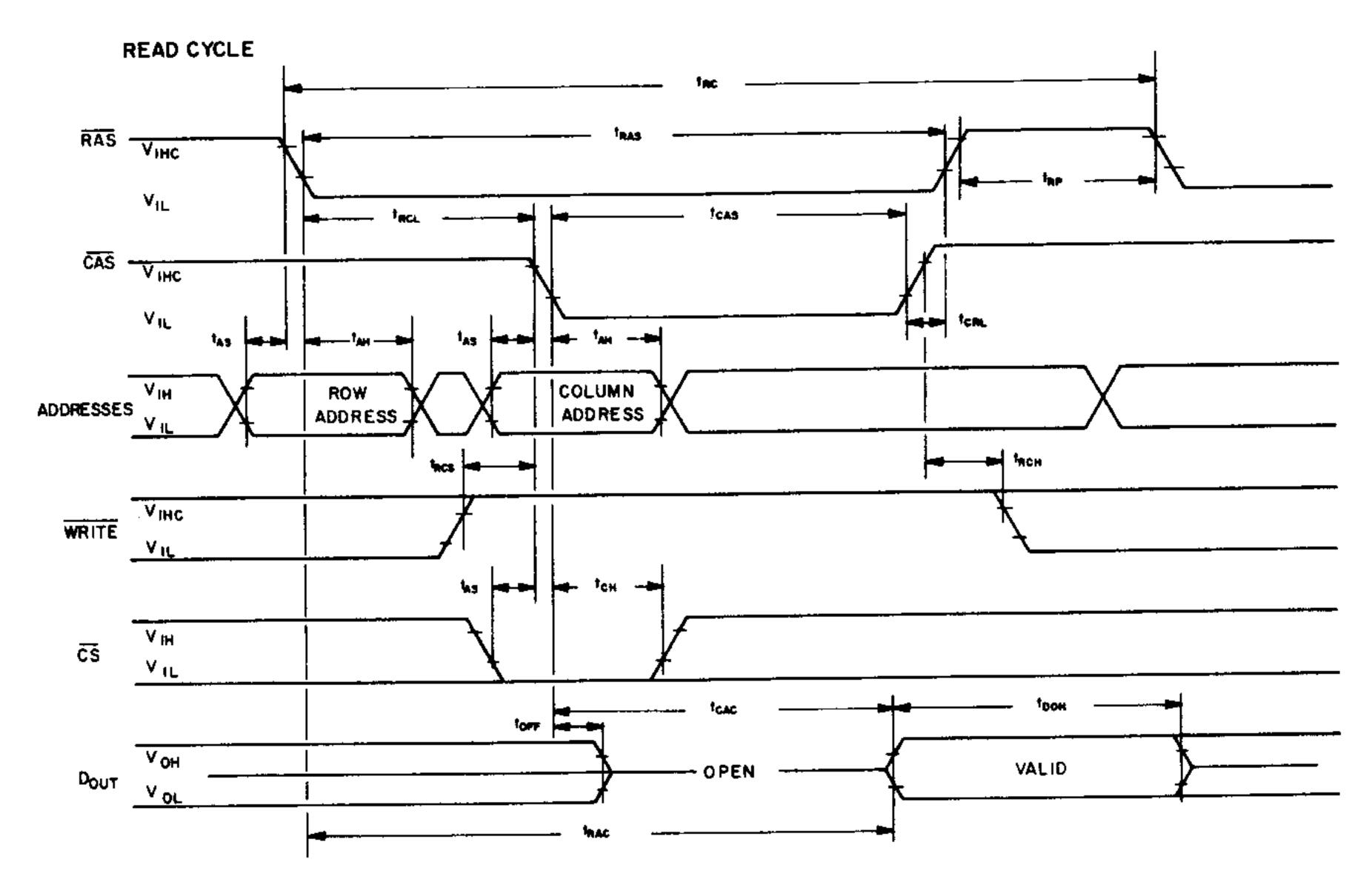

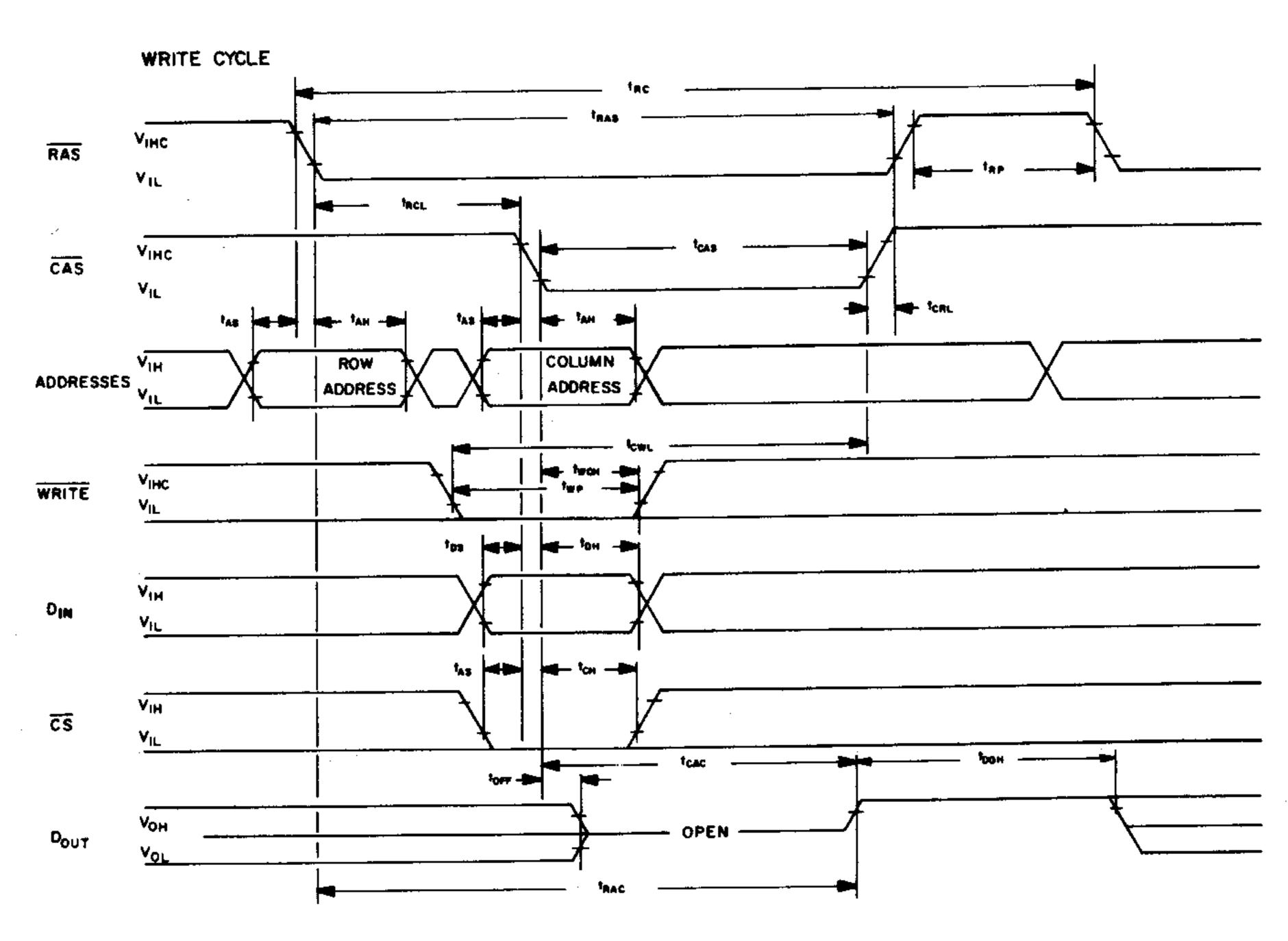

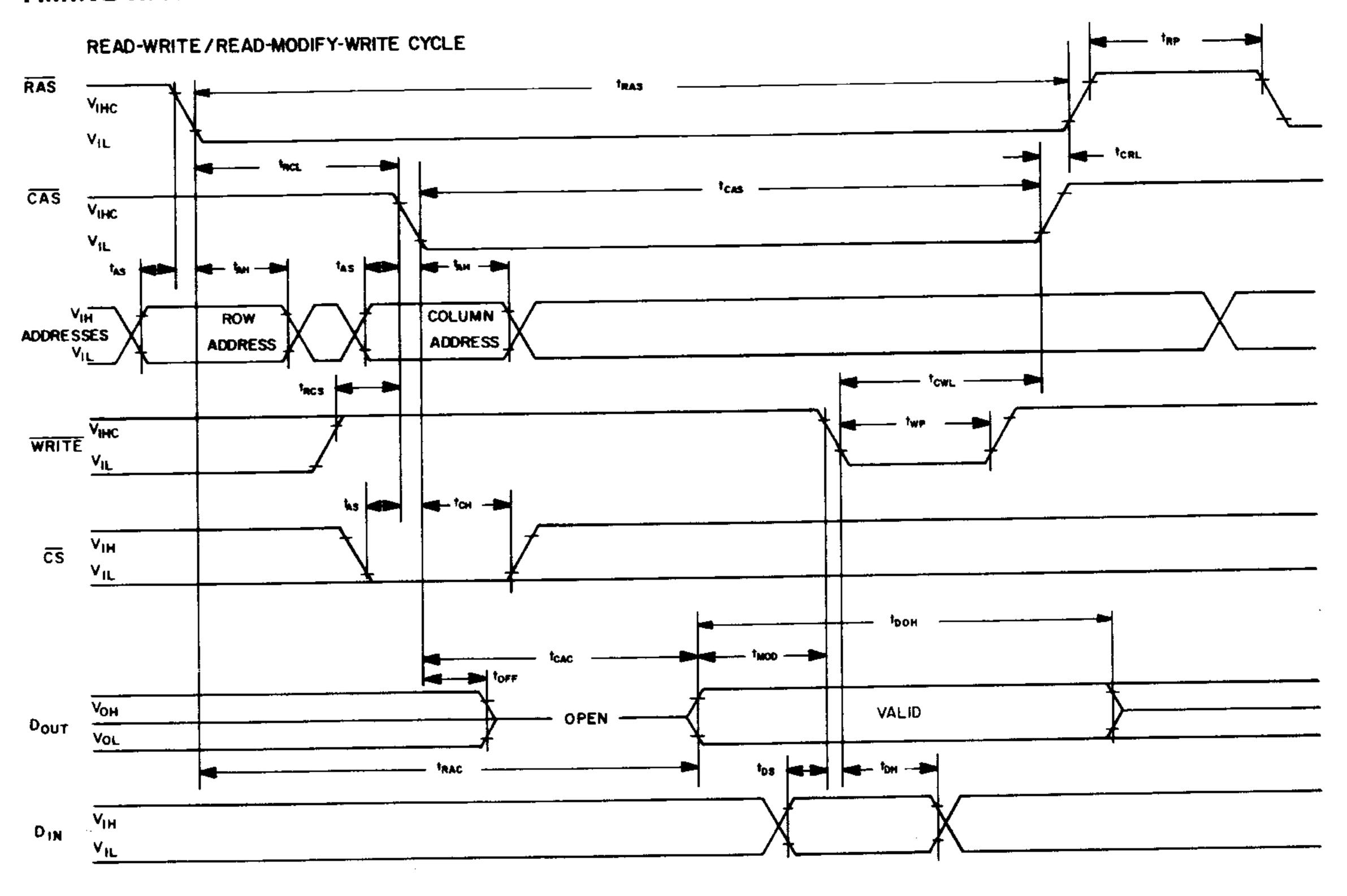

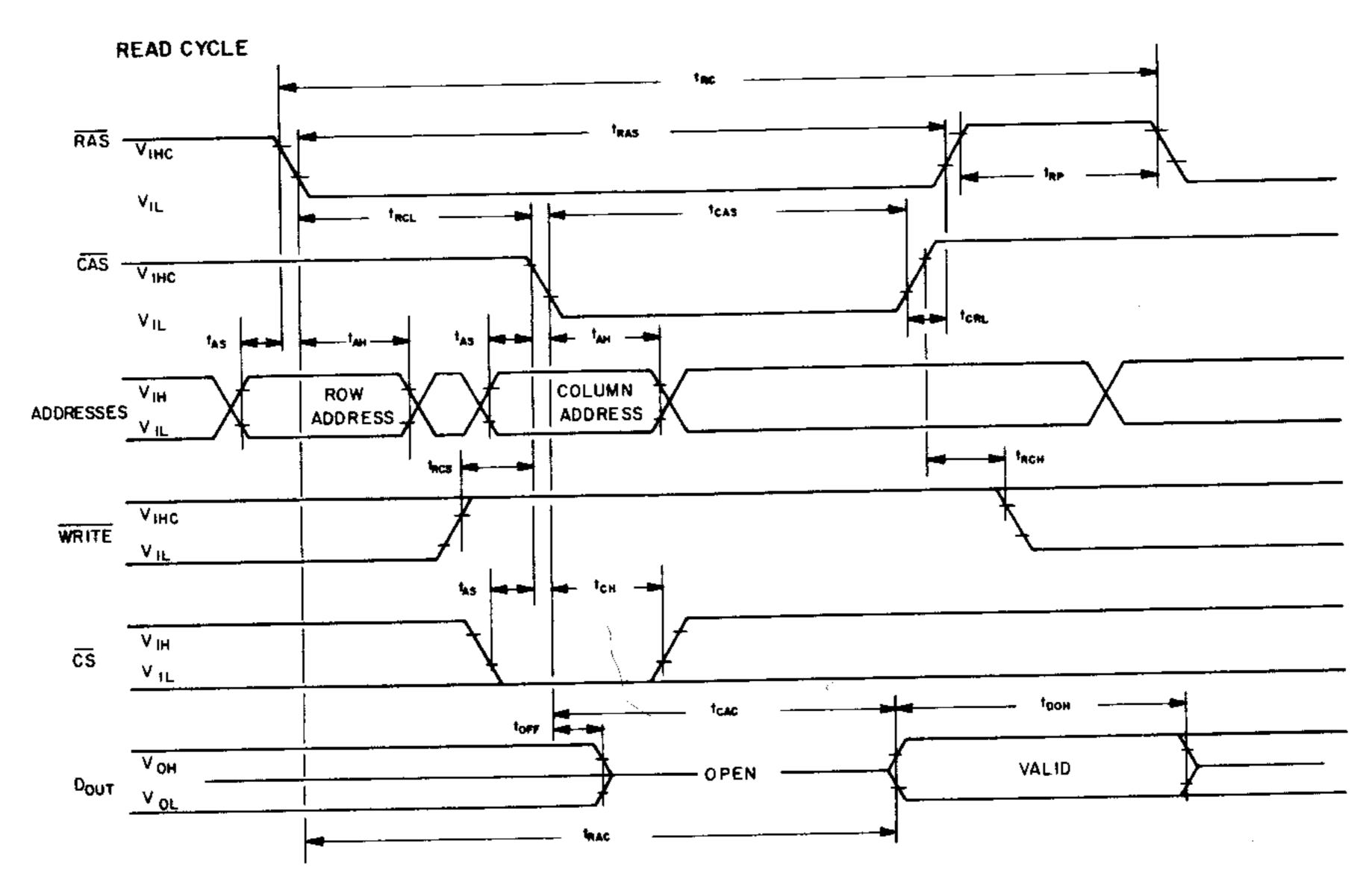

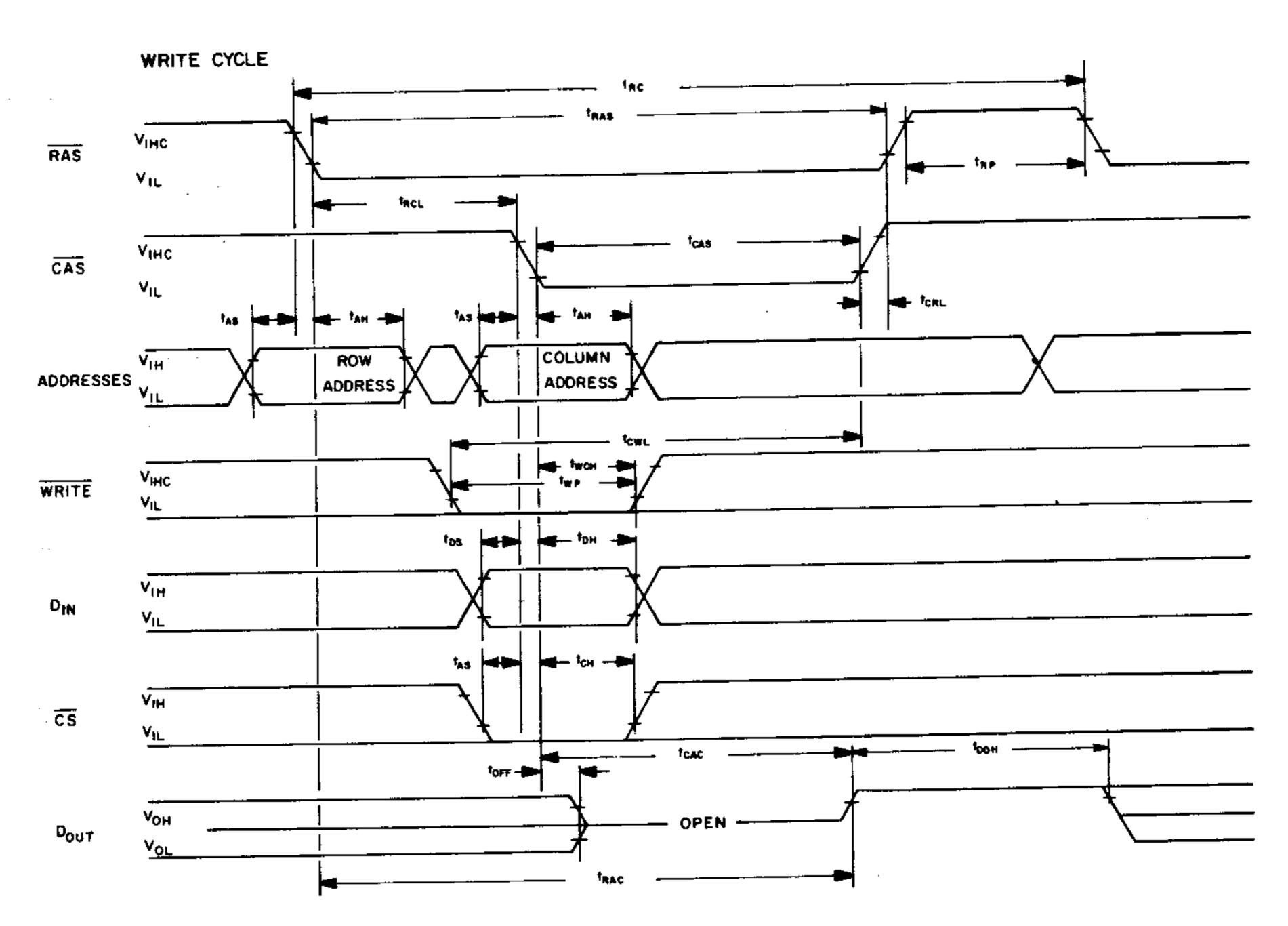

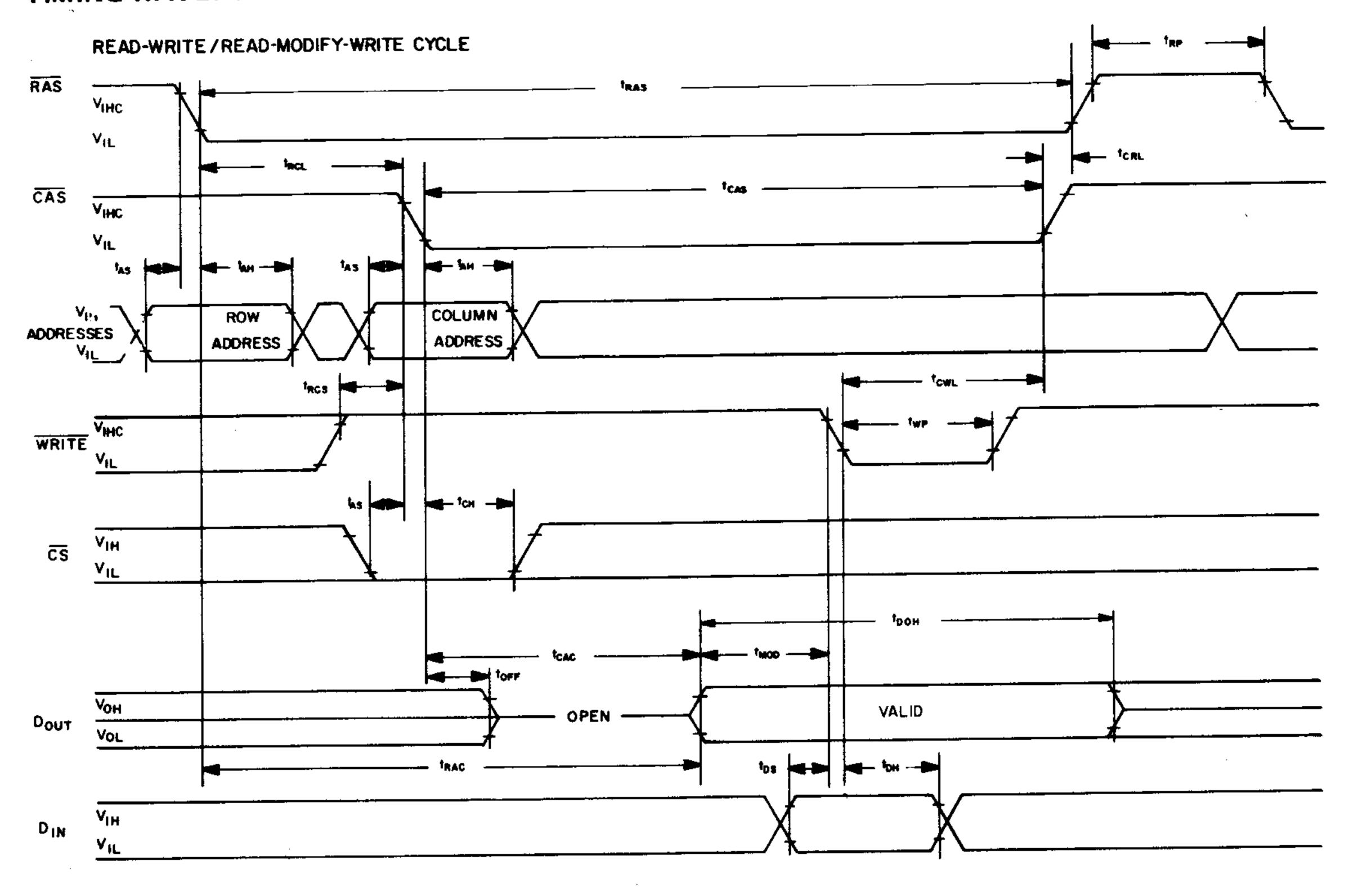

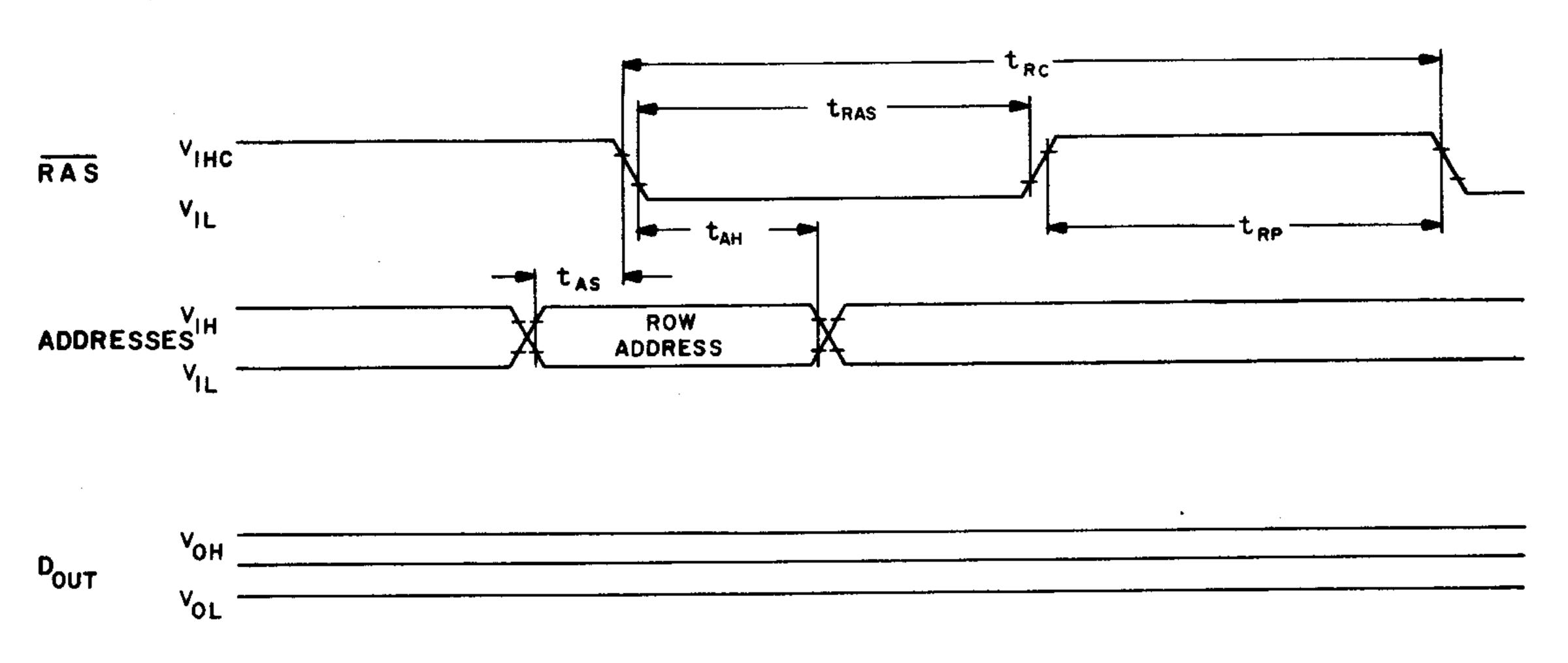

#### **TIMING WAVEFORMS**

www.DataSheet4U.com

### TIMING WAVEFORMS

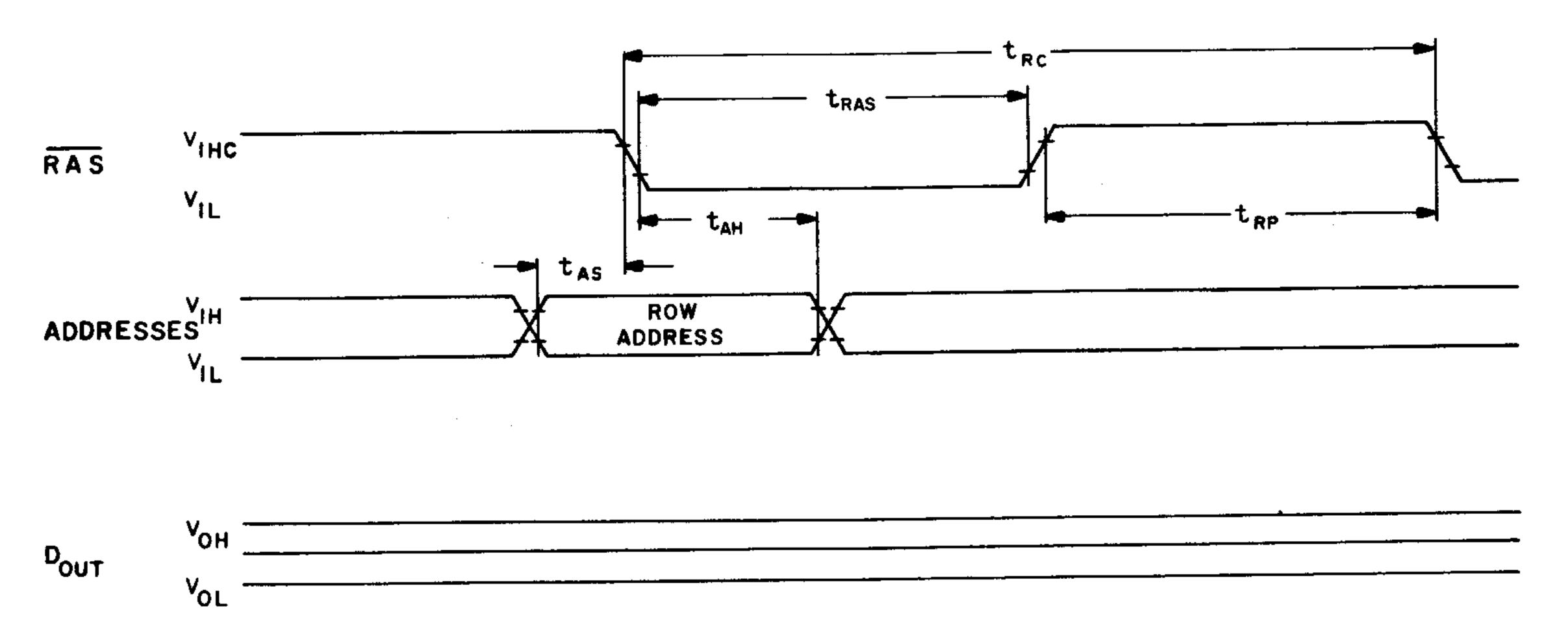

"RAS ONLY" REFRESH CYCLE

NOTE:

Prior to the first memory cycle following a period (beyond 2mS) of "RAS-only refresh, a memory-cycle employing both RAS and CAS must be performed to insure proper device operation.

#### **ADDRESSING**

The 12 address bits required to decode one of the 4096 cell locations within the MK 4096 are multiplexed onto the 6 address inputs and latched into the on-chip address latches by externally applying two negative going TTL level clocks. The first clock, the Row Address Strobe (RAS), latches the 6 row address bits into the chip. The second clock, the Column Address Strobe (CAS), subsequently latches the 6 column address bits plus Chip Select (CS) into the chip. (Note that since the Chip Select signal is not required until CAS time, which is well into the memory cycle, its decoding time does not add to system access or cycle time). Each of these signals, RAS and CAS, triggers a sequence of events which are controlled by different delayed internal clocks. The two clock chains are linked together logically in such a way that the address multiplexing operation is done outside of the critical path timing sequence for read data access. The later events in the CAS clock sequence are inhibited until the occurrence of a delayed signal derived from the RAS clock chain. This "gated CAS" feature allows the CAS clock to be externally activated as soon as the Row Address Hold Time specification (tAH) has been satisfied and the 6 address inputs have been changed from Row address to Column address information.

Note that CAS can be activated at any time after tAH and it will have no effect on the worst case data access time (tRAC) up to the point in time when the delayed row clock no longer inhibits the remaining sequence of column clocks. Two timing end points result from the internal gating of CAS which are called tRCL (min) and tRCL (max). No data storage or reading errors will result if CAS is applied to the MK 4096 at a point in time beyond the tRCL (max) limit. However, access time will then be determined exclusively by the access time from CAS (tCAC) rather than from RAS (tRAC), and access time from RAS will be lengthened by the amount that tRCL exceeds the tRCL (max) limit.

#### DATA INPUT/OUTPUT

Data to be written into a selected cell is latched into an on-chip register by a combination of WRITE and CAS while RAS is active. The later of the signals (WRITE or CAS) to make its negative transition is the strobe for the Data In register. This permits several options in the write cycle timing. In a write cycle, if the WRITE input is brought low prior to CAS, the Data In is strobed by CAS, and the set-up and hold times are referenced to CAS. If the data input is not available at CAS time or if it is desired that the cycle be a read-write or read-modify-write cycle, the WRITE signal must be delayed until after CAS. In this "delayed write cycle" the data input set-up and hold times are referenced to the negative edge of WRITE rather than to CAS.

(To illustrate this feature, Data In is referenced to WRITE in the timing diagram depicting the read-modify-write cycle while the "early write" cycle diagram shows Data In referenced to CAS). Note that if the chip is unselected (CS high at CAS time) WRITE commands are not executed and, consequently, data stored in the memory is unaffected.

www.DataSheet4U.com

Data is retrieved from the memory in a read cycle by maintaining WRITE in the inactive or high state throughout the portion of the memory cyle in which CAS is active. Data read from the selected cell will be available at the output within the specified access time.

#### DATA OUTPUT LATCH

Any change in the condition of the Data Out Latch is initiated by the CAS signal. The output buffer is not affected by memory (refresh) cycles in which only the RAS signal is applied to the MK 4096. Whenever CAS makes a negative transition, the output will go unconditionally open-circuited, independent of the state of any other input to the chip. If the cycle in progress is a read, read-modify-write, or a delayed write cycle and the chip is selected, then the output latch and buffer will again go active and at access time will contain the data read from the selected cell. This output data is the same polarity (not inverted) as the input data. If the cycle in progress is a write cycle (WRITE active low before CAS goes low) and the chip is selected, then at access time the output latch and buffer will contain a logic 1. Once having gone active, the output will remain valid until the MK 4096 receives the next CAS negative edge. Intervening refresh cycles in which a RAS is received (but no CAS) will not cause valid data to be affected. Conversely, the output will assume the open-circuit state during any cycle in which the MK 4096 receives a CAS but no RAS signal (regardless of the state of any other inputs). The output will also assume the open-circuit state in normal cycles (in which both RAS and CAS signals occur) if the chip is unselected.

The three-state data output buffer presents the data output pin with a low impedance to VCC for a logic 1 and a low impedance to VSS for a logic 0. The effective resistance to VCC (logic 1 state) is  $500\Omega$  maximum and  $150\Omega$  typically. The resistance to VSS (logic 0 state) is  $200\Omega$  maximum and  $100\Omega$  typically. The separate VCC pin allows the output buffer to be powered from the supply voltage of the logic to which the chip is interfaced. During battery standby operation, the VCC pin may have power removed without affecting the MK 4096 refresh operation. This allows all system logic except the RAS/CAS timing circuitry and the refresh address logic to be turned off during battery standby to conserve power.

#### REFRESH

Refresh of the dynamic cell matrix is accomplished by performing a memory cycle at each of the 64 row addresses within each 2 millisecond time interval. Any cycle in which a RAS signal occurs accomplishes a refresh operation. A read cycle will refresh the selected row, regardless of the Chip Select (CS) input. A write or read-modify-write cycle also refreshes the selected row, but the chip should be unselected to prevent writing data into the selected cell.

For standby operation, a "RAS-only" cycle can be employed to refresh the MK 4096. However, if "RAS-only" refresh cycles (where RAS is the only signal applied to the chip) are continued for extended periods, the output buffer may eventually lose proper data and go open-circuit. Prior to the first memory cycle following a period (beyond 2ms) of "RAS-only" refresh, a memory cycle employing both RAS and CAS must be performed to precharge the internal circuitry. This "dummy cycle" allows the output buffer to regain activity and enables the device to perform a read or write cycle upon command.

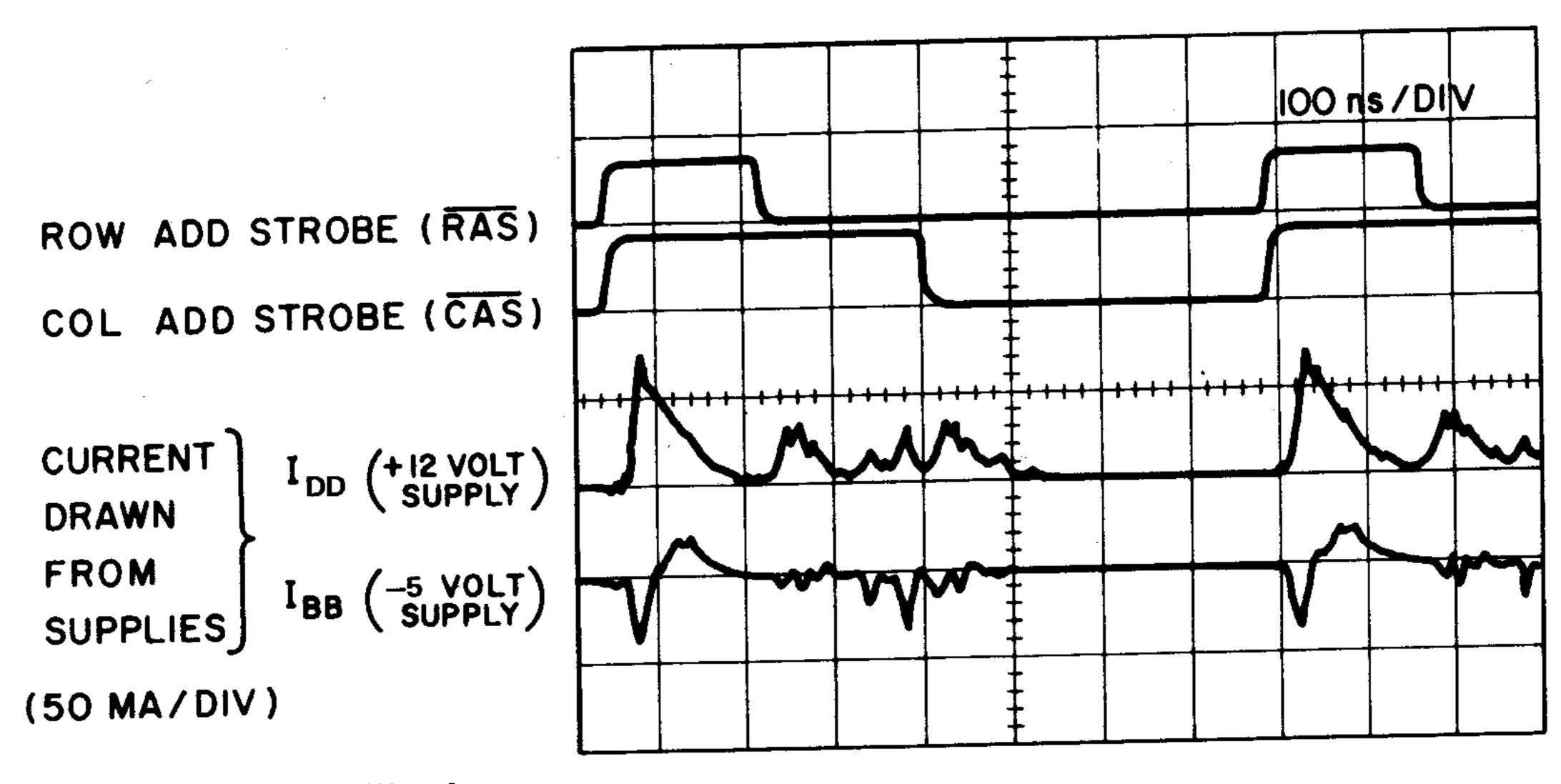

### POWER DISSIPATION/STANDBY MODE

Most of the circuitry used in the MK 4096 is dynamic and most of the power drawn is the result of an address strobe edge. Because the power is not drawn during the whole time the strobe is active, the dynamic power is a function of operating frequency rather than active duty cycle. Typically, the power is 120 mW at a 1 µsec cycle rate for the MK 4096 with a maximum power of less than 450 mW at 375 nsec cycle time. To minimize the overall system power, the Row Address Strobe (RAS) should be decoded and supplied to only the selected chips. The CAS must be supplied to all chips (to turn off the unselected output). Those chips that did not receive a RAS, however, will not dissipate any power on the CAS edges, except for that required to turn off the outputs. If the RAS signal is decoded and supplied only to the selected chips, then the Chip Select (CS) input of all chips can be at a logic 0. The chips that receive a CAS but no RAS will be unselected (output open-circuited) regardless of the Chip Select input. For refresh cycles, however, either the CS input of all chips must be high or the CAS input must be held high to prevent several "wire-ORed" outputs from turning on with opposing force.

www.DataSheet4U.com

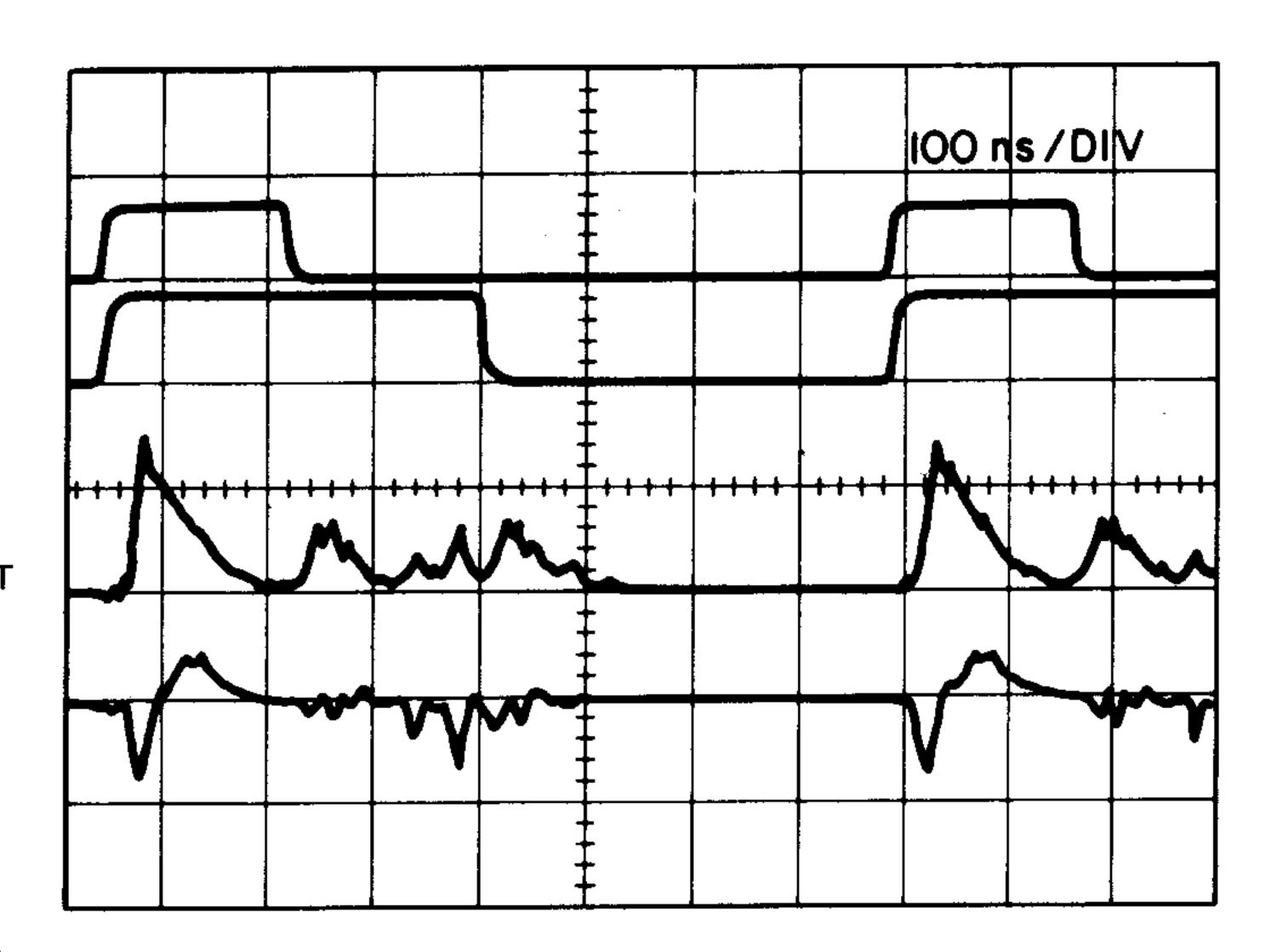

The current waveforms for the current drawn from the VDD and VBB supplies are shown in Figure A. Since the current is pulsed, proper power distribution and bypassing techniques are required to maintain system power supply noise levels at an acceptable level. Low inductance supply lines for VDD and VSS are desirable. One 0.01 microfarad, low inductance, bypass capacitor per two MK 4096 devices and one 6.8 microfarad electrolytic capacitor per eight MK 4096 devices on each of the VDD and VBB supply lines is desirable.

#### **POWER-UP**

Under normal operating conditions the MK 4096 requires no particular power-up sequence. However, in order to achieve the most reliable performance from the MK 4096, proper consideration should be given to the VBB/VDD power supply relationship. The VBB supply is an extremely important "protective voltage" since it performs two essential functions within the device. It establishes proper junction isolation and sets field-effect thresholds, both thin field and thick field. Misapplication of VBB or device operation without the VBB supply can affect long term device reliability. For optimum reliability performance from the MK 4096, it is suggested that measures be taken to not have VDD (+12V) applied to the device for over five (5) seconds without the application of VBB (-5V).

After power is applied to the device, the MK 4096 requires at least one memory cycle (RAS/CAS) before proper device operation is achieved. A normal 64 cycle refresh with both RAS and CAS is adequate for this purpose.

**Power Supply Current Waveforms**

# MOSTEK

## 4096 X 1 BIT DYNAMIC RAM

# MK4096 (P/N)-15

www.DataSheet4U.com

#### **FEATURES**

- ☐ Industry standard 16-pin DIP configuration

- ☐ Access time 350ns (MAX)

- Input latches for address, chip select and data in

- ☐ All inputs are low capacitance and TTL compatible

#### DESCRIPTION

The MK 4096 is the recognized industry standard 4096 word by 1 bit MOS Random Access Memory circuit packaged in a standard 16-pin DIP on 0.3 inch centers. This package configuration is made possible by a unique multiplexing and latching technique for the address inputs. The use of the 16-pin DIP for the MK 4096 provides high system bit densities and is compatible with widely available automated testing and insertion equipment.

The MK 4096 is fabricated with MOSTEK's standard Self-Aligned, Poly-Interconnect, N-Channel (SPIN) process. The SPIN process allows the MK 4096 to be a highly manufacturable, state-of-the-art memory circuit that exhibits the reliability and performance

Low cost for consumer and hobbyist microprocessor applications

☐ Three-state TTL compatible output, latched and valid into next cycle

☐ Low power dissipation

☐ Inputs protected against static charge

standards necessary for today's (and tomorrow's) data processing applications. The MK 4096 employs a single transistor storage cell, utilizing a dynamic storage technique and dynamic control circuitry to achieve optimum performance with low power dissipation.

System oriented features incorporated within the MK 4096 include direct interfacing capability with TTL, 6 instead of 12 address lines to drive, on-chip registers which can eliminate the need for interface registers, input logic levels selected to optimize the noise immunity, and two chip select methods to allow the user to determine the speed/power characteristics of his memory system.

#### **FUNCTIONAL DIAGRAM**

#### PIN CONNECTIONS

An - A5 AE CAS CC CS CH RAS RC

WRITE

PIN NAMES

ADDRESS INPUTS

COLUMN ADDRESS STROBE

CHIP SELECT

ROW ADDRESS STROBE

READ/WRITE INPUT

DIN DOUT VBB VCC VDD VSS

DATA IN

DATA OUT

POWER (-5V)

POWER (+5V)

POWER (+15V)

GROUND

### **ABSOLUTE MAXIMUM RATINGS\***

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# RECOMMENDED DC OPERATING CONDITIONS (17) $(0 \text{ C} \leq \text{TA} \leq +55 \text{ C})$

|      | PARAMETER                                          | MIN         | TYP  | MAX   | UNITS | NOTES |

|------|----------------------------------------------------|-------------|------|-------|-------|-------|

| VDD  | Supply Voltage                                     | 14.25       | 15.0 | 15.75 | Volts | 1     |

| VCC  | Supply Voltage                                     | Vss         |      | VDD   | Volts | 1,2   |

| VSS  | Supply Voltage                                     | 0           |      | 0     | Volts | 1     |

| VBB  | Supply Voltage                                     | <b>-4.5</b> | -5.0 | -5.5  | Volts | 1     |

| VIHC | Logic 1 Voltage —RAS,<br>CAS, WRITE                | 3.5         |      | 7.0   | Volts | 1,3   |

| VIH  | Logic 1 Voltage, all inputs except RAS, CAS, WRITE | 3.0         |      | 7.0   | Volts | 1,3   |

| VIL  | Logic 0 Voltage, all inputs                        | -1.0        |      | 0.8   | Volts | 1,3   |

#### DC ELECTRICAL CHARACTERISTICS (17)

$(0^{\circ}C \leq T_A \leq 55^{\circ}C) (V_{DD} = 15.0V \pm 5\%; V_{CC} = 5.0V \pm 10\%; V_{SS} = 0V; V_{BB} = -5.0V \pm 10\%)$

|       | PARAMETER                                           | MIN                                    | MAX | UNITS | NOTES |

|-------|-----------------------------------------------------|----------------------------------------|-----|-------|-------|

| IDD1  | Average VDD Power Supply Current                    |                                        | 35  | mA    | 4     |

| ICC   | VCC Power Supply Current                            |                                        |     | mA    | 5     |

| IBB   | Average VBB Power Supply Current                    |                                        | 75  | μΑ    |       |

| IDD2  | Standby VDD Power Supply Current                    | ······································ | 2   | mA    | 7     |

| IDD3  | Average VDD Supply Current during "RAS-only" cycles |                                        | 24  | mA    | 4     |

| (L)   | Input Leakage Current (any input)                   |                                        | 5   | μΑ    | 6     |

| 10(L) | Output Leakage Current                              |                                        | 10  | μΑ    | 7,8   |

| VOH   | Output Logic 1 Voltage @ IOUT= -5mA                 | 2.4                                    |     | Volts | 2     |

| VOL   | Output Logic 0 Voltage @ IOUT = 2mA                 |                                        | 0.4 | Volts |       |

#### **NOTES**

- All voltages referenced to VSS. VBB must be applied to and removed from the device within 5 seconds of VDD.

- Output voltage will swing from VSS to VCC if VCC ≤ VDD -4 volts. If VCC ≥ VDD -4 volts, the output will swing from VSS to a voltage somewhat less than VDD.

- 3. Device speed is not guaranteed at input voltages greater than TTL levels (0 to 5V).

- 4. Current is proportional to cycle rate; maximum current is measured at the fastest cycle rate.

- 5. ICC depends upon output loading. The VCC supply is connected to the output buffer only.

- 6. All device pins at 0 volts except VBB which is at -5 volts and the pin under test which is at +10 volts.

- 7. Output is disabled (open-circuit) and RAS and CAS are both at a logic 1.

- 8.  $0V \leq V_{OUT} \leq +10V$ .

### ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITONS (10,15,17)

$(0 \, \text{C} \leq \text{TA} \leq 55 \, \text{C}) \ (\text{V}_{DD} = 15.0 \, \text{V} \pm 5\%; \, \text{V}_{CC} = 5.0 \, \text{V} \pm 10\%, \, \text{V}_{SS} = 0 \, \text{V}, \, \text{V}_{BB} = -5.0 \, \text{V} \pm 10\%)$

| <u>.</u>        | PARAMETER                                   | MIN | MAX    | UNITS | NOTES |

|-----------------|---------------------------------------------|-----|--------|-------|-------|

| tRC             | Random Read or Write Cycle Time             | 500 |        | nsec  | 11    |

| tRAC            | Access time from Row Address Strobe         |     | 350    | nsec  | 11,13 |

| tCAC            | Access Time from Column Address<br>Strobe   |     | 200    | nsec  | 12,13 |

| tOFF            | Output Buffer Turn-Off Delay                | 0   | 100    | nsec  |       |

| tRP             | Row Address Strobe Precharge Time           | 150 |        | nsec  | :     |

| tRAS            | Row Address Strobe Pulse Width              | 350 | 10,000 | nsec  |       |

| tRCL            | Row To Column Strobe Lead Time              | 100 | 150    | nsec  | 14    |

| tCAS            | Column Address Strobe Pulse Width           | 200 |        | nsec  | 12    |

| tAS             | Address Set-Up Time                         | 0   |        | nsec  |       |

| <sup>t</sup> AH | Address Hold Time                           | 100 |        | nsec  |       |

| <sup>t</sup> CH | Chip Select Hold Time                       | 100 |        | nsec  |       |

| tΤ              | Rise and Fall Times                         | 3   | 50     | nsec  | 15    |

| tRCS            | Read Command Set-Up Time                    | 0   |        | nsec  |       |

| tRCH            | Read Command Hold Time                      | 0   |        | nsec  |       |

| twch            | Write Command Hold Time                     | 150 |        | nsec  |       |

| tWP             | Write Command Pulse Width                   | 150 | 6      | nsec  |       |

| tCRL            | Column to Row Strobe Lead Time              | -50 | +50    | nsec  |       |

| tCWL            | Write Command to Column Strobe<br>Lead Time | 150 |        | nsec  |       |

| tDS             | Data In Set-Up Time                         | 0 ' |        | nsec  | 16    |

| <sup>t</sup> DH | Data In Hold Time                           | 150 |        | nsec  | 16    |

| tRFSH           | Refresh Period                              |     | 1      | msec  |       |

| tMOD            | Modify Time                                 |     | 10     | μsec  |       |

| tDOH            | Data Out Hold Time                          | 10  |        | μsec  |       |

#### **NOTES Continued**

- 9. Capacitance measured with Boonton Meter or effective capacitance calculated from the equation:  $C = \frac{|\triangle|}{\Delta V}$  with current equal to a constant 20mA.

- 10. A C measurements assume t<sub>T</sub> = 5ns.

- 11. Assumes that tRCL + tT ≤ tRCL (max).

- 12. Assumes that t<sub>RCL</sub> + t<sub>T</sub> ≥t<sub>RCL</sub> (max).

- 13. Measured with a load circuit equivalent to 1 TTL load and C<sub>L</sub> = 100pF.

- 14. Operation within the t<sub>RCL</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met. t<sub>RCL</sub> (max) is specified as a reference point only; if t<sub>RCL</sub> is greater than the specified t<sub>RCL</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub> and t<sub>RAS</sub>, t<sub>RAC</sub> and t<sub>RCL</sub> will be longer by the amount t<sub>RCL</sub> + t<sub>T</sub> exceeds t<sub>RCL</sub> (max).

- 15. VIHC (min) or VIH (min) and VIL (max) are reference levels for measuring timing of input signals. Also, transition times are measured between VIHC or VIH and VIL.

- 16. These parameters are referenced to CAS leading edge in random write cycles and to WRITE leading edge in delayed write or readmodify-write cycles.

- 17. After the application of supply voltages or after extended periods of operation without clocks, the device must perform a minimum of one initialization cycle (any valid memory cycle containing both RAS and CAS) prior to normal operation.

# AC ELECTRICAL CHARACTERISTICS (0°C $\leq$ TA $\leq$ + 55°C) (VDD = 15.0V $\pm$ 5%, VCC = 5.0V $\pm$ 10%, VSS = 0V, VBB = -5.0V $\pm$ 10%)

| <del></del>      | PARAMETER                                    | TYP | MAX | UNITS | NOTES |  |

|------------------|----------------------------------------------|-----|-----|-------|-------|--|

| C <sub>1</sub> 1 | Input Capacitance (A0 – A5)                  | 7   | 10  | pF    | 9     |  |

| C <sub>12</sub>  | Input Capacitance (RAS, CAS, DIN, WRITE, CS) | 5   | 7   | pF    | 9     |  |

| Co               | Output Capacitance (DOUT)                    | 5   | 8   | рF    | 7,9   |  |

www.DataSheet4U.com

### **TIMING WAVEFORMS**

www.DataSheet4U.com

### **TIMING WAVEFORMS**

www.DataSheet4U.com

"RAS ONLY" REFRESH CYCLE (See text under Refresh)

#### NOTE:

Prior to the first memory cycle following a period (beyond 1mS) of "RAS-only refresh, a memory cycle employing both RAS and CAS must be performed to insure proper device operation.

#### **ADDRESSING**

The 12 address bits required to decode one of the 4096 cell locations within the MK 4096 are multiplexed onto the 6 address inputs and latched into the on-chip address latches by externally applying two negative going TTL level clocks. The first clock, the Row Address Strobe (RAS), latches the 6 row address bits into the chip. The second clock, the Column Address Strobe (CAS), subsequently latches the 6 column address bits plus Chip Select (CS) into the chip. (Note that since the Chip Select signal is not required until CAS time, which is well into the memory cycle, its decoding time does not add to system access or cycle time). Each of these signals, RAS and CAS, triggers a sequence of events which are controlled by different delayed internal clocks. The two clock chains are linked together logically in such a way that the address multiplexing operation is done outside of the critical path timing sequence for read data access. The later events in the CAS clock sequence are inhibited until the occurrence of a delayed signal derived from the RAS clock chain. This "gated CAS" feature allows the CAS clock to be externally activated as soon as the Row Address Hold Time specification (tAH) has been satisfied and the 6 address inputs have been changed from Row address to Column address information.

Note that CAS can be activated at any time after tAH and it will have no effect on the worst case data access time (tRAC) up to the point in time when the delayed row clock no longer inhibits the remaining sequence of column clocks. Two timing end points result from the internal gating of CAS which are called tRCL (min) and tRCL (max). No data storage or reading errors will result if CAS is applied to the MK 4096 at a point in time beyond the tRCL (max) limit. However, access time will then be determined exclusively by the access time from CAS (tCAC) rather than from RAS (tRAC), and access time from RAS will be lengthened by the amount that tRCL exceeds the tRCL (max) limit.

#### DATA INPUT/OUTPUT

Data to be written into a selected cell is latched into an on-chip register by a combination of WRITE and CAS while RAS is active. The later of the signals (WRITE or CAS) to make its negative transition is the strobe for the Data In register. This permits several options in the write cycle timing. In a write cycle, if the WRITE input is brought low prior to CAS, the Data In is strobed by CAS, and the set-up and hold times are referenced to CAS. If the data input is not available at CAS time or if it is desired that the cycle be a read-write or read-modify-write cycle, the WRITE signal must be delayed until after CAS. In this "delayed write cycle" the data input set-up and hold times are referenced to the negative edge of WRITE rather than to CAS.

(To illustrate this feature, Data In is referenced to WRITE in the timing diagram depicting the read-modify-write cycle while the "early write" cycle diagram shows Data In referenced to CAS). Note that if the chip is unselected (CS high at CAS time) WRITE commands are not executed and, consequently, data stored in the memory is unaffected.

www.DataSheet4U.com

Data is retrieved from the memory in a read cycle by maintaining WRITE in the inactive or high state throughout the portion of the memory cyle in which CAS is active. Data read from the selected cell will be available at the output within the specified access time.

#### DATA OUTPUT LATCH

Any change in the condition of the Data Out Latch is initiated by the CAS signal. The output buffer is not affected by memory (refresh) cycles in which only the RAS signal is applied to the MK 4096. Whenever CAS makes a negative transition, the output will go unconditionally open-circuited, independent of the state of any other input to the chip. If the cycle in progress is a read, read-modify-write, or a delayed write cycle and the chip is selected, then the output latch and buffer will again go active and at access time will contain the data read from the selected cell. This output data is the same polarity (not inverted) as the input data. If the cycle in progress is a write cycle (WRITE active low before CAS goes low) and the chip is selected, then at access time the output latch and buffer will contain a logic 1. Once having gone active, the output will remain valid until the MK 4096 receives the next CAS negative edge. Intervening refresh cycles in which a RAS is received (but no CAS) will not cause valid data to be affected. Conversely, the output will assume the open-circuit state during any cycle in which the MK 4096 receives a CAS but no RAS signal (regardless of the state of any other inputs). The output will also assume the open-circuit state in normal cycles (in which both RAS and CAS signals occur) if the chip is unselected.

The three-state data output buffer presents the data output pin with a low impedance to VCC for a logic 1 and a low impedance to VSS for a logic 0. The effective resistance to VCC (logic 1 state) is  $500\Omega$  maximum and  $150\Omega$  typically. The resistance to VSS (logic 0 state) is  $200\Omega$  maximum and  $100\Omega$  typically. The separate VCC pin allows the output buffer to be powered from the supply 'voltage of the logic to which the chip is interfaced. During battery standby operation, the VCC pin may have power removed without affecting the MK 4096 refresh operation. This allows all system logic except the RAS/CAS timing circuitry and the refresh address logic to be turned off during battery standby to conserve power.

#### **REFRESH**

Refresh of the dynamic cell matrix is accomplished by performing a memory cycle at each of the 64 row addresses within each 1 millisecond time interval. Any cycle in which a RAS signal occurs accomplishes a refresh operation. A read cycle will refresh the selected row, regardless of the Chip Select (CS) input. A write or read-modify-write cycle also refreshes the selected row, but the chip should be unselected to prevent writing data into the selected cell.

For standby operation, a "RAS-only" cycle can be employed to refresh the MK 4096. However, if "RAS-only" refresh cycles (where RAS is the only signal applied to the chip) are continued for extended periods, the output buffer may eventually lose proper data and go open-circuit. Prior to the first memory cycle following a period (beyond 2ms) of "RAS-only" refresh, a memory cycle employing both RAS and CAS must be performed to precharge the internal circuitry. This "dummy cycle" allows the output buffer to regain activity and enables the device to perform a read or write cycle upon command.

#### POWER DISSIPATION/STANDBY MODE

Most of the circuitry used in the MK 4096 is dynamic and most of the power drawn is the result of an address strobe edge. Because the power is not drawn during the whole time the strobe is active, the dynamic power is a function of operating frequency rather than active duty cycle. Typically, the power is 120 mW at a 1 µsec cycle rate for the MK 4096 with a maximum power of less than 550 mW at 500 nsec cycle time. To minimize the overall system power, the Row Address Strobe (RAS) should be decoded and supplied to only the selected chips. The CAS must be supplied to all chips (to turn off the unselected output). Those chips that did not receive a RAS, however, will not dissipate any power on the CAS edges, except for that required to turn off the outputs. If the RAS signal is decoded and supplied only to the selected chips, then the Chip Select (CS) input of all chips can be at a logic 0. The chips that receive a CAS but no RAS will be unselected (output open-circuited) regardless of the Chip Select input. For refresh cycles, however, either the CS input of all chips must be high or the CAS input must be held high to prevent several "wire-ORed" outputs from turning on with opposing force.

www.DataSheet4U.com

The current waveforms for the current drawn from the VDD and VBB supplies are shown in Figure A. Since the current is pulsed, proper power distribution and bypassing techniques are required to maintain system power supply noise levels at an acceptable level. Low inductance supply lines for VDD and VSS are desirable. One 0.01 microfarad, low inductance, bypass capacitor per two MK 4096 devices and one 6.8 microfarad electrolytic capacitor per eight MK 4096 devices on each of the VDD and VBB supply lines is desirable.

#### **POWER-UP**

Under normal operating conditions the MK 4096 requires no particular power-up sequence. However, in order to achieve the most reliable performance from the MK 4096, proper consideration should be given to the VBB/VDD power supply relationship. The VBB supply is an extremely important "protective voltage" since it performs two essential functions within the device. It establishes proper junction isolation and sets field-effect thresholds, both thin field and thick field. Misapplication of VBB or device operation without the VBB supply can affect long term device reliability. For optimum reliability performance from the MK 4096, it is suggested that measures be taken to not have VDD (+15V) applied to the device for over five (5) seconds without the application of VBB (-5V).

After power is applied to the device, the MK 4096 requires at least one memory cycle (RAS/CAS) before proper device operation is achieved. A normal 64 cycle refresh with both RAS and CAS is adequate for this purpose.

ROW ADD STROBE (RAS)

COL ADD STROBE (CAS)

CURRENT

DRAWN

I<sub>DD</sub> (+15 VOLT

FROM

SUPPLY)

SUPPLIES

IBB (-5 VOLT

(50 MA/DIV)

SUPPLY)

Power Supply Current Waveforms