# **Document Title**

512K x 16 Bit x 2 Banks (16-MBIT) SDRAM

# **Revision History**

| Revision No          | <u>History</u>                                                                                                         | <u>Draft Date</u> <u>Remark</u>                                       |

|----------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 0A<br>0B<br>0C<br>0D | Initial Draft<br>revise for typo on page 17<br>Add Pb-free package<br>Add speed grade -5ns<br>Obselte speed grade -8ns | August 28,2001<br>January 10,2002<br>December 02,2003<br>June 25,2004 |

The attached datasheets are provided by ICSI. Integrated Circuit Solution Inc reserve the right to change the specifications and products. ICSI will answer to your questions about device. If you have any questions, please contact the ICSI offices.

# 512K x 16 Bits x 2 Banks (16-MBIT) SYNCHRONOUS DYNAMIC RAM

#### **FEATURES**

- Clock frequency: 200, 166, 143 MHz

- Fully synchronous; all signals referenced to a positive clock edge

- Two banks can be operated simultaneously and independently

- · Dual internal bank controlled by A11 (bank select)

- Single 3.3V power supply

- · LVTTL interface

- Programmable burst length

(1, 2, 4, 8, full page)

- Programmable burst sequence: Sequential/Interleave

- · Auto refresh, self refresh

- · 4096 refresh cycles every 64 ms

- Random column address every clock cycle

- Programmable CAS latency (2, 3 clocks)

- Burst read/write and burst read/single write operations capability

- Burst termination by burst stop and precharge command

- · Byte controlled by LDQM and UDQM

- Package 400mil 50-pin TSOP-2

- Pb(lead)-free package is available

#### DESCRIPTION

*ICSI*'s 16Mb Synchronous DRAM IC42S16100 is organized as a 524,288-word x 16-bit x 2-bank for improved performance. The synchronous DRAMs achieve high-speed data transfer using pipeline architecture. All inputs and outputs signals refer to the rising edge of the clock input.

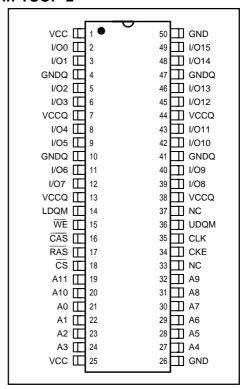

# PIN CONFIGURATIONS 50-Pin TSOP-2

#### PIN DESCRIPTIONS

| A0-A11        | Address Input              |

|---------------|----------------------------|

| A0-A10        | Row Address Input          |

| A11           | Bank Select Address        |

| A0-A7         | Column Address Input       |

| I/O0 to I/O15 | Data I/O                   |

| CLK           | System Clock Input         |

| CKE           | Clock Enable               |

| <u>CS</u>     | Chip Select                |

| RAS           | Row Address Strobe Command |

| CAS  | Column Address Strobe Command |

|------|-------------------------------|

| WE   | Write Enable                  |

| LDQM | Lower Bye, Input/Output Mask  |

| UDQM | Upper Bye, Input/Output Mask  |

| Vcc  | Power                         |

| GND  | Ground                        |

| VccQ | Power Supply for I/O Pin      |

| GNDQ | Ground for I/O Pin            |

| NC   | No Connection                 |

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution Inc.

# **PIN FUNCTIONS**

| Pin No.                                                       | Symbol           | Type             | Function (In Detail)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 to 24<br>27 to 32                                          | A0-A10           | Input Pin        | A0 to A10 are address inputs. A0-A10 are used as row address inputs during active command input and A0-A7 as column address inputs during read or write command input. A10 is also used to determine the precharge mode during other commands. If A10 is LOW during precharge command, the bank selected by A11 is precharged, but if A10 is HIGH, both banks will be precharged. When A10 is HIGH in read or write command cycle, the precharge starts automatically after the burst access.  These signals become part of the OP CODE during mode register set command input.                                       |

| 19                                                            | A11              | Input Pin        | A11 is the bank selection signal. When A11 is LOW, bank 0 is selected and when high, bank 1 is selected. This signal becomes part of the OP CODE during mode register set command input.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16                                                            | CAS              | Input Pin        | CAS, in conjunction with the RAS and WE, forms the device command. See the "Command Truth Table" item for details on device commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 34                                                            | CKE              | Input Pin        | The CKE input determines whether the CLK input is enabled within the device. When is CKE HIGH, the next rising edge of the CLK signal will be valid, and when LOW, invalid. When CKE is LOW, the device will be in either the power-down mode, the clock suspend mode, or the self refresh mode. The CKE is an asynchronous input.                                                                                                                                                                                                                                                                                    |

| 35                                                            | CLK              | Input Pin        | CLK is the master clock input for this device. Except for CKE, all inputs to this device are acquired in synchronization with the rising edge of this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18                                                            | ĊS               | Input Pin        | The $\overline{\text{CS}}$ input determines whether command input is enabled within the device. Command input is enabled when $\overline{\text{CS}}$ is LOW, and disabled with $\overline{\text{CS}}$ is HIGH. The device remains in the previous state when $\overline{\text{CS}}$ is HIGH.                                                                                                                                                                                                                                                                                                                          |

| 2, 3, 5, 6, 8, 9, 11<br>12, 39, 40, 42, 43,<br>45, 46, 48, 49 | I/O0 to<br>I/O15 | I/O Pin          | I/O0 to I/O15 are I/O pins. I/O through these pins can be controlled in byte units using the LDQM and UDQM pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

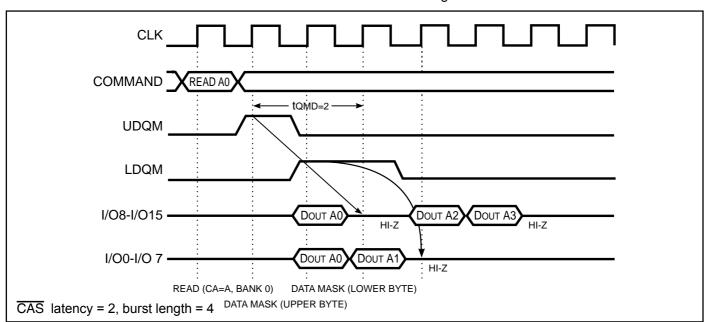

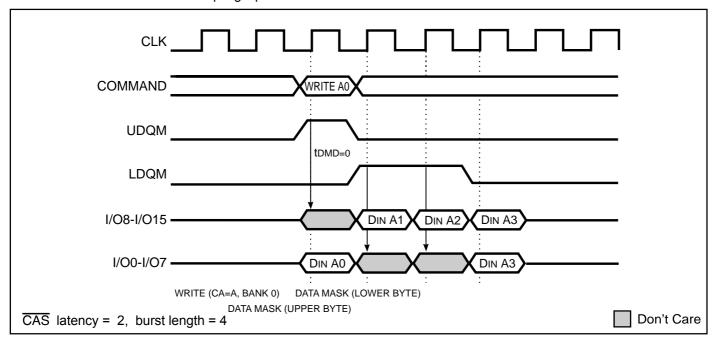

| 14, 36                                                        | LDQM,<br>UDQM    | Input Pin        | LDQM and UDQM control the lower and upper bytes of the I/O buffers. In read mode, LDQM and UDQM control the output buffer. When LDQM or UDQM is LOW, the corresponding buffer byte is enabled, and when HIGH, disabled. The outputs go to the HIGH impedance state when LDQM/UDQM is HIGH. This function corresponds to $\overline{OE}$ in conventional DRAMs. In write mode, LDQM and UDQM control the input buffer. When LDQM or UDQM is LOW, the corresponding buffer byte is enabled, and data can be written to the device. When LDQM or UDQM is HIGH, input data is masked and cannot be written to the device. |

| 17                                                            | RAS              | Input Pin        | RAS, in conjunction with CAS and WE, forms the device command. See the "Command Truth Table" item for details on device commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15                                                            | WE               | Input Pin        | WE, in conjunction with RAS and CAS, forms the device command. See the "Command Truth Table" item for details on device commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7, 13, 38, 44                                                 | VccQ             | Power Supply Pin | VccQ is the output buffer power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1, 25                                                         | Vcc              | Power Supply Pin | Vcc is the device internal power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4, 10, 41, 47                                                 | GNDQ             | Power Supply Pin | GNDQ is the output buffer ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 26, 50                                                        | GND              | Power Supply Pin | GND is the device internal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

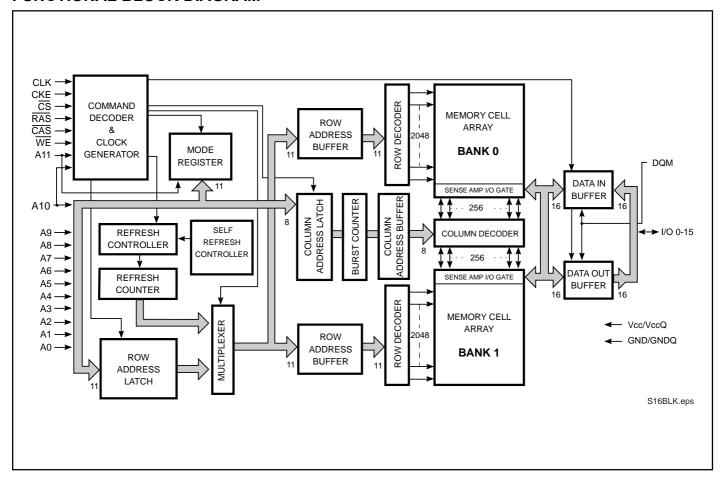

#### **FUNCTIONAL BLOCK DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol   | Parameters                               | Rating       | Unit |

|----------|------------------------------------------|--------------|------|

| VCC MAX  | Maximum Supply Voltage                   | -1.0 to +4.6 | V    |

| VCCQ MAX | Maximum Supply Voltage for Output Buffer | -1.0 to +4.6 | V    |

| VIN      | Input Voltage                            | -1.0 to +4.6 | V    |

| Vout     | Output Voltage                           | -1.0 to +4.6 | V    |

| PD MAX   | Allowable Power Dissipation              | 1            | W    |

| Ics      | Output Shorted Current                   | 50           | mA   |

| Topr     | Operating Temperature                    | 0 to +70     | °C   |

| Тѕтс     | Storage Temperature                      | -55 to +150  | °C   |

# DC RECOMMENDED OPERATING CONDITIONS<sup>(2)</sup> (At TA = 0 to +70°C)

| Symbol    | Parameter             | Min. | Тур. | Max.                  | Unit |

|-----------|-----------------------|------|------|-----------------------|------|

| Vcc, VccQ | Supply Voltage        | 3.0  | 3.3  | 3.6                   | V    |

| VIH       | Input High Voltage(3) | 2.0  | _    | V <sub>DD</sub> + 0.3 | V    |

| VIL       | Input Low Voltage(4)  | -0.3 | _    | +0.8                  | V    |

# **CAPACITANCE CHARACTERISTICS**(1,2) (At $T_A = 0$ to +25°C, $V_{CC} = V_{CC}Q = 3.3 \pm 0.3V$ , f = 1 MHz)

| Symbol | Parameter                                                   | Тур. | Max. | Unit |

|--------|-------------------------------------------------------------|------|------|------|

| Cin1   | Input Capacitance: A0-A11                                   | _    | 4    | рF   |

| CIN2   | Input Capacitance: (CLK, CKE, CS, RAS, CAS, WE, LDQM, UDQM) | _    | 4    | pF   |

| CI/O   | Data Input/Output Capacitance: I/O0-I/O15                   | _    | 5    | pF   |

- 1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. All voltages are referenced to GND.

- 3. Vih (max) = Vccq + 2.0V with a pulse width  $\leq 3$  ns.

- 4.  $V_{IL}$  (min) = GND 2.0V with a pulse < 3 ns and -1.5V with a pulse < 5ns.

# DC ELECTRICAL CHARACTERISTICS (Recommended Operation Conditions unless otherwise noted.)

| Symbol | Parameter                                      | <b>Test Condition</b>                                                    |                 | Speed | Min.           | Max. | Unit |

|--------|------------------------------------------------|--------------------------------------------------------------------------|-----------------|-------|----------------|------|------|

| lıL    | Input Leakage Current                          | 0V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> , with pi<br>the tested pin at 0V | ins other than  |       | <del>-</del> 5 | 5    | μA   |

| loL    | Output Leakage Current                         | Output is disabled<br>0V ≤ Vouт ≤ Vcc                                    |                 |       | -10            | 10   | μA   |

| Vон    | Output High Voltage Level                      | lоuт <b>= −2 mA</b>                                                      |                 |       | 2.4            | _    | V    |

| Vol    | Output Low Voltage Level                       | Iout = +2 mA                                                             |                 |       | _              | 0.4  | V    |

| Icc1   | Operating Current(1,2)                         | One Bank Operation,                                                      | CAS latency = 3 | -5    | _              | 150  | mA   |

|        |                                                | Burst Length=1                                                           |                 | -6    | _              | 145  | mΑ   |

|        |                                                | tRC≥tRC (min.)<br>Ιουτ = 0mA                                             |                 | -7    | _              | 140  | mA   |

| lcc2   | Precharge Standby Current (In Power-Down Mode) | CKE ≤ VIL (MAX)                                                          | tck = tck (MIN) |       | _              | 2    | mA   |

| Icc3   | Active Standby Current                         | CKE ≥ VIH (MIN)                                                          | tck = tck (MIN) | _     | <del>_</del> 5 | 50   | mA   |

|        | (In Non Power-Down Mode)                       |                                                                          |                 | _     | <del></del> 6  | 45   | mΑ   |

|        |                                                |                                                                          |                 | _     | <u> </u>       | 40   | mΑ   |

| Icc4   | Operating Current                              | tck = tck (MIN)                                                          |                 | -5    | _              | 150  | mA   |

|        | (In Burst Mode)(1)                             | Iout = 0mA                                                               |                 | -6    | _              | 140  | mΑ   |

|        |                                                |                                                                          |                 | -7    | _              | 130  | mΑ   |

| Icc5   | Auto-Refresh Current                           | trc = trc (MIN)                                                          |                 | -5    | _              | 100  | mA   |

|        |                                                |                                                                          |                 | -6    | _              | 90   | mΑ   |

|        |                                                |                                                                          |                 | -7    | _              | 80   | mΑ   |

| Icc6   | Self-Refresh Current                           | CKE ≤ 0.2V                                                               |                 | _     | _              | 1    | mA   |

<sup>1.</sup> These are the values at the minimum cycle time. Since the currents are transient, these values decrease as the cycle time increases. Also note that a bypass capacitor of at least 0.01 µF should be inserted between Vcc and GND for each memory chip to suppress power supply voltage noise (voltage drops) due to these transient currents.

<sup>2.</sup> lcc1 and lcc4 depend on the output load.

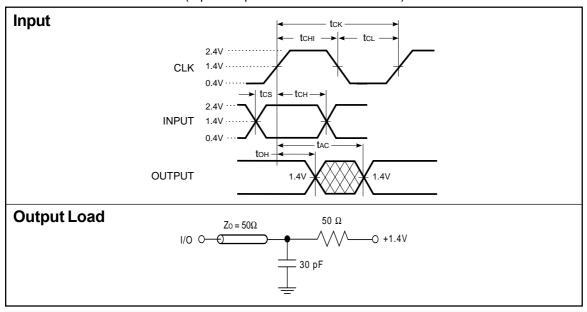

#### **AC CHARACTERISTICS**(1,2,3)

|                   |                                                     |          | -5      | -       | 6       | -        |         |       |

|-------------------|-----------------------------------------------------|----------|---------|---------|---------|----------|---------|-------|

| Symbol            | Parameter                                           | Min.     | Max.    | Min.    | Max.    | Min.     | Max     | Units |

| tcx3              | Clock Cycle Time CAS Laten                          | cy = 3 5 | _       | 6       | _       | 7        | _       | ns    |

| tck2              | CAS Laten                                           | ·        |         | 8       | _       | 8.6      | _       | ns    |

| tac3              | Access Time From CLK <sup>(4)</sup> CAS Laten       |          | 4.5     | _       | 5.5     | _        | 6       | ns    |

| tac2              | CAS Laten                                           | ,        | 5       | _       | 6       | _        | 6       | ns    |

| tсн               | CLK HIGH Level Width                                | 2        | _       | 2       | _       | 2.5      | _       | ns    |

| ta.               | CLK LOW Level Width                                 | 2        | _       | 2       | _       | 2.5      | _       | ns    |

| tон               | Output Data Hold Time                               | 2        | _       | 2       | _       | 2        | _       | ns    |

| <b>t</b> z        | Output LOW Impedance Time                           | 0        | _       | 0       | _       | 0        | _       | ns    |

| tHz3              | Output HIGH Impedance Time <sup>(5)</sup> CAS Laten |          | 4.5     | _       | 5.5     | _        | 6       | ns    |

| tHz2              | CAS Laten                                           | cy = 2 — | 5       |         | 6       |          | 6       | ns    |

| tos               | Input Data Setup Time                               | 2        | _       | 2       | _       | 2        | _       | ns    |

| tън               | Input Data Hold Time                                | 1        |         | 1       | _       | 1        | _       | ns    |

| tas               | Address Setup Time                                  | 2        | _       | 2       | _       | 2        | _       | ns    |

| <b>t</b> AH       | Address Hold Time                                   | 1        | _       | 1       | _       | 1        | _       | ns    |

| taks              | CKE Setup Time                                      | 2        | _       | 2       | _       | 2        | _       | ns    |

| taxx              | CKE Hold Time                                       | 1        | _       | 1       | _       | 1        | _       | ns    |

| toka              | CKE to CLK Recovery Delay Time                      | 1CLK+    | 3 —     | 1CLK+3  | _       | 1CLK+3   | _       | ns    |

| tcs               | Command Setup Time (CS, RAS, CAS, WE, DQM)          | 2        | _       | 2       | _       | 2        | _       | ns    |

| to <sub>H</sub>   | Command Hold Time (CS, RAS, CAS, WE, DQM)           | 1        | _       | 1       | _       | 1        | _       | ns    |

| <b>t</b> RC       | Command Period (REF to REF / ACT to ACT)            | 50       | _       | 60      | _       | 70       | _       | ns    |

| <b>T</b> RAS      | Command Period (ACT to PRE)                         | 30       | 100,000 | 36      | 100,000 | 42       | 100,000 | ns    |

| <b>t</b> RP       | Command Period (PRE to ACT)                         | 15       | _       | 18      | _       | 21       | _       | ns    |

| t <del>k</del> co | Active Command To Read / Write Command Delay Time   | 15       | _       | 18      | _       | 21       | _       | ns    |

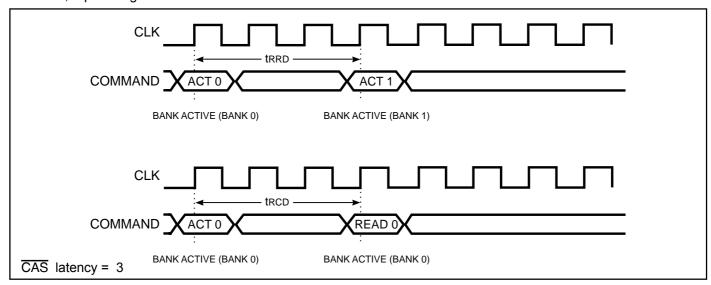

| <b>t</b> ASD      | Command Period (ACT [0] to ACT[1])                  | 10       | _       | 12      | _       | 14       | _       | ns    |

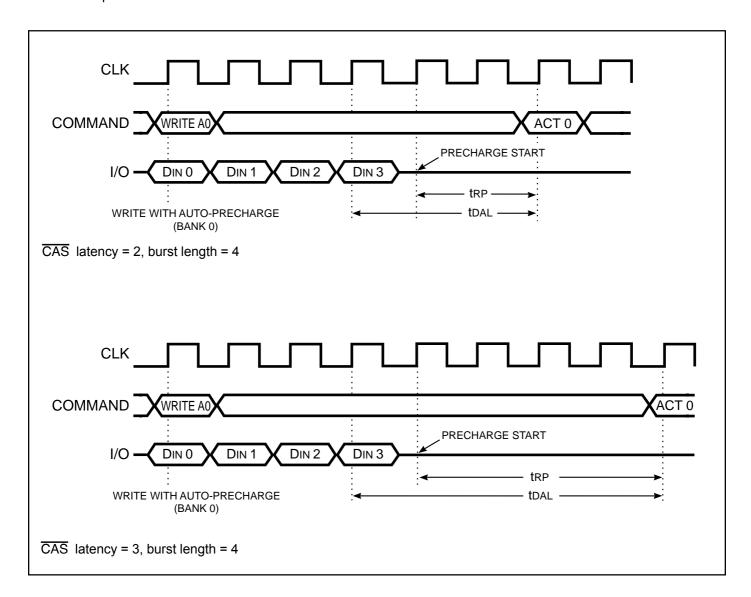

| top.              | Input Data To Precharge                             | 2CLK     | _       | 2CLK    | _       | 2CLK     | _       | ns    |

|                   | Command Delay time                                  |          |         |         |         |          |         |       |

| <b>t</b> DAL      | Input Data To Active / Refresh                      | 2CLK+tr  | RP —    | 2CLK+tr | · _     | 2CLK+trr | _       | ns    |

|                   | Command Delay time (During Auto-Precharge)          |          |         |         |         |          |         |       |

| t⊤                | Transition Time                                     | 1        | 10      | 1       | 10      | 1        | 10      | ns    |

| tref              | Refresh Cycle Time (4096)                           | _        | 64      | _       | 64      |          | 64      | ms    |

- 1. When power is first applied, memory operation should be started 100 µs after Vcc and VccQ reach their stipulated voltages. Also note that the power-on sequence must be executed before starting memory operation.

- 2. Measured with  $t_T = 1$  ns.

- 3. The reference level is 1.4 V when measuring input signal timing. Rise and fall times are measured between V<sub>IH</sub> (min.) and V<sub>IL</sub> (max.).

- 4. Access time is measured at 1.4V with the load shown in the figure below.

- 5. The time thz (max.) is defined as the time required for the output voltage to transition by ± 200 mV from VoH (min.) or VoL (max.) when the output is in the high impedance state.

# **OPERATING FREQUENCY / LATENCY RELATIONSHIPS**

|              |                                                                         | _   | _   | _   |       |

|--------------|-------------------------------------------------------------------------|-----|-----|-----|-------|

| Symb         | ol Parameter                                                            | -5  | -6  | -7  | Units |

| _            | Clock Cycle Time                                                        | 5   | 6   | 7   | ns    |

| _            | Operating Frequency                                                     | 200 | 166 | 143 | MHz   |

| tcac         | CAS Latency                                                             | 3   | 3   | 3   | cycle |

| trcd         | Active Command To Read/Write Command Delay Time                         | 3   | 3   | 3   | cycle |

| trac         | RAS Latency (trcd + tcac)                                               | 6   | 6   | 6   | cycle |

| trc          | Command Period (REF to REF / ACT to ACT)                                | 10  | 10  | 10  | cycle |

| tras         | Command Period (ACT to PRE)                                             | 6   | 6   | 6   | cycle |

| <b>t</b> RP  | Command Period (PRE to ACT)                                             | 3   | 3   | 3   | cycle |

| trrd         | Command Period (ACT[0] to ACT [1])                                      | 2   | 2   | 2   | cycle |

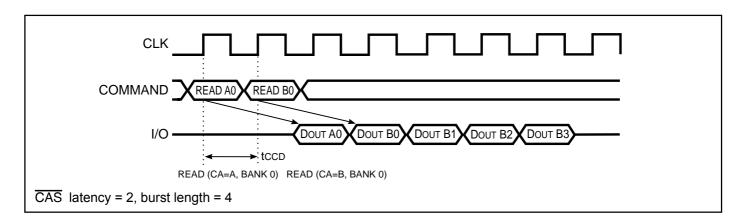

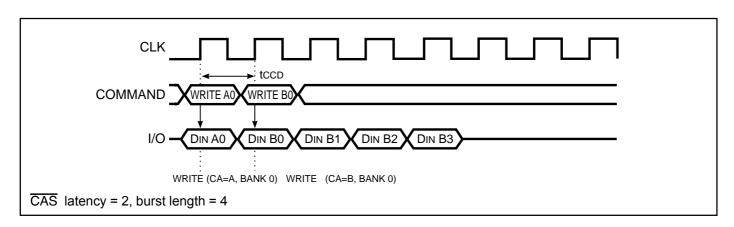

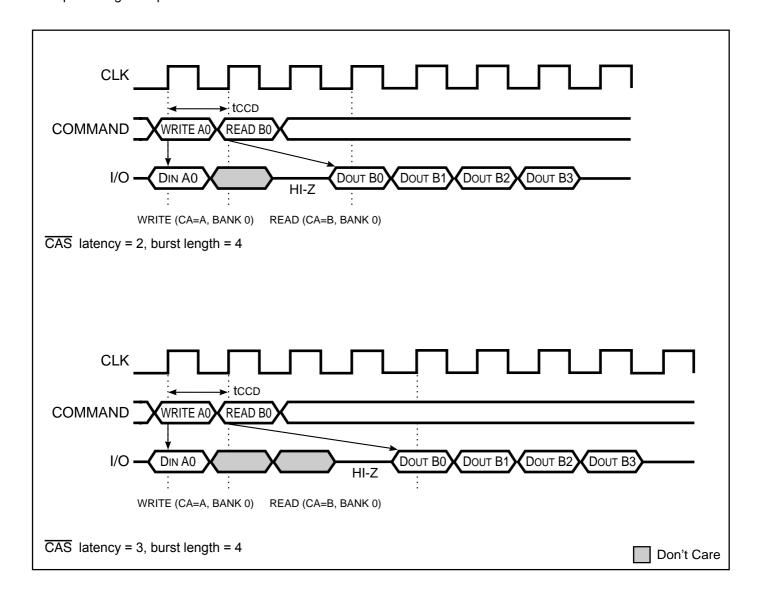

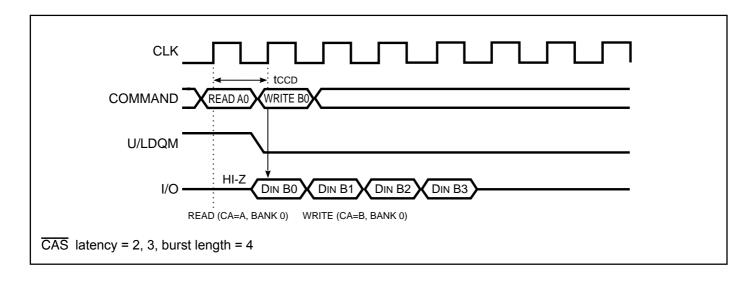

| tccd         | Column Command Delay Time<br>(READ, READA, WRIT, WRITA)                 | 1   | 1   | 1   | cycle |

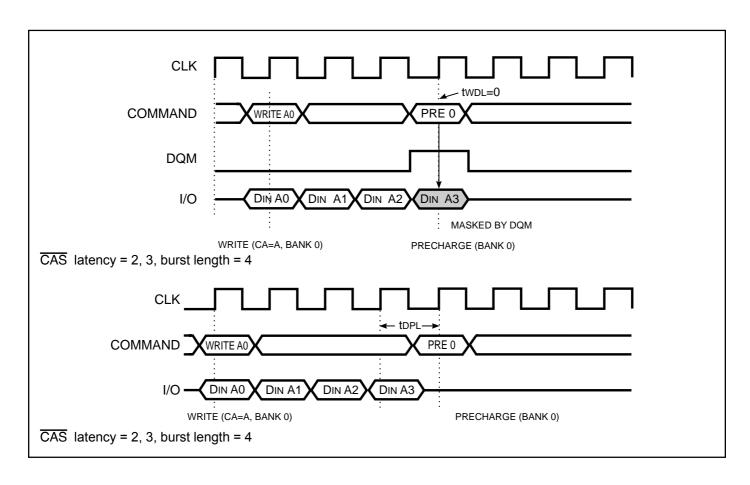

| tDPL         | Input Data To Precharge Command Delay Time                              | 2   | 2   | 2   | cycle |

| <b>t</b> DAL | Input Data To Active/Refresh Command Delay Time (During Auto-Precharge) | 5   | 5   | 5   | cycle |

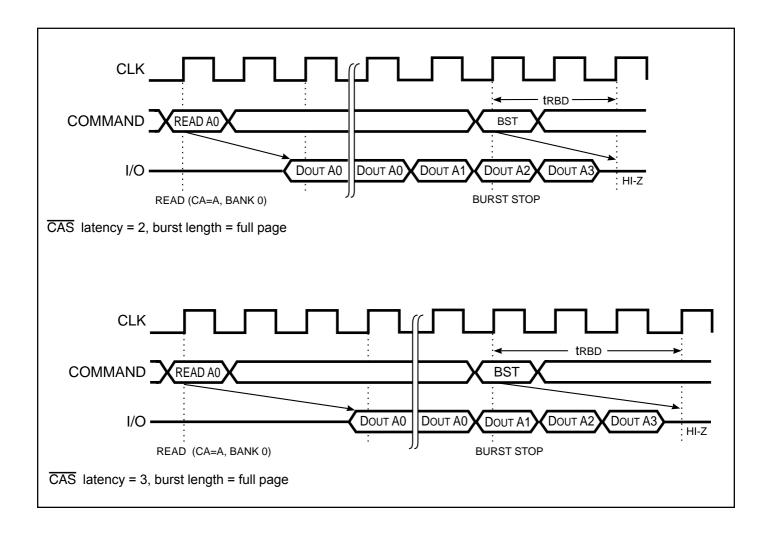

| <b>t</b> RBD | Burst Stop Command To Output in HIGH-Z Delay Time (Read)                | 3   | 3   | 3   | cycle |

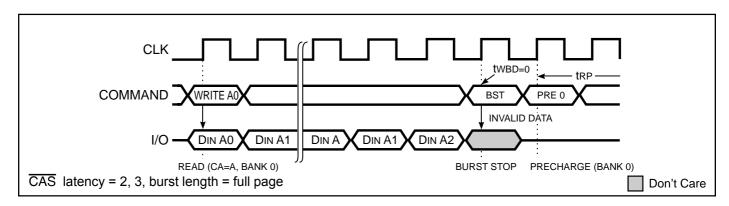

| twbd         | Burst Stop Command To Input in Invalid Delay Time (Write)               | 0   | 0   | 0   | cycle |

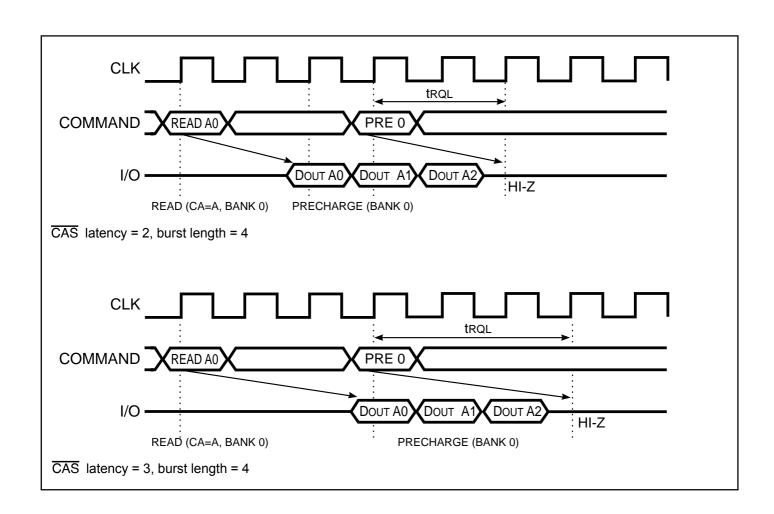

| <b>t</b> RQL | Precharge Command To Output in HIGH-Z Delay Time (Read)                 | 3   | 3   | 3   | cycle |

| twdl         | Precharge Command To Input in Invalid Delay Time (Write)                | 0   | 0   | 0   | cycle |

| <b>t</b> PQL | Last Output To Auto-Precharge Start Time (Read)                         | -2  | -2  | -2  | cycle |

| tqmd         | DQM To Output Delay Time (Read)                                         | 2   | 2   | 2   | cycle |

| <b>t</b> DMD | DQM To Input Delay Time (Write)                                         | 0   | 0   | 0   | cycle |

| <b>t</b> MCD | Mode Register Set To Command Delay Time                                 | 2   | 2   | 2   | cycle |

# AC TEST CONDITIONS (Input/Output Reference Level: 1.4V)

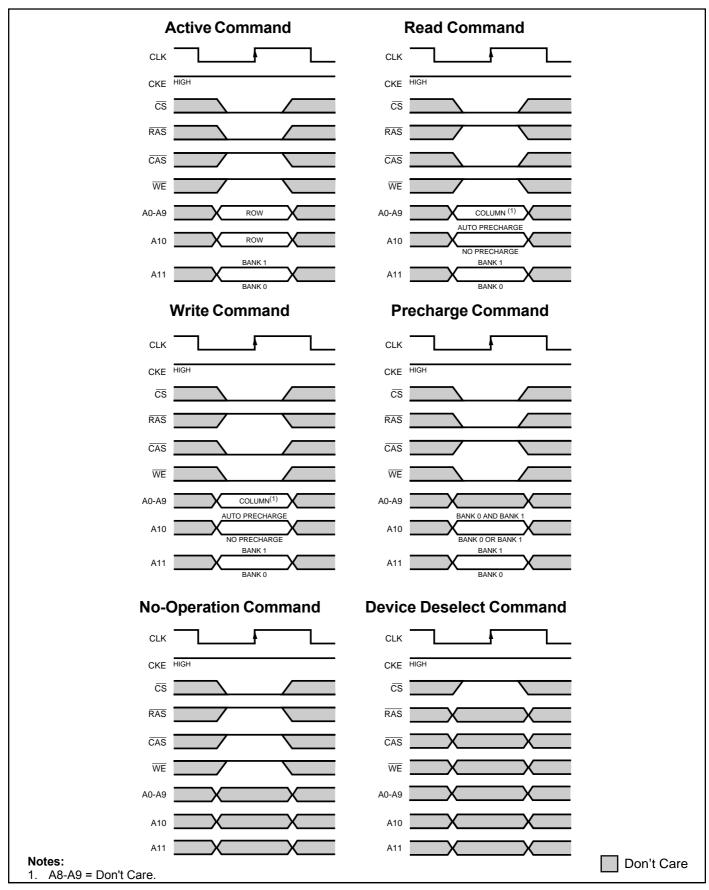

### **COMMANDS**

# **COMMANDS** (cont.)

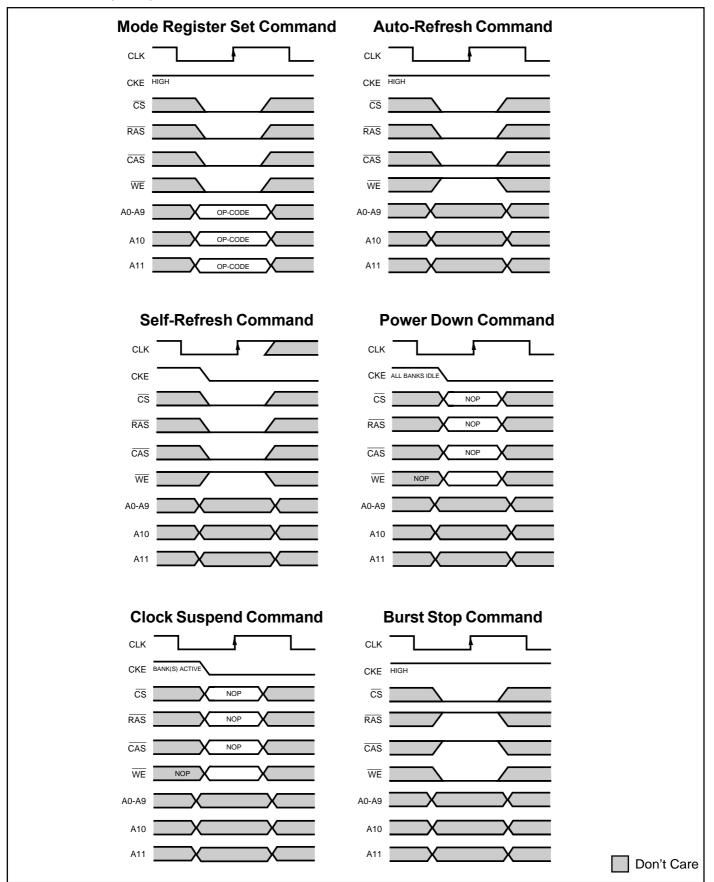

#### **Mode Register Set Command**

$(\overline{CS}, \overline{RAS}, \overline{CAS}, \overline{WE} = LOW)$

The IC42S16100 product incorporates a register that defines the device operating mode. This command functions as a data input pin that loads this register from the pins A0 to A11. When power is first applied, the stipulated power-on sequence should be executed and then the IC42S16100 should be initialized by executing a mode register set command.

Note that the mode register set command can be executed only when both banks are in the idle state (i.e. deactivated).

Another command cannot be executed after a mode register set command until after the passage of the period tMCD, which is the period required for mode register set command execution.

#### **Active Command**

$(\overline{CS}, \overline{RAS} = LOW, \overline{CAS}, \overline{WE} = HIGH)$

The IC42S16100 includes two banks of 4096 rows each. This command selects one of the two banks according to the A11 pin and activates the row selected by the pins A0 to A10.

This command corresponds to the fall of the RAS signal from HIGH to LOW in conventional DRAMs.

#### **Precharge Command**

(CS, RAS, WE = LOW, CAS = HIGH)

This command starts precharging the bank selected by pins A10 and A11. When A10 is HIGH, both banks are precharged at the same time. When A10 is LOW, the bank selected by A11 is precharged. After executing this command, the next command for the selected bank(s) is executed after passage of the period trap, which is the period required for bank precharging.

This command corresponds to the RAS signal from LOW to HIGH in conventional DRAMs

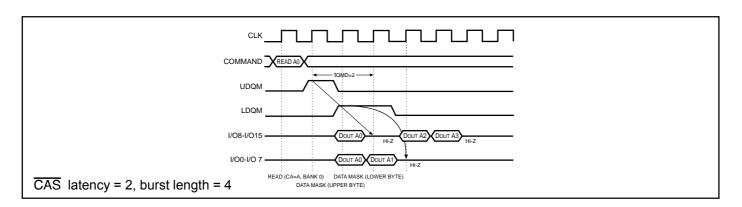

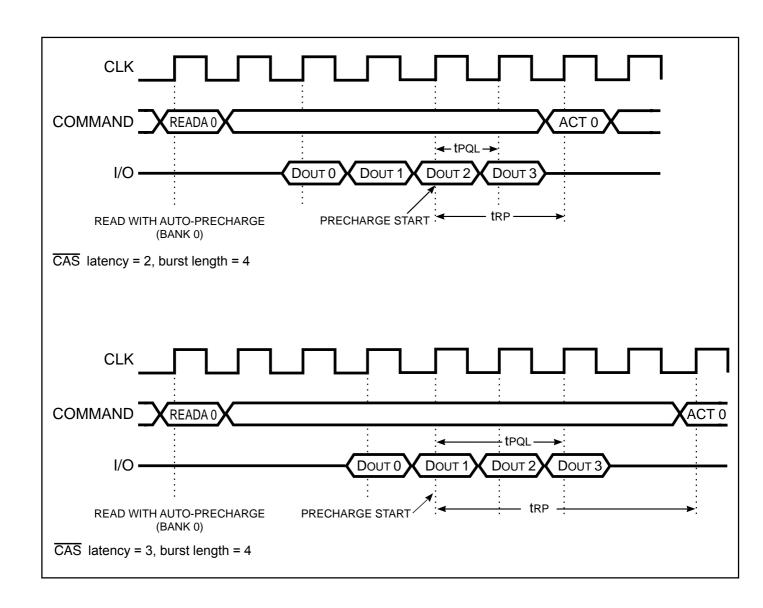

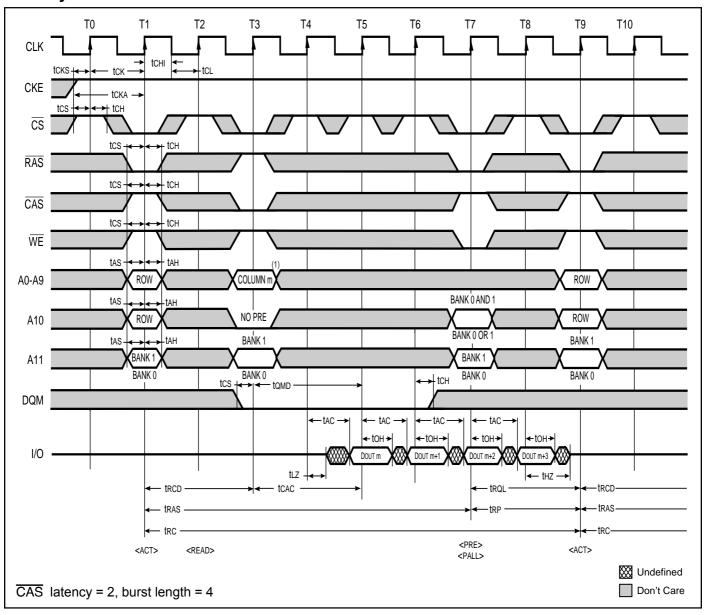

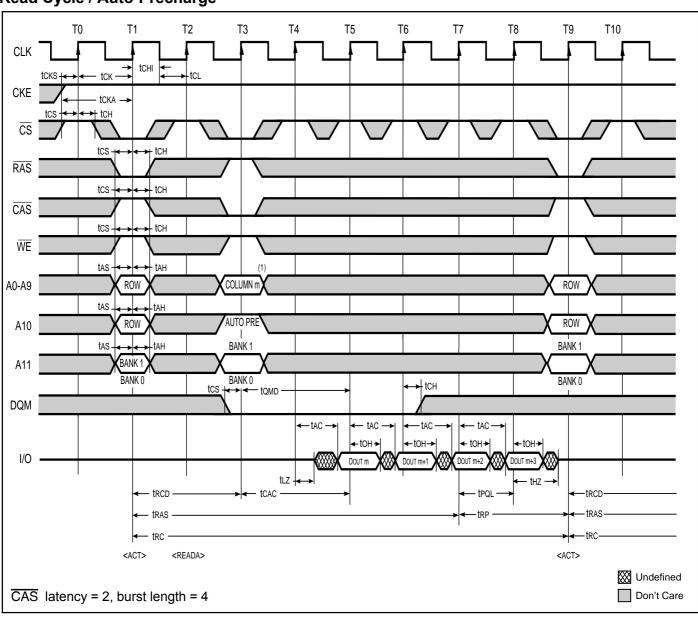

#### **Read Command**

$(\overline{CS}, \overline{CAS} = LOW, \overline{RAS}, \overline{WE} = HIGH)$

This command selects the bank specified by the A11 pin and starts a burst read operation at the start address specified by pins A0 to A9. Data is output following CAS latency.

The selected bank must be activated before executing this command.

When the A10 pin is HIGH, this command functions as a read with auto-precharge command. After the burst read completes, the bank selected by pin A11 is precharged. When the A10 pin is LOW, the bank selected by the A11 pin remains in the activated state after the burst read completes.

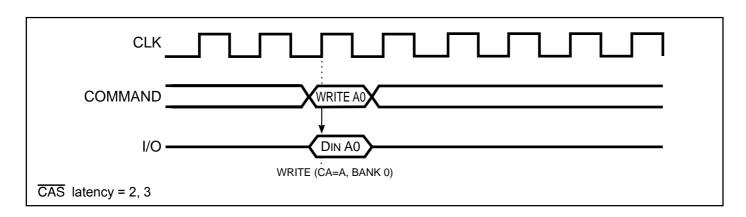

#### **Write Command**

$(\overline{CS}, \overline{CAS}, \overline{WE} = LOW, \overline{RAS} = HIGH)$

When burst write mode has been selected with the mode register set command, this command selects the bank specified by the A11 pin and starts a burst write operation at the start address specified by pins A0 to A9. This first data must be input to the I/O pins in the cycle in which this command.

The selected bank must be activated before executing this command.

When A10 pin is HIGH, this command functions as a write with auto-precharge command. After the burst write completes, the bank selected by pin A11 is precharged. When the A10 pin is low, the bank selected by the A11 pin remains in the activated state after the burst write completes.

After the input of the last burst write data, the application must wait for the write recovery period (tdpl, tdal) to elapse according to  $\overline{CAS}$  latency.

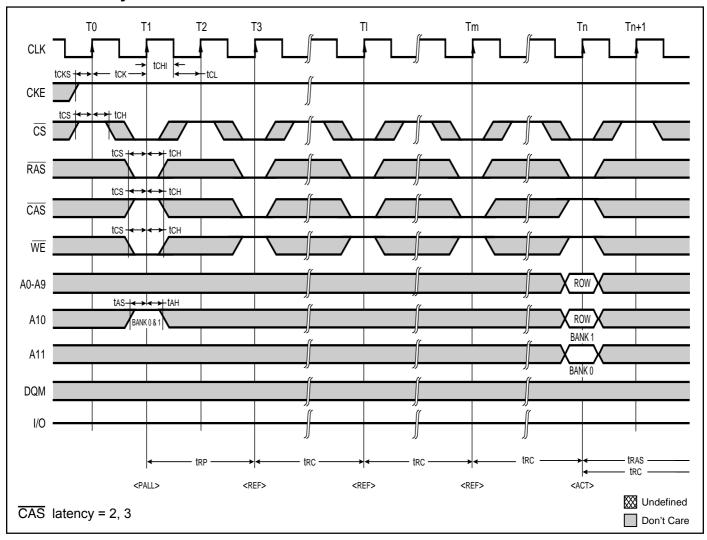

#### **Auto-Refresh Command**

$(\overline{CS}, \overline{RAS}, \overline{CAS} = LOW, \overline{WE}, CKE = HIGH)$

This command executes the auto-refresh operation. The row address and bank to be refreshed are automatically generated during this operation.

Both banks must be placed in the idle state before executing this command.

The stipulated period (tRC) is required for a single refresh operation, and no other commands can be executed during this period.

The device goes to the idle state after the internal refresh operation completes.

This command must be executed at least 4096 times every 64 ms.

This command corresponds to CBR auto-refresh in conventional DRAMs.

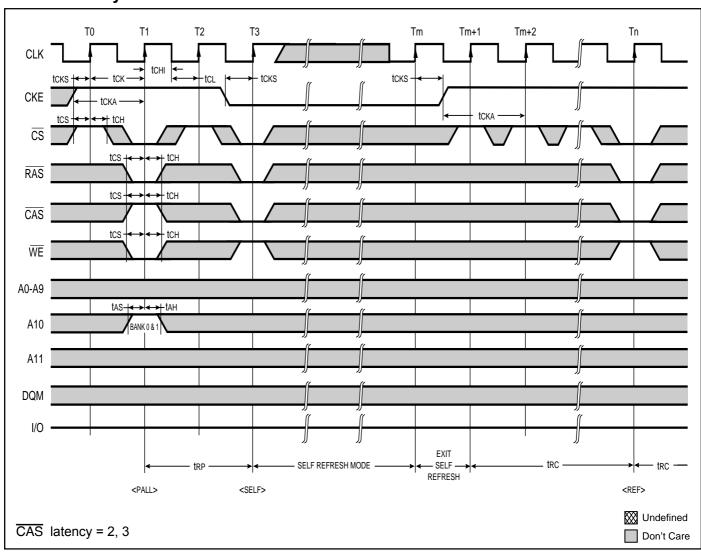

#### **Self-Refresh Command**

$(\overline{CS}, \overline{RAS}, \overline{CAS}, CKE = LOW, \overline{WE} = HIGH)$

This command executes the self-refresh operation. The row address to be refreshed, the bank, and the refresh interval are generated automatically internally during this operation. The self-refresh operation is started by dropping the CKE pin from HIGH to LOW. The self-refresh operation continues as long as the CKE pin remains LOW and there is no need for external control of any other pins. The self-refresh operation is terminated by raising the CKE pin from LOW to HIGH. The next command cannot be executed until the device internal recovery period (tRC) has elapsed. After the self-refresh, since it is impossible to determine the address of the last row to be refreshed, an auto-refresh should immediately be performed for all addresses (4096 cycles).

Both banks must be placed in the idle state before executing this command.

#### **Burst Stop Command**

(CS, WE, = LOW, RAS, CAS = HIGH)

The command forcibly terminates burst read and write operations. When this command is executed during a burst read operation, data output stops after the  $\overline{\text{CAS}}$  latency period has elapsed.

#### No Operation

$(\overline{CS}, = LOW, \overline{RAS}, \overline{CAS}, \overline{WE} = HIGH)$

This command has no effect on the device.

#### **Device Deselect Command**

$(\overline{CS} = HIGH)$

This command does not select the device for an object of operation. In other words, it performs no operation with respect to the device.

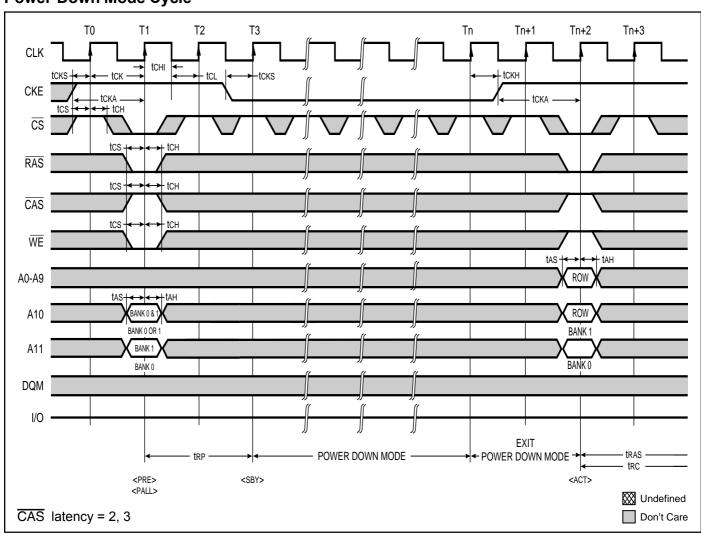

#### **Power-Down Command**

(CKE = LOW)

When both banks are in the idle (inactive) state, or when at least one of the banks is not in the idle (inactive) state, this command can be used to suppress device power dissipation by reducing device internal operations to the absolute minimum. Power-down mode is started by dropping the CKE pin from HIGH to LOW. Power-down mode continues as long as the CKE pin is held low. All pins other than the CKE pin are invalid and none of the other commands can be executed in this mode. The power-down operation is terminated by raising the CKE pin from LOW to HIGH. The next command cannot be executed until the recovery period (tcka) has elapsed.

Since this command differs from the self-refresh command described above in that the refresh operation is not performed automatically internally, the refresh operation must be performed within the refresh period (tref). Thus the maximum time that power-down mode can be held is just under the refresh cycle time.

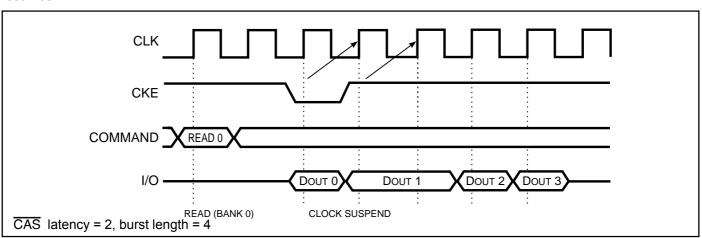

# **Clock Suspend**

(CKE = LOW)

This command can be used to stop the device internal clock temporarily during a read or write cycle. Clock suspend mode is started by dropping the CKE pin from HIGH to LOW. Clock suspend mode continues as long as the CKE pin is held LOW. All input pins other than the CKE pin are invalid and none of the other commands can be executed in this mode. Also note that the device internal state is maintained. Clock suspend mode is terminated by raising the CKE pin from LOW to HIGH, at which point device operation restarts. The next command cannot be executed until the recovery period (tcka) has elapsed.

Since this command differs from the self-refresh command described above in that the refresh operation is not performed automatically internally, the refresh operation must be performed within the refresh period (tref). Thus the maximum time that clock suspend mode can be held is just under the refresh cycle time.

# **COMMAND TRUTH TABLE**(1,2)

|        |                                          | CK  | Œ |    |     |     |    |     |            |       |            |        |

|--------|------------------------------------------|-----|---|----|-----|-----|----|-----|------------|-------|------------|--------|

| Symbol | Command                                  | n-1 | n | CS | RAS | CAS | WE | DQM | <b>A11</b> | A10   | A9-A0      | I/On   |

| MRS    | Mode Register Set <sup>(3,4)</sup>       | Н   | Χ | L  | L   | L   | L  | Χ   |            | OP CO | DE         | Х      |

| REF    | Auto-Refresh <sup>(5)</sup>              | Н   | Н | L  | L   | L   | Н  | Х   | Х          | Х     | Х          | HIGH-Z |

| SREF   | Self-Refresh <sup>(5,6)</sup>            | Н   | L | L  | L   | L   | Н  | Х   | Χ          | Х     | Х          | HIGH-Z |

| PRE    | Precharge Selected Bank                  | Н   | Χ | L  | L   | Н   | L  | Х   | BS         | L     | Х          | Х      |

| PALL   | Precharge Both Banks                     | Н   | Χ | L  | L   | Н   | L  | Х   | Х          | Н     | Х          | Х      |

| ACT    | Bank Activate <sup>(7)</sup>             | Н   | Χ | L  | L   | Н   | Н  | Х   | BS         | Row   | Row        | Χ      |

| WRIT   | Write                                    | Н   | Χ | L  | Н   | L   | L  | Х   | BS         | L     | Column(18) | Х      |

| WRITA  | Write With Auto-Precharge <sup>(8)</sup> | Н   | Χ | L  | Н   | L   | L  | Х   | BS         | Н     | Column(18) | Х      |

| READ   | Read <sup>(8)</sup>                      | Н   | Χ | L  | Н   | L   | Н  | Χ   | BS         | L     | Column(18) | Х      |

| READA  | Read With Auto-Precharge <sup>(8)</sup>  | Н   | Χ | L  | Н   | L   | Н  | Х   | BS         | Н     | Column(18) | Х      |

| BST    | Burst Stop <sup>(9)</sup>                | Н   | Χ | L  | Н   | Н   | L  | Х   | Х          | Х     | Х          | Х      |

| NOP    | No Operation                             | Н   | Χ | L  | Н   | Н   | Н  | Χ   | Χ          | Χ     | Х          | Х      |

| DESL   | Device Deselect                          | Н   | Χ | Н  | Χ   | Χ   | Х  | Х   | Χ          | Х     | Х          | Х      |

| SBY    | Clock Suspend / Standby Mode             | L   | Χ | Χ  | Χ   | Χ   | Χ  | Х   | Χ          | Х     | Х          | Х      |

| ENB    | Data Write / Output Enable               | Н   | Χ | Χ  | Χ   | Χ   | Χ  | L   | Χ          | Χ     | Х          | Active |

| MASK   | Data Mask / Output Disable               | Н   | Χ | Χ  | Χ   | Χ   | Χ  | Н   | Χ          | Χ     | Х          | HIGH-Z |

# **DQM TRUTH TABLE**(1,2)

|        |                                       | CKE |   | D     | QM    |

|--------|---------------------------------------|-----|---|-------|-------|

| Symbol | Command                               | n-1 | n | UPPER | LOWER |

| ENB    | Data Write / Output Enable            | Н   | Χ | L     | L     |

| MASK   | Data Mask / Output Disable            | Н   | Χ | Н     | Н     |

| ENBU   | Upper Byte Data Write / Output Enable | Н   | Χ | L     | Х     |

| ENBL   | Lower Byte Data Write / Output Enable | Н   | Χ | Х     | L     |

| MASKU  | Upper Byte Data Mask / Output Disable | Н   | Χ | Н     | Χ     |

| MASKL  | Lower Byte Data Mask / Output Disable | Н   | Χ | Х     | Н     |

# **CKE TRUTH TABLE**(1,2)

|        |                              | CKE                  |     |   |    |     |     |    |     |     |       |

|--------|------------------------------|----------------------|-----|---|----|-----|-----|----|-----|-----|-------|

| Symbol | Command                      | <b>Current State</b> | n-1 | n | CS | RAS | CAS | WE | A11 | A10 | A9-A0 |

| SPND   | Start Clock Suspend Mode     | Active               | Н   | L | Х  | Х   | Χ   | Х  | Х   | Χ   | Х     |

| _      | Clock Suspend                | Other States         | L   | L | Х  | Χ   | Х   | Х  | Х   | Х   | Х     |

| _      | Terminate Clock Suspend Mode | Clock Suspend        | L   | Н | Χ  | Χ   | Χ   | Χ  | Χ   | Χ   | Х     |

| REF    | Auto-Refresh                 | Idle                 | Н   | Н | L  | L   | L   | Н  | Χ   | Χ   | Χ     |

| SELF   | Start Self-Refresh Mode      | Idle                 | Н   | L | L  | L   | L   | Н  | Χ   | Χ   | Χ     |

| SELFX  | Terminate Self-Refresh Mode  | Self-Refresh         | L   | Н | L  | Н   | Н   | Н  | Χ   | Χ   | Χ     |

|        |                              |                      | L   | Н | Н  | Χ   | Χ   | Χ  | Χ   | Χ   | Χ     |

| PDWN   | Start Power-Down Mode        | Idle                 | Н   | L | L  | Н   | Н   | Н  | Χ   | Χ   | Χ     |

|        |                              |                      | Н   | L | Н  | Χ   | Χ   | Χ  | Χ   | Χ   | Χ     |

| _      | Terminate Power-Down Mode    | Power-Down           | L   | Н | Χ  | Χ   | Х   | Х  | Χ   | Χ   | Х     |

# **OPERATION COMMAND TABLE**(1,2)

| <b>Current State</b> | Command      | Operation                                                              | <u>cs</u> | RAS   | CAS | WE | A11    | A10        | A9-A0             |

|----------------------|--------------|------------------------------------------------------------------------|-----------|-------|-----|----|--------|------------|-------------------|

| Idle                 | DESL         | No Operation or Power-Down <sup>(12)</sup>                             | Н         | Х     | Х   | Χ  | Χ      | Χ          | Х                 |

|                      | NOP          | No Operation or Power-Down <sup>(12)</sup>                             | L         | Н     | Н   | Н  | Χ      | Χ          | Χ                 |

|                      | BST          | No Operation or Power-Down                                             | L         | Н     | Н   | L  | Χ      | Χ          | Χ                 |

|                      | READ / READA | Illegal                                                                | L         | Н     | L   | Н  | V      | V          | V <sup>(18)</sup> |

|                      | WRIT/WRITA   | Illegal                                                                | L         | Н     | L   | L  | V      | V          | V <sup>(18)</sup> |

|                      | ACT          | Row Active                                                             | L         | L     | Н   | Н  | V      | V          | V <sup>(18)</sup> |

|                      | PRE/PALL     | No Operation                                                           | L         | L     | Н   | L  | V      | V          | Χ                 |

|                      | REF/SELF     | Auto-Refresh or Self-Refresh <sup>(13)</sup>                           | L         | L     | L   | Н  | Χ      | Χ          | Χ                 |

|                      | MRS          | Mode Register Set                                                      | L         | L     | L   | L  | С      | P COI      | DE                |

| Row Active           | DESL         | No Operation                                                           | Н         | Х     | Χ   | Χ  | Х      | Х          | Χ                 |

|                      | NOP          | No Operation                                                           | L         | Н     | Н   | Н  | Χ      | Χ          | Χ                 |

|                      | BST          | No Operation                                                           | L         | Н     | Н   | L  | Χ      | Χ          | Χ                 |

|                      | READ/READA   | Read Start <sup>(17)</sup>                                             | L         | Н     | L   | Н  | V      | V          | V <sup>(18)</sup> |

|                      | WRIT/WRITA   | Write Start <sup>(17)</sup>                                            | L         | Н     | L   | L  | V      | V          | V <sup>(18)</sup> |

|                      | ACT          | Illegal <sup>(10)</sup>                                                | L         | L     | Н   | Н  | V      | V          | V <sup>(18)</sup> |

|                      | PRE/PALL     | Precharge <sup>(15)</sup>                                              | L         | L     | Н   | L  | V      | V          | Χ                 |

|                      | REF/SELF     | Illegal                                                                | L         | L     | L   | Н  | Χ      | Χ          | Χ                 |

|                      | MRS          | Illegal                                                                | L         | L     | L   | L  |        | P COI      |                   |

| Read                 | DESL         | Burst Read Continues, Row Active When Done                             | Н         | Х     | Χ   | Χ  | Х      | Х          | Х                 |

|                      | NOP          | Burst Read Continues, Row Active When Done                             | L         | Н     | Н   | Н  | Χ      | Χ          | Χ                 |

|                      | BST          | Burst Interrupted, Row Active After Interrupt                          | L         | Н     | Н   | L  | Χ      | Χ          | Χ                 |

|                      | READ/READA   | Burst Interrupted, Read Restart After Interrupt <sup>(16)</sup>        | L         | Н     | L   | Н  | V      | V          | V <sup>(18)</sup> |

|                      | WRIT/WRITA   | Burst Interrupted Write Start After Interrupt(11,16)                   | L         | Н     | L   | L  | V      | V          | V <sup>(18)</sup> |

|                      | ACT          | Illegal <sup>(10)</sup>                                                | L         | L     | Н   | Н  | V      | V          | V <sup>(18)</sup> |

|                      | PRE/PALL     | Burst Read Interrupted, Precharge After Interrupt                      | L         | L     | Н   | L  | V      | V          | Χ                 |

|                      | REF/SELF     | Illegal                                                                | L         | L     | L   | Н  | Χ      | Χ          | Χ                 |

|                      | MRS          | Illegal                                                                | L         | L     | L   | L  |        | P COI      |                   |

| Write                | DESL         | Burst Write Continues, Write Recovery When Done                        | H         | X     | X   | X  | Х      | Х          | Х                 |

|                      | NOP          | Burst Write Continues, Write Recovery When Done                        | L         | Н     | Н   | Н  | Х      | Х          | X                 |

|                      | BST          | Burst Write Interrupted, Row Active After Interrupt                    | L         | Н     | Н   | L  | Х      | Х          | Χ                 |

|                      | READ/READA   | Burst Write Interrupted, Read Start After Interrupt <sup>(11,16)</sup> | L         | H     | L   | Н  | V      | ٧          | V <sup>(18)</sup> |

|                      | WRIT/WRITA   | Burst Write Interrupted, Write Restart After Interrupt <sup>(16)</sup> | L         | Н     | L   | L  | V      | V          | V <sup>(18)</sup> |

|                      | ACT          | Illegal <sup>(10)</sup>                                                | L         | Ľ     | Н   | Н  | V      | ٧          | V <sup>(18)</sup> |

|                      | PRE/PALL     | Burst Write Interrupted, Precharge After Interrupt                     | L         | L     | н   | L  | V      | ٧          | X                 |

|                      | REF/SELF     | Illegal                                                                | L         | L     | L   | Н  | X      | X          | X                 |

|                      | MRS          | Illegal                                                                | -<br>I    | L     | L   | L  |        | P COI      |                   |

| Read With            | DESL         | Burst Read Continues, Precharge When Done                              | <u></u> Н | X     | X   | X  | X      | X          | X                 |

| Auto-                | NOP          | Burst Read Continues, Precharge When Done                              | L         | Ĥ     | H   | Ĥ  | X      | X          | X                 |

| Precharge            | BST          | Illegal                                                                | L         | Н     | H   | L  | Х      | Х          | Х                 |

|                      | READ/READA   | Illegal                                                                | ı         | <br>Н | L   | Н  | V      | ٧          | V <sup>(18)</sup> |

|                      | WRIT/WRITA   | Illegal                                                                | L         | <br>H | L   | L  | V      | V          | V <sup>(18)</sup> |

|                      | ACT          | Illegal <sup>(10)</sup>                                                | ı         | L     | Н   | Н  | V      | V          | V <sup>(18)</sup> |

|                      | PRE/PALL     | Illegal <sup>(10)</sup>                                                | ı         | L     | Н   | L  | V      | V          | X                 |

|                      | REF/SELF     | Illegal                                                                | L<br>I    | L     | L   | Н  | v<br>X | v<br>X     | X                 |

|                      |              | -                                                                      | L         |       |     |    |        | A<br>P COI |                   |

|                      | MRS          | Illegal                                                                | L         | L     | L   | L  | C      | ır UUl     | <i></i>           |

# **OPERATION COMMAND TABLE**(1,2)

| <b>Current State</b>         | Command    | Operation                                                      | <u>cs</u> | RAS | CAS | WE | <b>A11</b> | A10   | A9-A0             |  |  |

|------------------------------|------------|----------------------------------------------------------------|-----------|-----|-----|----|------------|-------|-------------------|--|--|

| Write With<br>Auto-Precharge | DESL       | Burst Write Continues, Write Recovery And Precharge When Done  | Н         | Х   | Х   | Х  | Χ          | Х     | Х                 |  |  |

|                              | NOP        | Burst Write Continues, Write Recovery And Precharge            | L         | Н   | Н   | Н  | Χ          | Χ     | Χ                 |  |  |

|                              | BST        | Illegal                                                        | L         | Н   | Н   | L  | Χ          | Χ     | Χ                 |  |  |

|                              | READ/READA | Illegal                                                        | L         | Н   | L   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | WRIT/WRITA | Illegal                                                        | L         | Н   | L   | L  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | ACT        | Illegal <sup>(10)</sup>                                        | L         | L   | Н   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | PRE/PALL   | Illegal <sup>(10)</sup>                                        | L         | L   | Н   | L  | V          | V     | Χ                 |  |  |

|                              | REF/SELF   | Illegal                                                        | L         | L   | L   | Н  | Χ          | Χ     | Χ                 |  |  |

|                              | MRS        | Illegal                                                        | L         | L   | L   | L  | C          | PCOE  | Œ                 |  |  |

| Row Precharge                | DESL       | No Operation, Idle State After tRP Has Elapsed                 | Н         | Χ   | Χ   | Χ  | Χ          | Χ     | Χ                 |  |  |

|                              | NOP        | No Operation, Idle State After tRP Has Elapsed                 | L         | Н   | Н   | Н  | Χ          | Χ     | Χ                 |  |  |

|                              | BST        | No Operation, Idle State After tRP Has Elapsed                 | L         | Н   | Н   | L  | Χ          | Χ     | Χ                 |  |  |

|                              | READ/READA | Illegal <sup>(10)</sup>                                        | L         | Н   | L   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | WRIT/WRITA | Illegal <sup>(10)</sup>                                        | L         | Н   | L   | L  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | ACT        | Illegal <sup>(10)</sup>                                        | L         | L   | Н   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | PRE/PALL   | No Operation, Idle State After trp Has Elapsed <sup>(10)</sup> | L         | L   | Н   | L  | V          | V     | Х                 |  |  |

|                              | REF/SELF   | Illegal                                                        | L         | L   | L   | Н  | Χ          | Χ     | Χ                 |  |  |

|                              | MRS        | Illegal                                                        | L         | L   | L   | L  | 0          | P COI | DE                |  |  |

| Immediately                  | DESL       | No Operation, Row Active After tRCD Has Elapsed                | Н         | Χ   | Χ   | Χ  | Χ          | Χ     | Χ                 |  |  |

| Following                    | NOP        | No Operation, Row Active After tRCD Has Elapsed                | L         | Н   | Н   | Н  | Χ          | Χ     | Χ                 |  |  |

| Row Active                   | BST        | No Operation, Row Active After tRCD Has Elapsed                | L         | Н   | Н   | L  | Χ          | Χ     | Χ                 |  |  |

|                              | READ/READA | Illegal <sup>(10)</sup>                                        | L         | Н   | L   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | WRIT/WRITA | Illegal <sup>(10)</sup>                                        | L         | Н   | L   | L  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | ACT        | Illegal <sup>(10,14)</sup>                                     | L         | L   | Н   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | PRE/PALL   | Illegal <sup>(10)</sup>                                        | L         | L   | Н   | L  | V          | V     | Χ                 |  |  |

|                              | REF/SELF   | Illegal                                                        | L         | L   | L   | Н  | Χ          | Χ     | Χ                 |  |  |

|                              | MRS        | Illegal                                                        | L         | L   | L   | L  | 0          | P COI | DΕ                |  |  |

| Write                        | DESL       | No Operation, Row Active After topl Has Elapsed                | Н         | Χ   | Χ   | Χ  | Χ          | Χ     | Х                 |  |  |

| Recovery                     | NOP        | No Operation, Row Active After topl Has Elapsed                | L         | Н   | Н   | Н  | Χ          | Χ     | Χ                 |  |  |

|                              | BST        | No Operation, Row Active After topl Has Elapsed                | L         | Н   | Н   | L  | Χ          | Χ     | Χ                 |  |  |

|                              | READ/READA | Read Start                                                     | L         | Н   | L   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | WRIT/WRITA | Write Restart                                                  | L         | Н   | L   | L  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | ACT        | Illegal <sup>(10)</sup>                                        | L         | L   | Н   | Н  | V          | V     | V <sup>(18)</sup> |  |  |

|                              | PRE/PALL   | Illegal <sup>(10)</sup>                                        | L         | L   | Н   | L  | V          | V     | Χ                 |  |  |

|                              | REF/SELF   | Illegal                                                        | L         | L   | L   | Н  | Χ          | Χ     | Χ                 |  |  |

|                              | MRS        | Illegal                                                        | L         | L   | L   | L  |            |       |                   |  |  |

#### **OPERATION COMMAND TABLE**(1,2)

| <b>Current State</b> | Command    | Operation                                       | <u>cs</u> | RAS | CAS | WE | A11 | A10   | A9-A0             |

|----------------------|------------|-------------------------------------------------|-----------|-----|-----|----|-----|-------|-------------------|

| Write Recovery       | DESL       | No Operation, Idle State After tDAL Has Elapsed | Н         | Χ   | Χ   | Х  | Х   | Х     | Χ                 |

| With Auto-           | NOP        | No Operation, Idle State After tDAL Has Elapsed | L         | Н   | Н   | Н  | Χ   | Χ     | Χ                 |

| Precharge            | BST        | No Operation, Idle State After tDAL Has Elapsed | L         | Н   | Н   | L  | Χ   | Χ     | Χ                 |

|                      | READ/READA | Illegal <sup>(10)</sup>                         | L         | Н   | L   | Н  | V   | V     | V <sup>(18)</sup> |

|                      | WRIT/WRITA | Illegal <sup>(10)</sup>                         | L         | Н   | L   | L  | V   | V     | V <sup>(18)</sup> |

|                      | ACT        | Illegal <sup>(10)</sup>                         | L         | L   | Н   | Н  | V   | V     | V <sup>(18)</sup> |

|                      | PRE/PALL   | Illegal <sup>(10)</sup>                         | L         | L   | Н   | L  | V   | V     | Χ                 |

|                      | REF/SELF   | Illegal                                         | L         | L   | L   | Н  | Χ   | Χ     | Χ                 |

|                      | MRS        | Illegal                                         | L         | L   | L   | L  | 0   | P COI | DE                |

| Refresh              | DESL       | No Operation, Idle State After tRP Has Elapsed  | Н         | Χ   | Χ   | Χ  | Х   | Х     | Х                 |

|                      | NOP        | No Operation, Idle State After tRP Has Elapsed  | L         | Н   | Н   | Н  | Χ   | Χ     | Χ                 |

|                      | BST        | No Operation, Idle State After tRP Has Elapsed  | L         | Н   | Н   | L  | Χ   | Χ     | Χ                 |

|                      | READ/READA | Illegal                                         | L         | Н   | L   | Н  | V   | V     | V <sup>(18)</sup> |

|                      | WRIT/WRITA | Illegal                                         | L         | Н   | L   | L  | V   | V     | V <sup>(18)</sup> |

|                      | ACT        | Illegal                                         | L         | L   | Н   | Н  | V   | V     | V <sup>(18)</sup> |

|                      | PRE/PALL   | Illegal                                         | L         | L   | Н   | L  | V   | V     | Χ                 |

|                      | REF/SELF   | Illegal                                         | L         | L   | L   | Н  | Χ   | Χ     | Χ                 |

|                      | MRS        | Illegal                                         | L         | L   | L   | L  | 0   | P COI | DE                |

| Mode Register        | DESL       | No Operation, Idle State After tMcD Has Elapsed | Н         | Χ   | Χ   | Χ  | Χ   | Х     | Χ                 |

| Set                  | NOP        | No Operation, Idle State After tmcD Has Elapsed | L         | Н   | Н   | Н  | Χ   | Χ     | Χ                 |

|                      | BST        | No Operation, Idle State After tmcD Has Elapsed | L         | Н   | Н   | L  | Χ   | Χ     | Χ                 |

|                      | READ/READA | Illegal                                         | L         | Н   | L   | Н  | V   | V     | $V^{(18)}$        |

|                      | WRIT/WRITA | Illegal                                         | L         | Н   | L   | L  | V   | V     | $V^{(18)}$        |

|                      | ACT        | Illegal                                         | L         | L   | Н   | Н  | V   | V     | V <sup>(18)</sup> |

|                      | PRE/PALL   | Illegal                                         | L         | L   | Н   | L  | V   | V     | Χ                 |

|                      | REF/SELF   | Illegal                                         | L         | L   | L   | Н  | Χ   | Χ     | Χ                 |

|                      | MRS        | Illegal                                         | L         | L   | L   | L  | 0   | P COI | DE                |

- 1. H: HIGH level input, L: LOW level input, X: HIGH or LOW level input, V: Valid data input

- 2. All input signals are latched on the rising edge of the CLK signal.

- 3. Both banks must be placed in the inactive (idle) state in advance.

- 4. The state of the A0 to A11 pins is loaded into the mode register as an OP code.

- 5. The row address is generated automatically internally at this time. The I/O pin and the address pin data is ignored.

- 6. During a self-refresh operation, all pin data (states) other than CKE is ignored.

- 7. The selected bank must be placed in the inactive (idle) state in advance.

- 8. The selected bank must be placed in the active state in advance.

- 9. This command is valid only when the burst length set to full page.

- 10. This is possible depending on the state of the bank selected by the A11 pin.

- 11. Time to switch internal busses is required.

- 12. The IC42S16100 can be switched to power-down mode by dropping the CKE pin LOW when both banks in the idle state. Input pins other than CKE are ignored at this time.

- 13. The IC42S16100 can be switched to self-refresh mode by dropping the CKE pin LOW when both banks in the idle state. Input pins other than CKE are ignored at this time.

- 14. Possible if tRRD is satisfied.

- 15. Illegal if tras is not satisfied.

- 16. The conditions for burst interruption must be observed. Also note that the IC42S16100 will enter the precharged state immediately after the burst operation completes if auto-precharge is selected.

- 17. Command input becomes possible after the period tree has elapsed. Also note that the IC42S16100 will enter the precharged state immediately after the burst operation completes if auto-precharge is selected.

- 18. A8,A9 = don't care.

## CKE RELATED COMMAND TRUTH TABLE(1)

|                       |                                                                         | CI  | ΚE |    |     |     |    |     |      |       |

|-----------------------|-------------------------------------------------------------------------|-----|----|----|-----|-----|----|-----|------|-------|

| <b>Current State</b>  | Operation                                                               | n-1 | n  | CS | RAS | CAS | WE | A11 | A10  | A9-A0 |

| Self-Refresh          | Undefined                                                               | Н   | Х  | Х  | Χ   | Χ   | Х  | Χ   | Х    | Χ     |

|                       | Self-Refresh Recovery(2)                                                | L   | Н  | Н  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Self-Refresh Recovery(2)                                                | L   | Н  | L  | Н   | Н   | Χ  | Χ   | Χ    | Χ     |

|                       | Illegal <sup>(2)</sup>                                                  | L   | Н  | L  | Н   | L   | Χ  | Χ   | Χ    | Χ     |

|                       | Illegal <sup>(2)</sup>                                                  | L   | Н  | L  | L   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Self-Refresh                                                            | L   | L  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

| Self-Refresh Recovery | Idle State After tRC Has Elapsed                                        | Н   | Н  | Н  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Idle State After tRC Has Elapsed                                        | Н   | Н  | L  | Н   | Н   | Χ  | Χ   | Χ    | Χ     |

|                       | Illegal                                                                 | Н   | Н  | L  | Н   | L   | Χ  | Χ   | Χ    | Χ     |

|                       | Illegal                                                                 | Н   | Н  | L  | L   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Power-Down on the Next Cycle                                            | Н   | L  | Н  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Power-Down on the Next Cycle                                            | Н   | L  | L  | Н   | Н   | Χ  | Χ   | Χ    | Χ     |

|                       | Illegal                                                                 | Н   | L  | L  | Н   | L   | Χ  | Χ   | Χ    | Χ     |

|                       | Illegal                                                                 | Н   | L  | L  | L   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Clock Suspend Termination on the Next Cycle (2)                         | L   | Н  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Clock Suspend                                                           | L   | L  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

| Power-Down            | Undefined                                                               | Н   | Χ  | Х  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Power-Down Mode Termination, Idle After That Termination <sup>(2)</sup> | L   | Н  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Х     |

|                       | Power-Down Mode                                                         | L   | L  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

| Both Banks Idle       | No Operation                                                            | Н   | Н  | Н  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | See the Operation Command Table                                         | Н   | Н  | L  | Н   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Bank Active Or Precharge                                                | Н   | Н  | L  | L   | Н   | Χ  | Χ   | Χ    | Χ     |

|                       | Auto-Refresh                                                            | Н   | Н  | L  | L   | L   | Н  | Χ   | Χ    | Χ     |

|                       | Mode Register Set                                                       | Н   | Н  | L  | L   | L   | L  | С   | P CO | DE    |

|                       | See the Operation Command Table                                         | Н   | L  | Н  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | See the Operation Command Table                                         | Н   | L  | L  | Н   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | See the Operation Command Table                                         | Н   | L  | L  | L   | Н   | Χ  | Χ   | Χ    | Χ     |

|                       | Self-Refresh <sup>(3)</sup>                                             | Н   | L  | L  | L   | L   | Н  | Χ   | Χ    | Χ     |

|                       | See the Operation Command Table                                         | Н   | L  | L  | L   | L   | L  | С   | P CO | DE    |

|                       | Power-Down Mode <sup>(3)</sup>                                          | L   | Χ  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

| Other States          | See the Operation Command Table                                         | Н   | Н  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Clock Suspend on the Next Cycle <sup>(4)</sup>                          | Н   | L  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Clock Suspend Termination on the Next Cycle                             | L   | Н  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

|                       | Clock Suspend Termination on the Next Cycle                             | L   | L  | Χ  | Χ   | Χ   | Χ  | Χ   | Χ    | Χ     |

- H: HIGH level input, L: LOW level input, X: HIGH or LOW level input

The CLK pin and the other input are reactivated asynchronously by the transition of the CKE level from LOW to HIGH. The minimum setup time (tcka) required before all commands other than mode termination must be satisfied.

- Both banks must be set to the inactive (idle) state in advance to switch to power-down mode or self-refresh mode.

- The input must be command defined in the operation command table.

# TWO BANKS OPERATION COMMAND TRUTH TABLE(1,2)

| Operation  | cs | RAS | CAS | WE | A11 | A10  | A9-A0             |         | us State<br>BANK 1 | Next S<br>BANK 0 |         |

|------------|----|-----|-----|----|-----|------|-------------------|---------|--------------------|------------------|---------|

| DESL       | Н  | Х   | Х   | Χ  | Χ   | Χ    | Χ                 | Any     | Any                | Any              | Any     |

| NOP        | L  | Н   | Н   | Н  | Х   | Х    | Χ                 | Any     | Any                | Any              | Any     |

| BST        | L  | Н   | Н   | L  | Χ   | Χ    | Χ                 | R/W/A   | I/A                | Α                | I/A     |

|            |    |     |     |    |     |      |                   | I       | I/A                | 1                | I/A     |

|            |    |     |     |    |     |      |                   | I/A     | R/W/A              | I/A              | Α       |

|            |    |     |     |    |     |      |                   | I/A     | l                  | I/A              | I       |

| READ/READA | L  | Н   | L   | Н  | Н   | Н    | CA <sup>(3)</sup> | I/A     | R/W/A              | I/A              | RP      |

|            |    |     |     |    | Н   | Н    | CA <sup>(3)</sup> | R/W     | Α                  | Α                | RP      |

|            |    |     |     |    | Н   | L    | CA <sup>(3)</sup> | I/A     | R/W/A              | I/A              | R       |

|            |    |     |     |    | Н   | L    | CA <sup>(3)</sup> | R/W     | Α                  | Α                | R       |

|            |    |     |     |    | L   | Н    | CA <sup>(3)</sup> | R/W/A   | I/A                | RP               | I/A     |

|            |    |     |     |    | L   | Н    | CA <sup>(3)</sup> | Α       | R/W                | RP               | Α       |

|            |    |     |     |    | L   | L    | CA <sup>(3)</sup> | R/W/A   | I/A                | R                | I/A     |

|            |    |     |     |    | L   | L    | CA <sup>(3)</sup> | Α       | R/W                | R                | Α       |

| WRIT/WRITA | L  | Н   | L   | L  | Н   | Н    | CA <sup>(3)</sup> | I/A     | R/W/A              | I/A              | WP      |

|            |    |     |     |    | Н   | Н    | CA <sup>(3)</sup> | R/W     | Α                  | Α                | WP      |

|            |    |     |     |    | Н   | L    | CA <sup>(3)</sup> | I/A     | R/W/A              | I/A              | W       |

|            |    |     |     |    | Н   | L    | CA <sup>(3)</sup> | R/W     | Α                  | Α                | W       |

|            |    |     |     |    | L   | Н    | CA <sup>(3)</sup> | R/W/A   | I/A                | WP               | I/A     |

|            |    |     |     |    | L   | Н    | CA <sup>(3)</sup> | Α       | R/W                | WP               | Α       |

|            |    |     |     |    | L   | L    | CA <sup>(3)</sup> | R/W/A   | I/A                | W                | I/A     |

|            |    |     |     |    | L   | L    | CA <sup>(3)</sup> | Α       | R/W                | W                | Α       |

| ACT        | L  | L   | Н   | Н  | Н   | RA   | RA                | Any     | ı                  | Any              | Α       |

|            |    |     |     |    | L   | RA   | RA                | ľ       | Any                | A                | Any     |

| PRE/PALL   | L  | L   | Н   | L  | Х   | Н    | Χ                 | R/W/A/I | I/A                | I                | I       |

|            |    |     |     |    | Χ   | Н    | Χ                 | I/A     | R/W/A/I            | 1                | 1       |

|            |    |     |     |    | Н   | L    | Χ                 | I/A     | R/W/A/I            | I/A              | 1       |

|            |    |     |     |    | Н   | L    | X                 | R/W/A/I | I/A                | R/W/A/I          | 1       |

|            |    |     |     |    | L   | L    | X                 | R/W/A/I | I/A                | l                | I/A     |

|            |    |     |     |    | L   | L    | Χ                 | I/A     | R/W/A/I            | l                | R/W/A/I |

| REF        | L  | L   | L   | Н  | Х   | Χ    | Χ                 |         | l                  | l                |         |

| MRS        | L  | L   | L   | L  | C   | PCOE | DΕ                | 1       |                    |                  | 1       |

- 1. H: HIGH level input, L: LOW level input, X: HIGH or LOW level input, RA: Row Address, CA: Column Address

- 2. The device state symbols are interpreted as follows:

- I Idle (inactive state)

- A Row Active State

- R Read

- W Write

- RP Read With Auto-Precharge

- WP Write With Auto-Precharge

- Any Any State

- 3. CA: A8,A9 = don't care.

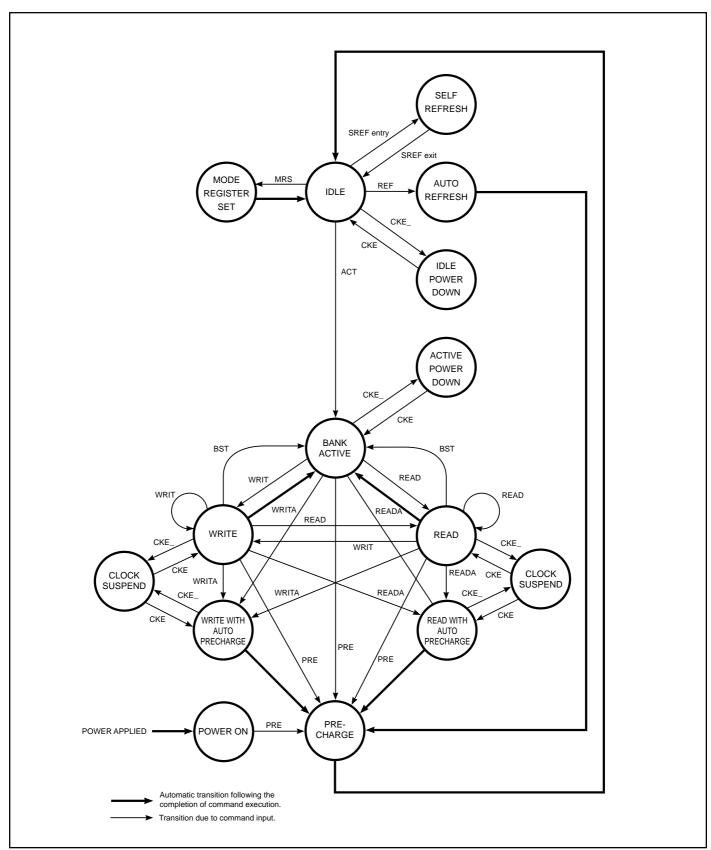

# SIMPLIFIED STATE TRANSITION DIAGRAM (One Bank Operation)

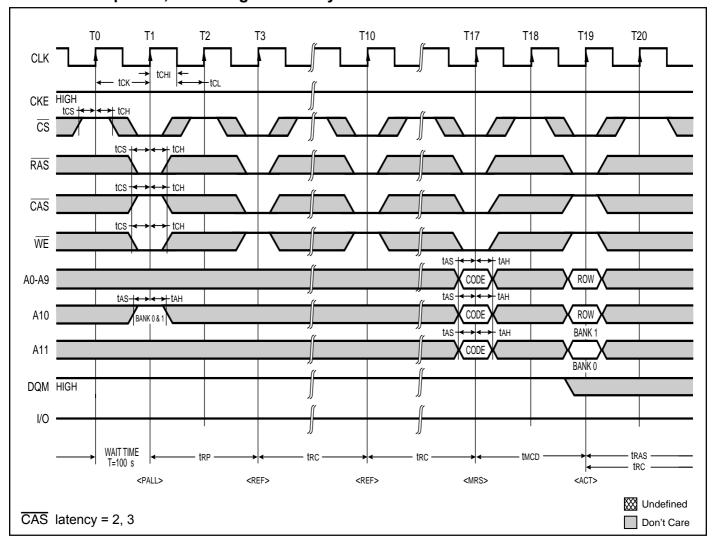

#### **Device Initialization At Power-On**

(Power-On Sequence)

As is the case with conventional DRAMs, the IC42S16100 product must be initialized by executing a stipulated power-on sequence after power is applied.

After power is applied and Vcc and VccQ reach their stipulated voltages, set and hold the CKE and DQM pins HIGH for 100  $\mu$ s. Then, execute the precharge command to precharge both bank. Next, execute the auto-refresh command twice or more and define the device operation mode by executing a mode register set command.

The mode register set command can be also set before auto-refresh command.

#### **Mode Register Settings**

The mode register set command sets the mode register. When this command is executed, pins A0 to A9, A10, and A11 function as data input pins for setting the register, and this data becomes the device internal OP code. This OP code has four fields as listed in the table below.

| Input Pin        | Field        |  |

|------------------|--------------|--|

| A11, A10, A9, A8 | Mode Options |  |

| A6, A5, A4       | CAS Latency  |  |

| A3               | Burst Type   |  |

| A2, A1, A0       | Burst Length |  |

Note that the mode register set command can be executed only when both banks are in the idle (inactive) state. Wait at least two cycles after executing a mode register set command before executing the next command.

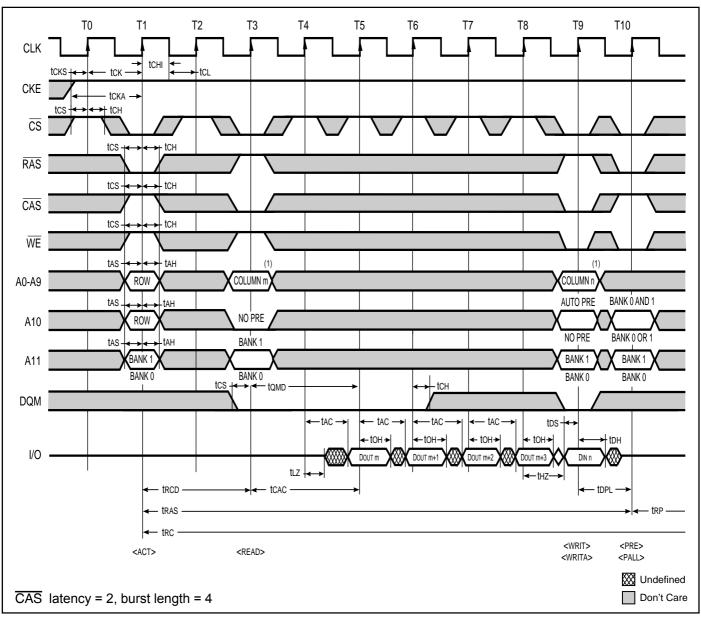

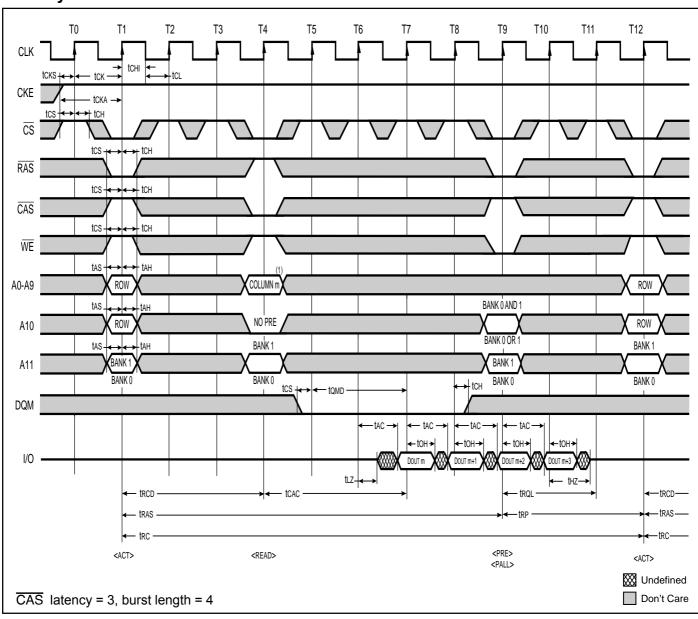

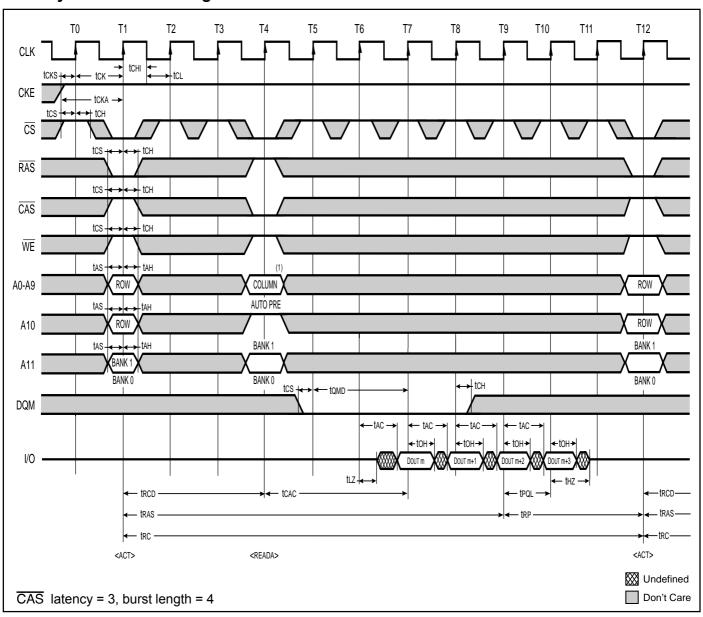

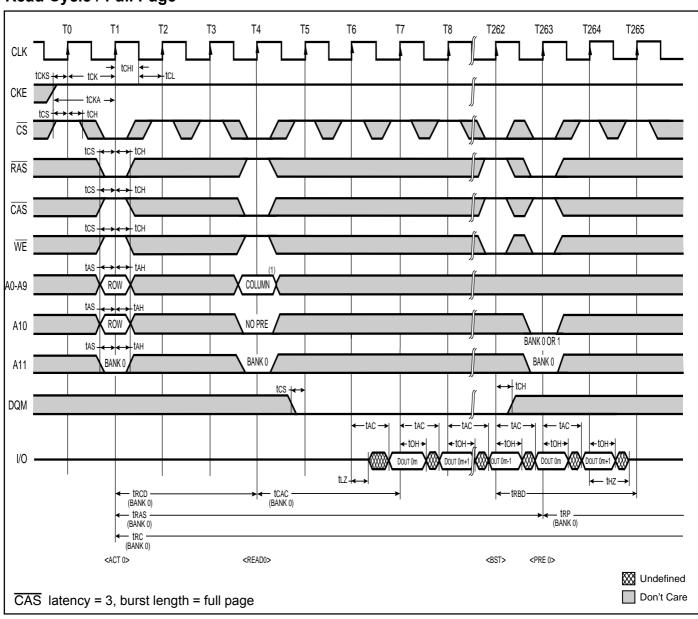

# **CAS** Latency