# Am79C401

# Advanced Micro Devices

# Integrated Data Protocol Controller (IDPC)

# **DISTINCTIVE CHARACTERISTICS**

#### **Data Link Controller**

- Full-featured bit-oriented communication controller supporting HDLC, SDLC, LAPB, LAPD, and DMI

- Data transfer rate: 2.048 Mb/s

- 32-byte receive FIFO and 16-byte transmit FIFO with programmable thresholds and DMA handshakes

- Multiple (four plus broadcast) address recognition modes

- Multiplexed serial interface with up to 31 8-bit channels or non-multiplexed serial interface

- Local and Remote Loopback Modes

- Transparent (Protocol-Free) Mode

- 56 kb/s Mode

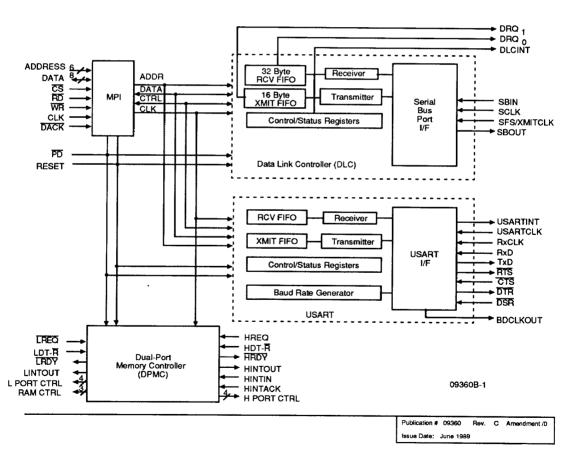

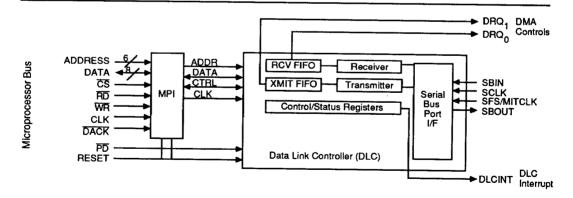

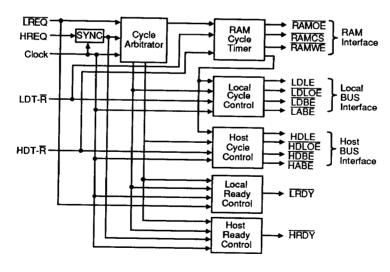

### **BLOCK DIAGRAM**

1-71

# **DISTINCTIVE CHARACTERISTICS (continued)**

#### **USART**

- Superset of Industry-Standard 8250 UART features

- Four-byte transmit/receive FIFOs

- Special character recognition (up to 128 programmable)

- Synchronous mode provides a transparent serial data path

- Local Loopback mode

#### **Dual-Port Memory Controller**

Memory bus arbitrator provides dual-port access to standard low-cost static RAM  Programmable inter-processor interrupts support RAM-based inter-processor mailboxes

### Microprocessor Interface

- 8-bit non-multiplexed data bus

- Operates with 12.5 MHz 80188 processor with zero wait states

#### **General Features**

- Compatible with Am79C30A DSC and Am79C32A IDC

- CMOS technology, single +5 V supply

- Power-down mode

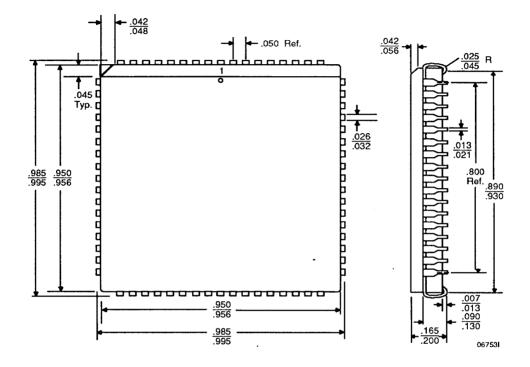

- 68-pin PLCC

### **GENERAL DESCRIPTION**

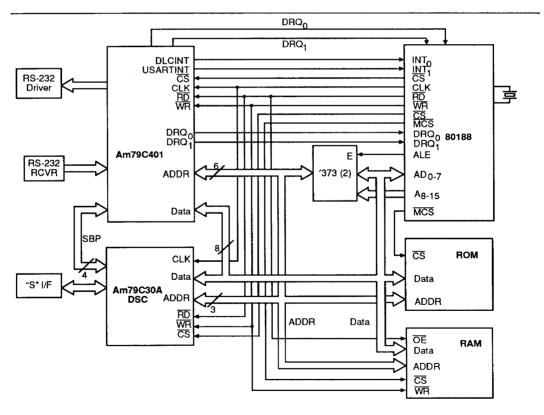

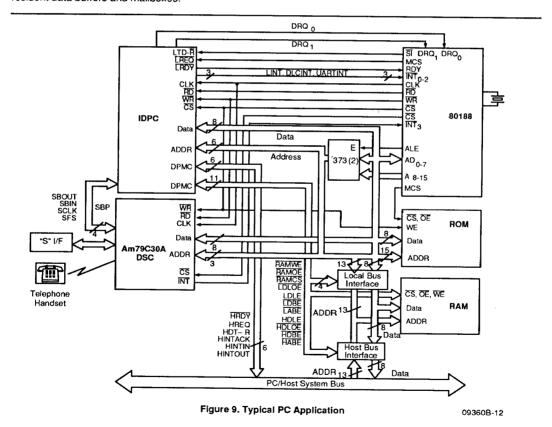

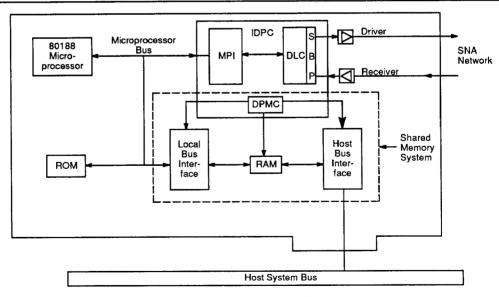

The Am79C401 Integrated Data Protocol Controller (IDPC) and companion software product, the Am79LLD401 IDPC Low-Level Driver (LLD), provide the essential building blocks for construction of a variety of communications systems. When combined with ROM, RAM, a microprocessor, and the physical layer transceiver, a complete ISDN, X.25, SNA, or similar system can be constructed. The IDPC is design-compatible with existing AMD communication components such as the Am79C30A Digital Subscriber Controller (DSC) and Am79C32A ISDN Data Controller (IDC) and off-the-shelf microprocessors such as the 80188.

The IDPC contains hardware and software support features for use in a single-processor environment (such as a terminal adapter for an ISDN network) or a multi-processor application (such as a communication interface for a PC or integrated voice/data work station application). For multi-processor applications, the IDPC controls access to an external "shared" static RAM by arbitrating simultaneous shared memory requests and supports an interprocessor interrupt scheme.

A companion software product, the Am79LLD401 IDPC LLD, provides isolation of the various hardware functions from the higher levels of packet protocol software. The LLD can be used with any bit-oriented protocol, including AmLink™, which is AMD's LAPD/LAPB implementation. Additionally, AMD's AmLink3™ package offers a complete implementation of the X.25 Packet Layer (Layer 3) protocol.

For ISDN D-channel applications, a similar function is provided by the Am79C30A DSC and Am79LLD30A LLD software.

The interfaces presented by the Am79LLD30A DSC LLD and the Am79LLD401 IDPC LLD use the same primitives so that both the D-channel and the B-channel can use the same layer-2 software. Both LLDs provide a hardware-independent interface to upper-layer protocols such as AmLink LAPD.

Functionally, the IDPC consists of four sections: a Data Link Controller (DLC), a Universal Synchronous/Asynchronous Receiver/Transmitter (USART), a Dual-Port Memory Controller (DPMC), and a Microprocessor Interface (MPI).

### Data Link Controller (DLC)

The DLC shown in the Block Diagram is a high-speed, bit-oriented protocol processor that supports either multiplexed or non-multiplexed data rates up to 2.048 Mb/s.

The DLC provides full-duplex (simultaneous transmit and receive) data transfer between the chip's Serial Bus Port (SBP) and internal parallel bus. Through the use of a 32-byte receive FIFO, a 16-byte transmit FIFO, and two external DMA channels, the DLC provides efficient movement of data to and from external memory and the SBP (network interface).

The DLC supports data transfers via DMA, interrupts, or polled I/O. The use of the FIFO buffers minimizes interrupt latency and frequency of interrupts.

The DLC has several programmable modes of operation which include:

- Non-multiplexed mode

- Multiplexed mode

- Local/Remote Test modes

- Transparent (Protocol-Free) Mode

- 56 kb/s Mode

### Non-multiplexed Mode

In non-multiplexed mode, the DLC functions as a conventional serial communications controller capable of supporting full-duplex data transfers at rates up to 2.048 Mb/s. This mode is useful in non-ISDN applications such as Local Area Networks, personal computer networks, Host-to-Host or terminal-to-Host applications.

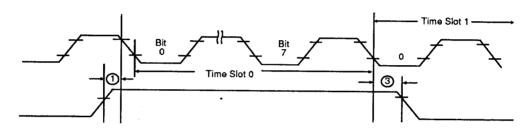

### **Multiplexed Mode**

In multiplexed mode, the DLC's SBP interfaces cleanly with the SBP on the Am79C30A DSC or the Am79C32A IDC, and provides access to 31 64 kb/s time slots.

# Local/Remote Loopback Test Modes

The DLC can be placed in either local or remote loopback mode under software control. In local loopback, the transmitter output is tied back to the receiver input. In remote loopback, the receiver input from the network is transmitted back to the network for system test purposes.

### **Transparent Mode**

In Transparent Mode, the DLC receives and transmits data without performing any HDLC protocol processing, creating a clear path between the SBP and the transmit and receive FIFOs. This mode can be used in either multiplexed or non-multiplexed modes.

#### 56 kb/s Mode

In 56 kb/s Mode, the DLC transmits and receives data at a 56 kb/s data rate. In this mode, the DLC sends data within an 8-bit time slot period, and always pulls the SBOUT pin High during the transmit time period of the eighth bit. Similarly, during data reception, the DLC shifts in 7 bits during the programmed time slot, but always waits until eight bits have been accumulated before transferring the data to the receive FIFO.

# Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The IDPC contains a USART for exchanging data between RS232 type terminals and the ISDN network in applications where there is no host processor. The USART provides a superset of 8250 UART features and supports both synchronous and asynchronous serial communications. The USART is capable of full-duplex operation at speeds up to 64 kb/s.

The USART supports the following functions:

- Programmable synchronous/asynchronous modes

- Software reset

- Line break recognition and generation

- Special character recognition

- Selectable stop bits (1-, 1.5-, or 2-stop bits)

- Modem control handshake lines (RTS, CTS, DSR, and DTR)

- Local loopback and "stick parity" test features

The USART receiver can detect up to 128 user-identified special characters. As each character is received, it is tested. If it is identified as a special character, a maskable interrupt can be generated.

The USART includes an internal Baud Rate Generator (BRG) that provides a clock for the transmitter and receiver sections (and to the external pin BDCLKOUT). The Baud Rate Generator's data rate is programmed by loading two "divisor latches" under software control.

# **Dual-Port Memory Controller (DPMC)**

The DPMC provides access control and an inter-processor interrupt mechanism that permits two processors to share static RAM memory without the expense of dual-port RAM. These features are necessary in developing network interface applications for PCs and Integrated Voice/Data Workstations (IVDWs).

In a typical multi-processor application, a local processor (such as the 80188) exchanges data with the host processor in the PC or IVDW using shared memory. The DPMC performs RAM access arbitration between the local and host processors, allowing the static RAM to appear as a dual-port memory to each processor.

The local processor can access any device on the IDPC local bus. The host processor can only access the RAM on the IDPC local bus. Any contention between the local processor and the host processor is arbitrated by the DPMC on the IDPC. Both processors communicate via memory-resident data buffers and mailboxes. An interprocessor interrupt scheme notifies the other processor when one of the processors has written data to a buffer or a command to a mailbox.

# Microprocessor Interface (MPI)

The MPI consists of an 8-bit non-multiplexed data bus that allows the IDPC to function with a 12.5-MHz 80188 processor (or other similar microprocessor) with zero wait-states.

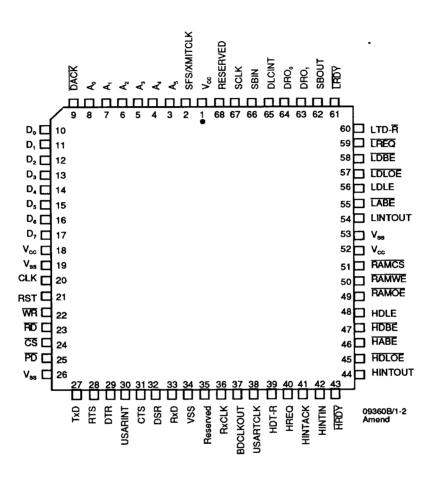

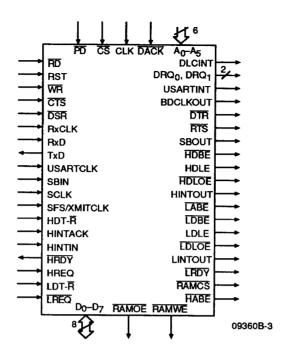

Note: Pin 1 is marked for orientation.

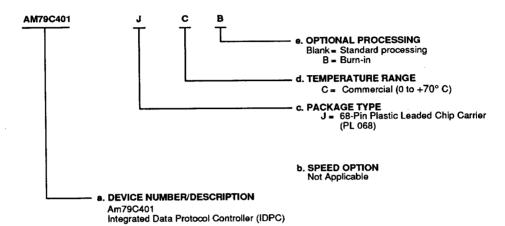

### ORDERING INFORMATION

# Standard Products

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of:

a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Combinations |         |  |  |  |  |  |

|--------------------|---------|--|--|--|--|--|

| AM79C401           | JC, JCB |  |  |  |  |  |

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

# PIN DESCRIPTION

The interface pins of the 68-pin IDPC chip can be classified into six major groups:

| Processor Bus Interface   | (25 pins) |

|---------------------------|-----------|

| USART Interface           | (9 pins)  |

| Serial Bus Port Interface | (4 pins)  |

| Bus Arbitration Control   | (21 pins) |

| Power/Ground              | (7 pins)  |

| No Connects (Reserved)    | (2 nins)  |

Unless otherwise specified, all input pins are TTL compatible.

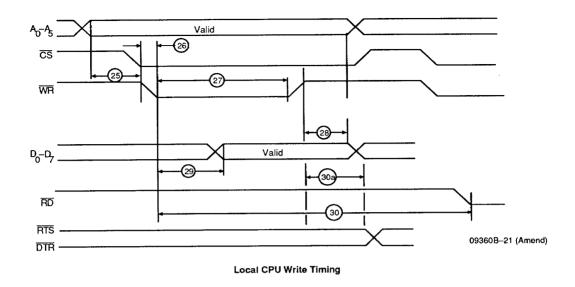

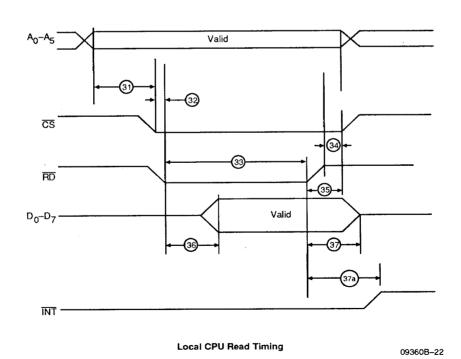

#### **Processor Bus Interface**

### A5-A0 Address Lines (Input)

These six address lines are generated by the external processor to select internal registers of the IDPC, and are valid only when  $\overline{CS}$  is active Low.

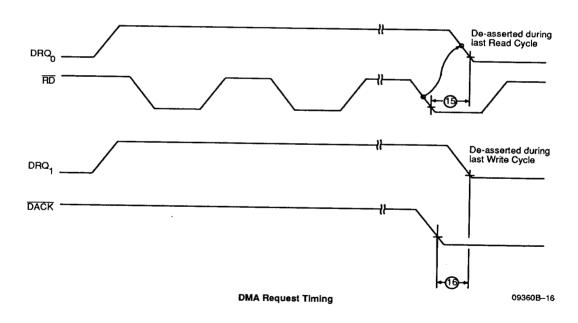

# DACK DMA Acknowledge (Input; Active Low)

The DACK signal is an indication that the DMA Controller is executing a DMA cycle to the DLC transmit FIFO. This indication occurs early in the DMA cycle, allowing the transmit FIFO to deactivate the DRQ1 signal when the last data transfer takes place (before an unwanted DMA cycle is initiated). An equivalent signal is not required for the DLC receive FIFO operation.

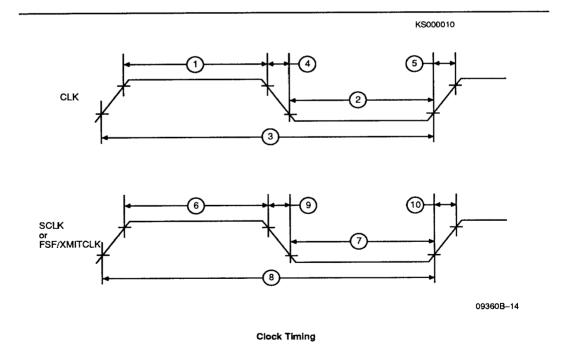

### CLK Master Clock (Input)

The Master Clock is an input that provides synchronization and timing for internal IDPC logic functions. CLK is normally the same clock used by the CPU.

# CS Chip Select (Input; Active Low)

CS is an input that indicates the IDPC has been selected for a read or write cycle.

#### D7-D0 Data Lines (Input/Output; Three State)

D7–D0 are bidirectional data lines used to transfer data between the local processor and the IDPC. The direction of the data transfer is controlled by the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  control lines. When  $\overline{\text{CS}}$  is inactive High, the data lines remain in a high-impedance state.

# DLCINT DLC Interrupt (Output; Active High)

DLCINT goes active High when the IDPC's DLC sets a status bit and the associated interrupt enable bit is set, and remains active until all pending DLC interrupts are cleared.

# DRQo Receive DMA Request (Output; Active High)

DRQo is an output signal used by the DLC's receive FIFO to begin a DMA cycle for received data.

DRQo goes active High under the following conditions:

- when number of bytes transferred into the receive FIFO equals the number specified in the DLC FIFO Threshold Register, or

- when an "end of packet" byte is loaded into the receive FIFO.

DRQo is deactivated Low under the following conditions:

- 1) Reset

- 2) when the receive FIFO becomes empty, or

- when the last byte of a packet is transferred from the receive FIFO to external memory.

# DRQ<sub>1</sub> Transmit DMA Request (Output; Active High)

DRQ<sub>1</sub> is an output signal used by the DLC's transmit FIFO to request the start of a DMA cycle for the transmit data.

DRQ<sub>1</sub> goes active High when ALL of the following conditions are met:

- 1) the transmit byte count is not equal to zero.

- last byte of the packet has not been loaded into the transmit FIFO, and

- number of bytes in the FIFO is equal to or less than the value programmed in the transmit FIFO Threshold.

DRQ<sub>1</sub> is deactivated Low under the following conditions:

- 1) Reset,

- 2) when the transmit FIFO is full, or

- when the last byte of the packet is loaded into the transmit FIFO.

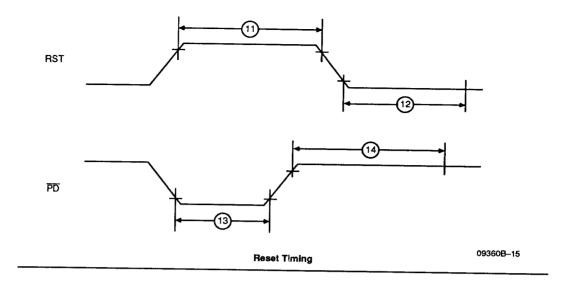

# PD Power Down (Input; Active Low)

This signal disables all internal clocks and places all three-state signals in a high-impedance state. HRDY and LRDY are disabled and all interrupt outputs are deactivated. Status and data will be lost but programming is retained. PD should be held active for a period of 8 MCLK cycles.

# RD Read (Input; Active Low)

This input is used by the IDPC to indicate when data from the IDPC is being requested.

RD is qualified internally with an active Low CS.

### RST Reset (Input; Active High)

This input forces all functions to terminate and places the IDPC in a default state.  $\overline{HRDY}$  and  $\overline{LRDY}$  are disabled and all three-state outputs are placed in a high-impedance state. RST should be held active for a period of 8 MCLK cycles.

**USARTINT USART Interrupt (Output; Active High)**USARTINT goes active High when the IDPC's USART sets a status bit and the associated interrupt enable bit is

Am79C401 1-77

active, and remains active until all pending USART interrupts are cleared.

# WR Write (Input; Active Low)

WR is used by the IDPC to latch incoming data (D<sub>7</sub>–D<sub>0</sub>) during a write cycle.

WR is qualified internally with an active Low CS.

#### **USART Interface**

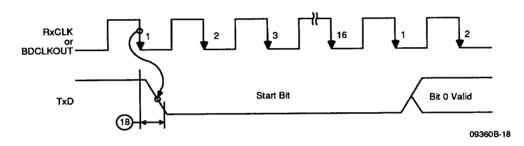

# BDCLKOUT Baud Rate Generator Clock Out (Output)

This signal is the output of the USART's Baud Rate Generator, and can be used as a common clocking source for a modern or other similar device.

# CTS Clear To Send (Input; Active Low)

Activity on CTS generates a maskable interrupt, but does not directly control the USART's transmitter.

# DSR Data Set Ready (Input; Active Low)

Activity on DSR generates a maskable interrupt, but does not directly control the USART's transmitter or receiver.

# DTR Data Terminal Ready (Output; Active Low)

DTR is user-controlled and does not directly control the USART's transmitter or receiver.

### RTS Request To Send (Output; Active Low)

RTS is user-controlled and does not directly control the USART's transmitter.

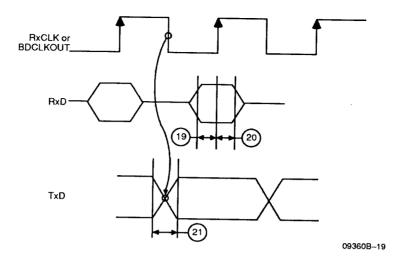

#### RxCLK Receive Clock (input)

RxCLK is an input to the USART and is used in synchronous and asynchronous operation. In asynchronous mode, the RxCLK should be 16 times the data rate. In synchronous mode, RxCLK is synchronized to the incoming data, and the rising edge is used to latch data on the RxD pin. The maximum data rate supported is 64 kb/s.

#### RxD Receive Data (Input; Active High)

RxD is an input to the USART. Data on this pin is clocked into the IDPC on the rising edge of the selected clock source.

#### TxD Transmit Data (Output; Active High)

TxD is an output of the USART. Data is clocked out of the IDPC on the falling edge of the selected clock source.

### **USARTCLK USART Clock (Input)**

This pin is the clock input for the USART's Baud Rate Generator. The frequency of this clock source must be an integer multiple of the desired baud rate (output of the Baud Rate Generator is the same as the data rate for synchronous operation and 16 times the data rate for asynchronous operation). If the Baud Rate Generator is programmed to divide by one, USARTCLK operates as a

direct input to the USART. When the IDPC is used in conjunction with the Am79C30 (DSC), the 12.288-MHz clock output can be used as the USART clock source. The maximum data rate supported is 64 kb/s.

### Serial Bus Port Interface

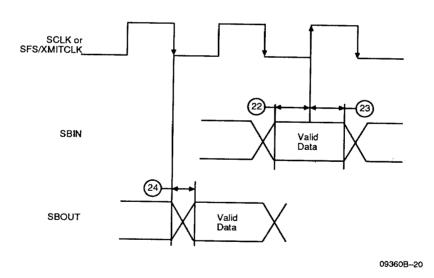

# SBIN Serial Data in (Input)

SBIN is the serial data input to the IDPC's DLC. Data is clocked into the DLC, LSB (bit 0) first, on the rising edge of SCLK. The maximum data rate supported is ½ of clock supplied via the CLK pin. This data rate, however, should not exceed 2.048 Mb/s.

In applications where an Am79C30A (DSC) is used, SBIN can be tied to the SBOUT pin of the DSC directly.

# SBOUT Serial Data Out (Output; Open Drain)

SBOUT is the serial data output of the IDPC's DLC. Data is clocked out, LSB (bit 0) first, on the falling edge of either SCLK or SFS/XMITCLK. SBOUT data rate may range from 0 to 2.048 Mb/s. In applications where an Am79C30A (DSC) is used, SBOUT of the IPDC is tied to SBIN of the DSC with a pullup resistor.

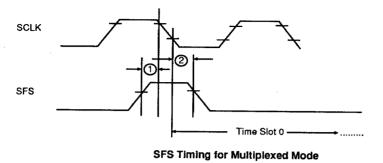

#### SCLK Serial Clock In (Input)

SCLK is used as the clocking source for the DLC.

In multiplexed mode, SCLK supplies both the transmit and receive clocks synchronized to SFS/XMITCLK. In non-multiplexed mode, SCLK is used as the receive clock and is not synchronized to SFS/XMITCLK. The rising edge of SCLK is used to latch data on SBIN and the falling edge is used to shift data out on SBOUT in multiplexed mode. The maximum data rate supported is 1/5 of clock supplied via the CLK pin. This data rate, however, should not exceed 2.048 Mb/s.

# SFS/XMITCLK Serial Frame Sync/Transmit Clock (Input)

This input clock signal has two different functions depending on the mode of operation selected by bits 4–0 in the DLC SBP Control Register. In multiplexed mode, this input pin functions as SFS, the synchronization pulse used to indicate the first of up to 31 independent 8-bit time slots on SBIN and SBOUT.

In non-multiplexed mode, SFS/XMITCLK is used by the DLC as the input for an independent transmit clock. SFS/XMITCLK is used by the DLC to shift data out onto SBOUT, LSB (bit 0) first, on the falling edge. This clock operates from 0 to 2.048 MHz.

# **Bus Arbitration Control**

# HDBE Host Data Bus Enable (Output; Active Low)

HDBE is an active Low output used to enable the data bus lines from the host processor to the shared RAM data bus. HDBE is driven active as a result of HDT-R

1-78 Am79C401

being sampled High (write cycle) and remains High until the end of the memory cycle.

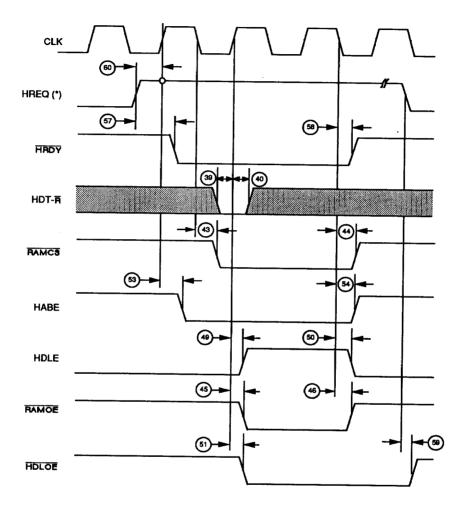

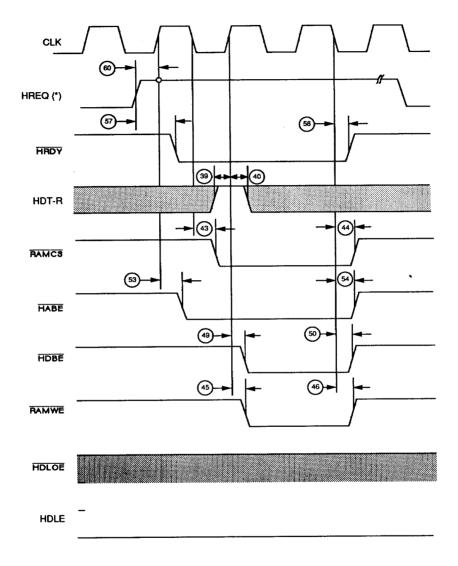

# HABE Host Address Bus Enable (Output; Active Low)

HABE is driven active Low by the IDPC as a result of receiving an HREQ from the host processor and is used to enable the address lines from the host processor and remains active until the end of the memory cycle.

# HDLE Host Data Latch Enable (Output; Active High)

This active High output is used to latch data from shared RAM to the host processor. HDLE is driven High as a result of HDT- $\overline{A}$  being sampled Low. HDLE returns Low at the end of the memory cycle.

# HDLOE Host Data Latch Output Enable (Output; Active Low)

This active Low output is used by the host processor to enable the output of the data bus latches to the host processor. HDLOE is driven Low when HDT-R is sampled Low. It is deactivated when HREQ goes inactive Low.

# HDT-R Host Data Transmit-Receive (Input)

HDT- $\overline{R}$  indicates whether a read or write cycle takes place to shared memory from the host processor. When HDT- $\overline{R}$  is sampled High, it indicates that a shared RAM write cycle is in progress. As a result,  $\overline{RAMWE}$  and  $\overline{HDBE}$  are driven active Low.

When HDT-R is sampled Low, a shared RAM read cycle occurs and RAMOE and HDLOE are driven active Low, and HDLE is driven active High.

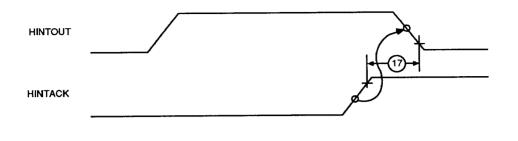

# HINTACK Host Interrupt Acknowledge (Input; Active High)

HINTACK is generated by the host processor in response to a Host Interrupt Out signal (HINTOUT) from the IDPC. HINTACK is used to clear bit 0 of the Semaphore Register, and deactivate the HINTOUT signal low

# HINTIN Host Interrupt In (Input; Active High)

This signal is used by the host processor to generate an interrupt to the local processor via the LINTOUT pin. When the host processor pulses this pin High, bit 1 of the Semaphore Register is set to '1' and LINTOUT is driven active High.

# HINTOUT Host Interrupt Out (Output; Active High)

HINTOUT is used to generate an interrupt to the host processor. This signal goes active High when the local processor sets bit 0 of the Semaphore Register to '1'. HINTOUT is deactivated Low by a pulse on the HINT-ACK pin or by Reset.

# HRDY Host Ready (Output; Active Low; Open Drain)

HRDY is an output from the IDPC used by the host processor to complete a shared RAM memory cycle. HRDY is normally High. It is pulled Low when a request for shared RAM is received from the host processor (HREQ) and is returned High at the end of the memory cycle, or by Reset.

# HREQ Host Processor Bus Request (Input; Active High)

The HREQ is a active High input to the IDPC from the host processor requesting access to the shared RAM. HREQ is sampled on the falling edge of every IDPC Master clock cycle. When sampled active, HREQ drives RAMCS and HABE active Low, and HRDY active Low. HREQ is an asynchronous input with respect to the IDPC's Master Clock and is synchronized internally.

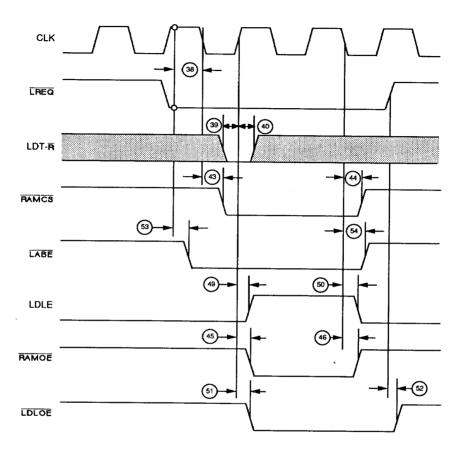

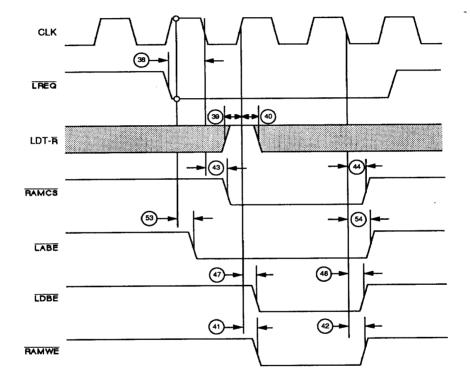

# LABE Local Address Bus Enable (Output; Active Low)

This signal is driven Low by the IDPC to enable the address lines from the local processor bus onto the shared memory bus when a Local Processor Bus Request (LREQ) is received from the local processor. LABE remains active Low until the end of the memory cycle.

# LDBE Local Data Bus Enable (Output; Active Low)

This signal is used to place the data from the local processor bus onto the shared RAM data bus. LDBE is driven active Low as a result of LDT-R being sampled High. LDBE remains Low until the end of a memory cycle.

# LDLE Local Data Latch Enable (Output; Active High)

This signal is driven High to latch data from shared RAM onto the local processor data bus. LDLE is driven High as a result of LDT-R being sampled Low, and is deactivated Low at the end of a memory cycle.

# LDLOE Local Data Latch Output Enable (Output; Active Low)

This signal is an active Low output from the IDPC that enables the output of the data bus latch onto the local processor. LDLOE is driven active Low when LDT-R is sampled Low, and is cleared when LREQ goes inactive High.

# LDT-R Local Data Transmit-Receive (Input)

LDT-R indicates whether a read or write cycle takes place to shared memory from the local processor. When this signal is sampled High, a shared RAM write cycle occurs. As a result, RAMWE and LDBE are driven active Low.

When LDT-R is sampled Low, a shared RAM read cycle occurs, RAMOE and LDLOE are driven active Low, and LDLE is driven active High.

# LINTOUT Local Interrupt Out (Output; Active High)

LINTOUT is driven active High when the HINTIN pin is pulsed high by the host processor, and goes Low when bit 1 in the Semaphore Register is cleared to "0" by software, or after a Reset.

# LRDY Local Ready (Output; Active Low; Open Drain)

LRDY is an active Low output from the IDPC used by the local processor to complete a shared RAM memory cycle. LRDY is normally High, and is driven Low when a request for shared RAM is received from the local processor (LREQ) and the host processor is currently accessing shared RAM.

# LREQ Local Processor Bus Request (Input; Active Low)

This active Low signal is an input to the IDPC from the local processor when it requests access to the shared RAM. LREQ is sampled on the falling edge of every IDPC Master Clock cycle.

LREQ must be synchronous to CLK.

# RAMCS RAM Chip Select (Output; Active Low)

This signal is an active Low output from the IDPC used by the shared RAM as its chip select. RAMCS is a driven Low when either LREQ or HREQ is sampled active. RAMCS remains active until the end of a memory cycle.

# RAMOE RAM Output Enable (Output; Active Low)

This signal is an active Low output signal from the IDPC used by the shared RAM to enable its output drivers. RAMOE is driven active Low when either LDT-R or HDT-R is sampled Low and is deactivated High at the end of the memory cycle.

# RAMWE RAM Write Enable (Output; Active Low)

This signal is an active Low output from the IDPC used by the shared RAM as a write strobe. RAMWE is driven Low when either LDT-R or HDT-R is sampled High and remains active until the end of a memory cycle.

#### Power/Ground

Vcc +5 V Power Supply

**Vss Ground**

1-80 Am79C401

# **FUNCTIONAL DESCRIPTION**

### **IDPC Block Diagram Description**

The IDPC contains three major functional modules which include:

- Data Link Controller (DLC)

- Universal Synchronous/Asynchronous Receiver/ Transmitter (USART)

- Dual-Port Memory Controller (DPMC)

# **Data Link Controller (DLC)**

The DLC consists of a transmitter, receiver, and of Control/Status registers (Figure 1).

#### **DLC Transmitter**

The transmitter resides between the IDPC's parallel bus and the serial communication network. The local processor builds a data block in memory containing the address, control, and information fields of an HDLC frame. This block of data is then moved into the transmit FIFO under either DMA or programmed I/O control.

The transmitter functions include: opening flag transmission, data transparency (via zero insertion), generation and transmission of the Frame Check Sequence (FCS) characters (if enabled), and transmission of the closing flag.

The transmitter may also be programmed to perform such functions as inverting the polarity of the data stream, transmitting an abort sequence, and transmitting an all "1s" pattern (Mark Idle) or back-to-back flags (Flag Idle) between packets.

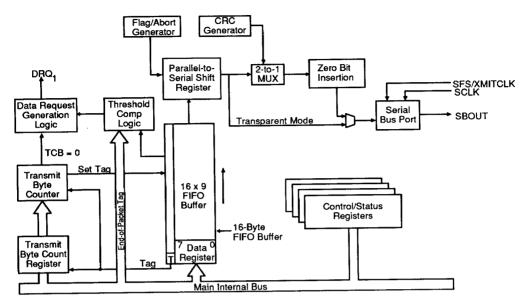

A block diagram of the DLC transmitter is shown in Figure 2.

Transmit FIFO—The transmit FIFO consists of a 16-byte FIFO buffer, transmit byte count register, trans-

mit byte counter, and DMA request logic. Data can be loaded into the transmit FIFO under programmed I/O or Direct Memory Access (DMA) control.

Data Register—The "user-addressable" portion of the FIFO is termed the data register. The transmit FIFO sets bit 3 (XMIT BUFFER AVAIL) in the FIFO Status Register to "1" to indicate when the Data Register is available. This bit is set any time the Data Register is empty, and is cleared when the Data Register is written to and the FIFO becomes full or the last byte of a packet is loaded into the FIFO.

Parallel-to-Serial Shift Register—The output of the transmit FIFO is loaded one byte at a time into the parallel-to-serial shift register then shifted out to the zero bit insertion logic before appearing at the SBOUT pin.

Flag and abort characters are loaded into the parallel-toserial shift register for transmission by the DLC when a flag or abort sequence is to be sent. During the transmission of a flag or abort sequence the zero bit insertion logic is disabled.

Bit Residue —The transmitter also has provisions for handling bit-residue. Bit-residue refers to the number of bits left over after the I (Information) field of a frame (excluding inserted zeros) is divided into 8-bit bytes. Protocols such as LAPD and SDLC specify that data be sent in 8-bit quantities. In HDLC, however, the information field can be any number of bits and not necessarily an integral number of 8-bit characters. On the IDPC a programmable 3-bit field is provided that specifies the number of valid data bits received or transmitted during the last byte of a frame. Transmitting packets with bit-residue I-fields requires that the user load a 3-bit register field (Residue Bit Status Control Register) with the number of residue

Figure 1. DLC Block Diagram

Am79C401

1-81

Figure 2. DLC Transmitter

09360B-5

bits in the packet (in the last byte of the I-field just prior to transmitting the FCS). When the last byte of the I-field is to be transmitted, the contents of the Residue Bit Status Control Register are used to determine when the FCS is actually sent.

**CRC Generator**—The Frame Check Sequence (FCS) is 16 bits long and contains the generated CRC code for the frame being transmitted. All data transmitted between the opening and closing flags (excluding inserted zeros) is included in the CRC calculation. The standard CCITT generator polynomial,  $X^{16} + X^{12} + X^5 + 1$ , is used.

Zero Bit Insertion—The zero bit insertion logic provides data transparency by ensuring that flag or abort characters embedded in the data is not recognized by the remote receiver as actual data link control characters. The zero bit insertion logic monitors the data stream between the opening and closing flags of a frame and inserts a "0" after detecting five contiguous "1"s.

Flag/Mark Idle Generation —The DLC transmitter may be programmed to either flag or mark idle when the transmitter is enabled and is not actively sending a data packet or an abort sequence.

Abort Generation —An abort sequence will be sent by the DLC transmitter whenever the Send Abort bit (bit 0 in

the DLC Command/Control Register) is set. The transmitter will continue sending an abort sequence as long as this bit is set; however, if the Send Abort bit is set and cleared on two successive writes to the DLC Command/Control Register at least one abort character will be sent.

Serial Bus Port—The Serial Bus Port (SBP) sits at the output of the transmitter and performs a number of functions related to time slot assignment, clock selection, data inversion, transmitter enable/disable, and loopback testing.

Time Slot Multiplexer: The time slot multiplexer operates in two modes: multiplexed and non-multiplexed. In the multiplexed mode, one of 31 time slots may be programmed to transmit data; in the non-multiplexed mode, the data is transmitted directly without multiplexing. In addition, time slots 0 and 1 can be concatenated in multiplexed mode into one 16-bit wide slot by holding the frame sync signal, SFS/XMIT, active through the first bit time of time slot 1.

Transmit Enable/Disable Logic: The transmit enable/ disable logic monitors bit 1 of the DLC Command/Control Register. When this bit is reset to "0," the SBOUT pin is set to a physical mark idle state (i.e., the SBOUT pin is pulled High). Note that if the transmitter is disabled or en-

abled during the programmed time slot (in multiplex mode), the disabling or enabling of the transmitter will occur at the end of the time slot.

Local Loopback Logic: The DLC can be placed in a local Loopback mode for test purposes by setting bit 6 in the SBP Control Register to "1." Local loopback disconnects the SBIN pin and connects the transmitter output to the receiver input. The selected transmit clock is used as the receive clock.

Remote Loopback Logic: The DLC can be placed in the remote loopback mode for diagnostic purposes by setting bit 7 of the SBP Control Register to "1." In remote loopback mode, the transmitter is disabled and data received at the SBIN pin is echoed out the SBOUT pin. The receiver operates normally in this mode.

Transparent Mode: In Transparent Mode, all HDLC protocol functions are bypassed. Data is transmitted exactly as it is loaded in the transmit FIFO. Transparent Mode is enabled when bit 7 of the DLC Residual Bit Status Control Register is set to "1." Two modes of operation are available in Transparent Mode using bit 6 of the DLC Residual Bit Status Control Register.

Transparent Mode 1—If bit 6 and bit 7 of the DLC Residual Bit Status Control Register are set to "1," the number of bytes to be sent, after the XMIT Enable bit in the DLC Command/Control Register is set to "1," is determined by the count programmed in the DLC Transmit Byte Count Register. When the number of bytes loaded into the transmit FIFO equals the programmed count further DMA requests are inhibited and, when the last bit of the last byte is transmitted, the XMIT Enable bit will be cleared to "0" and the Valid Packet Sent Status bit in the DLC Interrupt Source Register will be set to "1" to indicate that transmission has completed.

Transparent Mode 2—If bit 6 is set to "0" and bit 7 is set to "1" in the DLC Residual Bit Status Control Register, the number of bytes transmitted will be controlled by the XMIT Enable bit in the DLC Command/ Control Register and the DLC Transmit Byte Count Register will be ignored. In this mode of operation the DLC will start generating DMA requests and sends data for as long as the XMIT Enable bit is set to "1." When this bit is cleared to "0" further DMA requests are inhibited and, when the last bit of the last byte is transmitted, the Valid Packet Sent Status bit in the DLC Interrupt Source Register will be set to "1" to indicate that transmission has completed.

56 kb/s Mode: If bit 7 of the DLC Residual Bit Status Control Register is set to "1" and the DLC is programmed for multiplex operation, the DLC will transmit data at a 56 kb/s data rate instead of the normal 64 kb/s data rate. In this mode, the DLC will send data within an 8-bit time slot period, but will always disable the SBOUT pin High during the eighth bit time period.

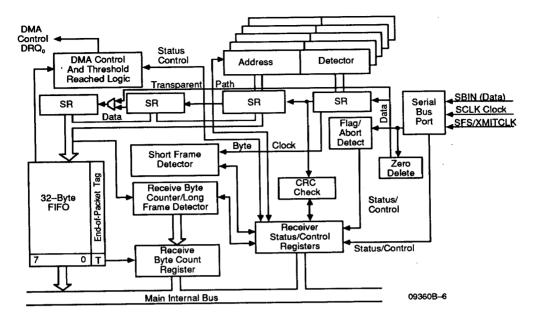

#### **DLC Receiver**

The receiver (shown in Figure 3) processes serial data packets from the SBP and transfers the data to a 32-byte receive FIFO, where it is transferred to "off-chip" RAM memory under DMA or processor control. Data rates from 0 to 2.048 Mb/s are allowed. The hardware can receive an entire packet and move the information to off-chip RAM without processor intervention if DMA is used in the design. Packet status information is then reported on a packet-by-packet basis at the time that the last byte of the packet has been moved to memory.

Dedicated hardware modules perform bit-level operations on each frame of data including mark-Idle and flag-Idle detection, data inversion, flag/abort recognition, zero bit deletion, CRC checking, and address recognition.

Functionally, the receiver consists of the following major circuits:

Serial Bus Port

Zero bit Deletion Unit

Short Frame Byte Counter

CRC Checker

Serial-to-Parallel Shift Register

Address Detection Unit

Receive FIFO

Receive Byte Counter

Serial Bus Port—The Serial Bus Port (SBP) receives serial data from the SBIN pin and sends it to the flag/abort detection unit and the zero bit deletion unit.

The SBP performs three operations on the incoming data:

- 1) Mark Idle Detection

- 2) Programmable data inversion

- 3) Time slot de-multiplexing

Zero Bit Deletion Unit—The zero bit deletion unit monitors the data stream between the opening and closing flags and removes a zero that appears after a string of five consecutive "1"s ("0"s are added during transmission to prevent a data pattern from resembling an abort, opening, or closing Flag).

Short Frame Byte Counter—The Short Frame Byte Counter is a 4-bit counter that counts the number of characters that have reached the serial-to-parallel shift register. If a frame ends in a flag, and the number of bytes received is less than the value programmed into the Minimum Packet Size Register, and data has been placed in the FIFO (Receive Byte Counter>0), the SHORT FRAME ERROR status bit in the Receive Frame Status Register will be set to "1" when the last byte of the packet is read from the receive FIFO. Note that packet status is reported to the user and interrupts are generated, when the last byte of the received packet is read by

Figure 3. DLC Receiver

the processor or placed in off-chip RAM by the DMA controller.

CRC Checker—The output of the flag/abort detection unit is shifted into the CRC Checker. When the closing flag is detected, the 16-bit Frame Check Sequence has just been shifted into the checker. At this point, the contents of the CRC Checker is examined. If an error is detected, the CRC ERROR status bit is set in the Receive Frame Status Register (bit 2) when the last byte of the packet is read from the receive FIFO. The FCS can optionally be placed in the receive FIFO by setting the ENABLE FCS PASS-THRU bit (bit 7) to "1" in the DLC Command/Control Register. If this bit is set to "0" the FCS is discarded by the DLC and is not available for use.

Serial-to-Parallel Shift Register—The output of the zero bit deletion unit is fed into a 32-bit shift register which converts the serial stream into bytes. The parallel output of the shift register is fed to the receive FIFO, one byte at a time.

Address Detection Unit—The address detection unit identifies packets that are addressed to the receiver. Depending on programming, the first, second, or both of the first two bytes of each received packet (after receipt of an opening flag) are compared with the contents of five address registers (four user-programmable registers and one broadcast). If address recognition is enabled and the incoming packet's address field matches one of the address registers, the packet is received; otherwise, the

packet is discarded and the receiver goes into a wait pattern looking for the next flag. As a programmable option, the Command/Response (C/R) bit (bit 1 of the first byte) can be ignored. If address recognition is disabled (i.e., bits 4–0 of the DLC Address Control Register are reset to "0"), all packets are accepted by the DLC.

Receive FIFO—The receive FIFO is a 32-byte buffer located between the serial-to-parallel shift register and the Microprocessor Interface (MPI). The FIFO is loaded by the shift register and unloaded by either the local processor or DMA controller. When the user-visible Data Register contains data, the RECV DATA AVAIL status bit in the DLC FIFO Status Register is set to "1" and a maskable interrupt is generated. This status bit is cleared to "0" when the byte is read from the Data Register and the receive FIFO becomes empty.

Receive FIFO Threshold Logic: This logic generates a receive FIFO Threshold Reached signal. This signal is High whenever the number of bytes in the receive FIFO are equal to or greater than the threshold level programmed into the FIFO Threshold Register (bits 7–4). This signal is used to set the RECV TRSHLD REACHD status bit to "1" in the DLC FIFO Status Register and generate a maskable interrupt. The Threshold Reached signal is also used to generate DRQo.

Data Movement Control: Data is moved from the receive FIFO either by DMA or Programmed I/O. The DRQo pin is the receive FIFO's Data Request output to

the off-chip DMA controller. DRQo is activated when the level in the FIFO reaches the programmed threshold, or the last byte of a packet is placed in the FIFO. Once activated, DRQo remains active until the FIFO becomes empty or the last byte of a packet is removed from the FIFO. DRQo will not be re-activated until the status of the previous packet has been read (by reading the least significant byte of the Receive Byte Count Register).

When programmed I/O is used, a maskable interrupt is generated when the programmed threshold is reached. The user removes data by reading the receive FIFO Data Register. If the last byte of a packet is placed in the FIFO, the end-of-packet Interrupt (maskable) indicates that the FIFO requires servicing. In this case, the user reads a data byte and then polls the RECV DATA AVAIL bit in the DLC FIFO Status Register. The user continues to remove data in this read-a-byte, poll RECV DATA AVAIL bit, read-a-byte fashion until the RECV DATA AVAIL bit is no longer set to "1." Since this procedure is in response to an end-of-packet Interrupt, the lack of a valid RECV DATA AVAIL bit indicates that the previously read data byte was the last in the packet and packet status should be read. The RECV DATA AVAIL bit de-activated by the receive is FIFO in response to the packet's last byte being removed. This happens even if the FIFO is not empty (for example, data from a new packet has been received). The RECV DATA AVAIL status bit will not be reactivated until the least significant byte of the Receive Byte Count Register is read (and additional data is in the FIFO).

Receive Byte Counter—The Receive Byte Counter keeps track of the number of current packet bytes transferred into the receive FIFO. When the last byte is removed from the FIFO, the contents of the counter are loaded into the Receive Byte Count Register.

The receive byte count is used to identify long frames and frames that have terminated prior to any data being placed in the buffer. Software uses the receive byte count to determine the length of a received frame.

Long Frame Error—A long frame error occurs when the closing flag of a frame is not detected before the number of received bytes equals the value programmed in the Maximum Packet Size Register. When this occurs, the byte that caused the long frame error is tagged as the last byte and the LONG FRAME ERROR status bit is set to "1" in the DLC Receive Frame Status Register.

Bit Residue—As data is shifted into the serial-to-parallel shift register, the bits in each byte are counted. When the counter reaches eight, a byte of data is transferred into the receive FIFO. If a closing flag is detected and this count does not equal eight the NON-INT#BYTES RECV status bit in the DLC Receive Frame Status Register will be set to "1" to indicate that a non-integer number of bytes has been received. When this occurs the 3-bit field (bits 2–0) in the DLC Residual Bit Status Control Register reports the number of data bits received at the time

the closing flag was detected. This register is a delayedreporting type register like the Receive Byte Count Register. The residue bits are right-justified before being placed in the receive FIFO.

Transparent Mode—In Transparent Mode, all receive HDLC functions (i.e., flag/abort detection, CRC checking, and zero bit deletion) are bypassed. Two modes of operation are provided through the use of bit 6 and bit 7 of the DLC Residual Bit Status Control Register. When the RECVER ENABLE bit in the DLC Command/Control Register is set to "1" data is loaded into the receive FIFO exactly as it is received. The FIFO operates normally. In addition, if bit 6 of the DLC Residual Bit Status Control Register is set to "1," the DLC Maximum Packet Receive Register is used to determine when the IDPC disables data reception.

Transparent Mode 1—If bit 6 and bit 7 of the DLC Residual Bit Status Control Register are set to "1," the number of bytes to be received, after the RECVER ENABLE bit in the DLC Command/Control Register is set to "1," is determined by the count programmed in the DLC Maximum Packet Receive Register. When the number of bytes loaded into the receive FIFO equals the programmed count further DMA requests are inhibited and, when the last byte is read from the FIFO, the VALID PACKET RECVD status bit in the DLC Interrupt Source Register is set to "1" to indicate that data reception is complete.

Transparent Mode 2—If bit 6 is reset to "0" and bit 7 is set to "1" in the DLC Residual Bit Status Control Register, the number of bytes received is controlled by the RECVER ENABLE bit in the DLC Command/Control Register. and the DLC Maximum Packet Receive Register is ignored. In this mode of operation, the DLC accumulates 8-bit characters and operates as in normal mode of operation as long as the RECVER ENABLE bit is set to "1." When this bit is reset to "0" further DMA requests are inhibited and, when the last byte is read from the FIFO, the VALID PACKET RECVD status bit in the DLC Interrupt Source Register will be set to "1" to indicate that data reception is complete.

56 kb/s Mode: If bit 7 of the DLC Residual Bit Status Control Register is set to "1" and the DLC is programmed for multiplexed operation, the DLC receives data at a 56 kb/s data rate instead of the normal 64 kb/s data rate. In this mode, the DLC receives 7 bits of data within an 8-bit time slot period, but always accumulates eight bits in the receive shift register before transferring it to the receive FIFO.

# Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The IDPC's USART provides a superset of the 8250 UART features and supports both synchronous and asynchronous serial communications. The USART is capable of full-duplex operation at speeds up to 64 kb/s us-

ing either the on-chip programmable Baud Rate Generator or external clock sources.

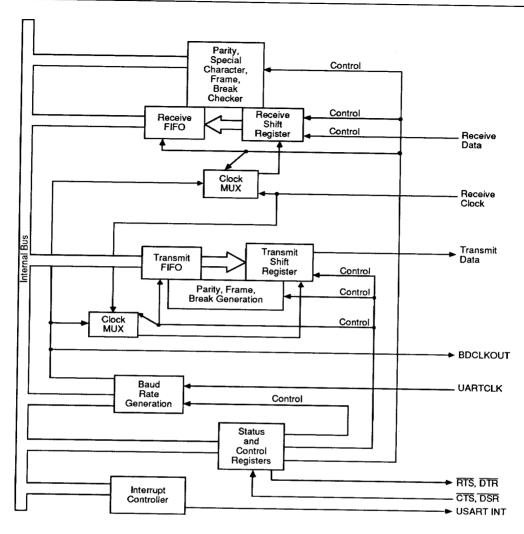

The USART consists of the following major circuits:

USART Receiver USART Transmitter Modem Control Unit Interrupt Controller Baud Rate Generator Clock Selector Unit

A simplified block diagram of the USART is shown in Figure 4.

#### **USART Receiver**

The receiver performs serial-to-parallel conversion, verifies framing, buffers the data in a FIFO, and detects break conditions, parity errors, and special characters. A maskable interrupt is generated if a parity error, framing error, or a break condition is detected. Data can be read out of the receive FIFO into external RAM memory under control of the external processor or DMA.

Parity Checking-If the ENABLE PARITY bit (bit 3) in the USART Line Control Register is set to "1," the parity generation/checking logic is enabled and parity is checked on all characters loaded into the receive FIFO. When the parity check bit generated by the receiver does not match the parity bit appended by the transmitter, the PARITY ERROR IN FIFO status bit in the USART Line Status Register is set to "1" and, if the RECV LINE STATUS bit in the USART Interrupt Enable Register is set to "1," an interrupt will be generated when that character is transfered to the receive FIFO. The CHAR w/ PARITY ERROR AVAIL status bit in the USART Status Register is then set to "1" when the character with the parity error reaches the output of the receive FIFO. No interrupt is generated by this bit. The selection of odd or even parity is made via bit 4 of the USART Line Control Register. Parity checking is available only in asynchronous mode.

Stick Parity—Stick parity is a test mode that forces the parity bit to be generated and detected as the logical inversion of the USART Line Control Register bit 4 when USART Line Control Register bits 5 and 3 are set. For example, if bits 5, 4, and 3 are set then the parity bit is always generated and detected as a "0." If bits 5 and 3 are set and bit 4 is cleared then the parity bit is always generated and detected as a "1."

Break Detection—Break Detection is performed in the asynchronous mode only. If the receive data input is held spacing ("0"s) for more than a full character time (start bit, data bits, parity bit, and stop bits), the USART sets the BREAK DETECT status bit (bit 4) in the USART Line Status Register to "1" and, if bit 2 in the USART Interrupt Enable Register, RECV LINE STATUS is set to "1" an interrupt is generated.

Framing Error Detection—Frame errors are detected in only the asynchronous mode. In this mode, if a received character does not have a valid stop bit and a Break condition is not present, the USART reports a framing error by setting bit 3 of the USART Line Status Register. If bit 2 in the USART Interrupt Enable Register, RECV LINE STATUS, is set to "1" an interrupt is generated.

Receive Shift Register—The receive shift register provides serial-to-parallel conversion for the serial data entering the Receive Data (RxD) pin.

Receive FIFO—The receive FIFO is a 4-byte, 10-bitwide buffer used for temporary storage of receive data from the receive shift register. The FIFO provides storage for 8 data bits, one special character flag, and one parity error flag. Parity and special character conditions are checked when data is loaded into the FIFO.

The presence of a character with either a special character or parity error flag is reported in the USART Line Status Register. Maskable interrupts are generated when an error condition is detected. Data is read out of the FIFO from the receive FIFO Data Register. Only the 8 data bits are accessible by the external processor or DMA controller.

While special character and parity error interrupts are generated when the character is loaded into the FIFO, the parity error present and special character available status bits (in the USART Line Status Register) are not set until the character is at the FIFO output. This allows the user to identify which character caused the interrupt.

The receive FIFO Data Register is the equivalent of the Receive Buffer Register in the 8250 UART. The presence of valid data in the receive FIFO Data Register is indicated by bit 0 (RECV DATA AVAIL bit) in the USART Line Status Register.

Receive Overrun Error Detection—If the receive FIFO is full when a newly received character is to be loaded into the FIFO, receive overrun error is reported via bit 1 (RECV BUFFER OVERUN) in the USART Line Status Register, and, if the RECV LINE STATUS bit in the USART Interrupt Enable Register is set to "1," an interrupt is generated.

Receive Character Length—If the USART Line Control Register is programmed to receive characters with fewer than 8 bits, the unused bit positions are filled with "0"s as the character is placed in the receive FIFO.

Receive FIFO Timeout—If the FIFO level is below the programmed threshold and no new characters are received within approximately 2048 receiver clocks, and, if the RECV FIFO TIMEOUT bit in the USART Interrupt Enable Register is set to "1," an interrupt is generated to in-

1-86 Am79C401

Figure 4. USART Simplified Block Diagram

09360B-7

dicate that data is available in the FIFO. This function is available only in the asynchronous mode.

Special Character Recognition Logic—Special character recognition is performed by using the lower order 7 bits of each received character as a pointer into a 128-bit RAM. If the addressed RAM bit has been programmed by the user to "1," the SPCHL CHAR IN FIFO status bit (bit 7) in the USART Line Status Register is set to "1," and, if the SPCHL CHAR bit (bit 5) in the USART Interrupt Enable Register is set to "1," an interrupt is generated. The SPCHL CHAR AVAIL status bit (bit 2) in the

USART Status Register is set when the special character reaches the output of the receive FIFO.

Synchronous Mode—The synchronous mode of operation is enabled when the SYNC/ASYNC SELECT bit (bit 2) in the USART Control Register is set to "1." In this mode of operation, the receiver clocks in data bits on each rising edge of the selected clock. Each 8 bits received are placed in the receive FIFO without regard for framing or breaks. This mode allows for transparent reception of a data stream, regardless of protocol.

### **USART Transmitter**

The USART Transmitter consists of the following major circuits:

Transmit FIFO

Parallel-to-Serial Shift Register

Frame, Break, and Parity Generation Logic

Transmit FIFO—The transmit FIFO serves as a buffer for data being moved from memory to the parallel-to-serial shift register. As the shift register becomes empty, the next character is moved from the FIFO to the parallel-to-serial shift register.

When the number of bytes in the transmit FIFO becomes less than or equal to the programmed transmit threshold level in the USART Control Register (bits 6 and 5), the XMIT TRSHLD REACHD status bit (bit 5) in the USART Line Status Register is set to "1," and , if the XMIT FIFO TRSHLD bit (bit 1) in the USART Interrupt Enable Register is set to "1," an interrupt is generated.

Bit 5 in the USART Line Status Register is the equivalent of the Transmitter Holding Register Empty in the 8250 UART.

Parallel-to-Serial Shift Register—The parallel-toserial shift register converts parallel data from the FIFO into serial form for transmission.

The shift register clock can come from either the Baud Rate Generator (BDCLKOUT) or from the RxCLK pin. The clock source for the shift register should be 16 times the data rate in asynchronous mode and the same as the data rate in synchronous mode. Bit 6 (XMIT SHIFT REG EMPTY) of the USART Line Status Register is set to "1" when the transmit FIFO is empty and the last bit of the transmit shift register has been shifted out. An interrupt is generated by this condition if the SHFTREG EMPTY bit (bit 6) in the USART Interrupt Enable Register is set to "1."

Frame, Break, and Parity Generation Logic—Frame generation takes place only in the asynchronous mode of operation. The number of stop bits and character length are programmed via the USART Line Control Register. The same parameters apply to the receiver. Even, odd, and no parity can be selected via the USART Line Control Register.

Break Generation—The USART will generate a break condition (all "0"s) when bit 6 (BREAK) in the USART Line Control Register is set to "1." When this bit is set the USART transmits a minimum 10 consecutive "0"s immediately after completing any character transmission in progress, and continues sending this pattern until the bit is cleared. When the bit is set and the current character being transmitted clears the shift register the transmit FIFO is cleared. When the bit is reset, the TxD pin will be returned High for at least one bit time before a new character is transmitted. This allows the start bit of the new character to be generated.

### Modem Control Unit

The USART contains modem handshake signals for use in controlling communications between the IDPC and a RS232 type terminal. The modem handshake signals include: RTS. CTS, DSR, and DTR.

RTS and DTR are outputs and are controlled by the local processor via bits 1 and 0 in the USART Modem Control Register, respectively. CTS and DSR are inputs and their status can be read via the USART Modem Status Register, bits 4 and 5 respectively. The Change in DSR and Change in CTS bits in the Modem Status Register indicate pin status since the USART Modem Status Register was last read. A maskable Modem Status Interrupt is generated if bit 3 of the USART Interrupt Enable Register and either bit 1 or bit 0 of the USART Modem Status Register are set. The Change in DSR and Change in CTS bits are cleared when the USART Modem Status Register is read.

### Interrupt Controller

The USART interrupt controller issues an interrupt request to the external processor if an interrupt occurs and that particular interrupt is enabled in the USART Interrupt Enable Register. The interrupt request remains active until the source of the interrupt is cleared. Bits 1, 2, and 3 of the USART Interrupt Identification Register define the source of the interrupt. Bit 0, when cleared, indicates that an interrupt is pending.

#### **Baud Rate Generator**

The USART Baud Rate Generator is a programmable 16-bit divider that receives its input from the USARTCLK pin and can provide the clock to the USART transmitter and receiver. The Baud Rate Generator is configured by loading the USART Baud Rate Divisor LSB and MSB Registers. These registers are accessed by setting the DIV LATCH ACCESS BIT (bit 7 in the USART Line Control Register) and then writing to USART hexadecimal addresses 20 and 21 (USART Data Registers and Interrupt Enable Register addresses when the DIV LATCH ACCESS BIT is cleared).

In asynchronous mode, the Baud Rate Generator must be programmed to a value 16 times the data rate. The output of the Baud Rate Generator is fed to the USART transmitter and receiver and BDCLKOUT pin. Programming the Baud Rate Generator to divide-by-1 passes the USARTCLK unaffected. An internal divide-by-16 circuit generates the appropriate clock rate for the transmitter.

# Clock Selector Unit

The sources of the transmitter and receiver clocks are independently selectable. For example, when bit 0 is set to "1" in the USART Control Register, the Receiver uses the output of the Baud Rate Generator for its clock. When bit 0 is cleared, the RxCLK input is used. The same options apply to the transmitter, except in this case, bit 1 in the USART Control Register specifies the clock source.

1-88 Am79C401

# **Duai-Port Memory Controller (DPMC)**

The DPMC permits the use of shared memory in a multiprocessing environment. The local processor exchanges data with the host processor via shared memory and interprocessor hardware interrupts. The local processor also accesses any device on the IDPC external bus. The host processor can only access the RAM on the IDPC external bus. Any contention between the local processor and the host processor is arbitrated by the DMPC logic internal to the IDPC, providing for transparent access to shared memory. Both processors communicate via memory-resident data buffers and "mailboxes." An inter-processor interrupt scheme notifies the other processor when one of the processors has written data to a buffer or a command to a mailbox.

Functionally, the Dual-Port Memory Controller consists of the following major circuits:

Memory Cycle Arbitration and Control Buffer/Latch Control Inter-processor Interrupt Controller

A simplified block diagram of the Dual-Port Memory Controller is shown in Figure 5.

### Memory Cycle Arbitration and Control

The DPMC generates the cycle timing for all accesses to shared RAM. The length of each cycle is fixed and independent of the cycle times of either the local or host processors. This logic generates memory cycles in response to processor requests. In case of conflicting requests, the logic arbitrates the conflict, granting the first memory access cycle to one processor while holding off the other

processor via the appropriate ready line. The DPMC always arbitrates in favor of the local processor (L-port). If a request from the host port (H-port) is present during a local memory cycle, the host processor is granted the next memory cycle.

# Buffer/Latch Control

The Buffer/Latch Control logic performs such functions as enabling RAM output drivers, enabling data bus latches, and generating RAM cycle timing.

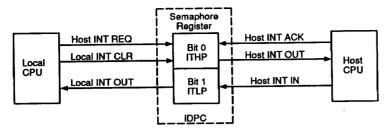

# Inter-Processor Interrupt Controller

The inter-processor interrupt controller provides for inter-processor interrupts via the Semaphore Register. The Semaphore Register is located in the IDPC and is used to coordinate inter-processor interrupts. The local processor can access the Semaphore Register directly, but the host processor cannot (access is provided via strobes to specific pins on the IDPC).

For a local-to-host-processor interrupt, the local processor writes a "1" in bit 0 of the Semaphore Register. When this bit is set, the Interrupt Controller activates the Host Interrupt Out (HINTOUT) pin. The host then responds by pulsing the Host Interrupt Acknowledge (HINTACK) line, clearing the bit and thus the interrupt.

A host-to-local-processor interrupt is initiated when the host pulses the Host Interrupt In (HINTIN) pin. When this happens, Bit 1 in the Semaphore Register is set, activating the Local Interrupt Out (LINTOUT) line. The local processor then acknowledges the interrupt by clearing bit 1 in the Semaphore Register.

Figure 5. Dual-Port Memory Controller (DPMC)

09360B-8

Am79C401

1-89

Notes: Local Interrupt Clear and Host Processor Requests are writes to the Semaphore Register by the local processor.

ITLP = Interrupt to Local Processor ITHP = Interrupt to Host Processor

09360B-9

Figure 6. Inter-Processor Interrupt Structure

# **Programmable Features**

The IDPC is controlled via internal registers that are written and read by software running on the local processor connected to the IDPC external bus. These internal registers may be mapped into either memory or I/O space.

The internal registers occupy a 64-byte block located in the local processor's memory address space. The starting address of the memory block is determined by address decode logic (external to the IDPC) that is used to generate the IDPC chip select signal (CS). The registers and their respective memory offset values are provided in Tables 1–4.

In systems containing more than one processor (e.g., a workstation application with host processor and local processor), only the local processor can access the IDPC registers. The host processor, however, can control IDPC operations indirectly by issuing requests to the local processor via shared memory supported by the IDPC's Dual Port Memory Controller.

The programmable registers are used for establishing modes of operation, configuring the IDPC, and monitoring/reporting status.

|                                               | Table 1. IDPC Address Map                 |  |

|-----------------------------------------------|-------------------------------------------|--|

| Offset (Hex)<br>00-1F<br>20-2A<br>2B-3E<br>3F | Block<br>DLC<br>USART<br>Reserved<br>DPMC |  |

### Data Link Controller (DLC)

# DLC Transmitter

The programmable features associated with the DLC transmitter include:

Transmit Enable—the transmitter may be disconnected from the output pin (SBOUT), leaving other transmit functions intact.

Abort Generation—interrupts a frame and places the transmitter in the abort condition.

Flag/Mark Idle—either condition may be selected as an idle state between frames.

CRC Generation—may be enabled or disabled.

FIFO Threshold—user selectable threshold of 0 to 15 bytes. When the level of the transmit FIFO falls to this level or below, status is reported and a DMA request is generated.

Transparent Mode—transmit HDLC control functions (i.e., flag generation, CRC generation, abort generation, and zero bit insertion) are disabled and data is sent as received from the transmit FIFO.

Interrupts—the following transmitter-related interrupts can be selectively enabled or disabled:

- Valid Packet Sent

- FIFO Buffer Available

- · Transmit Threshold Reached

- Transmit Underrun

1-90 Am79C401

#### **DLC Receiver**

The DLC receiver programmable features include:

Receiver Enable—when disabled, the receive data input pin (SBIN) is disconnected leaving other receiver functions intact.

CRC Check—selectively enables or disables the internal CRC compare operation.

CRC Pass-Thru—the FCS field can be placed into the receive FIFO with the data.

Address Recognition—program any combination of four unique one- or two-byte addresses and the broadcast address, performing address filtering on all incoming packets. In the 1-byte mode, either the first or second byte can be selected. In addition, the Command/Response bit (bit 1 of the first byte) can be ignored.

Minimum Packet Size—defines the minimum packet size in use. A short frame error is indicated if a packet is received containing fewer than the programmed number of bytes (0–15 bytes).

Maximum Packet Size—defines the maximum packet size in use. This prevents buffer overruns in the event of lost flags or protocol violations (65,536 bytes).

FIFO Threshold—select threshold of 2 to 32 bytes. When the level of the receive FIFO reaches this level or above, status is set (unless the last byte of a packet has already been read from the FIFO and status for that packet has not yet been read by the user) and a DMA request is generated. This forms an interlock that maintains synchronization between packet status and data.

Transparent Mode—receive HDLC related control functions (i.e., abort detection, CRC generation and checking, flag detection, and zero bit deletion) are disabled and data is received unaftered

56 kb/s Mode—data is received at a 56 kb/s data rate instead of the usual 64 kb/s rate while in multiplex mode.

Interrupts—the following DLC receiver interrupts may be selectively enabled or disabled:

- · Valid Packet Received

- Abort Received

- Non-Integer Number of Bytes Received (bit residual)

- Receive Data Available

- End-of-Packet in Receive FIFO

### DLC Transmit/Receive Options

The following programmable options affect both the DLC transmitter and receiver:

Data Inversion—the output of the transmitter and the input of the receiver are inverted when this option is selected.

Channel Selection—up to 31 8-bit time slots for multiplexing transmitted serial data and demultiplexing received serial data may be chosen. In non-multiplexed mode, received serial data is continuous and the SFS/XMITCLK pin is used as a transmit clock input independent of the receive clock input.

Local Loopback—the DLC can be programmed to route transmitted data to the receiver for diagnostic purposes.

Remote Loopback—the DLC can be programmed to route received data to the transmit data output for remote testing capabilities.

Reset—a software reset can be generated to stop all functions, clear the FIFOs, and set all registers to their default values.

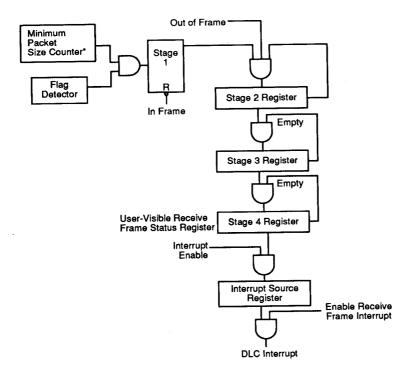

### **Delayed Status Reporting**

The DLC contains several registers that report status in a delayed fashion (see Figure 7). The Receive Frame Status Register, Receive Byte Count Register, Receive Link Address bit field (bits 2–0 of the Interrupt Source Register), and the Receive Field of the Residue Status Control Register (bits 2–0 require this specific implementation in order to support the reception of contiguous (back-to-back) frames. These registers, and residue bit fields, maintain a "history" of frame status, and byte counts of up to three previously received frames while a fourth frame is actually being received. This allows status storage for up to 4 frames.

Each of these registers and bit fields are comprised of the following four stages: current, holding, master, and slave.

As shown in Figure 7, stage 1 holds the current status of the frame presently being received on the link. This stage is updated with the current DLC receiver status as changes occur in real-time.

Stage 1 is transferred to stage 2 when stage 2 is empty and the last byte of another packet is transferred to the DLC receive FIFO. If stage 2 is not empty, then stage 1 retains its status. When stage 1 has transferred to stage 2, stage 1 is free to acquire status of the next packet.

Stage 2 status is transferred to stage 3 as soon as stage 3 becomes empty, allowing status to move from stage 1 to stage 2.

Stage 3 status is transferred to stage 4 (which is the actual status register read by user software) when stage 4 is empty and the last byte of a packet is received. If stage 4 is not empty, then stage 3 retains its status. Stage 4 is cleared when read by software or when DLC reset occurs

The frame status can back up. If stage 4 has not been read when an event occurs that would cause stage 3 to be transferred to stage 4, stage 3 is not transferred to stage 4. What happens is as follows: existing stages 1, 2,

\*Minimum packet size is used as one possible example.

09360B-10

Figure 7. Four-Stage Delayed Status Mechanism

3, and 4 are not disturbed, the DLC receiver freezes stage 1 and data at the SBIN pin is ignored.

Additional received packets are lost until stage 4 is read. As soon as stage 4 is read, stage 3 is transferred to stage 4, stage 2 moves to stage 3, and stage 1 is transferred to stage 2. At this point, the DLC receiver logic enters a "hunt-for-flag" state, and frame reception can begin again.

The valid and invalid packet received bits of the DLC Interrupt Source Register are also reported in a delayed fashion.

Note: If the various delayed-stacked status registers have not been read since the Interrupt Source Register was last read, and the LSB of the Receive Byte Count Register is read, these status registers will be cleared. This ensures that the four-layer stack will remain in sync if a packet is received and the status registers are not read.

Detailed Description of User-Visible DLC Registers

The DLC contains 23 registers, as shown in Table 2.

1-92 Am79C401

Table 2. DLC Registers

| Offset<br>(Hex) | Register Name                              | Size<br>(Bytes) | Туре       |

|-----------------|--------------------------------------------|-----------------|------------|

| 00              | Command/Control Register                   | 1               | Read/Write |

| 01              | Address Control Register                   | . 1             | Read/Write |

| 02              | Link Address Recognition Register 0        | 2               | Read/Write |

| 04              | Link Address Recognition Register 1        | 2               | Read/Write |

| 06              | Link Address Recognition Register 2        | 2               | Read/Write |

| 08              | Link Address Recognition Register 3        | 2               | Read/Write |

| 0A              | Serial Bus Port Control Register           |                 | Read/Write |

| 0B              | Minimum Receive Packet Size Register       | 1               | Read/Write |

| 0C              | Maximum Receive Packet Size Register       | 2               | Read/Write |

| 0E              | Interrupt Source Interrupt Enable Register | 1               | Read/Write |

| 0F              | Receive Frame Interrupt Enable Register    | 1               | Read/Write |

| 10              | Receive Link Interrupt Enable Register     | 1               | Read/Write |

| 11              | FIFO Status Interrupt Enable Register      | 1               | Read/Write |

| 12              | Transmit Byte Count Register               | 2               | Read/Write |

| . 14            | FIFO Threshold Register                    | 1               | Read/Write |

| 15              | Interrupt Source Register                  | 1               | Read Only  |

| 16              | Receive Byte Count Register                | 2               | Read Only  |

| 18              | Receive Frame Status Register              | 1               | Read Only  |

| 19              | Receive Link Status Register               | 1               | Read Only  |

| 1A              | FIFO Status Register                       | 1               | Read Only  |

| 1B              | Receive FIFO Data Register                 | 1               | Read Only  |

| 1C              | Transmit FIFO Data Register                | 1               | Write Only |

| 1D              | Residual Bit Control Status Register       | 1               | Read/Write |

| 1E-1F           | Reserved                                   | 2               | _          |

### DLC Command/Control Register (00 HEX)

This register is used to control basic transmitter and receiver functions.

| 7      | 6     | 5      | 4      | 3      | 2      | 1      | 0     |

|--------|-------|--------|--------|--------|--------|--------|-------|

| ENABLE | DLC   | ENABLE | ENABLE | FLAG/  | RECVER | XMIT   | SEND  |

| FCS    | RESET | CRC    | CRC    | MARK   | ENABLE | ENABLE | ABORT |

| PASS-  |       | GENER. | CHECK  | IDLE   |        |        |       |

| THRU   |       |        |        | SELECT |        |        |       |

- Bit 7: FCS Pass-Thru Enable (Default = 0)—The Frame Check Sequence (CRC) bytes will be transferred to the receive FIFO if this bit is set to "1"; otherwise, they will be discarded by the DLC.

- Bit 6: DLC Reset (Default = 0)—When this bit is set to "1," all DLC FIFOs, latches and status/control bits are forced to their default values. A delay of ten Master Clock (CLK) cycles is required before any DLC registers can be accessed, after resetting the DLC.

- Bit 5: CRC Generate Enable (Default = 1)—If this bit is set to "1," the frame is terminated by appending the calculated CRC bytes and closing flag to the last byte of a packet in the transmit FIFO. If it is cleared to "0," the frame is terminated by appending the closing flag to the byte last byte of a packet.

- Bit 4: CRC Check Enable (Default = 1)—If this bit is set to "1," then on reception of the closing flag, the result of the CRC check is transferred to the CRC Error bit (bit 2) in the Receive Frame Status Register; otherwise, the CRC result is ignored.

- Bit 3: Flag/Mark Idle (Default = 0)—This bit determines what the transmitter sends when not inframe. If it is set to "1," a flag pattern (011111110) is sent. If it is reset to "0," a mark pattern (11111111) is sent.

- Bit 2: Receiver Enable (Default = 0)—When this bit is set to "1" data is clocked into the Serial Bus Port; otherwise, the DLC receiver is disabled and data on the SBIN pin is ignored.

Note that if this bit is cleared while the DLC receiver is in the process of receiving a frame (i.e., the receiver is inframe), the SBIN pin will not be disabled until the closing flag of the frame being received is detected.

Bit 1: Transmitter Enable (Default = 0)—When set to "1," data from the DLC is shifted out the SBOUT pin under control of SCLK or SFS/XMITCLK; otherwise, the SBOUT pin is disabled.

Note that if this bit is cleared while in the process of sending a frame, the DLC will complete sending the frame before disabling the SBOUT pin.

Bit 0: Send Abort (Default = 0)—When set to "1," the DLC transmitter abort generator transmits abort characters (01111111, LSB on right). If this bit is set and cleared on two successive writes, the DLC will transmit at least one abort character. The transmitter will continue to send these abort patterns for as long as this bit is set. Abort characters are always sent in whole bytes.

Note that when this bit is set the DLC transmit FIFO, DLC byte counter, and the DLC Transmit Byte Count Register will be cleared.

# **DLC Address Control Register (01 HEX)**

All bits in the DLC Address Control Register are set and cleared by software except when initialized to default values as the result of a reset.

The DLC Address Control Register can be written and read by the local processor. When all link address enable bits (bits 3–0) and the broadcast enable bit (bit 4) are cleared to "0," the DLC does not perform address detec-

tion, and passes all received frame bytes to the DLC receive FIFO. In this case, bits 7-5 are ignored.

If one or more of the link address enable bits (bits 4–0) are set, then a successful link address compare must occur before any frame bytes can be transferred to the DLC receive FIFO.

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FIRST/ | ENABLE | 1–2    | ENABLE | ENABLE | ENABLE | ENABLE | ENABLE |

| SECOND | C/R    | BYTE   | BRDCST | ADDR   | ADDR   | ADDR   | ADDR   |

| BYTE   | віт    | ADDR   | ADDR   | DETECT | DETECT | DETECT | DETECT |

| SELECT | CMPARE | SELECT | DETECT | 3      | 2      | 1      | 0      |

- Bit 7: First/Second Byte Selection (Default = 0)—

This bit is ignored unless bit 5 of this register is set to "1." When this bit is set, only the second byte is monitored by the address recognizers (first eight bits are don't cares). When this bit is cleared, only the first byte is examined.

- Bit 6: C/R Address Enable (Default = 0)—At least one of the enable bits (4–0) must be set for this bit to have any effect on DLC operation.

If any of the enable bits are set, and the C/R address enable bit is cleared, then bit 1 of the first address byte of each received frame will be ignored.

If this bit is set, then bit 1 of the first received frame address byte must compare successfully along with the other address bits for address recognition to occur.

Bit 5: Address Size 1-2 (Default = 0)—At least one of the enable bits (4-0) must be set for this bit to have any affect on DLC operation. If any of the enable bits are set and bit 5 is cleared, then the first two address bytes of each received frame will be compared.

If bit 5 is set to "1," only one byte is compared (bit 7 specifies whether the first or second byte is compared).

- Bit 4: Broadcast Address Enable (Default = 1)—

When set to "1," this bit enables comparison of a receive frame address with an all "1"s (broadcast address) register. The comparison is conditioned by bits 7–5 of this register. When bits 4–0 are cleared, address detection by the DLC is inhibited. If bit 4 is cleared to a zero and one or more of the enable bits (3–0) is set, then the all "1"s pattern is ignored.

- Bit 3: Address Register 3 Enable (Default = 0)—Link address 3 enable.

- Bit 2: Address Register 2 Enable (Default = 0)—Link address 2 enable.

Bit 1: Address Register 1 Enable (Default = 0)—Link address 1 enable.

Bit 0: Address Register 0 Enable (Default = 0)—Link address 0 enable.

Note: When set to "1," bits 3-0 enable comparison of a received frame address with the contents of the DLC

Link Address Recognition Registers 0 through 3, respectively.

The comparison of a received frame address with the contents of all enabled Address Recognition Registers is conditioned by bits 7–5 of this register.

# DLC Link Address Recognition Registers (02-03, 04-05, 06-07, 08-09 Hex)

These four registers are two bytes wide with the LSB having the lower address. The LSB of each pair corresponds to the second byte following the flag. The MSB corresponds to the first byte following the flag.

All of the bits in the four Link Address Recognition Registers are set and cleared by software except when initialized to "0"s by a DLC reset or IDPC reset.

Each of these four registers has a corresponding enable bit in the DLC Address Control Register (bits 3–0). If the corresponding enable bit is set, then the value in the Link Address Recognition Register is conditioned by bits 7–5 of the DLC Address Control Register. Default = Hex 0000.

### DLC Serial Bus Port Control Register (0A HEX)

All bits in the Serial Bus Port Control Register are set and cleared by software, except when initialized to default values by a DLC reset or IDPC reset. This register can be written and read by the local processor.

| 7      | 6      | . 5    | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ENABLE | ENABLE | INVERT | CHAN   | CHAN   | CHAN   | CHAN   | CHAN   |