# F71858AD

Hardware Monitor, KBC with GPIO & ACPI

Release Date: Aug, 2010

Version: V0.12P

## F71858AD Datasheet Revision History

| Version | Date      | Page | Revision History                                             |

|---------|-----------|------|--------------------------------------------------------------|

| 0.10P   | 2009/6/19 | -    | Preliminary Version                                          |

| 0.11P   | 2009/8/6  | -    | Add Application Circuit Add Registers & Application Circuits |

| 0.12P   | 2010/10/5 | 39   | Add TSI/SMBus Address Register – Index 08h                   |

|         |           |      |                                                              |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Fintek for any damages resulting from such improper use or sales.

## **Table of Content**

| 1.  | General Description                                                  | 4   |

|-----|----------------------------------------------------------------------|-----|

| 2.  | Feature List                                                         | 4   |

| 3.  | Key Specification                                                    | 6   |

| 4.  | Pin Configuration                                                    | 7   |

| 5.  | Pin Description                                                      |     |

| ٥.  | 5.1 Power Pin                                                        |     |

|     | 5.2 LPC Interface                                                    | _   |

|     | 5.3 Keyboard Controller                                              |     |

|     | 5.4 ACPI                                                             |     |

| _   | 5.5 H/W Monitor                                                      |     |

| 6.  | Function Description                                                 |     |

|     | 6.1 Power on Strapping                                               |     |

|     | 6.2 Keyboard Controller                                              |     |

|     | 6.4 Hardware monitor                                                 |     |

|     | 6.5 LED function                                                     |     |

|     | 6.6 AMD TSI and Intel SST PECI Function                              |     |

|     | 6.7 Watchdog Timer Function                                          | .28 |

| 7.  | Register Description                                                 | .29 |

|     | 7.1 Global Control Registers                                         |     |

|     | 7.2 KBC Registers                                                    |     |

|     | 7.3 ACPI and PME Registers                                           |     |

|     | 7.4 Hardware Monitor Registers (Index port: 0x295; Data port: 0x296) |     |

|     | 7.6 WDT Registers                                                    |     |

| 8.  | PCB Layout Guide                                                     |     |

| 9.  | Electrical Characteristics                                           |     |

| Ο.  | 9.1 Absolute Maximum Ratings                                         |     |

|     | 9.2 DC Characteristics                                               | 69  |

|     | 9.3 DC Characteristics Continued                                     | 69  |

|     | 9.4 AC Characteristics                                               |     |

| 10. | Ordering Information                                                 | .75 |

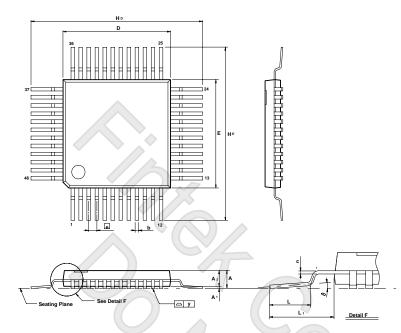

| 11. | Package Dimensions (48LQFP)                                          | .76 |

|     |                                                                      | 77  |

## 1. General Description

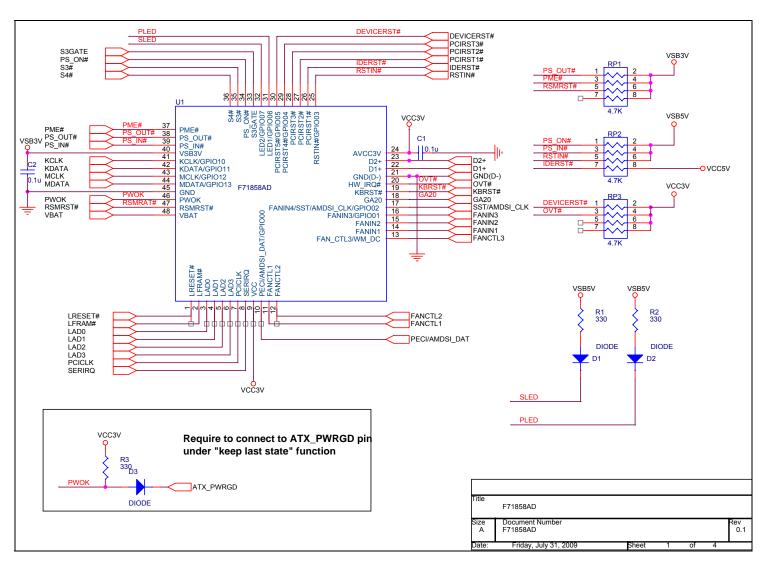

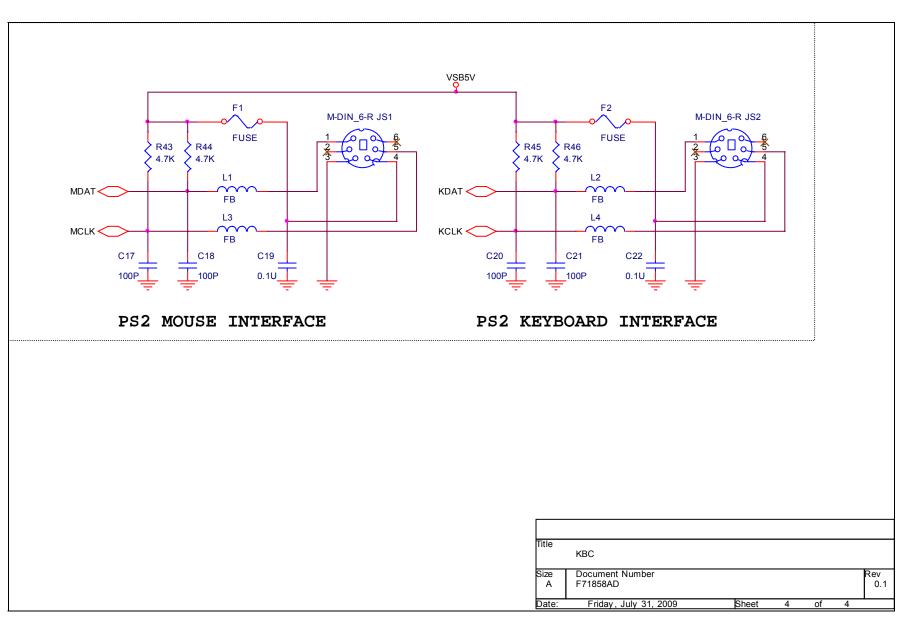

The F71858AD is hardware KBC integrating the ACPI, temperature sensing and fan control functions specific for the legacy free MB application. The KBC functions include one keyboard and one PS/2 mouse, and can be used with IBM®-compatible personal computers or PS/2-based systems. The controller receives serial data from the keyboard or PS/2 mouse, checks the parity of the data, and presents the data to the system as a byte of data in its output buffer. The controller will assert an interrupt to the system when data are placed in its output buffer.

The F71858AD provides the ACPI control signals as well such as S3 state, resume reset, 12 pins GPIO, WDT, PCI reset outputs or power OK signals. The power LED is programmable and compliant with PC2001.

As to the environment sensing functions, F71858AD provides 2 remote analog dual current temp. sensing inputs and one internal local temperature sensing. One HW\_IRQ (alert signal) will be issued while the temperature is over the programmable limit. 4 fan monitoring inputs and 3 fan controlling outputs provide Fintek's patented auto-fan controlling features. Besides, the F71858AD supports AMD TSI and Intel PECI/SST interfaces for next generation CPU temp. sensing technology.

F71858AD is in LPC interface and powered by 3VCC, 3V standby, and battery. The package is in 48 pin LQFP Green Package.

### 2. Feature List

#### General Functions

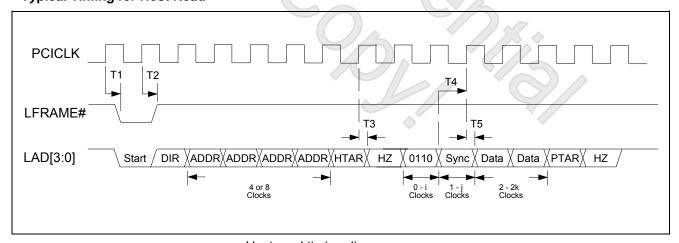

- ➤ Comply with LPC Spec. 1.1

- ➤ Hardware Keyboard Controller support one PS/2 keyboard and one PS/2 mouse

- ➤ Hardware Gate A20 and Hardware Keyboard Reset

- Support ACPI 3.0

- > 12 GPIO Pins

- WDT signal

- ➤ HWM functions (Also support PECI fan control mechanism)

#### KBC

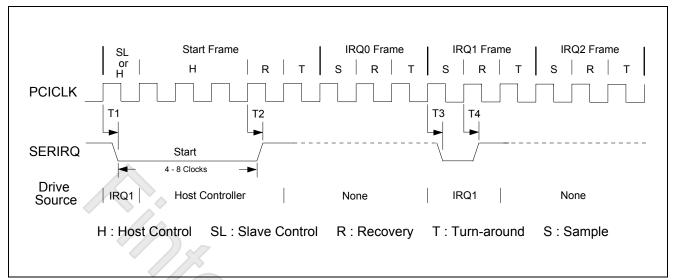

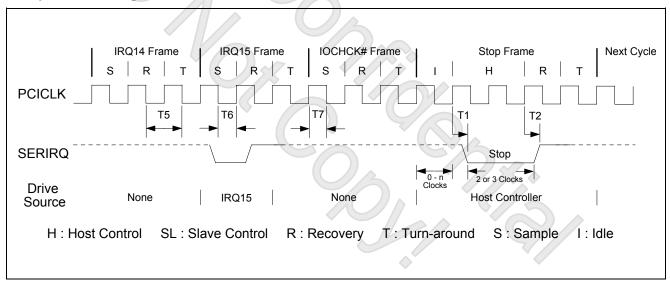

- ➤ LPC interface support serial interrupt channel 1, 12.

- Two 16bit Programmable Address fully decoder, default 0x60 and 0x64.

- ➤ Support two PS/2 interface, one for PS/2 mouse and the other for keyboard.

- Keyboard's scan code support set1, set2.

- > Programmable compatibility with the 8042.

- > Support both interrupt and polling modes.

- Hardware Gate A20 and Hardware Keyboard Reset.

#### ACPI Functions

- 1 reset input and 5 PCI reset output pins

- 2 programmable power LED

- > S3Gate control

- Resume reset

- Power ok signal

#### Hardware Monitor Functions

- ➤ 2 current type accurate (3°C) thermal inputs for CPU thermal diode/2N3906 transistors

- One internal local thermal sensor

- > Pin HW\_IRQ# (default limit 100°C for CPU temp.)

- ➤ Temperature sensing range from -40°C~127°C

- > 4 fan speed monitoring inputs

- > 3 fan speed auto-control (support 3 wire and 4 wire fans)

- Support PWM and DAC mode control

- ➤ Default PWM duty is 40% when system boot up promptly

- Provide Intel PECI/SST interface for temperature sensing

- Provide AMD TSI interface for temperature sensing

- Support 3 channels voltage monitor ( VCC3V + VSB3V + VBAT)

- Voltage monitor resolution is 8mV per LSB

#### GPIO Function

- > Total 12 pins GPIO

- GPIO supports interrupt event by PME/SERIRQ

### Watch Dog Timer

- > Time resolution minute/second by option

- > Maximum 256 minutes or 256 seconds

- > Output WDT signal via PWOK pin

### Package

> 48-pin LQFP

## 3. Key Specification

Supply Voltage

Operating Supply Current

3.0V to 3.6V

5 mA typ.

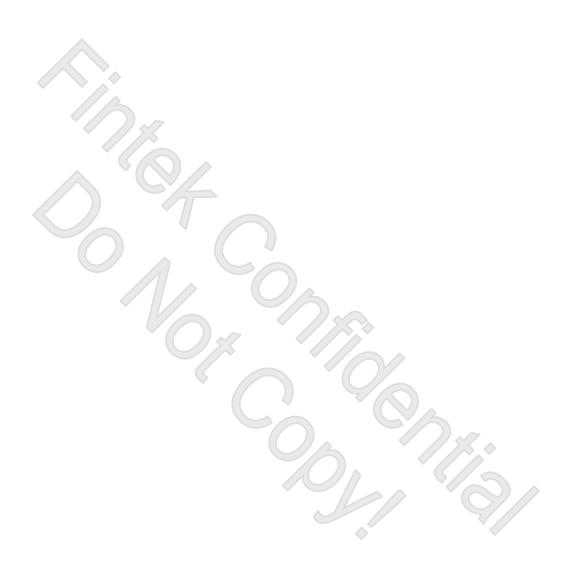

## 4. Pin Configuration

## 5. Pin Description

I/O<sub>12t</sub>

- TTL level bi-directional pin with 12 mA source-sink capability.

I/OOD<sub>12st 5v</sub>

- TTL level bi-directional pin and schmitt trigger, can select to OD or OUT by register, with 12 mA source-sink capability.

I/OOD<sub>16st.5v</sub>

- TTL level bi-directional pin and schmitt trigger, can select to OD or OUT by register, with 16 mA source-sink capability, 5V tolerance.

$OD_{16u,10k}$  $OD_{16,5V}$

- Open-drain output pin with 16 mA sink capability, pull-up 10k ohms.

- Open-drain output pin with 16 mA sink capability, 5V tolerance.

I/OD<sub>12st,5v</sub>

- TTL level bi-directional pin and schmitt trigger, Open-drain output with 12 mA sink capability, 5V tolerance.

I/OD<sub>12t,5v</sub>

-TTL level bi-directional pin, Open-drain output with 12 mA sink capability, 5V tolerance.

O<sub>16</sub>

-Output pin with 16 mA source-sink capability. Open-drain output pin with 12 mA sink capability

OD<sub>12</sub> OD<sub>12,5v</sub>

- Open-drain output pin with 12 mA sink capability, 5V tolerance.

- TTL level input pin,5V tolerance.  $IN_{t.5v}$ - TTL level input pin,5V tolerance.  $IN_{t.5v}$  $IN_{st}$ - TTL level input pin and schmitt trigger.

IN<sub>t</sub> - TTL level input pin

$\text{IN}_{\text{st,5v}}$

- TTL level input pin and schmitt trigger, 5V tolerance.

$I_{LV}/O_{D8.S1}$

- Bi-directional pin with 8mA source and 1mA sink capability, input level over 0.9v for high and under 0.5v for low.

$I_{Lv}/OD_{12}$

- Bi-directional pin with 12mA sink capability, input level over 0.9v for high and under 0.5v for low.

$I_{1}/OOD_{12}$

- Bi-directional pin, can select to OD or OUT by register, with 12mA source-sink capability, input level over 0.9v for high and under 0.5v for low.

$IN_{I\nu}\,$

- Input pin, input level over 0.9v for high and under 0.5v for low.

- Output pin(Analog). AOUT AIN - Input pin(Analog).

Ρ - Power.

#### 5.1 **Power Pin**

| Pin No. | Pin Name | Type | Description                                   |

|---------|----------|------|-----------------------------------------------|

| 9       | VCC      | Р    | 3V power                                      |

| 21      | GND(D-)  | Р    | Ground for temperature sensing usage.         |

| 24      | AVCC3V   | Р    | 3V power for analog (Provide voltage monitor) |

| 40      | VSB3V    | Р    | 3V stand by power (Provide voltage monitor)   |

| 45      | GND      | Р    | Ground                                        |

| 48      | VBAT     | Р    | Battery power (Provide voltage monitor)       |

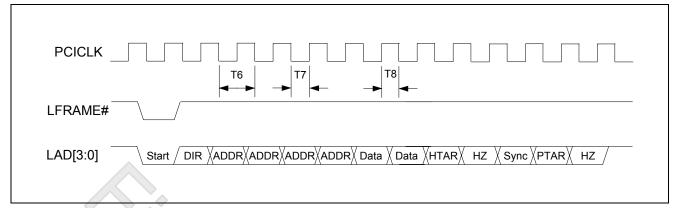

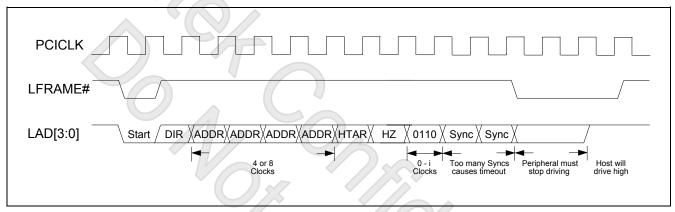

#### 5.2 LPC Interface

| Pin No. | Pin Name | Туре                | PWR | Description                                                 |

|---------|----------|---------------------|-----|-------------------------------------------------------------|

| 1       | LRESET#  | IN <sub>st,5v</sub> | VCC | Reset signal. It can connect to PCIRST# signal on the host. |

| 2       | LFRAME#  | IN <sub>st</sub>    | VCC | Indicates start of a new cycle or termination of a          |

|         |          |                    |     | broken cycle.                                                                                                           |

|---------|----------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 3,4,5,6 | LAD[3:0] | I/O <sub>12t</sub> | VCC | These signal lines communicate address, control, and data information over the LPC bus between a host and a peripheral. |

| 7       | PCICLK   | $IN_t$             | VCC | 33MHz PCI clock input.                                                                                                  |

| 8       | SERIRQ   | I/O <sub>12t</sub> | VCC | Serial IRQ input/Output.                                                                                                |

## 5.3 Keyboard Controller

| Pin No. | Pin Name | Туре                     | PWR | Description                                                                                            |

|---------|----------|--------------------------|-----|--------------------------------------------------------------------------------------------------------|

| 18      | GA20     | OD <sub>16,u10k</sub>    | VCC | Gate A20 output. This pin is high after system reset. Internal pull high 3.3V with 10k ohms. (KBC P21) |

| 19      | KBRST#   | OD <sub>16-u10k</sub>    | VCC | Keyboard reset. This pin is high after system reset. Internal pull high 3.3V with 10k ohms. (KBC P20)  |

| 41      | KCLK     | I/OD <sub>16st,5V</sub>  | VSB | Keyboard Clock.                                                                                        |

|         | GPIO10   | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                                     |

| 40      | KDATA    | I/OD <sub>16st,5V</sub>  | VSB | Keyboard Data.                                                                                         |

| 42      | GPIO11   | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                                     |

| 40      | MCLK     | I/OD <sub>16st,5V</sub>  | VSB | PS2 Mouse Clock.                                                                                       |

| 43      | GPIO12   | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                                     |

| 4.4     | MDATA    | I/OD <sub>16st,5V</sub>  | VSB | PS2 Mouse Data.                                                                                        |

| 44      | GPIO13   | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                                     |

## 5.4 ACPI

| Pin No. | Pin Name     | Туре                     | PWR | Description                                                                                   |

|---------|--------------|--------------------------|-----|-----------------------------------------------------------------------------------------------|

| 0.5     | RSTIN#       | IN <sub>st,5v</sub>      | VSB | Reset buffer input signal.                                                                    |

| 25      | GPIO03       | I/OOD <sub>12st,5V</sub> | VSB | General purpose IO                                                                            |

| 26      | PCIRST1#     | OD <sub>16,5V</sub>      | VSB | Output buffer of RSTIN# and LRESET# for IDE reset.                                            |

| 27,28   | PCIRST[2:3]# | O <sub>16</sub>          | VSB | Output buffer of RSTIN# and LRESET#.                                                          |

| 29      | PCIRST4#     | O <sub>16</sub>          | VSB | Output buffer of RSTIN# and LRESET#.                                                          |

| 29      | GPIO04       | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                            |

| 30      | PCIRST5#     | OD <sub>16,5V</sub>      | VSB | Output buffer of RSTIN# and LRESET# for IDE reset.                                            |

|         | GPIO05       | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                            |

| 31      | LED1         | OD <sub>16,5V</sub>      | VSB | Power LED for VSB.                                                                            |

| 31      | GPIO06       | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                            |

| 32      | LED2         | OD <sub>16,5V</sub>      | VSB | Power LED for VSB.                                                                            |

| 32      | GPIO07       | I/OOD <sub>16st,5V</sub> | VSB | General purpose IO                                                                            |

| 33      | S3GATE       | OD <sub>12,5v</sub>      | VSB | Control dual voltage signal.                                                                  |

| 34      | PS_ON#       | OD <sub>12,5v</sub>      | VSB | Power supply on-off control output. Connect to ATX power supply PS_ON# signal.                |

| 35      | S3#          | IN <sub>st</sub>         | VSB | S3# Input is Main power on-off switch input.                                                  |

| 36      | S4#          | IN <sub>st</sub>         | VSB | S4# Input is for S3/S4 (S5) state switch input.                                               |

| 38      | PS_OUT#      | OD <sub>12</sub>         | VSB | Panel Switch Output. This pin is low active and pulse output. It is power on request output#. |

| 39 | PS_IN#  | IN <sub>st,5v</sub>    | VSB  | Main power switch button input.                                                                                                                                         |

|----|---------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46 | PWOK    | I/OD <sub>12t,5V</sub> | VBAT | PWOK function, It is power good signal of VCC, which is delayed 400ms (default and programmable) as VCC arrives at 2.8V.  Watchdog signal can be asserted via this pin. |

| 47 | RSMRST# | OD <sub>12</sub>       | VBAT | Resume Reset# function, It is power good signal of VSB, which is delayed 66ms as VSB arrives at 2.3V.                                                                   |

## 5.5 H/W Monitor

| Pin No. | Pin Name    | Туре                                | PWR | Description                                                                                                                                                  |

|---------|-------------|-------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | PECI        | I <sub>Lv</sub> /O <sub>D8,S1</sub> |     | Intel PECI hardware monitor interface.                                                                                                                       |

| 10      | AMDTSI_DATA | I <sub>Lv</sub> /OD <sub>12</sub>   | VCC | AMD TSI data interface.                                                                                                                                      |

|         | GPIO00      | J <sub>Lv</sub> /OOD <sub>12</sub>  |     | General purpose IO                                                                                                                                           |

| 11      | FAN_CTL1    | OD <sub>12, 5v</sub><br>AOUT        | VCC | Fan 1 control output. This pin provides PWM duty-cycle output or a voltage output. Default PWM duty is 40%.                                                  |

| 12      | FAN_CTL2    | OD <sub>12,5v</sub><br>AOUT         | VCC | Fan 2 control output. This pin provides PWM duty-cycle output or a voltage output. Default PWM duty is 40%.                                                  |

| 40      | FAN_CTL3    | OD <sub>12,5V</sub><br>AOUT         | VCC | Fan 3 control output and 3pin fan is recommended to be controlled by this pin but not 4pin fan. This pin provides PWM duty-cycle output or a voltage output. |

| 13      | PWM_DC      | IN <sub>t,5v</sub>                  | VCC | Power on strapping : Pull high: Fan control method will be in PWM Mode NC: Fan control method will be in DAC Mode                                            |

| 14      | FANIN1      | IN <sub>st,5v</sub>                 | VCC | Fan 1 tachometer input.                                                                                                                                      |

| 15      | FANIN2      | IN <sub>st,5v</sub>                 | VCC | Fan 2 tachometer input.                                                                                                                                      |

| 16      | FANIN3      | IN <sub>st,5v</sub>                 | VCC | Fan 3 speed input. Default PWM duty is 40%.                                                                                                                  |

| 10      | GPIO01      | I/OOD <sub>12st,5V</sub>            | VCC | General purpose IO                                                                                                                                           |

|         | FANIN4      | IN <sub>Iv</sub>                    | ,   | Fan 4 speed input.                                                                                                                                           |

| 17      | SST         | $I_{Lv}/O_{D8,S1}$                  | VCC | Intel SST hardware monitor interface.                                                                                                                        |

|         | AMDTSI_CLK  | OD <sub>12</sub>                    |     | Clock output for AMD TSI interface.                                                                                                                          |

|         | GPIO02      | I <sub>Lv</sub> /OOD <sub>12</sub>  |     | General purpose IO                                                                                                                                           |

| 20      | HW_IRQ#     | OD <sub>12,5V</sub>                 | VCC | Active low output. This pin will be logic low when the temperature exceeds its limit or fan fault event.                                                     |

| 22      | D1+(CPU)    | AOUT<br>AIN                         | VCC | Thermal diode/transistor temperature sensor input.                                                                                                           |

| 23      | D2+         | AOUT<br>AIN                         | VCC | Thermal diode/transistor temperature sensor input.                                                                                                           |

| 37      | PME#        | OD <sub>12</sub>                    | VSB | Generated PME event. It supports the PCI PME# interface. This signal allows the peripheral to request the system to wake up from the S3 state.               |

## 6. Function Description

## 6.1 Power on Strapping

| Pin No. | Symbol | Value | Description                            |

|---------|--------|-------|----------------------------------------|

| 13      | DWM DC | 1     | Fan control mode: PWM mode. ( Default) |

|         | PWM_DC | 0     | Fan control mode: DAC mode.            |

## 6.2 Keyboard Controller

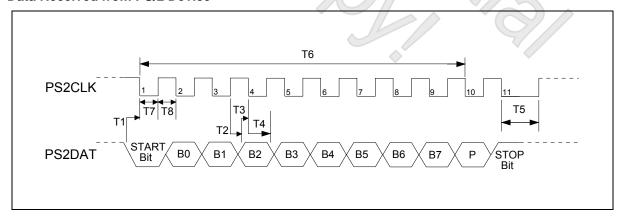

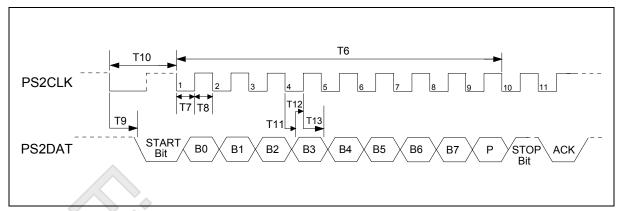

The KBC circuit provides the functions included a keyboard and/or a PS/2 mouse, and can be used with IBM®-compatible personal computers or PS/2-based systems. The controller receives serial data from the keyboard or PS/2 mouse, checks the parity of the data, and presents the data to the system as a byte of data in its output buffer. The controller will assert an interrupt to the system when data are placed in its output buffer.

### **Output Buffer**

The output buffer is an 8-bit read-only register at I/O address 60h. The keyboard controller uses the output buffer to send the scan code received from the keyboard and data bytes required by commands to the system.

#### **Input Buffer**

The input buffer is an 8-bit write-only register at I/O address 60h or 64h. Writing to address 60h sets a flag to indicate a data write; writing to address 64h sets a flag to indicate a command write. Data written to I/O address 60h is sent to keyboard through the controller's input buffer only if the input buffer full bit in the status register is "0".

#### Status Register

The status register is an 8-bit read-only register at I/O address 64h that holds information about the status of the keyboard controller and interface. It may be read at any time.

| BIT | BIT FUNCTION       | DESCRIPTION                                |

|-----|--------------------|--------------------------------------------|

| 0   | Output Buffer Full | Output buffer empty     Output buffer full |

| 1   | Input Buffer Full  | Input buffer empty     Input buffer full   |

|       | 2        | System Flag                 | This bit may be set to 0 or 1 by writing to the system flag bit in the command byte of the keyboard controller (KCCB). It defaults to 0 after a power-on reset. |  |  |  |  |

|-------|----------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       | 3        | Command/Data                | 0: Data byte<br>1: Command byte                                                                                                                                 |  |  |  |  |

|       | 4        | Inhibit Switch              | Keyboard is inhibited     Keyboard is not inhibited                                                                                                             |  |  |  |  |

|       | 5        | Mouse Output Buffer         | O: Muse output buffer empty     House output buffer full                                                                                                        |  |  |  |  |

|       | 6        | General Purpose<br>Time-out | 0: No time-out error 1: Time-out error                                                                                                                          |  |  |  |  |

|       | 7        | Parity Error                | 0: Odd parity 1: Even parity (error)                                                                                                                            |  |  |  |  |

| Comma | Commands |                             |                                                                                                                                                                 |  |  |  |  |

| COMMAND | FUNCTION                                   |  |  |  |  |  |  |

|---------|--------------------------------------------|--|--|--|--|--|--|

| 20h     | Read Command Byte                          |  |  |  |  |  |  |

|         | Write Command Byte                         |  |  |  |  |  |  |

|         | BIT DESCRIPTION                            |  |  |  |  |  |  |

|         | 0 Enable Keyboard Interrupt                |  |  |  |  |  |  |

|         | 1 Enable Mouse Interrupt                   |  |  |  |  |  |  |

|         | 2 System flag                              |  |  |  |  |  |  |

| 60h     | 3 Reserve                                  |  |  |  |  |  |  |

|         | 4 Disable Keyboard Interface               |  |  |  |  |  |  |

|         | 5 Disable Mouse interface                  |  |  |  |  |  |  |

|         | 6 IBM keyboard Translate Mode              |  |  |  |  |  |  |

|         | 7 Reserve                                  |  |  |  |  |  |  |

|         |                                            |  |  |  |  |  |  |

| A7h     | Disable Auxiliary Device Interface         |  |  |  |  |  |  |

| A8h     | Enable Auxiliary Device Interface          |  |  |  |  |  |  |

|         | Auxiliary Interface Test                   |  |  |  |  |  |  |

|         | 8'h00: indicate Auxiliary interface is ok. |  |  |  |  |  |  |

| A O.b.  | 8'h01: indicate Auxiliary clock is low.    |  |  |  |  |  |  |

| A9h     | 8'h02: indicate Auxiliary clock is high    |  |  |  |  |  |  |

|         | 8'h03: indicate Auxiliary data is low      |  |  |  |  |  |  |

|         | 8'h04: indicate Auxiliary data is high     |  |  |  |  |  |  |

| AAh     | Self-test Self-test                        |  |  |  |  |  |  |

| AAN     | Returns 055h if self test succeeds         |  |  |  |  |  |  |

| ABh | keyboard Interface Test 8'h00: indicate keyboard interface is ok. 8'h01: indicate keyboard clock is low. 8'h02: indicate keyboard clock is high 8'h03: indicate keyboard data is low 8'h04: indicate keyboard data is high |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADh | Disable Keyboard Interface                                                                                                                                                                                                 |

| AEh | Enable Keyboard Interface                                                                                                                                                                                                  |

| C0h | Read Input Port(P1) and send data to the system                                                                                                                                                                            |

| C1h | Continuously puts the lower four bits of Port1 into STATUS register                                                                                                                                                        |

| C2h | Continuously puts the upper four bits of Port1 into STATUS register                                                                                                                                                        |

| D0h | Send Port2 value to the system                                                                                                                                                                                             |

| D1h | Only set/reset GateA20 line based on the system data bit 1                                                                                                                                                                 |

| D2h | Send data back to the system as if it came from Keyboard                                                                                                                                                                   |

| D3h | Send data back to the system as if it came from Muse                                                                                                                                                                       |

| D4h | Output next received byte of data from system to Mouse                                                                                                                                                                     |

| FEh | Pulse only RC (the reset line) low for 6μs if Command byte is even                                                                                                                                                         |

**KBC** Command Description

### PS2 wakeup function

The KBC supports keyboard and mouse wakeup function. When pressing combinational keys as (1) CTRL +ESC (2) CTRL+F1 (3) CTRL+SPACE (4) ANY KEY (5) windows 98 wakeup up key under keyboard wakeup function, KBC will assert PME signal. KBC will also assert PME signal via mouse's (1) BUTTON CLICK or (2) BUTTON CLICK AND MOVEMENT. Those wakeup conditions are controlled by configuration register.

#### 6.3 ACPI function

The Advanced Configuration and Power Interface (ACPI) is a system for controlling the use of power in a computer. It lets computer manufacturer and user to determine the computer's power usage dynamically.

There are three ACPI states that are of primary concern to the system designer and they are designated S0, S3 and S5. S0 is a full-power state; the computer is being actively used in this state. The other two are called sleep states and reflect different power consumption when power-down. S3 is a state that the processor is powered down but the last procedural state is being stored in memory which is still active. S5 is a state that memory is off and the last procedural state of the processor has been stored to the hard disk. Take S3 and S5 as comparison, since memory is fast, the computer can quickly come back to full-power state, the disk is slower than the memory and the computer

takes longer time to come back to full-power state. However, since the memory is off, S5 draws the minimal power comparing to S0 and S3.

It is anticipated that only the following state transitions may happen:

$$S0 \rightarrow S3$$

,  $S0 \rightarrow S5$ ,  $S5 \rightarrow S0$ ,  $S3 \rightarrow S0$  and  $S3 \rightarrow S5$ .

Among them, S3 $\rightarrow$ S5 is illegal transition and won't be allowed by state machine. It is necessary to enter S0 first in order to get to S5 from S3. As for transition S5 $\rightarrow$ S3 will occur only as an immediate state during state transition from S5 $\rightarrow$ S0. It isn't allowed in the normal state transition.

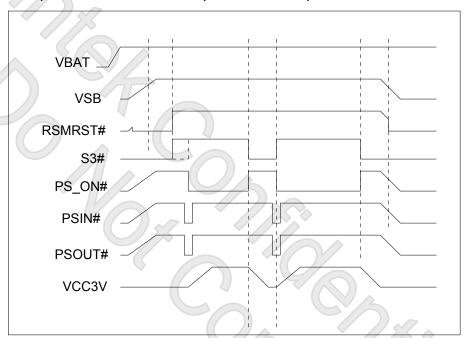

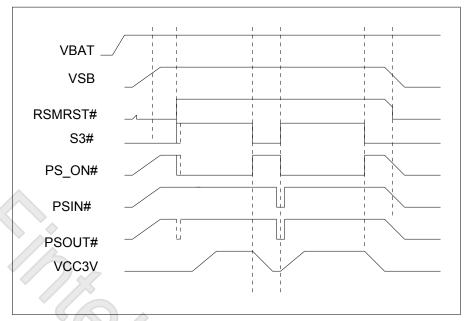

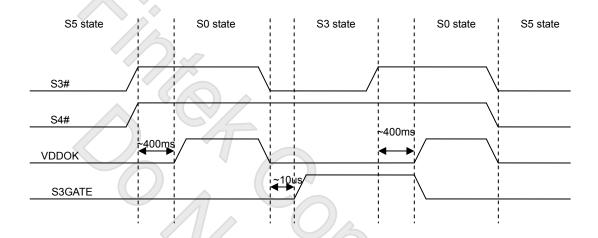

The below diagram described the timing, the always on and always off, keep last state could be set in control register. In keep last state mode, one register will keep the status of before power loss. If it is power on before power loss, it will remain power on when power is resumed, otherwise, if it is power off before power loss, it will remain power off when power is resumed.

**ACPI Default Timing Always Off**

ACPI Default Timing Always On

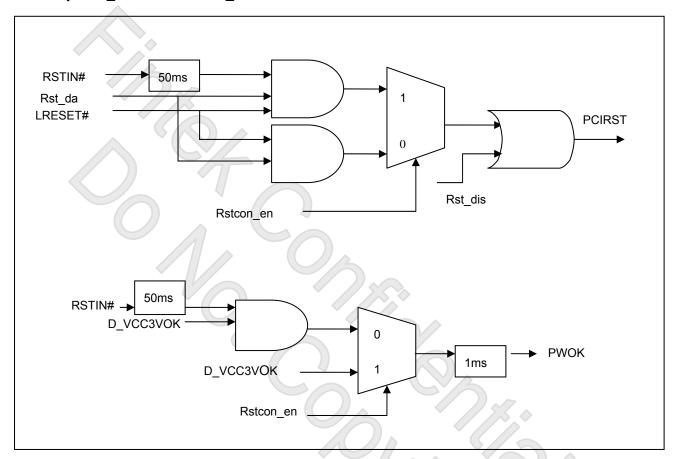

### **PCIRST and PWROK Signals**

The F71858AD supports 5 output buffers for 5 reset signals. The result of PCIRST [1:5]# outcome will be affected by conditions as below.

The PWROK signal is affected by RST\_IN#/LRESET#/DVCC3VOK.when rstcon\_en set 1, POWEROK signal is affected by D\_VCC3VOK and when rstcon\_en set 0, POWEROK signal is affected by RST\_IN#/ LRESET#/D\_VCC3VOK.See below for the reference.

PCIRST# and PWROK

### S3 GATE Signals

The S3GATE signal response S0/S3/S5 state and condition is as below. When system is in S3 state, S3GATE is asserted logic high; the other state is asserted logic low. It is anticipated that only the following state transitions may happen:

$$S0 \rightarrow S3$$

,  $S0 \rightarrow S5$ ,  $S5 \rightarrow S0$ ,  $S3 \rightarrow S0$  and  $S3 \rightarrow S5$ .

Among them, S5→S3 is illegal transition and S3GATE signal will be keep logic level.

S3GATE Timming

#### 6.4 Hardware monitor

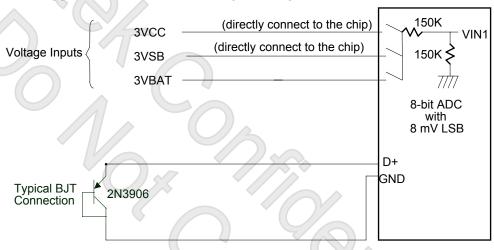

For the 8-bit ADC has the 8mv LSB, the maximum input voltage of the analog pin is 2.04V. Therefore the voltage under 2.04V (ex:1.5V) can be directly connected to these analog inputs. The voltage higher than 2.04V should be reduced by a factor with external resistors so as to obtain the input range. VCC, VSB 3.3V and VBAT 3V are the exception for it is main power of the F71858AD. Therefore these powers can directly connect to this chip's power pin and need no external resistors. There are two functions in these pins with 3.3V/3V. The first function is to supply internal logic power of the F71858AD and the second function is that this voltage with 3.3V/3V is connected to internal serial resistors to monitor the VCC VSB 3.3V and VBAT voltage. The internal serial resistors are two 150K ohm, so that the internal reduced voltage is half of 3.3V/3V.

F71858AD only support three power voltage monitor but without hardware high low limit protect. So it will not trigger PME event when voltage too high or too low.

The F71858AD monitors a local and 2 remote temperature sensor. Both can be measured from -40°C to 127°C. The temperature format is as the following table:

#### Table mode:

Display range is from -40°C to 127°C. The values in high byte registers bit7 is sign bit and the values in high byte registers bit6~bit0 are mean temperature reading value and the unit is 1°C. The value in low bye register bit7~bit5 are temperature reading value and the unit is 0.125°C.

| Temperature | Digital Output<br>(High byte) | Digital Output<br>(Low byte) |

|-------------|-------------------------------|------------------------------|

| -40°C       | 1101 1000                     | 000X XXXX                    |

| -1°C        | 1111 1111                     | 000X XXXX                    |

| 0°C         | 0000 0000                     | 000X XXXX                    |

| 100°C     | 0110 0100 | 000X XXXX |

|-----------|-----------|-----------|

| 127.875°C | 0111 1111 | 111X XXXX |

| open      | 1011 1011 | 000X XXXX |

| short     | 1100 1100 | 000X XXXX |

#### Remote-sensor transistor manufacturers

| Manufacturer | Model Number   |

|--------------|----------------|

| Panasonic    | 2SB0709 2N3906 |

| Philips      | PMBT3906       |

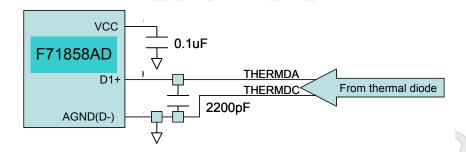

#### Monitor Temperature from "thermal diode"

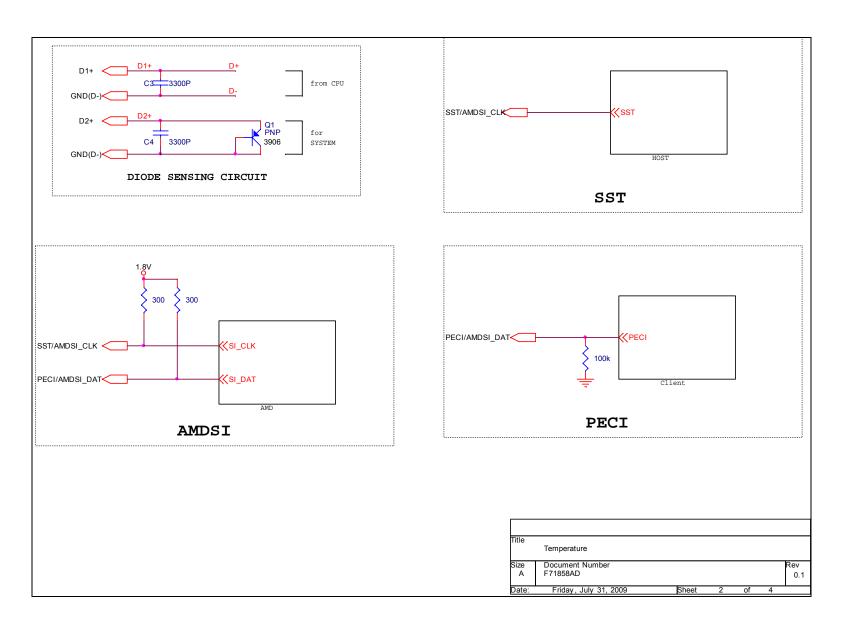

Also, if the CPU, GPU or external circuits provide thermal diode for temperature measurement, the F71858AD is capable to these situations. The build-in reference table is for PNP 2N3906 transistor, and each different kind of thermal diode should be matched with specific margin and BJT gain. The transistor is directly connected into temperature pins.

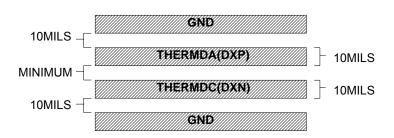

### **ADC Noise Filtering**

The ADC is integrating type with inherently good noise rejection. Micro-power operation places constraints on high-frequency noise rejection; therefore, careful PCB board layout and suitable external filtering are required for high-accuracy remote measurement in electronically noisy environment. High frequency EMI is best filtered at D+ and D- with an external 2200pF or 3300PF capacitor. Too high capacitance may introduce errors due to the rise time of the switched current source. Nearly all noise sources tested cause the ADC measurement to be higher than the actual temperature, depending on the frequency and amplitude.

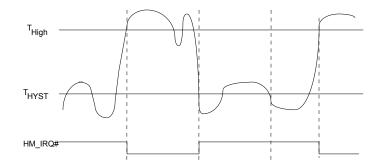

### Temperature HM\_IRQ Signal (HM\_IRQ# and PME#)

There are two mode of temperature HM IRQ function:

#### 1. Hysteresis mode:

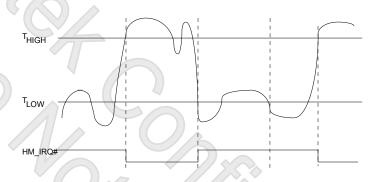

Over temperature event will trigger HM\_IRQ# that shown as figure. In hysteresis mode, when monitored temperature exceeds the high temperature threshold value, HM\_IRQ# will be asserted until the temperature goes below the hysteresis temperature.

### 2. High low limit mode: (default):

When in high low limit mode HM\_IRQ# for temperature is shown as figure. When monitored temperature exceeds the over-temperature threshold value, HM\_IRQ# will be asserted until the temperature goes below the low limit temperature.

### **Temperature PME#**

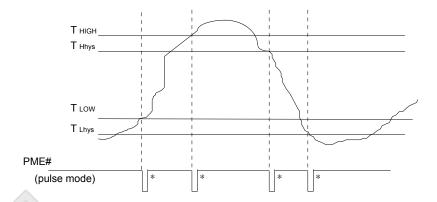

There are two mode of temperature PME# function:

#### 1. Hysteresis mode:

PME# interrupt for temperature is shown as figure. Temperature exceeding high limit (low limit) or going below high hysteresis (low hysteresis) will cause an interrupt if the previous interrupt has been reset by writing "1" all the interrupt Status Register.

\*Interrupt Reset when Interrupt Status Registers are written 1

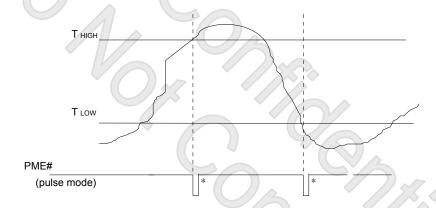

### 2. High low limit mode: (default):

PME# interrupt for temperature is shown as figure. Temperature exceeding high limit or going below low limit will cause an interrupt if the previous interrupt has been reset by writing "1" all the interrupt Status Register.

\*Interrupt Reset when Interrupt Status Registers are written 1

#### Fan speed count

Inputs are provided by the signals from fans equipped with tachometer outputs. The level of these signals should be set to TTL level, and maximum input voltage cannot be over 5V. If the input signals from the tachometer outputs are over the 5V, the external trimming circuit should be added to reduce the voltage to obtain the input specification.

Determine the fan counter according to the following equation:

$$Count = \frac{1.5 \times 10^6}{RPM}$$

In other words, the fan speed counter has been read from register, the fan speed can be evaluated by the following equation. As for fan, it would be best to use 2 pulses tachometer output per round.

$$RPM = \frac{1.5 \times 10^6}{Count}$$

### Fan speed control

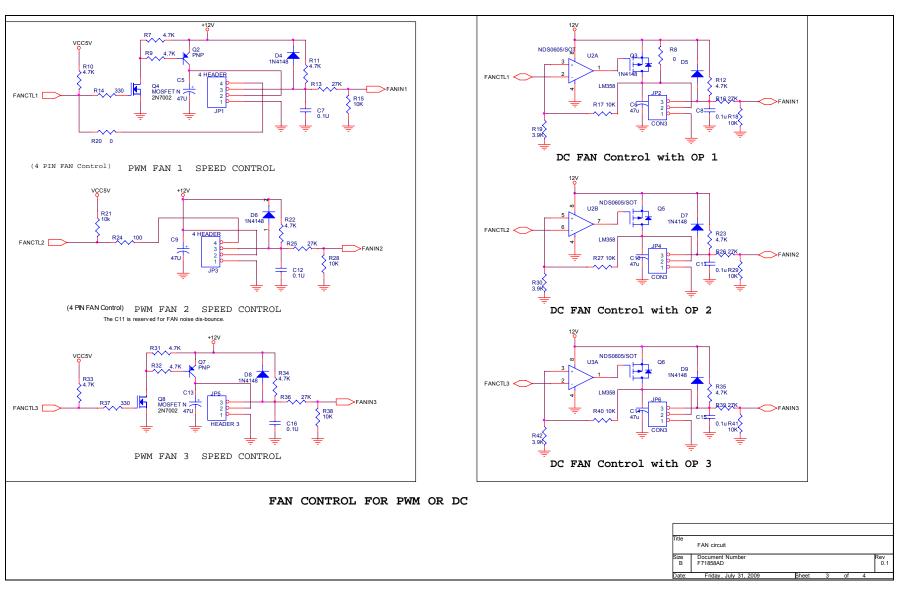

The F71858AD provides 2 fan speed control methods:

1. DAC FAN CONTROL

2. PWM DUTY CYCLE

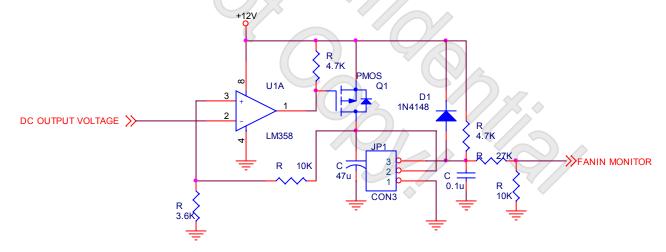

#### **DAC Fan Control**

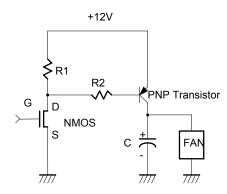

The range of DC output is 0~ VCC, controlled by 8-bit register. 1 LSB is about 0.013V (VCC=3.3V). The output DC voltage is amplified by external OP circuit, thus to reach maximum FAN OPERATION VOLTAGE, 12V. The output voltage will be given as followed:

And the suggested application circuit for DAC fan control would be:

#### **PWM duty Fan Control**

The duty cycle of PWM can be programmed by a 8-bit register. The default duty cycle is set to 40%, that is, the default 8-bit registers is set to 66h. The expression of duty can be represented as follows.

$$Duty\_cycle(\%) = \frac{Programmed\ 8bit\ Register\ Value}{255} \times 100\%$$

### Fan speed control mechanism

There are some modes to control fan speed and they are 1.Manual mode, 2.Stage auto mode, 3.Linear auto mode. More detail, please refer the description of registers.

#### Manual mode:

For manual mode, it generally acts as software fan speed control.

#### Stage auto mode:

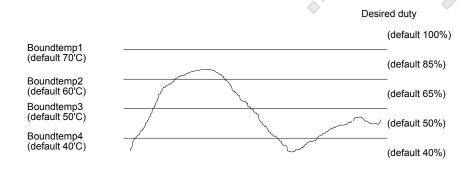

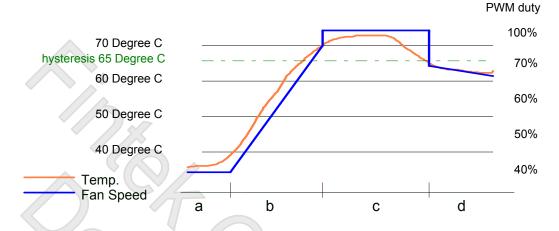

At this mode, the F71858AD provides automatic fan speed control related to positive or negative temperature variation of CPU/GPU or the system. The F71858AD can provide four temperature boundaries and five intervals, and each interval has its related fan speed count. All these values should be set by BIOS first. Take below figure as an example. When temperature boundaries are set as 40, 50, 60, and 70°C (each interval differs10°C), the related desired PWM duty for each interval is 100%, 85%, 65%, 50%, and 40%. When the temperature is within 50~60°C, the duty is 65%. Then, the F71858AD will adjust PWMOUT duty-cycle to meet the expected value. It can be said that the fan will be turned on with a specific speed set by BIOS and automatically controlled with the temperature variation. The F71858AD will take charge of all the fan speed control and does not require any software support.

There are two examples as below:

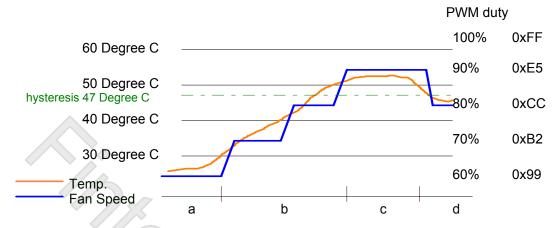

#### A. Stage auto mode (PWM Duty)

Set temperature as 60°C, 50°C, 40°C, 30°C and Duty as 100%, 90%, 80%, 70%, 60%

- a. Once temp. is under 30°C, the lowest fan speed keeps 60% PWM duty

- b. Once temp. is over 30°C,40°C,50°C, the fan speed will vary from 60% to 90% PWM duty and increase with temp. level.

- c. Once temp. keeps in 55°C, fan speed keeps in 90% PWM duty

- d. If set the hysteresis as 3°C (default 4°C), once temp reduces under 47°C, fan speed reduces to 80% PWM duty and stays there.

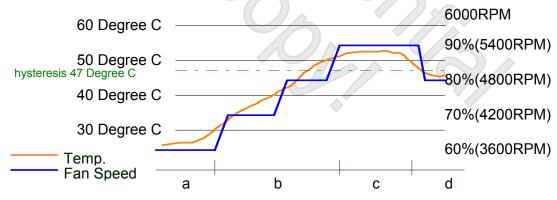

#### B. Stage auto mode (RPM%)

Set temperature as 60 °C, 50 °C, 40 °C, 30 °C and assume the Full Speed is 6000rpm, set 90% of full speed RPM(5400rpm), 80%(4800rpm), 70%(4200rpm), 60%(3600rpm) of full speed RPM

- a. Once temp. is under 30°C, the lowest fan speed keeps 60% of full speed (3600RPM).

- b. Once temp. is over 30°C,40°C,50°C, the fan speed will vary from 3600RPM to 5400RPM and increase with temp. level.

- c.Once temp. keeps in 55°C, fan speed keeps in 90% of full speed (5400RPM)

- d. If set the hysteresis as 3°C (default 4°C), once temp reduces under 47°C, fan speed

reduces to 4800RPM and stays there.

#### Linear auto mode:

Otherwise, F71858AD supports linear auto mode. Below two examples are to describe this mode. More detail, please refer the register description.

### A. Linear auto mode (PWM Duty)

Set temperature as 70°C, 60°C, 50°C, 40°C and Duty as 100%, 70%, 60%, 50%, 40%

- a. Once temp. is under 40°C, the lowest fan speed keeps 40% PWM duty

- b. Once temp. is over 40°C,50°C,60°C, the fan speed will vary from 40% to 70% PWM duty and linearly increase with temp. variation. The temp.-fan speed monitoring and flash interval is 1sec.

- c. Once temp. goes over 70°C, fan speed will directly increase to 100% PWM duty (full speed)

- d. If set the hysteresis as 5°C(default is 4°C), once temp reduces under 65°C (not 70°C), fan speed reduces from 100% PWM duty and decrease linearly with temp..

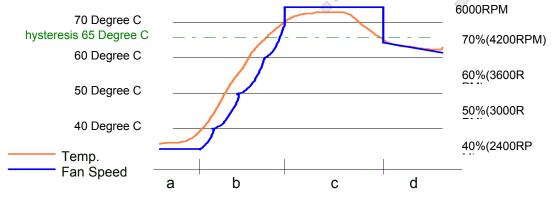

#### B. Linear auto mode (RPM%)

Set temperature as 70 °C, 60 °C, 50 °C, 40 °C and if full speed is 6000RPM, setting 100%, 70%, 60%, 50%, 40% of full speed.

- a. Once temp. is under 40°C, the lowest fan speed keeps 40% of full speed (2400RPM)

- b. Once temp. is over 40°C,50°C,60°C, the fan speed will vary from 40% to 70% of full

speed and almost linearly increase with temp. variation. The temp.-fan speed monitoring and flash interval is 1sec.

- c. Once temp. goes over 70 °C, fan speed will directly increase to full speed 6000RPM.

- d. If set the hysteresis as 5 °C, once temp reduces under 65 °C (not 70 °C), fan speed reduces from full speed and decrease linearly with temp..

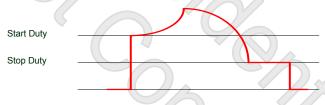

#### **PWMOUT Duty-cycle operating process**

In both "Manual RPM" and "Temperature RPM" modes, the F71858AD adjust PWMOUT duty-cycle according to current fan count and expected fan count. It will operate as follows:

- (1). When expected count is 0xFFF, PWMOUT duty-cycle will be set to 0x00 to turn off fan.

- (2). When expected count is 0x000, PWMOUT duty-cycle will be set to 0xFF to turn on fan with full speed.

- (3). If both (1) and (2) are not true,

When PWMOUT duty-cycle decrease to MIN\_DUTY(≠ 00h), obviously the duty-cycle will decrease to 00h next, When F71858AD up the fan speed will keep duty-cycle at start duty for 1.2 seconds. After that, the F71858AD starts to compare current fan count and expected count in order to increase or decrease its duty-cycle. This ensures that if there is any glitch during the period, the F71858AD will ignore it.

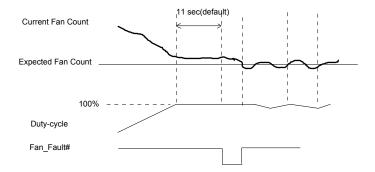

### FAN HM\_IRQ Signal (HM\_IRQ# and PME#)

Fan fault will be asserted when the fan speed doesn't meet the expected fan speed within a programmable period (default is 11 seconds) or when fan stops with respect to PWM duty-cycle which should be able to turn on the fan. There are two conditions may cause the FAN\_FAULT# event.

(1). When PWM\_Duty reaches 0xFF, the fan speed count can't reach the fan expected count in time.

(2). After the period of detecting fan full speed, when PWM\_Duty > Min. Duty, and fan count still in 0xFFF.

#### 6.5 LED function

The F71858AD provides two LEDs to indicate system state (S0, S3, and S5) which could be controlled via configuration register. System state could be set as (1) always 0 (2) oscillate 1Hz (3) oscillate 1/2 Hz and (4) always 1. When system is in S0, LED1 is default as 0 and LED2 as 1. When system is in S3, LED1 and LED2 oscillate 1Hz. When system is in S5, LED1 is default as 1 and LED2 as 0.

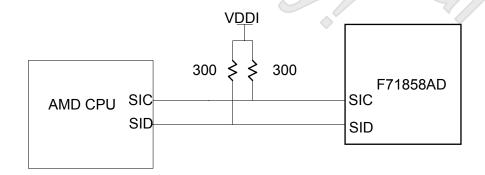

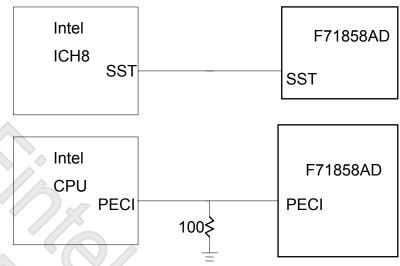

### 6.6 AMD TSI and Intel SST PECI Function

The F71858AD provides Intel SST/PECI/AMD TSI interfaces for new generational CPU temperature sensing. There are SCL and SDA signals for temperature reading from AMD CPU via TSI interface. The SCL signal is for clocking usage, and other is for data transferring. More detail please refer to the register description.

In Intel SST and PECI interfaces, the F71858AD can connect to CPU/SST directly. The F71858AD can read the temperature data from CPU, than the fan control machine of F71858AD can implement the Fan to cool down CPU temperature. As same as PECI, chipset can get information

from F71858AD including CPU temperature, system temperature (F71858AD provides D+/D- for system temperature sensing), fan speed status by SST. The application circuit is as below. More detail please refer to the register description.

## 6.7 Watchdog Timer Function

Watch dog timer is provided for system controlling. If time-out can trigger one signal to high/low level/pulse, the signal is depended on register setting.

The time unit has two ways from 1sec or 60sec. In pulse mode, there are four pulse widths can be selected (1ms/25ms/125ms/5sec). Please refer to the device register description for detail.

## 7. Register Description

### 7.1 Global Control Registers

The configuration register is used to control the behavior of the corresponding devices. To configure the register, using the index port to select the index and then writing data port to alter the parameters. The default index port and data port are 0x4E and 0x4F respectively. To enable configuration, the entry key 0x87 must be written to the index port. To disable configuration, write exit key 0x78 twice or key 0xaa once to the index port. Following is an example to enable configuration and disable configuration by using debug.

-o 4e 87

-o 4e 87 ( enable configuration )

-o 4e aa ( disable configuration )

#### 7.1.1 Software Reset Register — Index 02h

| Bit | Name     | R/W | Default | Description                                                    |

|-----|----------|-----|---------|----------------------------------------------------------------|

| 7-1 | Reserved | /-  | 1 /-/   | Reserved                                                       |

| 0   | SOFT_RST | R/W | 0       | Write 1 to reset the register and device powered by VDD (VCC). |

#### 7.1.2 Logic Device Number Register — Index 07h

| Bit | Name | R/W | Default | Description                                                                                            |

|-----|------|-----|---------|--------------------------------------------------------------------------------------------------------|

|     |      |     |         | 00h: Select KBC device configuration registers. 01h: Select PME & ACPI device configuration registers. |

| 7-0 | LDN  | R/W | 00h     | 02h: Select hardware monitor device configuration registers.                                           |

|     |      |     |         | 03h: Select GPIO device configuration registers. 04h: Select WDT device configuration registers.       |

#### 7.1.3 Chip ID Register — Index 20h

| Bit | Name     | R/W | Default | Description            |

|-----|----------|-----|---------|------------------------|

| 7-0 | CHIP_ID1 | R   | 09h     | Chip ID 1 of F71858AD. |

#### 7.1.4 Chip ID Register — Index 21h

| Bit | Name     | R/W | Default | Description           |

|-----|----------|-----|---------|-----------------------|

| 7-0 | CHIP_ID2 | R   | 03h     | Chip ID2 of F71858AD. |

#### 7.1.5 Vendor ID Register — Index 23h

| Bit | Name       | R/W | Default | Description                    |

|-----|------------|-----|---------|--------------------------------|

| 7-0 | VENDOR_ID1 | R   | 19h     | Vendor ID 1 of Fintek devices. |

#### 7.1.6 Vendor ID Register — Index 24h

| Bit | Name       | R/W | Default | Description                    |

|-----|------------|-----|---------|--------------------------------|

| 7-0 | VENDOR_ID2 | R   | 34h     | Vendor ID 2 of Fintek devices. |

#### 7.1.7 Port Select Register — Index 25h

| Bit | Name       | R/W | Default | Description                                                                                                                                       |

|-----|------------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | Reserved   | -   | -       | Reserved.                                                                                                                                         |

| 4   | PORT_4E_EN | R/W |         | The port could be changed by writing this register.  0: Configuration register port is 2E/2F.  1: Configuration register port is 4E/4F. (Default) |

| 3-0 | Reserved   | -   | 1       | Reserved.                                                                                                                                         |

### 7.1.8 Select KB/MO Wake Up Register — Index 27h (Powered by VBAT)

| Bit | Name          | R/W | Default | Description                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DIS_WAKEUP    | R/W | 0       | 0: enable KB/MO wakeup function.<br>1: disable KB/MO wakeup function                                                                                                                                                                                                                                                                                            |

| 6   | VSBOK_HYS_DIS | R/W | 0       | Enable VSBOK detect hysteresis.     Disable VSBOK detect hysteresys.                                                                                                                                                                                                                                                                                            |

| 5   | VSBOK_LVL_SEL | R/W |         | 0: VSB3V power good level is 2.8V and not good level is 2.5V.  1: VSB3V power good level is 3.05V and not good level is 2.95V.  By VSBOK_HYS_DIS and VSBOK_LVL_SEL, RSMRST# falling edge could be determined:  00: when VSB3V is lower than 2.5V.  01: when VSB3V is lower than 2.95V.  10: when VSB3V is lower than 2.8V.  11: when VSB3V is lower than 3.05V. |

| 4   | Reserved      | -   | 0       | Reserved.                                                                                                                                                                                                                                                                                                                                                       |

| 3   | KEY_SEL_ADD   | R/W | 0       | This bit is added to add more wakeup key function.                                                                                                                                                                                                                                                                                                              |

| 2   | MO_SEL        | R/W | 0       | Select mouse Key to wakeup host<br>0: click mouse key<br>1:any mouse key                                                                                                                                                                                                                                                                                        |

|     |         |     |    | This registers sele | ect the keyboa    | rd wake up key. Accompanying with |

|-----|---------|-----|----|---------------------|-------------------|-----------------------------------|

|     |         |     |    | KEY_SEL_ADD, the    | ere are eight wak | eup keys:                         |

|     |         |     |    | KEY_SEL_ADD         | KEY_SEL           | Wakeup Key                        |

|     |         |     |    | 0                   | 00                | CTRL + ESC                        |

|     |         |     |    | 0                   | 01                | CTRL + F1                         |

|     |         |     |    | 0                   | 10                | CTRL + USER_WAKEUP_CODE           |

| 1-0 | KEY_SEL | R/W | 00 |                     |                   | (SPACE)                           |

|     |         |     |    | 0                   | 11                | Any Key                           |

|     |         |     |    | 1                   | 00                | Windows Wakeup                    |

|     |         |     |    | 1                   | 01                | Windows Power                     |

|     |         | 2/2 | 0/ | 1                   | 10                | CTRL + Alt + USER_WAKEUP_CODE     |

|     |         |     | 1  |                     |                   | (SPACE)                           |

|     |         |     |    |                     | 11                | USER_WAKEUP_CODE (SPACE)          |

### 7.1.9 Multi-Function Select Register 1 — Index 28h (Powered by VSB3V)

|     | india randon cocci region i mask ten (regional sy rezer) |     |         |                                                                                                                                                                |  |  |  |

|-----|----------------------------------------------------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Name                                                     | R/W | Default | Description                                                                                                                                                    |  |  |  |

| 7   | Reserved                                                 | -   | (-)     | Reserved.                                                                                                                                                      |  |  |  |

| 6   | GPIO03_EN                                                | R/W |         | RSTIN#/GPIO03 Function Select. 0: Pin function is RSTIN#. 1: Pin function is GPIO03.                                                                           |  |  |  |

| 5-4 | GPIO02_SEL                                               | R/W |         | FANIN4/SST/AMDTSI_CLK/GPIO02 Function Select. 00: Pin function is FANIN4. 01: Pin function is SST. 10: Pin function is AMDTSI_CLK. 11: Pin function is GPIO02. |  |  |  |

| 3   | Reserved                                                 | -   | -       | Reserved.                                                                                                                                                      |  |  |  |

| 2   | GPIO01_EN                                                | R/W | 0       | FANIN3/GPIO01 Function Select. 0: Pin function is FANIN3. 1: Pin function is GPIO01.                                                                           |  |  |  |

| 1-0 | GPIO00_SEL                                               | R/W |         | PECI/AMDTSI_DAT/GPI000 Function Select. 00: Pin function is PECI. 01: Reserved. 10: Pin function is AMDTSI_DAT. 11: Pin function is GPI000.                    |  |  |  |

#### 7.1.10 Multi-Function Select Register 2 — Index 29h (Powered by VSB3V)

| Bit | Name      | R/W  | Default  | Description                                          |

|-----|-----------|------|----------|------------------------------------------------------|

|     |           |      |          | LED2/GPIO07 Function Select.                         |

| 7   | GPIO07_EN | R/W  | 0        | 0: Pin function is LED2.                             |

|     |           |      |          | 1: Pin function is GPIO07.                           |

|     |           |      |          | LED1/GPIO06 Function Select.                         |

| 6   | GPIO06_EN | R/W  | 0        | 0: Pin function is LED1.                             |

|     |           |      |          | 1: Pin function is GPIO06.                           |

|     |           |      |          | PCIRST5#/GPIO05 Function Select.                     |

| 5   | GPIO05_EN | R/W  | 0        | 0: Pin function is PCIRST5#.                         |

|     |           |      |          | 1: Pin function is GPIO05.                           |

|     |           |      |          | PCIRST4#/GPIO04 Function Select.                     |

| 4   | GPIO04_EN | R/W  | 0        | 0: Pin function is PCIRST4#.                         |

|     |           | 7,33 |          | 1: Pin function is GPIO04.                           |

| 3-2 | Reserved  | (-/. | 5-       | Reserved.                                            |

|     |           |      | V//      | Keyboard Interface and GPIO Function Select.         |

| 1   | KB_GP_EN  | R/W  | 0        | 0: Pin 41 and 42 are KCLK and KDATA respectively.    |

|     |           |      | Ĭ        | 1: Pin 41 and 42 are GPIO10 and GPIO11 respectively. |

|     |           |      |          | Mouse Interface and GPIO Function Select.            |

| 0   | MO_GP_EN  | R/W  | <b>0</b> | 0: Pin 43 and 44 are MCLK and MDATA respectively.    |

|     |           |      |          | 1: Pin 43 and 44 are GPIO12 and GPIO13 respectively. |

## 7.2 KBC Registers

## 7.2.1 Logic Device Number Register

Logic Device Number Register — Index 07H

| Bit | Name | R/W | Default | Description                                                                                                                                                                                                                                                          |

|-----|------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | LDN  | R/W | 00h     | 00h: Select KBC device configuration registers. 01h: Select PME & ACPI device configuration registers. 02h: Select hardware monitor device configuration registers. 03h: Select GPIO device configuration registers. 04h: Select WDT device configuration registers. |

#### 7.2.2 KBC Configuration Registers

KBC Device Enable Register — Index 30h

| NDC D | ABC Device Lilable Register — Index 3011 |     |         |                                   |  |  |  |  |

|-------|------------------------------------------|-----|---------|-----------------------------------|--|--|--|--|

| Bit   | Name                                     | R/W | Default | Description                       |  |  |  |  |

| 7-1   | Reserved                                 | ı   | -       | Reserved                          |  |  |  |  |

| 0     | KBC_EN                                   | R/W | 1       | 0: disable KBC.<br>1: enable KBC. |  |  |  |  |

#### Base Address High Register — Index 60h

| Bit | Name         | R/W | Default | Description                  |

|-----|--------------|-----|---------|------------------------------|

| 7-0 | BASE_ADDR_HI | R/W | 00h     | The MSB of KBC base address. |

#### Base Address Low Register — Index 61h

| Bit | Name         | R/W | Default | Description                  |

|-----|--------------|-----|---------|------------------------------|

| 7-0 | BASE_ADDR_LO | R/W | 60h     | The LSB of KBC base address. |

#### Keyboard IRQ Channel Enable Register — Index 70h

| Bit | Name     | R/W | Default | Description                          |

|-----|----------|-----|---------|--------------------------------------|

| 7-6 | Reserved | -   | -       | Reserved.                            |

| 0   | ENKBCIRQ | R/W | 1       | Enable the IRQ channel for Keyboard. |

#### Mouse IRQ Channel Enable Register — Index 72h

| Bit | Name     | R/W | Default      | Description                       |

|-----|----------|-----|--------------|-----------------------------------|

| 7-6 | Reserved | 5 4 | <b>)</b> - ~ | Reserved.                         |

| 0   | ENMOCIRQ | R/W | 1/_          | Enable the IRQ channel for Mouse. |

#### Auto Swap Register — Index FEh (Powered by VBAT)

| Bit | Name        | R/W | Default | Description                                                                                                                                                            |

|-----|-------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTO_DET_EN | R/W | 0       | 0: disable auto detect keyboard/mouse swap.  1: enable auto detect keyboard/mouse swap.                                                                                |

| 6-5 | Reserved    | 1   | (-)     | Reserved.                                                                                                                                                              |

| 4   | KB_MO_SWAP  | R/W | 0       | O: Keyboard/mouse does not swap.  1: Keyboard/mouse swap.  This bit is set/clear by hardware if AUTO_DET_EN is set to "1". Users could also program this bit manually. |

| 3-0 | Reserved    | 1   | -       | Reserved                                                                                                                                                               |

#### User Wakeup Code Register — Index FFh (Powered by VBAT)

| Bit | Name           | R/W   | Default | Description                                        |

|-----|----------------|-------|---------|----------------------------------------------------|

| 7-0 | USER_WAKEUP_CO | O R/W | 29h     | This is used define walkers and a Default is areas |

| 7-0 | DE             | IN/VV | 2911    | This is user define wakeup code. Default is space. |

## 7.3 ACPI and PME Registers

### 7.3.1 Logic Device Number Register

#### Logic Device Number Register — Index 07H

| Bit | Name | R/W | Default | Description                                                                                                                                                   |

|-----|------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      |     |         | 00h: Select KBC device configuration registers. 01h: Select PME & ACPI device configuration registers.                                                        |

| 7-0 | LDN  | R/W | 00h     | 02h: Select hardware monitor device configuration registers. 03h: Select GPIO device configuration registers. 04h: Select WDT device configuration registers. |

### 7.3.2 ACPI and PME Configuration Registers

#### Device Enable Register — Index 30h

| Bit | Name     | R/W | Default | Description                    |

|-----|----------|-----|---------|--------------------------------|

| 7-1 | Reserved |     |         | Reserved                       |

| 0   | PME_EN   | R/W | 0       | 0: disable PME. 1: enable PME. |

#### PME Event Enable Register — Index F0h

| Bit | Name       | R/W | Default | Description                                                                                                     |

|-----|------------|-----|---------|-----------------------------------------------------------------------------------------------------------------|

| 7   | WDT_PME_EN | R/W | 0       | Watchdog Timer PME event enable. 0: disable Watchdog Timer PME event. 1: enable Watchdog Timer PME event.       |

| 6   | MS_PME_EN  | R/W |         | PS/2 mouse PME event enable. 0: disable PS/2 mouse PME event. 1: enable PS/2 mouse PME event.                   |

| 5   | KB_PME_EN  | R/W | 0       | PS/2 keyboard PME event enable. 0: disable PS/2 keyboard PME event. 1: enable PS/2 keyboard PME event.          |

| 4   | GP_PME_EN  | R/W | 0       | GPIO PME event enable. 0: disable GPIO PME event. 1: enable GPIO PME event.                                     |

| 3-1 | Reserved   | -   | -       | Reserved                                                                                                        |

| 0   | HM_PME_EN  | R/W | 0       | Hardware Monitor PME event enable. 0: disable Hardware Monitor PME event. 1: enable Hardware Monitor PME event. |

#### PME Event Status Register — Index F1h

| Bit | Name       | R/W  | Default | Description                                                                                                                                                        |

|-----|------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WDT_PME_ST | R/WC | -       | Watchdog Timer PME event status. 0: Watchdog Timer has no PME event. 1: Watchdog Timer has a PME event to assert. Write 1 to clear to be ready for next PME event. |

| 6   | MS_PME_ST | R/W  | 0 | PS/2 mouse PME event status. 0: PS/2 mouse has no PME event. 1: PS/2 mouse has a PME event to assert. Write 1 to clear to be ready for next PME event.                   |

|-----|-----------|------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | KB_PME_ST | R/W  | 0 | PS/2 keyboard PME event status. 0: PS/2 keyboard has no PME event. 1: PS/2 keyboard has a PME event to assert. Write 1 to clear to be ready for next PME event.          |

| 4   | GP_PME_ST | R/WC | - | GPIO PME event status. 0: GPIO has no PME event. 1: GPIO has a PME event to assert. Write 1 to clear to be ready for next PME event.                                     |

| 3-1 | Reserved  | -    | - | Reserved                                                                                                                                                                 |

| 0   | HM_PME_ST | R/W  | 0 | Hardware Monitor PME event status. 0: Hardware Monitor has no PME event. 1: Hardware Monitor has a PME event to assert. Write 1 to clear to be ready for next PME event. |

#### ACPI Control Register — Index F4h

| Bit | Name         | R/W | Default | Description                                                                                                            |

|-----|--------------|-----|---------|------------------------------------------------------------------------------------------------------------------------|

| 7   | TS3          | R/W | 1 ()    | Set to 1 to enable keyboard or mouse can wakeup from S1 state, It must also set EN_KBCWAKEUP and EN_MOWAKEUP register. |

| 6-5 | Reserved     | -// | // -    | Reserved.                                                                                                              |

| 4   | ENKBWAKEUP   | R/W | 0       | 0:disable keyboard wakeup signal (PS_OUT#) 1:enable keyboard wakeup signal                                             |

| 3   | ENMOWAKEUP   | R/W | 0       | 0:disable mouse wakeup signal (PS_OUT#) 1:enable mouse wakeup signal                                                   |

| 2-1 | PWRCTRL      | R/W | 11      | The ACPI Control the PSON# to 00 : keep last state 10 : Always on 01 : Bypass mode. 11: Always off                     |

| 0   | VSB_PWR_LOSS | R/W | 0       | When VSB 3V comes, it will set to 1, and write 1 to clear it                                                           |

#### ACPI Control Register — Index F5h

| Bit | Name        | R/W | Default | Description                                                                                                                      |

|-----|-------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------|

| 7   | SEL_S3      | R/W |         | KBC S3 Signal Select 0: KBC enter S3 state if S3# is low (TS3 is 0) or TS3 is set. 1: KBC enter S3 state if VDD3V below 2.5V.    |

| 6   | Reserved    | -   | -       | Reserved                                                                                                                         |

| 5   | BYPASS_LRST | R/W | 1       | 0: Enable LRESET# de-bounce circuit (200us) for PCIRST# signal. 1: Disable LRESET# de-bounce circuit (200us) for PCIRST# signal. |

| 4   | RSTCON_EN   | R/W | 0       | 0: RSTCON# asserts via PWROK. 1: RSTCON# asserts via PCIRST#.                                                                    |

| 3-2 | DELAY       | R/W | 11      | The PWROK delay timing from VCC3VOK by following setting 00 : 100ms 01 : 200ms 10 : 300ms 11 : 400ms                             |

| 1 | Bypass_db | R/W | 0 | BYPASS the S3#/S4#/PSIN#/RSTIN# Pins.                                                |

|---|-----------|-----|---|--------------------------------------------------------------------------------------|

| 0 | VINDB_EN  | R/W | 1 | 0: Disable RSTCON# 50ms de-bounce circuit. 1: Enable RSTCON# 50ms de-bounce circuit. |

#### ACPI Soft reset Register — Index F6h

| Bit | Name          | R/W | Default | Description                                   |

|-----|---------------|-----|---------|-----------------------------------------------|

| 7   | SOFT_RST_ACPI | W   | 0       | Software Reset to ACPI Set to 1 to reset ACPI |

| 6-0 | Reserved      | -   | -       | Reserved                                      |

#### ACPI reset enable Register — Index F7h

| Bit | Name       | R/W | Default | Description                                            |

|-----|------------|-----|---------|--------------------------------------------------------|

| 7-5 | Reserved   | 1   | -       | Reserved                                               |

| 4   | PCIRST5_EN | R/W | 1       | 0: Disable PCIRST5# output. 1: Enable PCIRST5# output. |

| 3   | PCIRST4_EN | R/W | 1       | 0: Disable PCIRST4# output. 1: Enable PCIRST4# output. |

| 2   | PCIRST3_EN | R/W | 1       | 0: Disable PCIRST3# output. 1: Enable PCIRST3# output. |

| 1   | PCIRST2_EN | R/W | 1       | 0: Disable PCIRST2# output. 1: Enable PCIRST2# output. |

| 0   | PCIRST1_EN | R/W | 1       | 0: Disable PCIRST1# output. 1: Enable PCIRST1# output. |

### ACPI reset data Register — Index F8h

| Bit | Name        | R/W | Default | Description                                 |

|-----|-------------|-----|---------|---------------------------------------------|

| 7-5 | Reserved    | -   | -       | Reserved                                    |

| 4   | PCIRST5_DAT | R/W | 0       | Write "1" to output PCIRST5# 2ms low pulse. |

| 3   | PCIRST4_DAT | R/W | 0       | Write "1" to output PCIRST4# 2ms low pulse. |

| 2   | PCIRST3_DAT | R/W | 0       | Write "1" to output PCIRST3# 2ms low pulse. |

| 1   | PCIRST2_DAT | R/W | 0       | Write "1" to output PCIRST2# 2ms low pulse. |

| 0   | PCIRST1_DAT | R/W | 0       | Write "1" to output PCIRST1# 2ms low pulse. |

#### LED S0 status Register — Index F9h

| Bit | Name     | R/W | Default | Description                                                                                                     |

|-----|----------|-----|---------|-----------------------------------------------------------------------------------------------------------------|

| 7   | Phase    | R/W | 0       | When bit 7 is the same of the bit 3, LED2 oscillate phase is same with LED1.                                    |

| 6   | Reserved | -   | -       | Reserved                                                                                                        |

| 5-4 | LED2_S0  | R/W |         | Indicate LED2 response when system is in S0 00:LED assert 0 01: oscillate 1Hz 10: oscillate 1/2Hz 11: tri-state |

| 3   | Phase    | R/W | 0       | When bit 7 is same with bit 3, LED2 oscillate phase is same with LED1.                                          |

| 2   | Reserved | -   | -       | Reserved                                                                                                        |

|     |         |   |       | Indicate LED1 response when system in S0 state |

|-----|---------|---|-------|------------------------------------------------|

|     |         |   |       | 00:LED assert 0                                |

| 1-0 | LED1_S0 | W | 2'b00 | 01: oscillate 1Hz                              |

|     |         |   |       | 10: oscillate 1/2Hz                            |

|     |         |   |       | 11: tri-state                                  |

#### LED S3/S5 status Register — Index FAh

| Bit | Name    | R/W | Default | Description                                                                                                         |  |

|-----|---------|-----|---------|---------------------------------------------------------------------------------------------------------------------|--|

| 7-6 | LED2_S5 | R/W | 2'b00   | Indicate LED2 response when system in S5 state 00:LED assert 0 01: oscillate 1Hz 10: oscillate 1/2Hz 11: tri-state  |  |

| 5-4 | LED2_S3 | R/W | 2'b01   | Indicate LED2 response when system in S3 state 00:LED assert 0 01: oscillate 1Hz 10: oscillate 1/2Hz 11: tri-state  |  |

| 3-2 | LED1_S5 | R/W |         | Indicate LED1 response when system in S5 state 00:LED assert 0 01: oscillate 1Hz 10: oscillate 1/2Hz 11: tri-state. |  |

| 1-0 | LED1_S3 | W   | 2'b01   | Indicate LED1 response when system in S3 state 00:LED assert 0 01: oscillate 1Hz 10: oscillate 1/2Hz 11: tri-state  |  |

#### PWOK & PS\_ON Control Register — Index FBh

| Bit | Name        | R/W | Default | Description                                                                |  |

|-----|-------------|-----|---------|----------------------------------------------------------------------------|--|