# 650 kHz/1.3 MHz, 4 A, Step-Up, PWM, DC-to-DC Switching Converter

Data Sheet ADP1614

#### **FEATURES**

Adjustable current limit, up to 4 A

2.5 V to 5.5 V input voltage range

650 kHz or 1.3 MHz fixed frequency option

Adjustable output voltage, up to 20 V

Adjustable soft start

Undervoltage lockout

Thermal shutdown

3 mm × 3 mm, 10-lead LFCSP

Supported by ADIsimPower design tool

#### **APPLICATIONS**

TFT LCD bias supplies

Portable applications

Industrial/instrumentation equipment

#### **GENERAL DESCRIPTION**

The ADP1614 is a step-up, dc-to-dc switching converter with an integrated power switch capable of providing an output voltage as high as 20 V. The ADP1614 is available with a pinadjustable current limit that is set via an external resistor. The boost switching frequency is fixed to either 650 kHz or 1.3 MHz. With a package height of 0.8 mm, the ADP1614 is optimal for space constrained applications, such as portable devices or thin film transistor (TFT) liquid crystal displays (LCDs).

The ADP1614 operates in current-mode pulse-width modulation (PWM) with up to 94% efficiency. Adjustable soft start prevents inrush currents when the part is enabled. The PWM current-mode architecture allows excellent transient response, easy noise filtering, and the use of small, cost-saving external inductors and capacitors. Other key features include undervoltage lockout (UVLO), thermal shutdown (TSD), and logic controlled enable.

The ADP1614 is available in a Pb-free, 10-lead lead frame chip scale package (LFCSP).

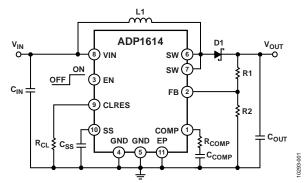

#### **TYPICAL APPLICATIONS CIRCUIT**

Figure 1. Step-Up Regulator Configuration

# **TABLE OF CONTENTS**

| reatures                                    |

|---------------------------------------------|

| Applications                                |

| General Description                         |

| Typical Applications Circuit                |

| Revision History                            |

| Specifications                              |

| Absolute Maximum Ratings                    |

| Thermal Resistance                          |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Theory of Operation10                       |

| Current-Mode PWM Operation1                 |

| Adjustable Current Limit1                   |

| Frequency Selection                         |

|   | Soft Start                               | 11 |

|---|------------------------------------------|----|

|   | Thermal Shutdown (TSD)                   | 11 |

|   | Undervoltage Lockout (UVLO)              | 11 |

|   | Shutdown Mode                            | 11 |

| A | pplications Information                  | 12 |

|   | ADIsimPower Design Tool                  | 12 |

|   | Setting the Output Voltage               | 12 |

|   | Inductor Selection                       | 12 |

|   | Choosing the Input and Output Capacitors | 13 |

|   | Diode Selection                          | 13 |

|   | Loop Compensation                        | 13 |

|   | Soft Start Capacitor                     | 14 |

| P | CB Layout Guidelines                     | 15 |

| С | Outline Dimensions                       | 16 |

|   | Ordering Guide                           | 16 |

#### **REVISION HISTORY**

6/12—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{\rm IN}$  = 3.6 V, unless otherwise noted. Minimum and maximum values are guaranteed for  $T_{\rm J}$  = -40°C to +125°C. Typical values specified are at T<sub>J</sub> = 25°C. All limits at temperature extremes are guaranteed by correlation and characterization using standard statistical quality control (SQC), unless otherwise noted.

Table 1.

| Parameter                               | Symbol             | Test Conditions/Comments                                                              | Min             | Тур   | Max       | Unit     |

|-----------------------------------------|--------------------|---------------------------------------------------------------------------------------|-----------------|-------|-----------|----------|

| SUPPLY                                  |                    |                                                                                       |                 |       |           |          |

| Input Voltage                           | V <sub>IN</sub>    |                                                                                       | 2.5             |       | 5.5       | V        |

| Quiescent Current                       |                    |                                                                                       |                 |       |           |          |

| Shutdown                                | I <sub>QSHDN</sub> | $V_{EN} = 0 V$                                                                        |                 | 0.25  | 1.5       | μΑ       |

| Nonswitching State                      | $I_Q$              | $V_{FB} = 1.3 \text{ V}, f_{SW} = 1.3 \text{ MHz} \text{ and } 650 \text{ kHz}$       |                 | 700   | 1100      | μΑ       |

| Switching State <sup>1</sup>            | I <sub>QSW</sub>   | f <sub>sw</sub> = 1.3 MHz, no load                                                    |                 | 5.5   | 7         | mA       |

|                                         |                    | $f_{SW} = 650 \text{ kHz}$ , no load                                                  |                 | 3     | 4.5       | mA       |

| Enable Pin Bias Current                 | I <sub>EN</sub>    | $V_{EN} = 3.6 \text{ V}$                                                              |                 | 3.4   | 7         | μΑ       |

| UNDERVOLTAGE LOCKOUT (UVLO)             |                    |                                                                                       |                 |       |           | -        |

| Undervoltage Lockout Threshold          |                    | V <sub>IN</sub> rising                                                                |                 | 2.33  | 2.5       | V        |

| -                                       |                    | V <sub>IN</sub> falling                                                               | 2.0             | 2.20  |           | V        |

| OUTPUT                                  |                    |                                                                                       |                 |       |           |          |

| Output Voltage                          | V <sub>OUT</sub>   |                                                                                       | V <sub>IN</sub> |       | 20        | V        |

| Load Regulation                         |                    | $V_{OUT} = 10 \text{ V}, I_{LOAD} = 1 \text{ mA to } 1 \text{ A}$                     |                 | 0.005 |           | mV/mA    |

| REFERENCE                               |                    |                                                                                       |                 |       |           |          |

| Feedback Voltage                        | $V_{FB}$           |                                                                                       | -1.6%           | 1.245 | +1.6%     | V        |

| Line Regulation                         | 1                  | $V_{IN} = 2.5 \text{ V to } 5.5 \text{ V}$                                            | 11075           | 0.02  | 0.2       | %/V      |

| ERROR AMPLIFIER                         |                    |                                                                                       |                 |       |           | , -, -   |

| Transconductance                        | G <sub>MEA</sub>   | $\Delta I = 4 \mu A$                                                                  |                 | 150   |           | μA/V     |

| Voltage Gain                            | Av                 | Δ μ                                                                                   |                 | 80    |           | dB       |

| FB Pin Bias Current                     | 1,10               | V <sub>FB</sub> = 1.245 V                                                             |                 | 1     | 50        | nA       |

| SWITCH (SW)                             |                    | 110 112 10 1                                                                          |                 | •     |           |          |

| On Resistance                           | R <sub>DSON</sub>  | I <sub>sw</sub> = 1.0 A                                                               |                 | 50    | 100       | mΩ       |

| Leakage Current                         | NDSON              | $V_{SW} = 20 \text{ V}$                                                               |                 | 0.1   | 100       | μΑ       |

| Peak Current Limit <sup>2</sup>         |                    | $R_{CL} = 154 \text{ k}\Omega$ , duty cycle = 70%                                     | 0.95            | 1.3   | 1.65      | Α        |

| Maximum Peak Current Limit <sup>3</sup> |                    | $R_{CL} = 61.9 \text{ k}\Omega$ , $V_{IN} = 3.6 \text{ V}$ , $V_{OUT} = 15 \text{ V}$ | 0.55            | 4     | 1.03      | A        |

| CLRES VOLTAGE <sup>4</sup>              |                    | $I_{\text{CLRES}} = 5  \mu \text{A}$                                                  | 1.225           | 1.27  | 1.315     | V        |

| CERES VOLINGE                           |                    | $I_{CLRES} = 3 \mu A$                                                                 | 1.18            | 1.22  | 1.25      | v        |

| OSCILLATOR                              |                    | ictres – 20 µrt                                                                       | 1.10            | 1,22  | 1.23      | <b>V</b> |

| Oscillator Frequency                    | f <sub>sw</sub>    | ADP1614ACPZ-1.3-R7                                                                    | 1.1             | 1.3   | 1.4       | MHz      |

| Oscillator Frequency                    | 12//               | ADP1614ACPZ-650-R7                                                                    | 500             | 650   | 720       | kHz      |

| Maximum Duty Cycle                      | D <sub>MAX</sub>   | COMP = open, $V_{FB} = 1 \text{ V}$ , $f_{SW} = 1.3 \text{ MHz}$ and 650 kHz          | 88              | 92    | 720       | %        |

| EN LOGIC THRESHOLD                      | DIVIAN             | $V_{IN} = 2.5 \text{ V to } 5.5 \text{ V}$                                            | +               |       |           | / -      |

| Input Voltage Low                       | VIL                |                                                                                       |                 |       | 0.3       | V        |

| Input Voltage High                      | VIH                |                                                                                       | 1.6             |       |           | v        |

| SOFT START (SS)                         | - ""               |                                                                                       | +               |       |           | -        |

| Charging Current                        | I <sub>SS</sub>    | $V_{SS} = 0 V$                                                                        | 3.4             | 5.5   | 7         | μΑ       |

| Pin Voltage                             | V <sub>SS</sub>    | V <sub>55</sub> – 0 V<br>V <sub>FB</sub> = 1.3 V                                      | 1.17            | 1.23  | ,<br>1.29 | V        |

|                                         | V 33               | V10 1.5 V                                                                             | '''             | 1.23  | 1.27      |          |

| THERMAL SHUTDOWN                        |                    |                                                                                       | 1               |       |           |          |

| Thermal Shutdown Threshold              |                    |                                                                                       | 1               | 150   |           | °C       |

| Thermal Shutdown Hysteresis             |                    |                                                                                       |                 | 20    |           | °C       |

<sup>&</sup>lt;sup>1</sup> This parameter specifies the average current when the device switches internally with the SW pins (Pin 6 and Pin 7) floating.

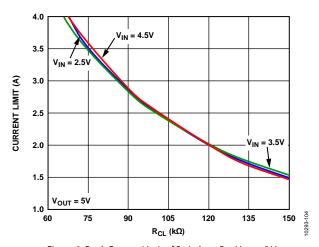

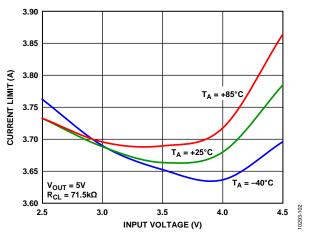

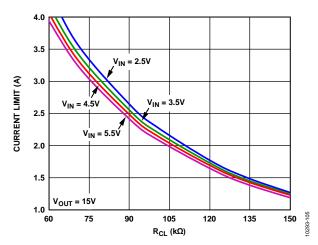

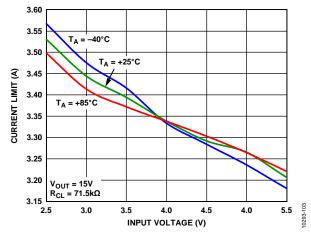

<sup>2</sup> Current limit is a function of duty cycle. For the adjustable current limit versions, it is also a function of the resistor on the CLRES pin. See Figure 9 through Figure 12.

<sup>&</sup>lt;sup>3</sup> Guaranteed by design.

<sup>&</sup>lt;sup>4</sup>The CLRES pin cannot be controlled with a current source. An equivalent resistance should be used.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating           |

|--------------------------------------|------------------|

| VIN, EN, FB to GND                   | -0.3 V to +6 V   |

| CLRES to GND                         | −0.3 V to VIN    |

| COMP to GND                          | 1.0 V to 1.6 V   |

| SS to GND                            | −0.3 V to +1.3 V |

| SW to GND                            | 21 V             |

| Operating Junction Temperature Range | −40°C to +125°C  |

| Storage Temperature Range            | −65°C to +150°C  |

| Soldering Conditions                 | JEDEC J-STD-020  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination.

#### THERMAL RESISTANCE

The junction-to-ambient thermal resistance  $(\theta_{JA})$  of the package is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. The  $\theta_{JA}$  is highly dependent on the application and board layout. In applications where high maximum power dissipation exists, attention to thermal board design is required. The value of  $\theta_{JA}$  may vary, depending on the printed circuit board (PCB) material, layout, and environmental conditions.

The boundary conditions for the thermal resistance of the ADP1614 are modeled under natural convection cooling at 25°C ambient temperature, JESD 51-9, and 1 W power input on a 4-layer board.

Table 3. Thermal Resistance<sup>1</sup>

| Package Type  | θ <sub>JA</sub> | θις  | Unit |

|---------------|-----------------|------|------|

| 10-Lead LFCSP | 47              | 7.22 | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal numbers per JEDEC standard JESD 51-9.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

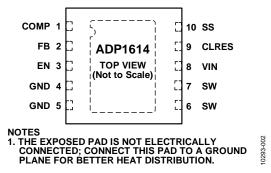

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | COMP     | Compensation Input. Connect a series resistor-capacitor network from COMP to GND to compensate the regulator.                                                                                              |

| 2       | FB       | Output Voltage Feedback Input. Connect a resistive voltage divider from the output voltage to FB to set the regulator output voltage.                                                                      |

| 3       | EN       | Enable Input. Drive EN low to shut down the regulator; drive EN high to turn on the regulator.                                                                                                             |

| 4, 5    | GND      | Ground.                                                                                                                                                                                                    |

| 6, 7    | SW       | Switching Output. Connect the power inductor from the input voltage to SW and connect the external rectifier from SW to the output voltage to complete the step-up converter.                              |

| 8       | VIN      | Main Power Supply Input. VIN powers the ADP1614 internal circuitry. Connect VIN to the input source voltage. Bypass VIN to GND with a 10 $\mu$ F or greater capacitor as close to the ADP1614 as possible. |

| 9       | CLRES    | Connect a resistor to GND to set the peak inductor current.                                                                                                                                                |

| 10      | SS       | Soft Start. A capacitor connected from SS to GND brings up the output slowly at power-up and reduces inrush current.                                                                                       |

| 11      | EP       | Exposed Die Attach Pad. The exposed pad is not electrically connected; connect this pad to a ground plane for better heat distribution.                                                                    |

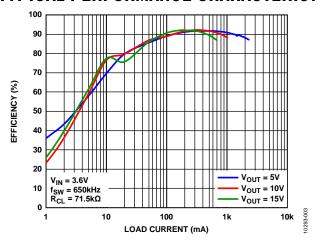

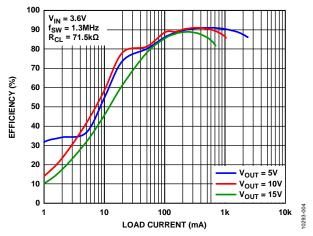

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Efficiency vs. Load Current,  $V_{IN} = 3.6 \text{ V}$ ,  $f_{SW} = 650 \text{ kHz}$

Figure 4. Efficiency vs. Load Current,  $V_{IN} = 3.6 \text{ V}$ ,  $f_{SW} = 1.3 \text{ MHz}$

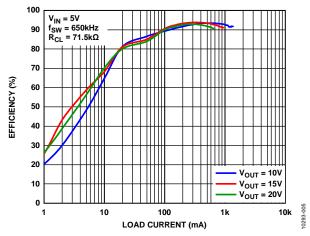

Figure 5. Efficiency vs. Load Current,  $V_{IN} = 5 V$ ,  $f_{SW} = 650 \text{ kHz}$

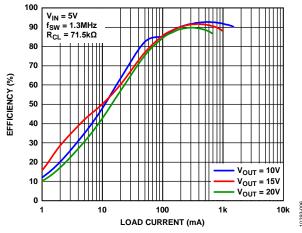

Figure 6. Efficiency vs. Load Current,  $V_{IN} = 5 V$ ,  $f_{SW} = 1.3 MHz$

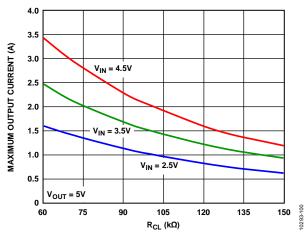

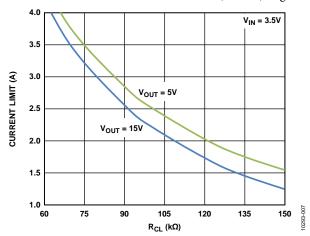

Figure 7. Typical Maximum Continuous Output Current vs.  $R_{CL}$ ,  $V_{OUT} = 5 V$

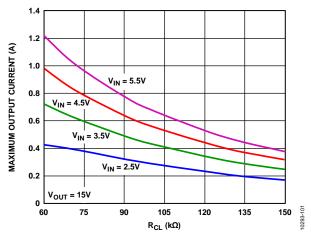

Figure 8. Typical Maximum Continuous Output Current vs.  $R_{CL}$ ,  $V_{OUT} = 15 \text{ V}$

Figure 9. Peak Current Limit of Switch vs.  $R_{CL}$ ,  $V_{OUT} = 5 V$

Figure 10. Peak Current Limit of Switch vs.  $V_{IN}$  over Temperature,  $V_{OUT} = 5 V$

Figure 11. Peak Current Limit of Switch vs.  $R_{CL}$ ,  $V_{OUT} = 15 V$

Figure 12. Peak Current Limit of Switch vs.  $V_{IN}$  over Temperature,  $V_{OUT} = 15 \text{ V}$

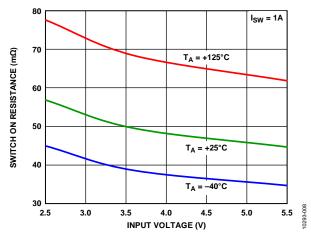

Figure 13. Switch On Resistance vs. Input Voltage

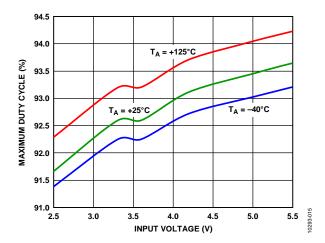

Figure 14. Maximum Duty Cycle vs. Input Voltage

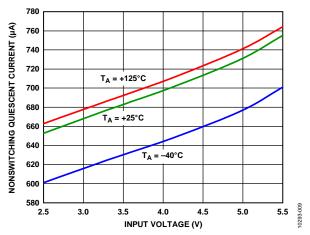

Figure 15. Nonswitching Quiescent Current vs. Input Voltage

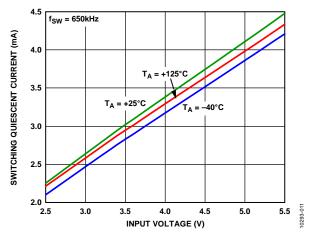

Figure 16. Switching Quiescent Current vs. Input Voltage, f<sub>SW</sub> = 650 kHz

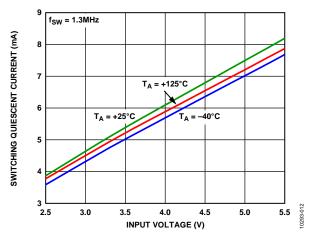

Figure 17. Switching Quiescent Current vs. Input Voltage, f<sub>SW</sub> = 1.3 MHz

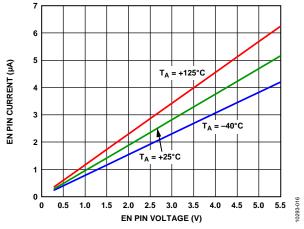

Figure 18. EN Pin Current vs. EN Pin Voltage

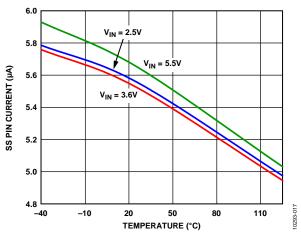

Figure 19. SS Pin Current vs. Temperature

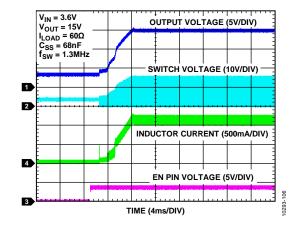

Figure 20. Startup,  $C_{SS} = 68 \text{ nF}$

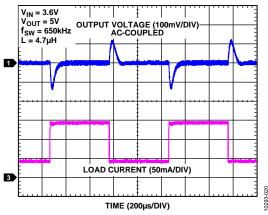

Figure 21. 50 mA to 150 mA Load Transient,  $V_{IN} = 3.6 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 650 \text{ kHz}$

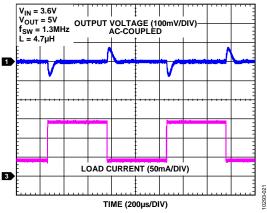

Figure 22. 50 mA to 150 mA Load Transient,  $V_{IN} = 3.6 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 1.3 \text{ MHz}$

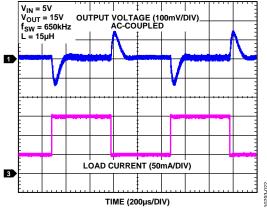

Figure 23. 50 mA to 150 mA Load Transient,  $V_{IN} = 5 \text{ V}$ ,  $V_{OUT} = 15 \text{ V}$ ,  $f_{SW} = 650 \text{ kHz}$

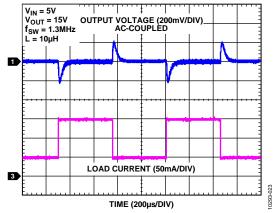

Figure 24. 50 mA to 150 mA Load Transient,  $V_{IN} = 5 \text{ V}$ ,  $V_{OUT} = 15 \text{ V}$ ,  $f_{SW} = 1.3 \text{ MHz}$

## THEORY OF OPERATION

The ADP1614 current-mode, step-up switching converter boosts a 2.5 V to 5.5 V input voltage to an output voltage as high as 20 V. The internal switch allows a high output current, and the 650 kHz/1.3 MHz switching frequency allows the use of tiny external components. The switch current is monitored on a pulse-by-pulse basis to limit the current to the value set by the R<sub>CL</sub> resistor on the CLRES pin.

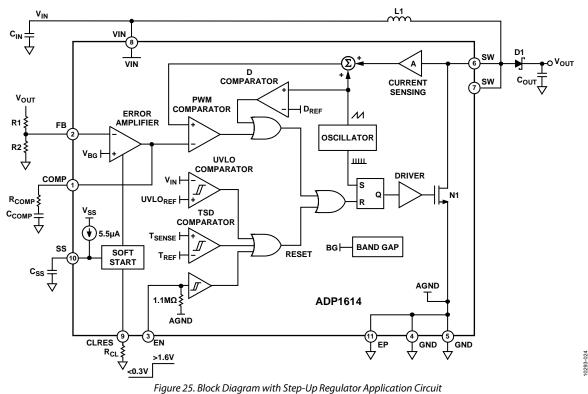

Figure 25. Block Diagram with Step-Up Regulator Application Circuit

#### **CURRENT-MODE PWM OPERATION**

The ADP1614 utilizes a current-mode PWM control scheme to regulate the output voltage over all load conditions. The output voltage is monitored at FB through a resistive voltage divider. The voltage at FB is compared with the internal 1.245 V reference by the internal transconductance error amplifier to create an error voltage at COMP. The current of the switch is internally measured and added to the stabilizing ramp. The resulting sum is compared with the error voltage at COMP to control the PWM modulator. This current-mode regulation system allows fast transient response while maintaining a stable output voltage. By selecting the proper resistor-capacitor network from COMP to GND, the regulator response is optimized for a wide range of input voltages, output voltages, and load conditions.

#### **ADJUSTABLE CURRENT LIMIT**

A key feature of the ADP1614 is a pin-adjustable peak current limit of up to 4 A (see Figure 9 to Figure 12 and Figure 26). This adjustable current limit allows the other external components to be selected specifically for the application. The current limit is set via an external resistor connected from Pin 9 (CLRES) to ground.

Figure 26. Peak Current Limit of Switch vs. R<sub>CL</sub>

#### **FREQUENCY SELECTION**

The ADP1614 is internally programmed to operate at either 650 kHz or 1.3 MHz. Operation of the ADP1614 at 650 kHz (ADP1614ACPZ-650-R7) optimizes the efficiency of the device, whereas operation of the ADP1614 at 1.3 MHz (ADP1614ACPZ-1.3-R7) enables the device to be used with smaller external components.

#### **SOFT START**

To prevent input inrush current to the converter when the part is enabled, connect a capacitor from SS to GND to set the soft start period. After the ADP1614 is turned on, SS sources 5  $\mu A$  (typical) to the soft start capacitor (Css) until it reaches 1.23 V at startup. As the soft start capacitor charges, it limits the peak current allowed by the part. By slowly charging the soft start capacitor, the input current ramps slowly to prevent it from overshooting excessively at startup. When the ADP1614 is disabled, the SS pin is internally shorted to GND to discharge the soft start capacitor.

#### **THERMAL SHUTDOWN (TSD)**

The ADP1614 includes TSD protection. If the die temperature exceeds 150°C (typical), TSD turns off the NMOS power device, significantly reducing power dissipation in the device and preventing output voltage regulation. The NMOS power device remains off until the die temperature is reduced to 130°C (typical). The soft start capacitor is discharged during TSD to ensure low output voltage overshoot and inrush currents when regulation resumes.

#### **UNDERVOLTAGE LOCKOUT (UVLO)**

If the input voltage is below the UVLO threshold, the ADP1614 automatically turns off the power switch and places the part into a low power consumption mode. This prevents potentially erratic operation at low input voltages and prevents the power device from turning on when the control circuitry cannot operate it. The UVLO levels have ~100 mV of hysteresis to ensure glitch-free startup.

#### **SHUTDOWN MODE**

The EN pin turns the ADP1614 regulator on or off. Drive EN low to shut down the regulator and reduce the input current to 0.25  $\mu$ A (typical). Drive EN high to turn on the regulator.

When the converter is in shutdown mode (EN  $\leq$  0.3 V), there is a dc path from the input to the output through the inductor and output rectifier. This causes the output voltage to remain slightly below the input voltage by the forward voltage of the rectifier, preventing the output voltage from dropping to ground when the regulator is shut down.

Regardless of the state of the EN pin, when a voltage is applied to the VIN pin, a large current spike occurs due to the nonisolated path through the inductor and diode between  $V_{\rm IN}$  and  $V_{\rm OUT}$ . The high current is a result of the output capacitor charging. The peak value is dependent on the inductor, output capacitor, and any load active on the output of the regulator.

## APPLICATIONS INFORMATION

#### **ADIsimPower DESIGN TOOL**

The ADP1614 is supported by the ADIsimPower™ design toolset. ADIsimPower is a collection of tools that produce complete power designs that are optimized for a specific design goal. The tools enable the user to generate a full schematic and bill of materials and to calculate performance in minutes. ADIsimPower can optimize designs for cost, area, efficiency, and parts count while taking into consideration the operating conditions and limitations of the IC and the external components. For more information about the ADIsimPower design tools, visit www.analog.com/ADIsimPower. The toolset is available from this website, and users can request an unpopulated board.

#### **SETTING THE OUTPUT VOLTAGE**

The ADP1614 features an adjustable output voltage range of  $V_{\rm IN}$  to 20 V. The output voltage is set by the resistor voltage divider, R1 and R2 (see Figure 25), from the output voltage ( $V_{\rm OUT}$ ) to the 1.245 V feedback input at FB. Use the following equation to determine the output voltage:

$$V_{OUT} = 1.245 \times (1 + R1/R2) \tag{1}$$

Choose R1 based on the following equation:

$$R1 = R2 \times \left(\frac{V_{OUT} - 1.245}{1.245}\right) \tag{2}$$

#### **INDUCTOR SELECTION**

The inductor is an essential part of the step-up switching converter. It stores energy during the on time of the power switch and transfers that energy to the output through the output rectifier during the off time. To balance the trade-offs between small inductor current ripple and efficiency, inductance values in the range of 4.7  $\mu H$  to 22  $\mu H$  are recommended. In general, lower inductance values have higher saturation current and lower series resistance for a given physical size. However, lower inductance values result in higher peak current, which can lead to reduced efficiency and greater input and/or output ripple and noise. A peak-to-peak inductor ripple current close to 30% of the maximum dc input current typically yields an optimal compromise.

For determining the inductor ripple current in continuous operation, the input  $(V_{IN})$  and output  $(V_{OUT})$  voltages determine the switch duty cycle (D) as follows:

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}} \tag{3}$$

The duty cycle and switching frequency  $(f_{SW})$  can be used to determine the on time:

$$t_{ON} = \frac{D}{f_{SW}} \tag{4}$$

The inductor ripple current ( $\Delta I_L$ ) in steady state is calculated by

$$\Delta I_L = \frac{V_{IN} \times t_{ON}}{L} \tag{5}$$

Solve for the inductance value (L) as follows:

$$L = \frac{V_{IN} \times t_{ON}}{\Delta I_{I}} \tag{6}$$

Ensure that the peak inductor current (the maximum input current plus half the inductor ripple current) is below the rated saturation current of the inductor. Likewise, make sure that the maximum rated rms current of the inductor is greater than the maximum dc input current to the regulator.

For continuous current-mode (CCM) duty cycles greater than 50% that occur with input voltages less than one-half the output voltage, slope compensation is required to maintain stability of the current-mode regulator. For stable current-mode operation, ensure that the selected inductance is equal to or greater than the minimum calculated inductance,  $L_{\rm MIN}$ , for the application parameters in the following equation:

$$L > L_{MIN} = \frac{(V_{OUT} - 2 \times V_{IN})}{8 \times f_{SW}} \tag{7}$$

Inductors smaller than the  $4.7 \,\mu\text{H}$  to  $22 \,\mu\text{H}$  recommended range can be used as long as Equation 7 is satisfied for the given application. For input/output combinations that approach the 90% maximum duty cycle, doubling the inductor is recommended to ensure stable operation. Table 5 suggests a series of inductors for use with the ADP1614.

**Table 5. Suggested Inductors**

| 1 4010 01 0 4080000 1114400010 |                                                |  |  |  |  |

|--------------------------------|------------------------------------------------|--|--|--|--|

| Manufacturer                   | Part Series                                    |  |  |  |  |

| Coilcraft                      | XAL40xx, XAL50xx, XAL6060, DO3316P             |  |  |  |  |

| TOKO Inc.                      | FDV06xx, DG6045C, FDSD0630, DEM8045C, FDVE1040 |  |  |  |  |

| Würth Elektronik               | WE-HCI, WE-TPC, WE-PD, WE-PD2, WE -PDF         |  |  |  |  |

| Vishay Dale                    | IHLP-2020, IHLP-2525, IHLP-3232, IHLP-4040     |  |  |  |  |

| TDK Components                 | SPM6530, VLP8040, VLF10040, VLF10045           |  |  |  |  |

| Taiyo Yuden                    | NRS8030, NRS8040                               |  |  |  |  |

#### **CHOOSING THE INPUT AND OUTPUT CAPACITORS**

The ADP1614 requires input and output bypass capacitors to supply transient currents while maintaining constant input and output voltages. Use low equivalent series resistance (ESR) capacitors of 10  $\mu$ F or greater to prevent noise at the ADP1614 input. Place the capacitor between VIN and GND, as close as possible to the ADP1614. Ceramic capacitors are preferable because of their low ESR characteristics. Alternatively, use a high value, medium ESR capacitor in parallel with a 0.1  $\mu$ F low ESR capacitor, placed as close as possible to the ADP1614.

The output capacitor maintains the output voltage and supplies current to the load while the ADP1614 switch is on. The value and characteristics of the output capacitor greatly affect the output voltage ripple and stability of the regulator. A low ESR ceramic dielectric capacitor is preferable. The output voltage ripple ( $\Delta V_{OUT}$ ) is calculated as follows:

$$\Delta V_{OUT} = \frac{Q_C}{C_{OUT}} = \frac{I_{OUT} \times t_{ON}}{C_{OUT}}$$

(8)

where:

$Q_C$  is the charge removed from the capacitor.

$C_{OUT}$  is the output capacitance.

$I_{OUT}$  is the output load current.

$t_{ON}$  is the on time of the switch.

The on time of the switch is determined as follows:

$$t_{ON} = \frac{D}{f_{SW}} \tag{9}$$

The input  $(V_{IN})$  and output  $(V_{OUT})$  voltages determine the switch duty cycle (D) as follows:

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}} \tag{10}$$

Choose the output capacitor based on the following equation:

$$C_{OUT} \ge \frac{I_{OUT} \times (V_{OUT} - V_{IN})}{f_{SW} \times V_{OUT} \times \Delta V_{OUT}}$$

(11)

Multilayer ceramic capacitors are recommended for this application.

#### **DIODE SELECTION**

The output rectifier conducts the inductor current to the output capacitor and load while the switch is off. For high efficiency, minimize the forward voltage drop of the diode. For this reason, using Schottky rectifiers is recommended. However, for high voltage, high temperature applications, where the Schottky rectifier reverse leakage current becomes significant and can degrade efficiency, use an ultrafast junction diode.

Many diode manufacturers derate the current capability of the diode as a function of the duty cycle. Verify that the output

diode is rated to handle the average output load current with the minimum duty cycle. The minimum duty cycle in CCM of the ADP1614 is

$$D_{MIN} = \frac{V_{OUT} - V_{IN(MAX)}}{V_{OUT}} \tag{12}$$

where  $V_{IN(MAX)}$  is the maximum input voltage.

The following are suggested Schottky diode manufacturers:

- ON Semiconductor

- Diodes, Inc.

- Toshiba

- ROHM Semiconductor

#### **LOOP COMPENSATION**

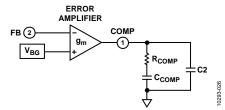

The ADP1614 uses external components to compensate the regulator loop, allowing optimization of the loop dynamics for a given application.

The step-up converter produces an undesirable right-half plane zero in the regulation feedback loop. This requires compensating the regulator such that the crossover frequency occurs well below the frequency of the right-half plane zero. The right-half plane zero is determined by the following equation:

$$F_Z(RHP) = \left(\frac{V_{IN}}{V_{OUT}}\right)^2 \times \frac{R_{LOAD}}{2\pi \times L}$$

(13)

where:

$F_Z(RHP)$  is the right-half plane zero.

$R_{LOAD}$  is the equivalent load resistance or the output voltage divided by the load current.

To stabilize the regulator, ensure that the regulator crossover frequency is less than or equal to one-fifth of the right-half plane zero.

The regulator loop gain is

$$A_{VL} = \frac{V_{FB}}{V_{OUT}} \times \frac{V_{IN}}{V_{OUT}} \times G_{MEA} \times \left| R_{OUT} \right| \left| Z_{COMP} \right| \times G_{CS} \times \left| Z_{OUT} \right| (14)$$

where:

$A_{VL}$  is the loop gain.

$V_{FB}$  is the feedback regulation voltage, 1.245 V.

$V_{OUT}$  is the regulated output voltage.

$V_{IN}$  is the input voltage.

$G_{MEA}$  is the error amplifier transconductance gain.

$R_{OUT} = 67 \text{ M}\Omega.$

$Z_{COMP}$  is the impedance of the series RC network from COMP to CNID.

$G_{CS}$  is the current sense transconductance gain (the inductor current divided by the voltage at COMP), which is internally set by the ADP1614.

$Z_{OUT}$  is the impedance of the load in parallel with the output capacitor.

To determine the crossover frequency, it is important to note that at the crossover frequency the compensation impedance ( $Z_{\text{COMP}}$ ) is dominated by a resistor, and the output impedance ( $Z_{\text{OUT}}$ ) is dominated by the impedance of an output capacitor. Therefore, when solving for the crossover frequency, the equation (by definition of the crossover frequency) is simplified to

$$|A_{VL}| = \frac{V_{FB}}{V_{OUT}} \times \frac{V_{IN}}{V_{OUT}} \times G_{MEA} \times R_{COMP} \times G_{CS} \times \frac{1}{2\pi \times f_C \times C_{OUT}} = 1$$

(15)

where:

$R_{COMP}$  is the compensation resistor.

$f_C$  is the crossover frequency.

Solve for R<sub>COMP</sub> as follows:

$$R_{COMP} = \frac{2\pi \times f_C \times C_{OUT} \times (V_{OUT})^2}{V_{FR} \times V_{IN} \times G_{MFA} \times G_{CS}}$$

(16)

where:

$V_{FB} = 1.245 \text{ V}.$

$G_{MEA} = 150 \,\mu\text{A/V}.$

$G_{CS} = 7 \text{ A/V}.$

Therefore,

$$R_{COMP} = \frac{4806 \times f_C \times C_{OUT} \times (V_{OUT})^2}{V_{IN}}$$

(17)

After the compensation resistor is known, set the zero formed by the compensation capacitor and resistor to one-fourth of the crossover frequency, or

$$C_{COMP} = \frac{2}{\pi \times f_C \times R_{COMP}}$$

(18)

where  $C_{COMP}$  is the compensation capacitor.

Figure 27. Compensation Components

Capacitor C2 is chosen to cancel the zero introduced by the ESR of the output capacitor.

Solve for C2 as follows:

$$C2 = \frac{ESR \times C_{OUT}}{R_{COMP}} \tag{19}$$

If a low ESR, ceramic output capacitor is used for  $C_{OUT}$ , C2 is optional. For optimal transient performance,  $R_{COMP}$  and  $C_{COMP}$  might need to be adjusted by observing the load transient response of the ADP1614. For most applications, the compensation resistor should be within the range of 1 k $\Omega$  to 100 k $\Omega$ , and the compensation capacitor should be within the range of 100 pF to 10 nF.

#### **SOFT START CAPACITOR**

Upon startup (EN  $\geq$  1.6 V) or fault recovery, the voltage at SS ramps up slowly by charging the soft start capacitor ( $C_{SS}$ ) with an internal 5.5  $\mu$ A current source ( $I_{SS}$ ). As the soft start capacitor charges, it limits the peak current allowed by the part to prevent excessive overshoot at startup. Use the following equation to determine the necessary value of the soft start capacitor ( $C_{SS}$ ) for a specific overshoot and start-up time when the part is at the current limit with maximum load:

$$C_{SS} = I_{SS} \frac{\Delta t}{V_{SS}} \tag{20}$$

where:

$I_{SS} = 5.5 \,\mu\text{A}$  (typical).

$\Delta t$  is the start-up time at the current limit.

$V_{SS} = 1.23 \text{ V (typical)}.$

If the applied load does not place the part at the current limit, the value of C<sub>ss</sub> can be reduced. A 68 nF soft start capacitor results in negligible input current overshoot at startup and, therefore, is suitable for most applications. If an unusually large output capacitor is used, a longer soft start period is required to prevent input inrush current.

However, if fast startup is required, the soft start capacitor can be reduced or removed, which allows the ADP1614 to start quickly but with greater peak switch current.

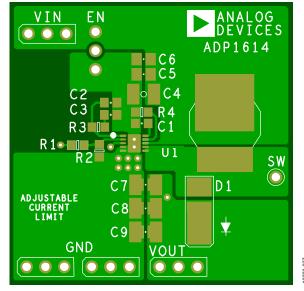

### PCB LAYOUT GUIDELINES

For high efficiency, good regulation, and stability, a well designed PCB layout is required.

Use the following guidelines when designing PCBs (see Figure 25 for a block diagram and Figure 2 for a pin configuration).

- Keep the low ESR input capacitor (C<sub>IN</sub>), which is labeled as C4 in Figure 28, close to VIN and GND. This minimizes noise injected into the part from board parasitic inductance.

- Keep the high current path from  $C_{\rm IN}$  through the L1 inductor to SW and GND as short as possible.

- Keep the high current path from VIN through the inductor (L1), the rectifier (D1), and the output capacitor (C<sub>OUT</sub>), which is labeled as C7 in Figure 28, as short as possible.

- Keep high current traces as short and as wide as possible.

- Place the feedback resistors as close to FB as possible to prevent noise pickup. Connect the ground of the feedback network directly to an AGND plane that makes a Kelvin connection to the GND pin.

- Place the compensation components as close as possible to COMP. Connect the ground of the compensation network directly to an AGND plane that makes a Kelvin connection to the GND pin.

- Connect the soft start capacitor (*C*<sub>SS</sub>), which is labeled as C1 in Figure 28, as close as possible to the device. Connect the ground of the soft start capacitor to an AGND plane that makes a Kelvin connection to the GND pin.

- Connect the current limit set resistor (R<sub>CL</sub>), which is labeled as R4 in Figure 28, as close as possible to the device.

Connect the ground of the CL resistor to an AGND plane that makes a Kelvin connection to the GND pin.

- The PCB must be properly designed to conduct the heat away from the package. This is achieved by adding thermal vias to the PCB, which provide a thermal path to the inner or bottom layers. Thermal vias should be placed on the PCB underneath the exposed pad of the LFCSP and in the GND plane around the ADP1614 package to improve thermal performance of the package.

Avoid routing high impedance traces from the compensation and feedback resistors near any node connected to SW or near the inductor to prevent radiated noise injection.

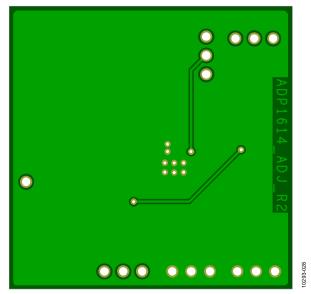

Figure 28. ADP1614 Recommended Top Layer Layout for Boost Application

Figure 29. ADP1614 Recommended Bottom Layer Layout for Boost Application

## **OUTLINE DIMENSIONS**

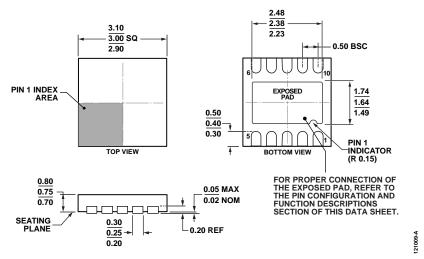

Figure 30. 10-Lead Lead Frame Chip Scale Package [LFCSP\_WD] 3 mm × 3 mm Body, Very Very Thin, Dual Lead (CP-10-9) Dimensions shown in millimeters

#### **ORDERING GUIDE**

|                    | Temperature     | Switching |                                                     | Package |          |

|--------------------|-----------------|-----------|-----------------------------------------------------|---------|----------|

| Model <sup>1</sup> | Range           | Frequency | Package Description                                 | Option  | Branding |

| ADP1614ACPZ-1.3-R7 | −40°C to +125°C | 1.3 MHz   | 10-Lead Lead Frame Chip Scale Package [LFCSP_WD]    | CP-10-9 | LM4      |

| ADP1614ACPZ-650-R7 | −40°C to +125°C | 650 kHz   | 10-Lead Lead Frame Chip Scale Package [LFCSP_WD]    | CP-10-9 | LM5      |

| ADP1614-1.3-EVALZ  |                 | 1.3 MHz   | Evaluation Board, 15 V Output Voltage Configuration |         |          |

| ADP1614-650-EVALZ  |                 | 650 kHz   | Evaluation Board, 5 V Output Voltage Configuration  |         |          |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.