## **DATA SHEET**

# SD1210

Dual-Interface SXGA TFT LCD Display Controller

November 1999

## SD1210 DATA SHEET DAT-SD1210-1199-B

November 1999

| Document          | Revisions             | Date          |

|-------------------|-----------------------|---------------|

| DAT-SD1210-1099-A | SD1210 Data Sheet - A | October 1999  |

| DAT-SD1210-1199-B | SD1210 Data Sheet - B | November 1999 |

Copyright 1999, SmartASIC, Inc. All Right Reserved

SmartASIC, Inc. reserves the right to change or modify the information contained herein without notice. It is the customer's responsibility to ensure he/she has the most recent revision of the user guide. SmartASIC, Inc. makes no warranty for the use of its products and bears no responsibility for any error or omissions, which may appear in this document.

## **1. OVERVIEW**

The SD1210 is enhanced version of the SD1200 chip. It is an IC designed for dualinterface SXGA TFT LCD monitors. A dual-interface LCD monitor takes analog or digital RGB signals from a graphic card of a personal computer, the exact same input interface as a conventional CRT monitor. This feature makes a dual-interface LCD monitor a true replacement for a conventional CRT monitor.

The analog input RGB signals are first sampled by six channels of 8-bit A/D converters, and the 48-bit RGB data are then fed into the SD1210. For digital interface, the input data are first received by a TMDS receiver, and the 24/48 bit RGB output data of TMDS receiver are then fed into the SD1210. The SD1210 is capable of performing automatic detection of the display resolution and timing of input signals generated from various PC graphic cards. No special driver is required for the timing detection, nor any manual adjustment. The SD1210 then automatically scales the input image to fill the full screen of the LCD monitor. The SD1210 can interface with TFT LCD panels from various manufacturers by generating either 24-bit or 48-bit RGB signal to the LCD panel based upon the timing parameters saved in the EEPROM.

The SD1210 implements four advanced display technologies:

- 1. Advanced mode detection and auto-calibration without any external CPU assist

- 2. Advanced programmable interpolation algorithm

- 3. Stand-alone mode support, and

- 4. Advanced true color support with both dithering and frame modulation.

The SD1210 also provides distinguished system features to the TFT LCD monitor solution. The first one is "plug-and-play", and the second one is "cost-effective system solution". To be truly plug-and-display, the SD1210 performs automatic input mode detection and auto phase calibration, so the LCD monitor can ensure that the A/D converters' sample clock is precisely synchronized with the input video data, and to preserve the highest image bandwidth for the highest image quality. Furthermore, the SD1210 can generate output video even when the input signal is beyond the specifications or no input signal is fed.

For "cost-effective system solution", the SD1210 implements many system support features such as OSD mixer, error status indicators, 2-wire serial interface for both EEPROM and host CPU interface, and low-cost IC package. Another important contributing factor is that the SD1210 does not require external frame buffer memory for the automatic image scaling and synchronization.

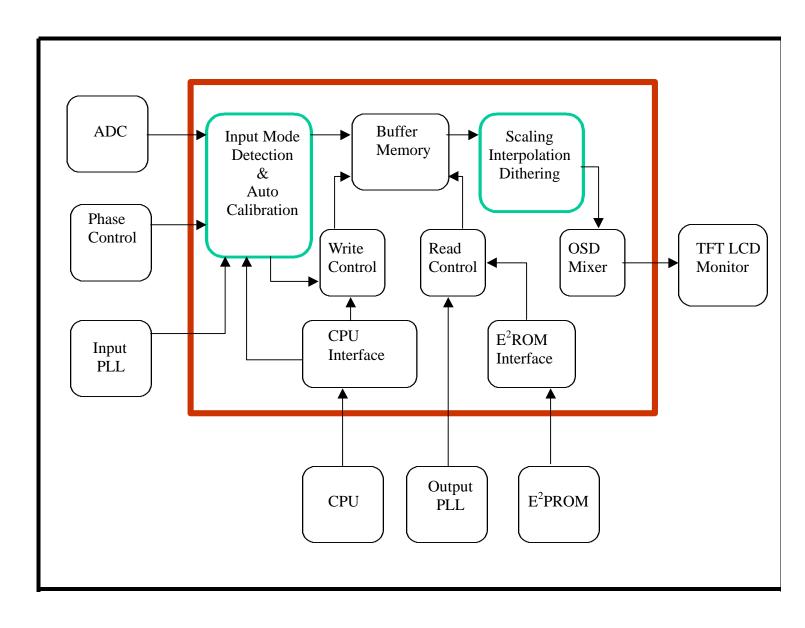

Figure 1 shows the block diagram of the SD1210 as well as the connections of important system components around the SD1210.

## SmartASIC, Inc.

### Figure 1: SD1210 Functional Block Diagram

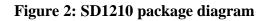

## 2. PIN DESCRIPTION

| Symbol   | PIN Number | I/O | Description                                                |

|----------|------------|-----|------------------------------------------------------------|

| B_IN10   | 1          | Ι   | Channel B Data Input Color Blue (LSB)                      |

| B_IN11   | 2          | Ι   | Channel B Data Input Color Blue                            |

| B_IN12   | 3          | Ι   | Channel B Data Input Color Blue                            |

| B_IN13   | 4          | Ι   | Channel B Data Input Color Blue                            |

| DATA_SEL | 5          | Ι   | Indicate Channel A or Channel B contains valid input       |

|          |            |     | data:                                                      |

|          |            |     | 1: data in Channel A is valid                              |

|          |            |     | 0: data in Channel B is valid                              |

| B_IN14   | 6          | Ι   | Channel B Data Input Color Blue                            |

| B_IN15   | 7          | Ι   | Channel B Data Input Color Blue                            |

| B_IN16   | 8          | Ι   | Channel B Data Input Color Blue                            |

| B_IN17   | 9          | Ι   | Channel B Data Input Color Blue (MSB)                      |

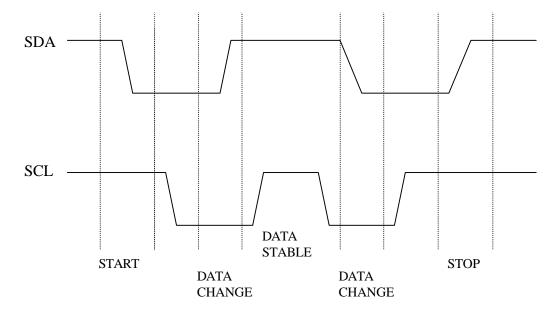

| ROM_SCL  | 10         | 0   | SCL in I <sup>2</sup> C for EEPROM interface               |

| ROM_SDA  | 11         | I/O | SDA in I <sup>2</sup> C for EEPROM interface               |

| GND      | 12         |     | Ground                                                     |

| CPU_SCL  | 13         | Ι   | SCL in I <sup>2</sup> C for CPU interface                  |

| CPU_SDA  | 14         | I/O | SDA in I <sup>2</sup> C for CPU interface                  |

| PWM_CTL  | 15         | 0   | PWM control signal (Detail description in PWM              |

|          |            |     | Operation Section)                                         |

| CLK_1M   | 16         | Ι   | Free Running Clock (default: 1MHz)                         |

| VDD      | 17         |     | Power Supply                                               |

| CLK_1M_O | 18         | 0   | Feedback of free Running Clock                             |

| RESET_B  | 19         | Ι   | System Reset ( active LOW)                                 |

| R_OSD    | 20         | Ι   | OSD Color Red                                              |

| G_OSD    | 21         | Ι   | OSD Color Green                                            |

| B_OSD    | 22         | Ι   | OSD Color Blue                                             |

| EN_OSD   | 23         | Ι   | OSD Mixer Enable                                           |

|          |            |     | =0, No OSD output                                          |

|          |            |     | =1,R_OUT[7:0]= {R_OSD repeat 8 times}                      |

|          |            |     | $G_OUT[7:0] = \{G_OSD \text{ repeat } 8 \text{ times } \}$ |

|          |            |     | B_OUT[7:0]= {B_OSD repeat 8 times }                        |

| SCAN_EN  | 24         | I   | Manufacturing test pin (NC)                                |

| TEST_EN  | 25         | Ι   | Manufacturing test pin (NC)                                |

| VCLK01   | 26         | Ι   | Input Clock 1                                              |

| FCLK0    | 27         | 0   | Input PLL Feedback Clock                                   |

| VCLK00   | 28         | I   | Input Clock 0                                              |

| FCLK1    | 29         | 0   | Output PLL Feedback Clock                                  |

| VCLK1    | 30         | I   | Output PLL Output Clock                                    |

| HSYNC_O  | 31         | 0   | Output HSYNC (the polarity is programmable through         |

|          |            | -   | CPU, default is active low)                                |

| VSYNC_O  | 32         | 0   | Output VSYNC (the polarity is programmable through         |

|          | 22         |     | CPU, default is active low)                                |

| DCLK_OUT | 33         | 0   | Output Clock to Control Panel (the polarity is             |

|          | 24         |     | programmable through CPU)                                  |

| DE_OUT   | 34         | 0   | Output Display Enable for Panel (the polarity is           |

| CND      | 25         |     | programmable through CPU, default is active HIGH)          |

| GND      | 35         |     | Ground                                                     |

| VDD      | 36         | 0   | Power Supply                                               |

| R_OUT0_E | 37         | 0   | Output Color Red Even Pixel (left pixel)                   |

#### Table 1: SD1210 pin description (sorted by pin number)

| R_OUT2_E39OOutput Color Red Even Pixel (left pixel)R_OUT3_E40OOutput Color Red Even Pixel (left pixel)HSYNC_X41ODefault VSYNC generated by ASIC (active LOW)GND43GroundGroundR_OUT4_E44OOutput Color Red Even Pixel (left pixel)VDD45Power SupplyVDD46Power SupplyR_OUT5_E47OOutput Color Red Even Pixel (left pixel)GND48GroundR_OUT7_E50OOutput Color Red Even Pixel (left pixel)R_OUT7_E50OOutput Color Red Even Pixel (left pixel)R_OUT0_O52OOutput Color Red Odd Pixel (right pixel)R_OUT1_O52OOutput Color Red Odd Pixel (right pixel)R_OUT1_O53OOutput Color Red Odd Pixel (right pixel)R_OUT1_O55OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT5_O59OOutput Color Gene Odd Pixel (right pixel)R_OUT2_E64OOutput Color Green Even Pixel (left pixel)GOUT1_E63OOutput Color Green Even Pixel (left pixel)GOUT1_E64OOutput Color Green Even Pixel (left pixel)GOUT5_O78OOutput Color Green Even Pixel (left pixel)GOUT5_C79OOutput Color Green Even Pixel (left pixe                                                                                                                                                                                                                       | R_OUT1_E | 38 | 0 | Output Color Red Even Pixel (left pixel)   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|---|--------------------------------------------|

| R_OUT3_E40OOutput Color Red Even Pixel (left pixel)HSYNC_X41ODefault HSYNC generated by ASIC (active LOW)VSYNC_X42ODefault VSYNC generated by ASIC (active LOW)GND43GroundR_OUT4_E44OOutput Color Red Even Pixel (left pixel)VDD45Power SupplyVDD46Power SupplyR_OUT5_E47OGND48GroundR_OUT6_E49OOutput Color Red Even Pixel (left pixel)GND51GroundR_OUT7_D50O Utput Color Red Odd Pixel (right pixel)R_OUT1_O52OQUT1_O53O Utput Color Red Odd Pixel (right pixel)R_OUT2_O54O Output Color Red Odd Pixel (right pixel)R_OUT4_O57OQUT4_O57O Utput Color Red Odd Pixel (right pixel)R_OUT5_O58OQUT4_O57OQUT0_CO60Output Color Red Odd Pixel (right pixel)R_OUT6_O59OQUT0_CO61GroundG_OUT0_E62OQUT1_E63OQUT1_E64OQUT1_E64OQUT1_CO77QUT5_O58OQUT1_CO78OQUT1_CO77QUT1_CO61GroundGroundG_OUT1_E62OQUT1_CO78QUT1_CO79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |    | - |                                            |

| HSYNC_X41ODefault HSYNC generated by ASIC (active LOW)VSNC_X42ODefault VSYNC generated by ASIC (active LOW)GND43Ground $R_OUT4_E$ 44OOutput Color Red Even Pixel (left pixel)VDD45Power SupplyVDD46Power SupplyR_OUT5_E47OOutput Color Red Even Pixel (left pixel)GND48Ground $R_OUT6_E$ 49OOutput Color Red Even Pixel (left pixel)R_OUT6_E49OOutput Color Red Odd Pixel (right pixel)R_OUT0_052OOutput Color Red Odd Pixel (right pixel)R_OUT1_053OOutput Color Red Odd Pixel (right pixel)R_OUT3_055OOutput Color Red Odd Pixel (right pixel)R_OUT4_057OOutput Color Red Odd Pixel (right pixel)R_OUT5_058OOutput Color Red Odd Pixel (right pixel)R_OUT5_059OOutput Color Red Odd Pixel (right pixel)R_OUT5_058OOutput Color Green Even Pixel (left pixel)R_OUT5_060OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT2_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)                                                                                                                                                                                                          |          |    |   |                                            |

| VSYNC_X42ODefault VSYNC generated by ASIC (active LOW)GND43GroundR_OUT4_E44OOutput Color Red Even Pixel (left pixel)VDD45Power SupplyVDD46Power SupplyR_OUT5_E47OGND48GroundR_OUT6_T_E50Output Color Red Even Pixel (left pixel)GND51GroundR_OUT1_O52OGND51GroundR_OUT1_O53OQUT2_O54OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)R_OUT4_O57OVDD56Power SupplyR_OUT5_O58OQUT2_O58OVDD56Power SupplyR_OUT4_O57OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT0_E62OGND61GroundGroundG_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel) <tr< td=""><td></td><td></td><td></td><td></td></tr<>                                                                                                                                                                                                                                                                                                                                                                                    |          |    |   |                                            |

| GND43GroundR_OUT4_E44OOutput Color Red Even Pixel (left pixel)VDD45Power SupplyVDD46Power SupplyR_OUT5_E47OOutput Color Red Even Pixel (left pixel)GND48GroundR_OUT6_E49OOutput Color Red Even Pixel (left pixel)R_OUT7_E50OOutput Color Red Even Pixel (left pixel)R_OUT7_D51GroundR_OUT1_O52OOutput Color Red Odd Pixel (right pixel)R_OUT2_O54OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)R_OUT3_O56Power SupplyVDD56Power SupplyR_OUT4_O57OQUT6_O59OOutput Color Red Odd Pixel (right pixel)R_OUT5_O60OQUT0_C58OOutput Color Red Odd Pixel (right pixel)R_OUT5_O60OQUT0_C60OQUT0_C60OOUT0_C61GroundGroundG_OUT1_E63OG_OUT1_E64OOOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOOutput Color Green Even Pixe                                                                                                                                                                                                                                                                                                                                                                                                                    |          |    | - |                                            |

| R_OUT4_E440Output Color Red Even Pixel (left pixel)VDD45Power SupplyVDD46Power SupplyR_OUT5_E470Output Color Red Even Pixel (left pixel)GND48GroundR_OUT6_E490Output Color Red Even Pixel (left pixel)GND51GroundR_OUT7_D520Output Color Red Odd Pixel (right pixel)R_OUT1_O520Output Color Red Odd Pixel (right pixel)R_OUT1_O530Output Color Red Odd Pixel (right pixel)R_OUT3_O550Output Color Red Odd Pixel (right pixel)R_OUT3_O550Output Color Red Odd Pixel (right pixel)R_OUT4_O570Output Color Red Odd Pixel (right pixel)R_OUT5_O580Output Color Red Odd Pixel (right pixel)R_OUT6_O590Output Color Red Odd Pixel (right pixel)GND61GroundGroundG_OUT0_E620Output Color Green Even Pixel (left pixel)G_OUT3_E650Output Color Green Even Pixel (left pixel)G_OUT3_E660Output Color Green Even Pixel (left pixel)G_OUT3_E680Output Color Green Even Pixel (left pixel)G_OUT5_E680Output Color Green Even Pixel (left pixel)G_OUT3_E660Output Color Green Even Pixel (left pixel)G_OUT5_E680Output Color Green Even Pixel (left pixel)G_OUT5_E68<                                                                                                                                                                                                                                              |          |    | 0 |                                            |

| VDD45Power SupplyVDD46Power SupplyR_OUT5_E47OGND48GroundR_OUT6_E49OOutput Color Red Even Pixel (left pixel)R_OUT7_E50OODT051GroundR_OUT1_O52OOutput Color Red Odd Pixel (right pixel)R_OUT1_O53OQUT1_O53OQUT1_O54OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)R_OUT4_O57OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OQUT0_C 059OQUtput Color Red Odd Pixel (right pixel)R_OUT5_O58OQUT0_C 059OQUtput Color Red Odd Pixel (right pixel)R_OUT7_O60OOutput Color Red Odd Pixel (right pixel)R_OUT2_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OQUT1_C E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E68OOUT1_C Color Green Even Pixel (left pixel)G_OUT3_E68OOutput Color Green Even Pixel (left pixel)G_OUT3_E68OOutput Color Green Even Pixel (left pixel)G_OUT3_E69OOutput Color Green Even Pixel (left pixel)G_OUT3_E69 </td <td></td> <td></td> <td>0</td> <td></td>                                                                                                                                                                                                                                                                                                                                                      |          |    | 0 |                                            |

| VDD46Power Supply $R_OUT5\_E$ 47OOutput Color Red Even Pixel (left pixel) $GND$ 48Ground $R_OUT6\_E$ 49OOutput Color Red Even Pixel (left pixel) $R_OUT7\_E$ 50OOutput Color Red Even Pixel (left pixel) $R_OUT0\_O$ 52O Output Color Red Odd Pixel (right pixel) $R_OUT0\_O$ 53OOutput Color Red Odd Pixel (right pixel) $R_OUT3\_O$ 54OOutput Color Red Odd Pixel (right pixel) $R_OUT3\_O$ 55OOutput Color Red Odd Pixel (right pixel) $R_OUT3\_O$ 57OOutput Color Red Odd Pixel (right pixel) $R_OUT5\_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT5\_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT5\_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT5\_O$ 59OOutput Color Reen Odd Pixel (right pixel) $R_OUT5\_O$ 64Output Color Green Even Pixel (left pixel) $G_OUT0\_E$ 62OOutput Color Green Even Pixel (left pixel) $G_OUT3\_E$ 64OOutput Color Green Even Pixel (left pixel) $G_OUT3\_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT3\_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT3\_E$ 64OOutput Color Green Even Pixel (left pixel) $G_OUT3\_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT5\_E$ 68OOutput Color Green Even Pixe                                                                                                   |          |    | 0 |                                            |

| R_OUT5_E47OOutput Color Red Even Pixel (left pixel)GND48GroundR_OUT6_E49OOutput Color Red Even Pixel (left pixel)R_OUT7_E50OOutput Color Red Odd Pixel (right pixel)GND51GroundR_OUT1_O52OOutput Color Red Odd Pixel (right pixel)R_OUT1_O53OOutput Color Red Odd Pixel (right pixel)R_OUT1_O53OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)R_OUT4_O57OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT5_O59OOutput Color Red Odd Pixel (right pixel)R_OUT6_D59OOutput Color Green Even Pixel (left pixel)GND61GroundG_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT1_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E66OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E69OOutput Color Green Even Pixel (left pixel)G_OUT5_E69OOutput Color Green Odd Pixel (right pixel)G_OUT5_E69OOutput Col                                                                                                                                                                                                                       |          |    |   |                                            |

| GND48Ground $R_OUT6_E$ 49OOutput Color Red Even Pixel (left pixel) $R_OUT7_E$ 50OOutput Color Red Even Pixel (left pixel)GND51Ground $R_OUT1_O$ 52OOutput Color Red Odd Pixel (right pixel) $R_OUT2_O$ 53OOutput Color Red Odd Pixel (right pixel) $R_OUT2_O$ 54OOutput Color Red Odd Pixel (right pixel) $R_OUT3_O$ 55OOutput Color Red Odd Pixel (right pixel) $R_OUT4_O$ 57OOutput Color Red Odd Pixel (right pixel) $R_OUT5_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT5_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT5_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT5_O$ 59OOutput Color Red Odd Pixel (right pixel) $R_OUT7_O$ 60OOutput Color Green Even Pixel (left pixel) $G_OUT0_E$ 62OOutput Color Green Even Pixel (left pixel) $G_OUT1_E$ 63OOutput Color Green Even Pixel (left pixel) $G_OUT3_E$ 64OOutput Color Green Even Pixel (left pixel) $G_OUT5_E$ 68OOutput Color Gree                                                                                                                                           |          |    | 0 | 11 7                                       |

| $R_OUT6_E$ 49OOutput Color Red Even Pixel (left pixel) $R_OUT7_E$ 50OOutput Color Red Even Pixel (left pixel) $GND$ 51Ground $R_OUT0_O$ 52OOutput Color Red Odd Pixel (right pixel) $R_OUT1_O$ 53OOutput Color Red Odd Pixel (right pixel) $R_OUT3_O$ 55OOutput Color Red Odd Pixel (right pixel) $R_OUT3_O$ 55OOutput Color Red Odd Pixel (right pixel) $R_OUT3_O$ 56Power Supply $R_OUT5_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT6_O$ 59OOutput Color Red Odd Pixel (right pixel) $R_OUT6_O$ 59OOutput Color Red Odd Pixel (right pixel) $R_OUT6_O$ 59OOutput Color Red Odd Pixel (right pixel) $GND$ 61GroundGround $G_OUT0_E$ 62OOutput Color Green Even Pixel (left pixel) $G_OUT1_E$ 63OOutput Color Green Even Pixel (left pixel) $G_OUT3_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT3_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT4_E$ 66OOutput Color Green Even Pixel (left pixel) $G_OUT5_E$ 68OOutput Color Green Even Pixel (left pixel) $G_OUT7_E$ 70OOutput Color Green Odd Pixel (right pixel) $G_OUT7_E$ 71Ground $GND$ 72Ground $GUT1_O$ 74O $Output Color Green Odd Pi$                                                                                                                                                                        |          |    | 0 |                                            |

| R_OUT7_E50OOutput Color Red Even Pixel (left pixel)GND51GroundR_OUT0_O52OOutput Color Red Odd Pixel (right pixel)R_OUT1_O53OOutput Color Red Odd Pixel (right pixel)R_OUT2_O54OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)R_OUT4_O57OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT7_O60OOutput Color Red Odd Pixel (right pixel)R_OUT7_D60OOutput Color Green Even Pixel (left pixel)G_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT2_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E69OOutput Color Green Odd Pixel (right pixel)G_OUT1_O73OOutput Color Green Odd Pixel (right pixel)G_OUT3_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)G_OUT5_O73OOu                                                                                                                                                                                            |          |    | 0 |                                            |

| GND51GroundR_OUT0_O52OOutput Color Red Odd Pixel (right pixel)R_OUT1_O53OOutput Color Red Odd Pixel (right pixel)R_OUT2_O54OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)WDD56Power SupplyR_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT5_O59OOutput Color Red Odd Pixel (right pixel)R_OUT6_O59OOutput Color Red Odd Pixel (right pixel)R_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT2_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E69OOutput Color Green Even Pixel (left pixel)G_OUT7_E70OOutput Color Green Even Pixel (left pixel)G_OUT7_E70OOutput Color Green Odd Pixel (right pixel)G_OUT1_O73OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel) <td></td> <td></td> <td></td> <td></td>                                                                                                                                              |          |    |   |                                            |

| R_OUT0_O52OOutput Color Red Odd Pixel (right pixel)R_OUT1_O53OOutput Color Red Odd Pixel (right pixel)R_OUT3_O54OOutput Color Red Odd Pixel (right pixel)R_OUT3_O55OOutput Color Red Odd Pixel (right pixel)VDD56Power SupplyR_OUT4_O57OOutput Color Red Odd Pixel (right pixel)R_OUT5_O58OOutput Color Red Odd Pixel (right pixel)R_OUT6_O59OOutput Color Red Odd Pixel (right pixel)R_OUT7_O60OOutput Color Red Odd Pixel (right pixel)GND61GroundG_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT2_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT3_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E69OOutput Color Green Odd Pixel (right pixel)G_OUT5_E71GroundGND71GroundGND72GroundG_OUT1_O73OOOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOOutput Color Green Odd Pixel (right pixel)<                                                                                                                                                                                                                                                       |          |    | 0 |                                            |

| $R_{-}OUT1_{-}O$ 53OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT2_{-}O$ 54OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT3_{-}O$ 55OOutput Color Red Odd Pixel (right pixel) $NDD$ 56Power Supply $R_{-}OUT4_{-}O$ 57OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT5_{-}O$ 58OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT5_{-}O$ 58OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT5_{-}O$ 58OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT5_{-}O$ 60OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT0_{-}E$ 62OOutput Color Green Even Pixel (left pixel) $G_{-}OUT0_{-}E$ 62OOutput Color Green Even Pixel (left pixel) $G_{-}OUT1_{-}E$ 63OOutput Color Green Even Pixel (left pixel) $G_{-}OUT3_{-}E$ 64OOutput Color Green Even Pixel (left pixel) $G_{-}OUT4_{-}E$ 66OOutput Color Green Even Pixel (left pixel) $G_{-}OUT4_{-}E$ 66OOutput Color Green Even Pixel (left pixel) $G_{-}OUT5_{-}E$ 68OOutput Color Green Even Pixel (left pixel) $G_{-}OUT7_{-}E$ 70OOutput Color Green Even Pixel (left pixel) $G_{-}OUT7_{-}E$ 70OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT7_{-}D$ 73OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT1_{-}O$ 74OOutput Color Green Odd Pixel (right                                                            |          |    | 0 |                                            |

| R_OUT2_054OOutput Color Red Odd Pixel (right pixel)R_OUT3_055OOutput Color Red Odd Pixel (right pixel)VDD56Power SupplyR_OUT4_057OOutput Color Red Odd Pixel (right pixel)R_OUT5_058OOutput Color Red Odd Pixel (right pixel)R_OUT6_059OOutput Color Red Odd Pixel (right pixel)R_OUT6_059OOutput Color Red Odd Pixel (right pixel)GND61GroundG_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT2_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT7_E70OOutput Color Green Odd Pixel (right pixel)G_OUT7_E70OOutput Color Green Odd Pixel (right pixel)G_OUT1_O73OOutput Color Green Odd Pixel (right pixel)G_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel                                                                                                                                                                                   |          |    |   |                                            |

| R_OUT3_055OOutput Color Red Odd Pixel (right pixel)VDD56Power SupplyR_OUT4_057OOutput Color Red Odd Pixel (right pixel)R_OUT5_058OOutput Color Red Odd Pixel (right pixel)R_OUT6_059OOutput Color Red Odd Pixel (right pixel)R_OUT7_060OOutput Color Red Odd Pixel (right pixel)GND61GroundG_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT2_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E69OOutput Color Green Even Pixel (left pixel)G_OUT6_E69OOutput Color Green Even Pixel (left pixel)G_OUT7_E70OOutput Color Green Odd Pixel (right pixel)G_OUT1_073OOutput Color Green Odd Pixel (right pixel)G_OUT1_074OOutput Color Green Odd Pixel (right pixel)G_OUT2_075OOutput Color Green Odd Pixel (right pixel)G_OUT3_076OOutput Color Green Odd Pixel (right pixel)G_OUT5_079OOutput Color Green Odd Pixel (right pixel)G_OUT5_081OOutput Color Green Odd Pixel (right pix                                                                                                                                                                                   |          |    |   |                                            |

| VDD56Power Supply $R_OUT4_O$ 57OOutput Color Red Odd Pixel (right pixel) $R_OUT5_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT6_O$ 59OOutput Color Red Odd Pixel (right pixel) $R_OUT7_O$ 60OOutput Color Red Odd Pixel (right pixel) $GDT0_C$ 60OOutput Color Green Even Pixel (left pixel) $G_OUT0_E$ 62OOutput Color Green Even Pixel (left pixel) $G_OUT1_E$ 63OOutput Color Green Even Pixel (left pixel) $G_OUT3_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT4_E$ 66OOutput Color Green Even Pixel (left pixel) $G_OUT5_E$ 68OOutput Color Green Even Pixel (left pixel) $G_OUT5_E$ 70OOutput Color Green Odd Pixel (right pixel) $G_OUT0_O$ 73OOutput Color Green Odd Pixel (right pixel) $G_OUT1_O$ 75OOutput Color Green Odd Pixel (right pixel) $G_OUT3_O$ 76OOutput Color Green Odd Pixel (right pixel) $G_OUT5_O$ 78OOutput Color Green Odd Pixel (right pixel) $G_OUT5_O$ 79OOutput Color Green Odd Pixel (right pixel) $G_OUT5_O$ 80OOutput Color Green Odd Pixel (right pixel) <td></td> <td></td> <td>-</td> <td>1</td>                                                                 |          |    | - | 1                                          |

| $R_OUT4_O$ 57OOutput Color Red Odd Pixel (right pixel) $R_OUT5_O$ 58OOutput Color Red Odd Pixel (right pixel) $R_OUT6_O$ 59OOutput Color Red Odd Pixel (right pixel) $R_OUT7_O$ 60OOutput Color Red Odd Pixel (right pixel) $GND$ 61Ground $G_OUT0_E$ 62OOutput Color Green Even Pixel (left pixel) $G_OUT1_E$ 63OOutput Color Green Even Pixel (left pixel) $G_OUT2_E$ 64OOutput Color Green Even Pixel (left pixel) $G_OUT3_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT4_E$ 66OOutput Color Green Even Pixel (left pixel) $G_OUT5_E$ 68OOutput Color Green Even Pixel (left pixel) $G_OUT5_E$ 69OOutput Color Green Even Pixel (left pixel) $G_OUT6_O$ 73OOutput Color Green Odd Pixel (right pixel) $G_OUT1_O$ 73OOutput Color Green Odd Pixel (right pixel) $G_OUT3_O$ 76OOutput Color Green Odd Pixel (right pixel) $G_OUT5_O$ 78OOutput Color Green Odd Pixel (right pixel) $G_OUT5_O$ 78OOutput Color Green Odd Pixel (right pixel) $G_OUT5_O$ 80OOutput Color Green Odd Pixel (right pixel)<                                                                                                           |          |    | 0 |                                            |

| $R_{-}OUT5_{-}O$ 58OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT6_{-}O$ 59OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT7_{-}O$ 60OOutput Color Red Odd Pixel (right pixel) $GND$ 61Ground $G_{-}OUT0_{-}E$ 62OOutput Color Green Even Pixel (left pixel) $G_{-}OUT1_{-}E$ 63OOutput Color Green Even Pixel (left pixel) $G_{-}OUT3_{-}E$ 64OOutput Color Green Even Pixel (left pixel) $G_{-}OUT3_{-}E$ 65OOutput Color Green Even Pixel (left pixel) $G_{-}OUT3_{-}E$ 66OOutput Color Green Even Pixel (left pixel) $G_{-}OUT4_{-}E$ 66OOutput Color Green Even Pixel (left pixel) $G_{-}OUT5_{-}E$ 68OOutput Color Green Even Pixel (left pixel) $G_{-}OUT6_{-}E$ 69OOutput Color Green Even Pixel (left pixel) $G_{-}OUT7_{-}E$ 70OOutput Color Green Even Pixel (left pixel) $G_{-}OUT7_{-}E$ 70OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT7_{-}D$ 73OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT3_{-}O$ 75OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT3_{-}O$ 76OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT3_{-}O$ 78OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT3_{-}O$ 78OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT4_{-}O$ 78OOutput Color Green Odd Pixel (ri                                                           |          |    |   | 11 7                                       |

| $R_{-}OUT6_{-}O$ 59OOutput Color Red Odd Pixel (right pixel) $R_{-}OUT7_{-}O$ 60OOutput Color Red Odd Pixel (right pixel) $GND$ 61Ground $G_{-}OUT0_{-}E$ 62OOutput Color Green Even Pixel (left pixel) $G_{-}OUT1_{-}E$ 63OOutput Color Green Even Pixel (left pixel) $G_{-}OUT2_{-}E$ 64OOutput Color Green Even Pixel (left pixel) $G_{-}OUT3_{-}E$ 65OOutput Color Green Even Pixel (left pixel) $G_{-}OUT5_{-}E$ 68OOutput Color Green Even Pixel (left pixel) $G_{-}OUT5_{-}E$ 70OOutput Color Green Even Pixel (left pixel) $G_{-}OUT7_{-}E$ 70OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT1_{-}O$ 73OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT2_{-}O$ 75OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT3_{-}O$ 76OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT4_{-}O$ 78OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT4_{-}O$ 81OOutput Color Green Odd Pixel (right pixel) $G_{-}OUT4_{-}O$ 81OOutput Color Green Odd Pixel (                                                           |          |    |   |                                            |

| R_OUT7_O60OOutput Color Red Odd Pixel (right pixel)GND61GroundG_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT3_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT6_E69OOutput Color Green Even Pixel (left pixel)GND71GroundGND71GroundGND72GroundG_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)G_OUT5_E84OOutput Color Green Odd Pixel (right pixel)G_OUT5_O81OOutput Color Green Odd Pixel (right pixel)G_OUT5_O81OOutput Color                                                                                                                                                                                                                                                                                                                                    |          |    | - |                                            |

| GND61GroundG_OUT0_E62OOutput Color Green Even Pixel (left pixel)G_OUT1_E63OOutput Color Green Even Pixel (left pixel)G_OUT3_E64OOutput Color Green Even Pixel (left pixel)G_OUT3_E65OOutput Color Green Even Pixel (left pixel)G_OUT4_E66OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT7_E70OOutput Color Green Even Pixel (left pixel)GND71GroundGND72GroundG_OUT1_O73OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)G_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT5_O80OOOutput Color Green Odd Pixel (right pixel)G_OUT5_E84OOutput Color Green Odd Pixel (right pixel)B_OUT0_E84OOOutput Color Green Odd Pixel (right pixel)G_OUT5_E86OOOutput Color Blue Even Pixel (left pixel)B_OUT                                                                                                                                                                                                                                                                    |          |    | - |                                            |

| $G_{OUT0\_E}$ $62$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT1\_E}$ $63$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT3\_E}$ $64$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT3\_E}$ $65$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT4\_E}$ $66$ $O$ Output Color Green Even Pixel (left pixel) $WDD$ $67$ Power Supply $G_{OUT5\_E}$ $68$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT5\_E}$ $68$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT5\_E}$ $69$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT7\_E}$ $70$ $O$ Output Color Green Even Pixel (left pixel) $G_{OUT7\_E}$ $70$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT1\_O}$ $73$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT1\_O}$ $74$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT3\_O}$ $76$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT4\_O}$ $78$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT4\_O}$ $78$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT4\_O}$ $78$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT5\_O}$ $79$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT4\_O}$ $81$ $O$ Output Color Green Odd Pixel (right pixel) $G_{OUT4\_O}$ $81$ $O$ Output Color Green |          |    | 0 |                                            |

| $G_{OUT1\_E}$ 63OOutput Color Green Even Pixel (left pixel) $G_{OUT2\_E}$ 64OOutput Color Green Even Pixel (left pixel) $G_{OUT3\_E}$ 65OOutput Color Green Even Pixel (left pixel) $G_{OUT4\_E}$ 66OOutput Color Green Even Pixel (left pixel) $VDD$ 67Power Supply $G_{OUT5\_E}$ 68OOutput Color Green Even Pixel (left pixel) $G_{OUT6\_E}$ 69OOutput Color Green Even Pixel (left pixel) $G_{OUT6\_E}$ 69OOutput Color Green Even Pixel (left pixel) $G_{OUT7\_E}$ 70OOutput Color Green Even Pixel (left pixel) $G_{OUT7\_E}$ 70OOutput Color Green Even Pixel (left pixel) $G_{OUT7\_E}$ 71Ground $GND$ 71Ground $G_{OUT1\_O}$ 73O $G_{OUT1\_O}$ 74O $G_{OUT2\_O}$ 75O $G_{OUT3\_O}$ 76O $VDD$ 77 $Power Supply$ $G_{OUT4\_O}$ 78O $G_{OUT5\_O}$ 79O $G_{OUT5\_O}$ 79 $G_{OUT4\_O}$ 81 $G_{OUT5\_O}$ 81 $G_{OUT5\_O}$ 82 $G_{OUT5\_O}$ 81 $G_{OUT5\_O}$ 82 $G_{OUT5\_O}$ 83 $G_{OUT5\_O}$ 84 $G_{OUT5\_O}$ 84 $G_{OUT5\_O}$ 84 $G_{OUT5\_O}$ 84 $G_{OUT5\_O}$ 84 $G_{OUT5\_O}$ 85 $G_{OUT5\_O}$ $G_{OUT5\_O}$ <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                           |          |    |   |                                            |

| $G_OUT2_E$ 64OOutput Color Green Even Pixel (left pixel) $G_OUT3_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT4_E$ 66OOutput Color Green Even Pixel (left pixel) $VDD$ 67Power Supply $G_OUT5_E$ 68OOutput Color Green Even Pixel (left pixel) $G_OUT6_E$ 69OOutput Color Green Even Pixel (left pixel) $G_OUT7_E$ 70OOutput Color Green Even Pixel (left pixel) $GOUT7_E$ 70OOutput Color Green Even Pixel (left pixel) $GND$ 71Ground $GVT1_O$ 73OOutput Color Green Odd Pixel (right pixel) $G_OUT1_O$ 73OOutput Color Green Odd Pixel (right pixel) $G_OUT2_O$ 75OOutput Color Green Odd Pixel (right pixel) $G_OUT3_O$ 76OOutput Color Green Odd Pixel (right pixel) $VDD$ 77Power Supply $G_OUT4_O$ 78OOutput Color Green Odd Pixel (right pixel) $G_OUT5_O$ 79OOutput Color Green Odd Pixel (right pixel) $GND$ 82Ground $GND$ 83Ground $GND$ 83Ground $B_OUT0_E$ 84O $Output Color Green Odd Pixel (right pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87O$                                                                                                                                                                                                                                                |          |    |   |                                            |

| $G_OUT3_E$ 65OOutput Color Green Even Pixel (left pixel) $G_OUT4_E$ 66OOutput Color Green Even Pixel (left pixel) $VDD$ 67Power Supply $G_OUT5_E$ 68OOutput Color Green Even Pixel (left pixel) $G_OUT6_E$ 69OOutput Color Green Even Pixel (left pixel) $G_OUT7_E$ 70OOutput Color Green Even Pixel (left pixel) $GND$ 71Ground $GND$ 72Ground $G_OUT0_O$ 73O $G_OUT1_O$ 74O $G_OUT2_O$ 75O $G_OUT3_O$ 76O $OUtput Color Green Odd Pixel (right pixel)$ $G_OUT3_O$ 78 $O$ Output Color Green Odd Pixel (right pixel) $G_OUT4_O$ 78O $OUtput Color Green Odd Pixel (right pixel)$ $G_OUT5_O$ 79 $O$ Output Color Green Odd Pixel (right pixel) $G_OUT5_O$ 80O $O$ Output Color Green Odd Pixel (right pixel) $G_OUT5_O$ 81O $O$ Output Color Green Odd Pixel (right pixel) $GND$ 82Ground $GND$ 83Ground $B_OUT0_E$ 84O $O$ Output Color Blue Even Pixel (left pixel) $B_OUT1_E$ 85O $O$ Output Color Blue Even Pixel (left pixel) $B_OUT3_E$ 87O $O$ Output Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                       |          |    |   |                                            |

| $G_{-}OUT4_{-}E$ 66OOutput Color Green Even Pixel (left pixel) $VDD$ 67Power Supply $G_{-}OUT5_{-}E$ 68OOutput Color Green Even Pixel (left pixel) $G_{-}OUT6_{-}E$ 69OOutput Color Green Even Pixel (left pixel) $G_{-}OUT7_{-}E$ 70OOutput Color Green Even Pixel (left pixel) $GND$ 71Ground $GND$ 72Ground $G_{-}OUT1_{-}O$ 73O $GUT1_{-}O$ 74O $GUT2_{-}O$ 75O $GUT1_{-}O$ 76O $GUT1_{-}O$ 77 $Power Supply$ $G_{-}OUT3_{-}O$ 76O $GUT1_{-}O$ 78O $Output Color Green Odd Pixel (right pixel)$ $G_{-}OUT4_{-}O$ 78O $GUT1_{-}O$ 79O $GUT1_{-}O$ 81O $GND$ 82Ground $GND$ 83Ground $GND$ 83Ground $GND$ 83Ground $GND$ 83Ground $GND$ 84O $Output Color Blue Even Pixel (left pixel)B_{-}OUT0_{-}E84OOutput Color Blue Even Pixel (left pixel)B_{-}OUT1_{-}E85OOutput Color Blue Even Pixel (left pixel)B_{-}OUT3_{-}E87OOutput Color Blue Even Pixel (left pixel)B_{-}OUT3_{-}E87OUTPU_{-}E86OUTPU_{-}E86OUTPU_{-}EB$                                                                                                                                                                                                                                                                                                                                                                            |          |    |   | •                                          |

| VDD $67$ Power SupplyG_OUT5_E $68$ OOutput Color Green Even Pixel (left pixel)G_OUT6_E $69$ OOutput Color Green Even Pixel (left pixel)G_OUT7_E $70$ OOutput Color Green Even Pixel (left pixel)GND $71$ GroundGND $72$ GroundG_OUT0_O $73$ OOutput Color Green Odd Pixel (right pixel)G_OUT1_O $74$ OOutput Color Green Odd Pixel (right pixel)G_OUT2_O $75$ OOutput Color Green Odd Pixel (right pixel)G_OUT3_O $76$ OOutput Color Green Odd Pixel (right pixel)G_OUT4_O $78$ OOutput Color Green Odd Pixel (right pixel)G_OUT5_O $79$ OOutput Color Green Odd Pixel (right pixel)G_OUT5_O $79$ OOutput Color Green Odd Pixel (right pixel)G_OUT6_O $80$ OOutput Color Green Odd Pixel (right pixel)G_OUT7_O $81$ OOutput Color Green Odd Pixel (right pixel)GND $82$ GroundGND $83$ GroundB_OUT0_E $84$ OOutput Color Blue Even Pixel (left pixel)B_OUT1_E $85$ OOutput Color Blue Even Pixel (left pixel)B_OUT3_E $87$ OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                 |          |    | - |                                            |

| G_OUT5_E68OOutput Color Green Even Pixel (left pixel)G_OUT6_E69OOutput Color Green Even Pixel (left pixel)G_OUT7_E70OOutput Color Green Even Pixel (left pixel)GND71GroundGND72GroundG_OUT0_O73OOutput Color Green Odd Pixel (right pixel)G_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT5_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT5_O80OOutput Color Green Odd Pixel (right pixel)G_OUT4_O81OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                 |          |    | 0 |                                            |

| $G_OUT6_E$ $69$ $O$ Output Color Green Even Pixel (left pixel) $G_OUT7_E$ $70$ $O$ Output Color Green Even Pixel (left pixel) $GND$ $71$ $Ground$ $GND$ $72$ $Ground$ $G_OUT0_O$ $73$ $O$ Output Color Green Odd Pixel (right pixel) $G_OUT1_O$ $74$ $O$ Output Color Green Odd Pixel (right pixel) $G_OUT2_O$ $75$ $O$ Output Color Green Odd Pixel (right pixel) $G_OUT3_O$ $76$ $O$ Output Color Green Odd Pixel (right pixel) $VDD$ $77$ Power Supply $G_OUT4_O$ $78$ $O$ $G_OUT5_O$ $79$ $O$ $Output Color Green Odd Pixel (right pixel)$ $G_OUT5_O$ $79$ $O$ $Output Color Green Odd Pixel (right pixel)$ $G_OUT7_O$ $81$ $O$ $Output Color Green Odd Pixel (right pixel)$ $GND$ $82$ $Ground$ $GND$ $83$ $Ground$ $B_OUT0_E$ $84$ $O$ $Output Color Blue Even Pixel (left pixel)$ $B_OUT1_E$ $86$ $O$ $Output Color Blue Even Pixel (left pixel)$ $B_OUT3_E$ $87$ $O$ $Output Color Blue Even Pixel (left pixel)$                                                                                                                                                                                                                                                                                                                                                                              |          |    |   | 11 0                                       |

| G_OUT7_E70OOutput Color Green Even Pixel (left pixel)GND71GroundGND72GroundG_OUT0_O73OOutput Color Green Odd Pixel (right pixel)G_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)G_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OB_OUT1_E85OB_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |    | 0 | •                                          |

| GND71GroundGND72GroundG_OUT0_O73OOutput Color Green Odd Pixel (right pixel)G_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |    | 0 | Output Color Green Even Pixel (left pixel) |

| GND72GroundG_OUT0_O73OOutput Color Green Odd Pixel (right pixel)G_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | G_OUT7_E | 70 | 0 | Output Color Green Even Pixel (left pixel) |

| G_OUT0_O73OOutput Color Green Odd Pixel (right pixel)G_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundMDD83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GND      | 71 |   | Ground                                     |

| G_OUT1_O74OOutput Color Green Odd Pixel (right pixel)G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GND      | 72 |   | Ground                                     |

| G_OUT2_O75OOutput Color Green Odd Pixel (right pixel)G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | G_OUT0_O | 73 | 0 | Output Color Green Odd Pixel (right pixel) |

| G_OUT3_O76OOutput Color Green Odd Pixel (right pixel)VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | G_OUT1_O |    | 0 | Output Color Green Odd Pixel (right pixel) |

| VDD77Power SupplyG_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | G_OUT2_O | 75 | 0 | Output Color Green Odd Pixel (right pixel) |

| G_OUT4_O78OOutput Color Green Odd Pixel (right pixel)G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 76 | 0 | Output Color Green Odd Pixel (right pixel) |

| G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VDD      | 77 |   | Power Supply                               |

| G_OUT5_O79OOutput Color Green Odd Pixel (right pixel)G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | G_OUT4_O | 78 | 0 | Output Color Green Odd Pixel (right pixel) |

| G_OUT6_O80OOutput Color Green Odd Pixel (right pixel)G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | G_OUT5_O | 79 | 0 |                                            |

| G_OUT7_O81OOutput Color Green Odd Pixel (right pixel)GND82GroundGND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 80 | 0 |                                            |

| GND82GroundGND83GroundB_OUT0_E84ODUT1_E85ODUT2_E86ODUT2_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 81 | 0 |                                            |

| GND83GroundB_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |    |   |                                            |

| B_OUT0_E84OOutput Color Blue Even Pixel (left pixel)B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |    |   |                                            |

| B_OUT1_E85OOutput Color Blue Even Pixel (left pixel)B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |    | 0 |                                            |

| B_OUT2_E86OOutput Color Blue Even Pixel (left pixel)B_OUT3_E87OOutput Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |    |   |                                            |

| B_OUT3_E 87 O Output Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |    |   |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |    | - |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B_OUT4_E | 88 | 0 | Output Color Blue Even Pixel (left pixel)  |

| B_OUT5_E     89     O     Output Color Blue Even Pixel (left pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |    |   | -                                          |

*November, 1999* Revision B SmartASIC Confidential

| B_OUT6_E         | 90   | 0      | Output Color Blue Even Pixel (left pixel) |

|------------------|------|--------|-------------------------------------------|

| VDD              | 91   |        | Power Supply                              |