#### **Features**

- Organization

- 131,072 words  $\times$  32 bits  $\times$  2 banks

- Fully synchronous

- All signals referenced to positive edge of clock

- Internal pipeline operation

- Column address can be changed every clock cycle

- Two internal banks controlled by BA (bank select)

- High speed

- 150/133/100 MHz

- 6.5/7/9 ns clock access time

- 1024 refresh cycles, 16 ms refresh interval (Auto or Self)

- · Auto precharge and Auto refresh modes

- Two color registers

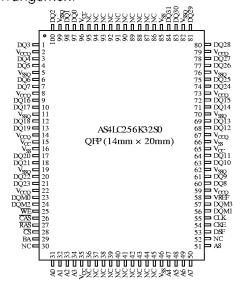

## Pin arrangement

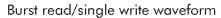

- Burst read, single write operation

- LVTTL compatible I/ O

- 3.3V power supply

- JEDEC standard package, pinout and function

- 100-pin PQFP

- · Read/ write data masking

- Programmable burst length (1/2/4/8/full page)

- Programmable burst sequence (sequential/interleaved)

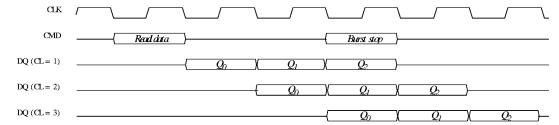

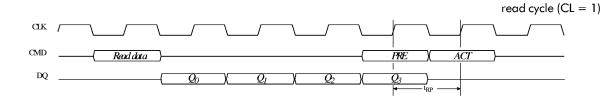

- Programmable CAS latency (1/2/3)

- · Graphics features

- SMRS cycle

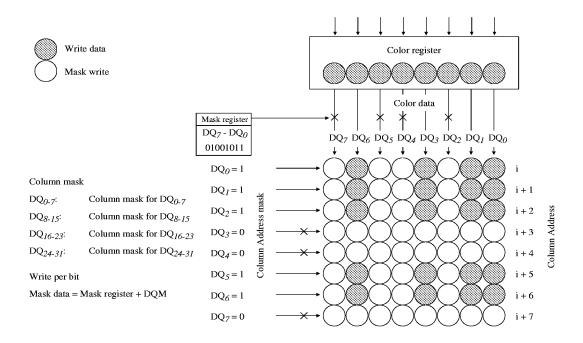

- Block write (8 columns), write per bit

#### Pin designation

| Pin(s)                             | Description                  |

|------------------------------------|------------------------------|

| DQM0 to DQM3                       | Output disable/ write mask   |

| A0 to A8                           | Address inputs               |

| BA                                 | Bank select input            |

| DQ0 to DQ31                        | Input/ output                |

| RAS                                | Row address strobe           |

| CAS                                | Column address strobe        |

| WE                                 | Write enable                 |

| <u>cs</u>                          | Chip select                  |

| V <sub>CC</sub> , V <sub>CCQ</sub> | Power $(3.3V \pm 0.3V)$      |

| V <sub>SS</sub> , V <sub>SSQ</sub> | Ground                       |

| CLK                                | Clock input                  |

| CKE                                | Clock enable                 |

| DSF                                | Special function enable      |

| VREF                               | SSIL reference voltage input |

#### Selection guide

|                                            | Symbol          | -150 | -133 | -100 | Unit |

|--------------------------------------------|-----------------|------|------|------|------|

| Bus frequency                              | $ m f_{max}$    | 150  | 133  | 100  | MHz  |

| Maximum clock access time                  | $t_{AC}$        | 6.5  | 7    | 9    | ns   |

| Minimum address setup time                 | t <sub>AS</sub> | 2    | 2.5  | 2.5  | ns   |

| Minimum address hold time                  | t <sub>AH</sub> | 1.5  | 1.5  | 1.5  | ns   |

| Minimum row cycle time                     | t <sub>RC</sub> | 60   | 67.5 | 78   | ns   |

| Maximum operating current                  | $I_{CC1}$       | 300  | 275  | 185  | mA   |

| Maximum CMOS standby current, self refresh | $I_{CC6}$       | 3    | 3    | 3    | mA   |

DID 11-60**00**2-A. 1/12/99

ALLIANGE SEMICONDUCTOR

405

Copyright ©1998 Alliance Semiconductor. All rights reserved.

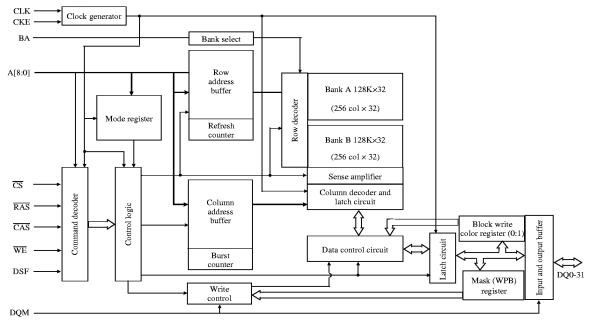

#### Functional description

The AS4LC256K32SO is a high performance 8 megabit CMOS Synchronous Graphics Random Access Memory (SGRAM) organized as 131,072 words × 32 bits × 2 banks. Very high bandwidth is achieved using a pipelined architecture where all inputs and outputs are referenced to the rising edge of a common clock. Programmable burst mode can be used to read up to a full page of data without selecting a new column address.

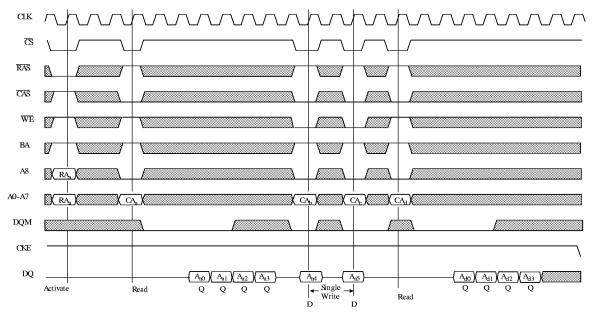

The two internal banks can be alternately accessed (read or write) at the maximum clock frequency for seamless interleaving operations. This provides a significant advantage over asynchronous EDO and fast page mode devices.

This SGRAM product also features a programmable mode register, allowing users to select read latency as well as burst length and type (sequential or interleaved). Lower latency improves first data access in terms of CIK cycles, while higher latency improves maximum frequency of operation. This feature enables flexible performance optimization for a variety of applications.

DRAM commands and functions are decoded from control inputs. Basic commands are as follows:

- · Mode register set

- Select column, write

- · Auto precharge with read/ write

- · Special mode register set

- De-activate bank

- Select column, read

- Self refresh

- Deactivate all banks

- Deselect, power down

- Block write

- Select row, activate bank

- CBR refresh

- Write per bit

The 8 Mb SGRAM device is available in a 100-pin PQFP. It operates with a power supply of  $3.3V \pm 0.3V$ . Multiple power and ground pins are provided for low switching noise and EMI. Inputs and outputs are LVTIL compatible.

#### Logic block diagram

406

ALLIANCE SEMICONDUCTOR

DID 11-60002-A 1/12/99

| Albert Aller B    | 000000000000000000000000000000000000000                                                | 10000000000000000000000000000000000000                | 00000000000000000000000000000000000000                | 50000000000000000000000000000000000000                |

|-------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|                   |                                                                                        |                                                       |                                                       |                                                       |

| Symbol            | Min                                                                                    | Nominal                                               | Max                                                   | Unit                                                  |

| $V_{CC}V_{CCQ}$   | 3.0                                                                                    | 3.3                                                   | 3.6                                                   | V                                                     |

| GND               | 0.0                                                                                    | 0.0                                                   | 0.0                                                   | V                                                     |

| $V_{\mathrm{IH}}$ | 2.0                                                                                    | -                                                     | $V_{CC} + 0.3$                                        | V                                                     |

| $V_{ m IL}$       | -0.5 <sup>†</sup>                                                                      | _                                                     | 0.8                                                   | V                                                     |

| $V_{OH}$          | 2.4                                                                                    | _                                                     | -                                                     | V                                                     |

| $V_{OL}$          | -                                                                                      |                                                       | 0.4                                                   | V                                                     |

| $T_A$             | 0                                                                                      |                                                       | 70                                                    | °C                                                    |

|                   | Symbol  Vac Vacq  GND  V <sub>IH</sub> V <sub>IL</sub> V <sub>OH</sub> V <sub>OL</sub> | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

$<sup>^{\</sup>dagger}V_{IL}$  min = -1.5V for pulse widths less than 5 ns.

Recommended operating conditions apply throughout this document unless otherwise specified.

## Absolute maximum ratings

| Parameter                     | Symbol            | Min  | Max  | Unit |

|-------------------------------|-------------------|------|------|------|

| Input voltage                 | $V_{in}, V_{out}$ | -1.0 | +4.6 | V    |

| Power supply voltage          | $v_{cc}v_{ccQ}$   | -1.0 | +4.6 | V    |

| Storage temperature (plastic) | $T_{SIG}$         | -55  | +150 | °C   |

| Power dissipation             | $P_{D}$           | _    | 1    | W    |

| Short circuit output current  | I <sub>out</sub>  | _    | 50   | mA   |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

$<sup>^{\</sup>ddagger}I_{\mbox{\scriptsize OH}}\!=$  -2mA, and  $I_{\mbox{\scriptsize OL}}\!=$  2mA

## DC electrical characteristics

|                                                 |                    |                                                                                                                                                                                      |       | - 1 | 50  | -1  | 33  | -1  | 00  |      |         |

|-------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-----|-----|-----|-----|------|---------|

| Parameter                                       | Symbol             | Test conditions                                                                                                                                                                      |       | Min | Max | Min | Max | Min | Max | Unit | Notes   |

| Input leakage current                           | $I_{\mathrm{IL}}$  | $0V \le V_{in} \le V_{CC}$<br>Pins not under test = $0V$                                                                                                                             |       | -3  | +3  | -3  | +3  | -3  | +3  | μΑ   |         |

| Output leakage current                          | $I_{OL}$           | $D_{OUT}$ disabled, $0V \le V_{out} \le V_{CCQ}$                                                                                                                                     |       | -3  | +3  | -3  | +3  | -3  | +3  | μΑ   |         |

| Operating current                               | т                  | t <sub>RC</sub> ≥ min, IOL= 0mA,                                                                                                                                                     | CL= 3 | -   | 300 | _   | 275 | _   | 185 | A    | 1       |

| (one bank active)                               | l <sub>CC1</sub>   | burst length = 1                                                                                                                                                                     | CL= 2 | _   | 275 | _   | 250 | _   | 175 | mA   | 1       |

| Precharge standby current                       | $I_{CC2P}$         | $CKE \le V_{IL}(max)$ , $t_{CK} = 15$ ns                                                                                                                                             |       | _   | 3   | _   | 3   | _   | 3   | mA   |         |

| (power down mode)                               | I <sub>CC2PS</sub> | $\text{CKE\&CLK} \leq \text{V}_{\text{IL}}(\text{max}),  \text{t}_{\text{CK}} = \infty$                                                                                              |       | -   | 3   | _   | 3   | _   | 3   | mA   | _       |

| Precharge standby current (non power down mode) | $I_{CC2N}$         | $CS \ge V_{IH}(min)$ , $CKE \ge V_{IH}(min)$ , $t_{CC} = 15$ ns; input signals changed once during 30 ns                                                                             |       | _   | 45  | ı   | 45  | _   | 45  | mA   |         |

| (non power down mode)                           | I <sub>CC2NS</sub> | $CLK \le V_{IL}(max)$ , $CKE \ge V_{IH}(min)$ , $t_{CK} = \infty$ ; input signals stable                                                                                             |       | -   | 20  | -   | 20  | -   | 20  | mA   |         |

| Active standby current                          | I <sub>CC3P</sub>  | $CKE \le V_{IL}(max)$ , $t_{CK} = 15$ ns                                                                                                                                             |       | _   | 3   | _   | 3   | _   | 3   | mA   |         |

| (power down mode)                               | $I_{CC3PS}$        | CLK, CKE $\leq$ V <sub>II</sub> (max), t <sub>CK</sub> = $\infty$                                                                                                                    |       | _   | 3   | _   | 3   | _   | 3   | mA   |         |

| Active standby current (non power down mode,    | I <sub>CC3N</sub>  | CKE $\geq$ V <sub>IH</sub> (min), CS $\geq$ V <sub>IH</sub> (min),<br>t <sub>CK</sub> = 15 ns; input signals changed<br>once during 30 ns                                            |       | _   | 50  | -   | 50  | _   | 50  | mA   |         |

| one bank active)                                | $I_{CC3NS}$        | $\begin{aligned} & \text{CKE} \geq V_{\text{IH}}(\text{min}), & \text{CLK} \geq V_{\text{IL}}(\text{max}), \\ & t_{\text{CK}} = \infty; & \text{input signals stable} \end{aligned}$ |       | _   | 25  | -   | 25  | _   | 25  | mA   |         |

| Operating current                               |                    | $I_{OL} = 0$ mA, Page burst                                                                                                                                                          | CL= 3 | _   | 225 | _   | 200 | _   | 190 |      |         |

| (burst mode)                                    | I <sub>CC4</sub>   | All banks activated $t_{CCD} = t_{CCD}(min)$                                                                                                                                         | CL= 2 | _   | 175 | _   | 150 | _   | 140 | mA   | 1,2     |

| Refresh current                                 | T                  | t >t (min)                                                                                                                                                                           | CL= 3 | _   | 180 | _   | 150 | _   | 150 | mA   | 3       |

| Achesii current                                 | Iccs               | $t_{RC} \ge t_{RC}(\min)$                                                                                                                                                            | CL= 2 | _   | 150 | _   | 130 | _   | 130 | ША   | <i></i> |

| Self refresh current                            | ICC6               | CKE≤0.2 V                                                                                                                                                                            |       | _   | 3   | _   | 3   | _   | 3   | mA   |         |

<sup>\*</sup> CL = CAS latency

<sup>1</sup> This parameter depends on output loading and cycle rates. Measured with outputs open, inputs only change one time during  $t_{CK}$  (min).

$<sup>2 \</sup>quad \text{Assumed } t_{CCD}(min)$

<sup>3</sup> Refresh period = 16ms

# AC parameters common to all waveforms

|                  |                                          | CAS     | -1  | 50   | -1   | 33   | -1  | .00  |      |       |

|------------------|------------------------------------------|---------|-----|------|------|------|-----|------|------|-------|

| Symbol           | Parameter                                | latency | Min | Max  | Min  | Max  | Min | Max  | Unit | Notes |

| t <sub>RRD</sub> | Row active to row active delay           |         | 6.5 | _    | 7.5  | _    | 10  | _    | ns   | 1     |

| t <sub>RCD</sub> | RAS to CAS delay time                    |         | 20  | _    | 22.5 | _    | 30  | _    | ns   | 1     |

| t <sub>RP</sub>  | Row precharge                            |         | 20  | _    | 22.5 | _    | 30  | _    | ns   | 1     |

| t <sub>RAS</sub> | Row active                               |         | 40  | 120K | 45   | 120K | 60  | 120K | ns   | 1     |

| t <sub>RC</sub>  | Row cycle time                           |         | 60  | _    | 67.5 | _    | 90  | _    | ns   | 1     |

| t <sub>CDL</sub> | Last data in to new column address delay |         | 1   | _    | 1    | _    | 1   | _    | CLK  | 2     |

| t <sub>RDL</sub> | Last data in to row precharge            |         | 1   | _    | 1    | _    | 1   | _    | CLK  | 2     |

| t <sub>BDL</sub> | Last data in to burst stop               |         | 1   | _    | 1    | _    | 1   | 1    | CLK  | 2     |

| t <sub>CCD</sub> | Column address to column address delay   |         | 1   | _    | 1    | _    | 1   | _    | CLK  | 3     |

|                  | CIV avalations                           | 3       | 6.7 | _    | 7.5  | _    | 10  | -    |      | 4     |

| $t_{CK}$         | CLK cycle time                           | 2       | 10  | _    | 12   | -    | 15  | 1000 | ns   | 4     |

| +                | CIV to valid output delev                | 3       | _   | 6.5  | _    | 7.0  | _   | 9.0  |      | 4,5   |

| t <sub>AC</sub>  | CLK to valid output delay                | 2       | _   | 7.5  | _    | 10   | _   | 12   | ns   | 4,5   |

| t <sub>OH</sub>  | Output data hold time                    |         | 3.5 | -    | 3.5  | -    | 3.5 | 1    | ns   |       |

| t <sub>CH</sub>  | CIK high pulse width                     |         | 3.0 | _    | 3.0  | _    | 3.5 | -    | ns   | 6     |

| $t_{CL}$         | CLK low pulse width                      |         | 2.5 | -    | 3.0  | -    | 3.5 | -    | ns   | 6     |

| $t_S$            | Input setup time                         |         | 2.0 | _    | 2.5  | _    | 2.5 | -    | ns   | 6     |

| t <sub>H</sub>   | Input hold time                          |         | 1.5 | _    | 1.5  | _    | 1.5 | _    | ns   | 6     |

| t <sub>SLZ</sub> | CIK to output in low Z                   |         | 3   | _    | 3    | _    | 3   | _    | ns   | 5     |

| t <sub>SHZ</sub> | CLK to output in high Z                  |         | 3.5 | 6.7  | 3.5  | 7.5  | 3.5 | 10   | ns   |       |

Minimum clock cycles = (Minimum time / clock cycle time) rounded up

<sup>2</sup> Minimum delay required to complete write.

<sup>3</sup> Column address change allowed every cycle.

<sup>4</sup> Parameters dependent on CAS latency.

<sup>5</sup> If clock rising time > 1ns, (tr/ 2-0.5)ns should be added to parameter.

<sup>6</sup> If (tr and tf) > 1ns, [(tr+tf)/ 2-1]ns should be added to parameter.

| ***************                    |                        | RRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRR | 6 A              |           | 900000 | 000000000000000000000000000000000000000 | COCCOCCACACACACACACACACACACACACACACACAC | RRRRRRRRRR | XXXXXXXXXXXXXX | RRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRR | RRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRR |           | RRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRR |

|------------------------------------|------------------------|-----------------------------------------|------------------|-----------|--------|-----------------------------------------|-----------------------------------------|------------|----------------|-----------------------------------------|-----------------------------------------|-----------|-----------------------------------------|

| Operating modes                    |                        |                                         | -                |           | XXXXX  |                                         |                                         |            |                |                                         |                                         |           |                                         |

| Command                            |                        | CKE <sub>n-1</sub>                      | CKE <sub>n</sub> | <u>CS</u> | RAS    | CAS                                     | WE                                      | DSF        | DQM            | BA                                      | A8                                      | A7-A0     | Note                                    |

| Mode register set                  |                        | Н                                       | X                | L         | L      | L                                       | L                                       | L          | X              |                                         | Op                                      | code      | 1,2                                     |

| Special mode register set          |                        | Н                                       | X                | L         | L      | L                                       | L                                       | Н          | X              |                                         | Op                                      | code      |                                         |

| Auto refresh                       |                        | Н                                       | Н                | L         | L      | L                                       | Н                                       | X          | X              | X                                       | X                                       | X         | 3                                       |

|                                    | Entry                  | Н                                       | L                | L         | L      | L                                       | Н                                       | X          | X              | X                                       | X                                       | X         | 3                                       |

| Self refresh                       | Exit                   | L                                       | Н                | L         | Н      | Н                                       | Н                                       | X          | X              | X                                       | X                                       | X         | 3                                       |

|                                    | EXII                   | L                                       | п                | Н         | X      | X                                       | X                                       | X          | X              | X                                       | X                                       | X         | 3                                       |

| Bank activate                      |                        | - н                                     | Х                | L         | L      | Н                                       | Н                                       | L          | X              | V                                       |                                         | v address |                                         |

| Dank activate                      | w/ WPB                 | - н                                     | А                | L         | L      | п                                       | п                                       | Н          | X              | V                                       | · rov                                   | v address |                                         |

| Dead                               | Auto precharge disable | - н                                     | Х                | L         | Н      | L                                       | Н                                       | X          | Х              | v                                       | L                                       | column    | 4                                       |

| Read                               | Auto precharge enable  | - н                                     | Λ                | L         | н      | L                                       | н                                       | Λ          | Λ              | V                                       | Н                                       | address   | 4,5                                     |

| Write                              | Auto precharge disable | - н                                     | v                | X L       | Н      | L                                       | L                                       | т.         | X              | V                                       | L                                       | column    | 4                                       |

|                                    | Auto precharge enable  |                                         | Λ                |           |        |                                         |                                         | L          |                | ٧                                       | Н                                       | address   | 4,5                                     |

| TOI 1 '.                           | Auto precharge disable | **                                      | 37               |           |        |                                         |                                         |            | v              | v                                       | L                                       | column    |                                         |

| Block write                        | Auto precharge enable  | - H                                     | X                | L         | Н      | L                                       | L                                       | Н          | X              | V                                       | Н                                       | address   |                                         |

| Burst stop                         |                        | Н                                       | X                | L         | Н      | Н                                       | L                                       | X          | X              | X                                       | X                                       | X         | 6                                       |

| D 1                                | Selected bank          |                                         | 3.7              |           |        |                                         |                                         | 37         | 37             | V                                       | L                                       | 37        |                                         |

| Precharge                          | Both banks             | - H                                     | X                | L         | L      | Н                                       | L                                       | X          | X              | X                                       | Н                                       | X         |                                         |

|                                    | D.                     |                                         |                  | Н         | X      | X                                       | X                                       |            | X              | X                                       | X                                       | X         |                                         |

| Clock suspend or active power down | Entry                  | Н                                       | L                | L         | V      | V                                       | V                                       |            | X              | X                                       | X                                       | X         | -                                       |

| power down                         | Exit                   | L                                       | Н                | X         | X      | X                                       | X                                       |            | X              | X                                       | X                                       | X         | _                                       |

|                                    | D.                     | **                                      |                  | Н         | X      | X                                       | X                                       |            | X              | X                                       | X                                       | X         |                                         |

| Precharge power down               | Entry                  | H                                       | L                | L         | Н      | Н                                       | Н                                       |            | X              | X                                       | X                                       | X         | -                                       |

| mode                               |                        | _                                       |                  | Н         | X      | X                                       | X                                       |            | X              | X                                       | X                                       | X         | -                                       |

|                                    | Exit                   | L                                       | Н                | L         | V      | V                                       | V                                       |            | X              | X                                       | X                                       | X         | -                                       |

| DQM                                |                        | Н                                       | X                | X         | X      | X                                       | X                                       |            | V              | X                                       | X                                       | X         | 7                                       |

| Deselect device                    |                        | Н                                       | X                | Н         | X      | X                                       | X                                       | X          | X              | X                                       | X                                       | X         |                                         |

| No operation                       |                        | Н                                       | X                | L         | Н      | Н                                       | Н                                       | X          | X              | X                                       | X                                       | X         |                                         |

<sup>1</sup> OP = operation code

A0~ A8 BA see above

- 2 MRS can be issued only when both banks are precharged. A new command can be issued 2 clock cycles after MRS

- 3 Auto refresh functions similarly to CBR DRAM refresh. However, precharge is automatic. Auto/ self refresh can only be issued after both banks are precharged.

- 4 A8: bank select address. If low during read, write, row active and precharge, bank A is selected.

If high during those states, bank B is selected. Both banks are selected and A8 is ignored if A7 is high during row precharge.

- 5 A new read/ write command cannot be issued during a burst read/ write with auto precharge.

It must be issued after the end of the burst. A new row active command can be issued after t<sub>RP</sub> from the end of the burst.

- 6 Burst stop command valid at every burst length.

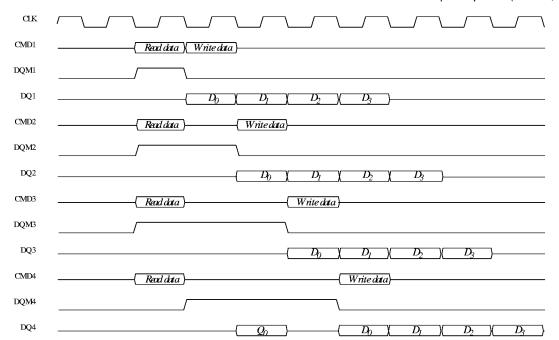

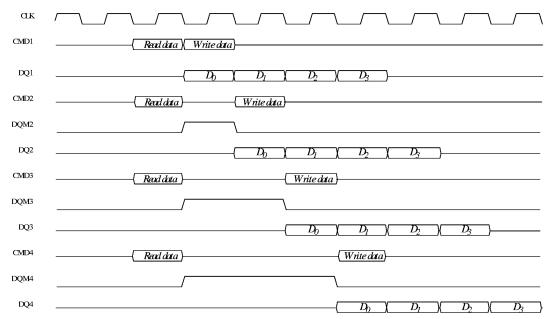

- 7 DQM sampled at positive edge of CLK Data-in may be masked at every CLK (Write DQM latency is 0). Data-out mask is active 2 CLK cycles after issuance. (Read DQM latency is 2).

ALLIANCE SEMICONDUCTOR

DID 11-60002-A. 1/12/99

## Mode register fields

#### Register programmed with MRS

| Address  | BA    | A8   | A7 | A6 | A5      | A4 | A3 | A2 | A1         | A0 |

|----------|-------|------|----|----|---------|----|----|----|------------|----|

| Function | Write | mode | CR |    | LT mode |    | ВТ | bu | ırst lengt | h  |

RFU = 0 during MRS cycle.

## Write burst length

| BA | A8 | Mode                             |

|----|----|----------------------------------|

| 0  | 0  | Normal                           |

| 1  | 0  | Multiple burst with single write |

Burst type

| A3 | Туре        |

|----|-------------|

| 0  | Sequential  |

| 1  | Interleaved |

#### Color register

| A7 | Registers |

|----|-----------|

| 0  | One color |

| 1  | Two color |

#### CAS latency

| A6 | A5 | A4 | Latency  |

|----|----|----|----------|

| 0  | 0  | 0  | Reserved |

| 0  | 0  | 1  | 1        |

| 0  | 1  | 0  | 2        |

| 0  | 1  | 1  | 3        |

| 1  | X  | X  | Reserved |

#### Burst length

| A2 | Al | A0 | BT = 0                |

|----|----|----|-----------------------|

| 0  | 0  | 0  | 1                     |

| 0  | 0  | 1  | 2                     |

| 0  | 1  | 0  | 4                     |

| 0  | 1  | 1  | 8                     |

| 1  | X  | X  | Reserved <sup>†</sup> |

†Burst length = full page when  $A2 \sim A0 = 1$ .

(burst length = 2)

| Initial address |   |        |       |   |

|-----------------|---|--------|-------|---|

| A0              |   | ential | Inter |   |

| 0               | 0 | 1      | 0     | 1 |

| 1               | 1 | 0      | 1     | 0 |

Burst sequence

(burst length = 4)

Initial address

| Al | A0 | Sequential |   |   |   | Interleave |   |   |   |

|----|----|------------|---|---|---|------------|---|---|---|

| 0  | 0  | 0          | 1 | 2 | 3 | 0          | 1 | 2 | 3 |

| 0  | 1  | 1          | 2 | 3 | 0 | 1          | 0 | 3 | 2 |

| 1  | 0  | 2          | 3 | 0 | 1 | 2          | 3 | 0 | 1 |

| 1  | 1  | 3          | 0 | 1 | 2 | 3          | 2 | 1 | 0 |

## Burst sequence

(burst length = 8)

Initial address

|    | mma aaa | .00.5 | _ |   |   |      |        |   |   |   |   |   |   |       |       |   |   |   |

|----|---------|-------|---|---|---|------|--------|---|---|---|---|---|---|-------|-------|---|---|---|

| A2 | A1      | A0    |   |   |   | Sequ | ential |   |   |   |   |   |   | Inter | leave |   |   |   |

| 0  | 0       | 0     | 0 | 1 | 2 | 3    | 4      | 5 | 6 | 7 | 0 | 1 | 2 | 3     | 4     | 5 | 6 | 7 |

| 0  | 0       | 1     | 1 | 2 | 3 | 4    | 5      | 6 | 7 | 0 | 1 | 0 | 3 | 2     | 5     | 4 | 7 | 6 |

| 0  | 1       | 0     | 2 | 3 | 4 | 5    | 6      | 7 | 0 | 1 | 2 | 3 | 0 | 1     | 6     | 7 | 4 | 5 |

| 0  | 1       | 1     | 3 | 4 | 5 | 6    | 7      | 0 | 1 | 2 | 3 | 2 | 1 | 0     | 7     | 6 | 5 | 4 |

| 1  | 0       | 0     | 4 | 5 | 6 | 7    | 0      | 1 | 2 | 3 | 4 | 5 | 6 | 7     | 0     | 1 | 2 | 3 |

| 1  | 0       | 1     | 5 | 6 | 7 | 0    | 1      | 2 | 3 | 4 | 5 | 4 | 7 | 6     | 1     | 0 | 3 | 2 |

| 1  | 1       | 0     | 6 | 7 | 0 | 1    | 2      | 3 | 4 | 5 | 6 | 7 | 4 | 5     | 2     | 3 | 0 | 1 |

| 1  | 1       | 1     | 7 | 0 | 1 | 2    | 3      | 4 | 5 | 6 | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

ALLIANCE SEMICONDUCTOR DD 11-60002-A 1/12/99

| 100000000000000000000000000000000000000 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin descrip                             | tions                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin                                     | Name                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CIK                                     | System clock               | All operations synchronized to rising edge of CLK, CLK, driven by the system clock, increments the internal burst counter and controls output registers.                                                                                                                                                                                                                                                                                                            |

| СКЕ                                     | Clock enable               | Controls CLK input. If CKE is high, the next CLK rising edge is valid. If CKE is low, the internal clock is suspended from the next clock cycle and the burst address and output states are frozen. If both banks are idle and CKE goes low, the SCRAM will enter power down mode from the next clock cycle. When in power down mode and CKE is low, no input commands will be acknowledged. To exit power down mode, raise CKE high before the rising edge of CLK. |

| CS                                      | Chip select                | Enables or disables device operation by masking or enabling all inputs except CLK, CKE, DQM. Input commands are ignored when $\overline{CS}$ = High.                                                                                                                                                                                                                                                                                                                |

| A0~ A8                                  | Address                    | Row and column addresses are multiplexed. Row address: A0~A8 during Active command. Column address: A0~A7 when $\overline{\text{CAS}}$ is active; A8 enables/disables Auto Prechage.                                                                                                                                                                                                                                                                                |

| BA                                      | Bank select                | Memory cell array is organized in 2 banks. BA selects which internal bank will be active. BA is latched during bank activate, read, write, mode register set, and precharge operations. Asserting BA low selects Bank A; BA high selects Bank B.                                                                                                                                                                                                                    |

| RAS                                     | Row address strobe         | Enables row access and precharge operation. When $\overline{RAS}$ is low, row address is latched at the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                         |

| CAS                                     | Column address strobe      | Enables column access. When $\overline{\text{CAS}}$ is low, column address is latched at the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                    |

| WE                                      | Write enable               | Enables write operation and row precharge operation. When $\overline{WE}$ is low, input data is latched starting from $\overline{CAS}$                                                                                                                                                                                                                                                                                                                              |

| DQM0~3                                  | Output disable/ write mask | Controls I/ O buffers. When DQM is high, output buffers are disabled during a read operation and input data is masked during a write operation. DQM latency is 2 clocks for Read and 0 clocks for Write.                                                                                                                                                                                                                                                            |

| DQ0~DQ31                                | Data input/ output         | Data inputs/ outputs are multiplexed. Input mask for Writer-per-bit; column address mask when block write is active.                                                                                                                                                                                                                                                                                                                                                |

| DSF                                     | Special function variable  | Enables block write, write-per-bit, and/ or special mode register load.                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD</sub> / V <sub>SS</sub>       | Power supply/ ground       | Power and ground for core logic and input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>DDQ</sub> / V <sub>SSQ</sub>     | Data output power/ ground  | Power and ground for data output buffers.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                         |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

DID 11-60002-A 1/12/99 ALLIANCE SEMICONDUCTOR 41.3

| Device operat                                |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command                                      | Pin settings                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                              |                                                                                                                                                                                                       | The following sequence is recommended prior to normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Power up                                     |                                                                                                                                                                                                       | <ol> <li>Apply power, start clock, and hold all inputs high.</li> <li>After power-up, pause for a minimum of 100μs.         Drive CKE high prior to a positive clock edge; all others NOP.     </li> <li>Precharge both banks.</li> <li>Perform a minimum of 2 auto refresh cycles to stabilize internal circuitry.</li> <li>Perform Mode Register Set command to initialize mode register.</li> </ol>                                                                                                                                                                                                                 |

| Mode register set                            | $\overline{CS} = \overline{RAS} = \overline{CAS} = \overline{WE} =$ low; $A0 \sim A8 =$ opcode                                                                                                        | The mode register stores the user selected opcode for the SCRAM operating modes. The CAS latency, burst length, burst type, test mode and other vendor specific functions are selected/ programmed during the Mode Register Set command cycle. The default setting of the mode register is not defined after power-up. Therefore, it is recommended that the power-up and mode register set cycle be executed prior to normal SCRAM operation. Refer to the Mode Register Set table and timing for details.                                                                                                            |

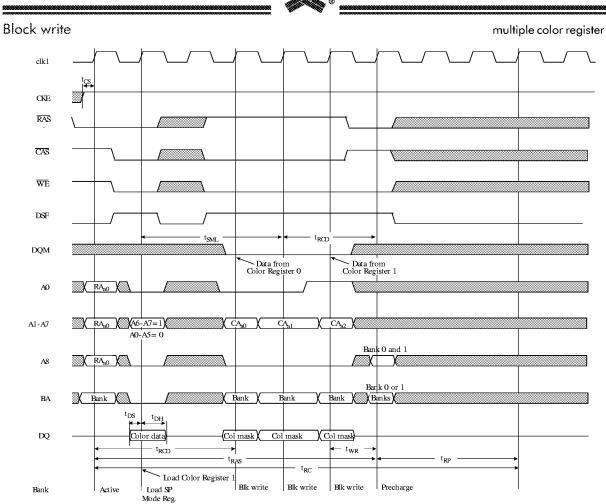

| Special mode register set                    |                                                                                                                                                                                                       | Use this command to load the mask and color registers used in block write and masked write cycles. Control information is applied to address inputs; data to be written to color or mask registers is applied to DQs. If $A6 = 1$ , and all other inputs are 0, color register 0 receives DQ data. If $A6 = A7 = Mode$ Register $M7 = 1$ , color register 1 receives DQ data. If $A5 = 1$ and all other address inputs are 0, mask register receives DQ data.                                                                                                                                                          |

| Device deselect<br>and no operation<br>(NOP) | $\overline{CS}$ = high                                                                                                                                                                                | The SGRAM is deselected when $\overline{CS}$ is high. $\overline{CS}$ high disables the command decoder such that $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ and address inputs are ignored. Device deselection is also considered a NOP. The SGRAM also performs a NOP when $\overline{RAS}$ , $\overline{CAS}$ , and $\overline{WE}$ = high. Since the NOP performs no operation, it may be used as a wait state in performing normal SGRAM functions.                                                                                                                                                    |

| Bank activation                              | $\overline{\text{CS}} = \overline{\text{RAS}} = \text{low}; \overline{\text{CAS}} = \overline{\text{WE}} = \text{high}; A0 \sim A8 = \text{row address}; BA = \text{bank select}$                     | The SCRAM is configured with two internal banks. Use the Bank Activate command to select a row in one of the two idle banks. Initiate a read or write operation after $t_{\text{RCD}}(\text{min})$ from the time of bank activation.                                                                                                                                                                                                                                                                                                                                                                                   |

| Bank activation with WPB                     |                                                                                                                                                                                                       | Write-per-bit is activated during a Bank Activation command. All write or block write cycles to the selected bank/ row are masked based on the mask register.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

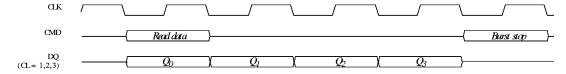

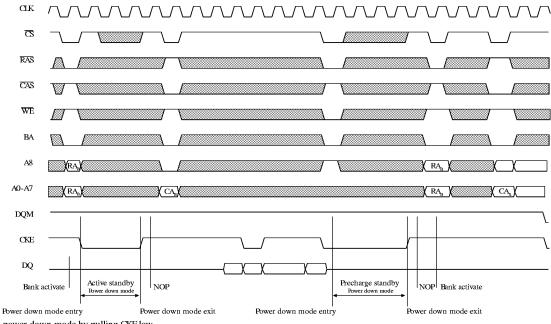

| Burst read                                   | $\overline{\text{CS}} = \overline{\text{CAS}} = A8 = \text{low};$<br>$\overline{\text{RAS}} = \overline{\text{WE}} = \text{high}; \text{BA} = \text{bank select}, A0 \sim A7 = \text{column address}$ | Use the Burst Read command to access a consecutive burst of data from an active row in an active bank. Burst read can be initiated on any column address of an active row. The burst length, sequence and latency are determined by the mode register setting. The first output data appears after the CAS latency from the read command. The output goes into a high impedance state at the end of the burst (BL= 1,2,4,8) unless a new burst read is initiated to form a gapless output data stream. Terminate the burst with a burst stop command, precharge command to the same bank or another burst read/ write. |

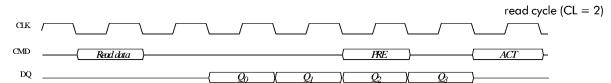

| Burst write                                  | $\overline{\text{CS}} = \overline{\text{CAS}} = \overline{\text{WE}} = \text{A10} = \text{low}; \overline{\text{RAS}} = \text{high}; \text{A0} \sim \text{A8} = \text{column address}$                | Use the Burst Write command to write data into the SGRAM on consecutive clock cycles to adjacent column addresses. The burst length and addressing mode is determined by the mode register opcode. Input the initial write address in the same clock cycle as the Burst Write command. Terminate the burst with a burst stop command, precharge command to the same bank or another burst read/ write. DQM can also be used to mask the input data.                                                                                                                                                                    |

# 414 ALLIANCE SEMICONDUCTOR DID 11-60002-A-1/12/99

| RORRORRORRORRORRORRORRORRORRORRORRORROR    |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command                                    | Pin settings                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

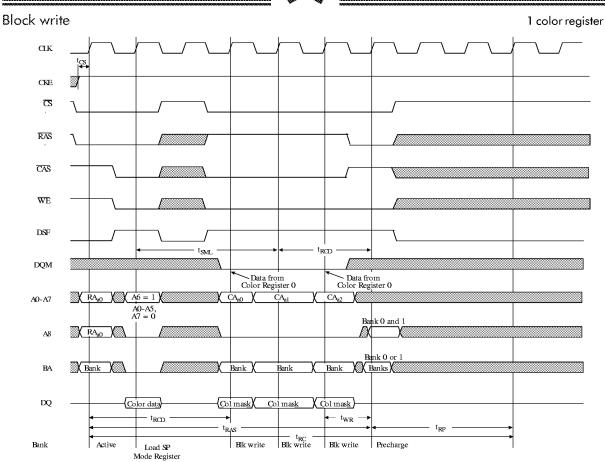

| Block write                                |                                                                                                                                                                                                                        | Use block write to write a single data value to a block of eight consecutive column locations addressed by A7-A3. A Special Mode Register Set command must occur before a block write to assign this data to the color register. Input data on DQs is used to mask specified column/ byte combinations within the block.                                                                                                                                                                     |

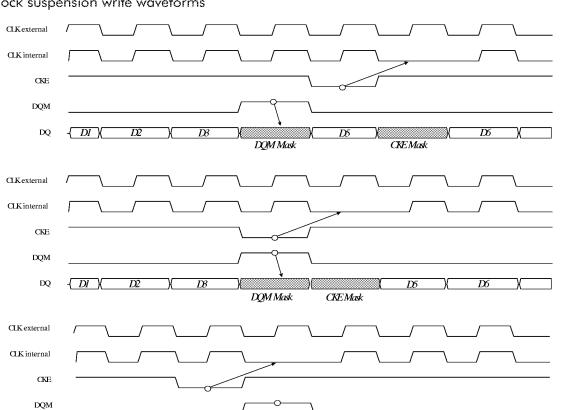

| DQM operation                              |                                                                                                                                                                                                                        | Use DQM to mask input and output data. It disables the output buffers in a read operation and masks input data in a write operation. The output data is tri-stated 2 clocks after DQM assertion (2 clock latency). Input data is masked on the same clock as DQM assertion (0 clock latency).                                                                                                                                                                                                |

| Burst stop                                 | $\overline{CS} = \overline{WE} = low; \overline{RAS} = \overline{CAS} = high$                                                                                                                                          | Use burst stop to terminate burst operation. This command may be used to terminate all legal burst lengths.                                                                                                                                                                                                                                                                                                                                                                                  |

| Bank precharge                             | $\overline{\text{CS}} = \text{A8} = \overline{\text{RAS}} = \overline{\text{WE}} = \text{low}; \overline{\text{CAS}} = \text{high}; \text{BA} = \text{bank select}; A0~A7 = \text{don't care}$                         | The Bank Precharge command precharges the bank specified by BA. The precharged bank is switched from active to idle state and is ready to be activated again. Assert the precharge command after $t_{RAS}(min)$ of the bank activate command in the specified bank. The precharge operation requires a time of $t_{RP}(min)$ to complete.                                                                                                                                                    |

| Precharge all                              | $\overline{\text{CS}} = \overline{\text{RAS}} = \overline{\text{WE}} = \text{low};$<br>$\overline{\text{CAS}} = \text{A8} = \text{high}; \text{BA} = \text{bank select}; \text{A0} \sim \text{A7} = \text{don't care}$ | The Precharge All command may be used to precharge both banks simultaneously. If A8 is high, BA is a don't care and both banks are simultaneously precharged. If A8 is low, BA specifies which bank is to be precharged. Both banks are switched to the idle state on precharge completion.                                                                                                                                                                                                  |

| Auto precharge                             | $\overline{\text{CS}} = \overline{\text{CAS}} = \overline{\text{WE}}(\text{write}) = $ low; $\overline{\text{RAS}} = \overline{\text{WE}}(\text{read}) = $ A8 = high; BA = bank select; A0~A7 = column address         | During auto precharge, the SGRAM adjusts internal timing to satisfy $t_{RAS}(\min)$ and $t_{RP}$ for the programmed CAS latency and burst length. Couple the auto precharge with a burst read/ write operation by asserting A8 to a high state at the same time the burst read/ write commands are issued. At auto precharge completion, the specified bank is switched from active to idle state. Note that no new commands can be issued until the specified bank achieves the idle state. |

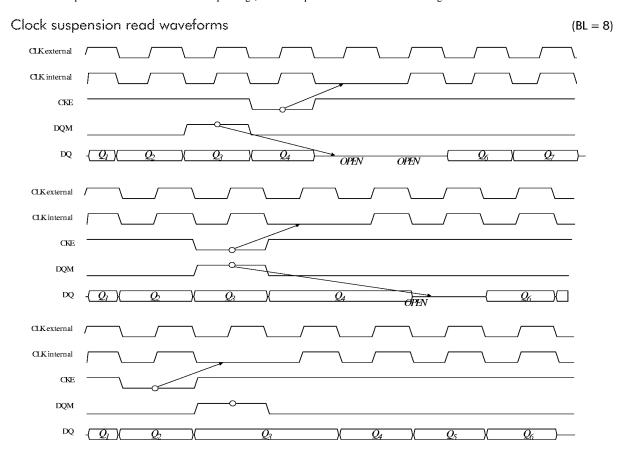

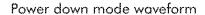

| Clock suspend/<br>power down<br>mode entry | CKE = low                                                                                                                                                                                                              | When CKE is low, the internal clock is frozen or suspended from the next clock cycle and the state of the output and burst address are frozen. If both banks are idle and CKE goes low, the SGRAM enters power down mode at the next clock cycle. When in power down mode, no input commands are acknowledged as long as CKE remains low. To exit power down mode, raise CKE high before the rising edge of CLK.                                                                             |

| Clock suspend/<br>power down<br>mode exit  | CKE= high                                                                                                                                                                                                              | Resume internal clock operation by asserting CKEhigh before the rising edge of CLK. Subsequent commands can be issued one clock cycle after the end of the Exit command.                                                                                                                                                                                                                                                                                                                     |

DID 11-60002-A 1/12/99 ALLIANCE SEMICONDUCTOR 41.5

| Command      | Pin settings                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

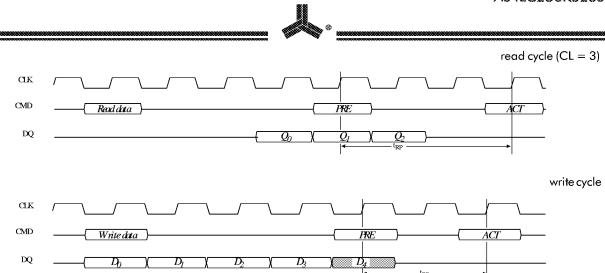

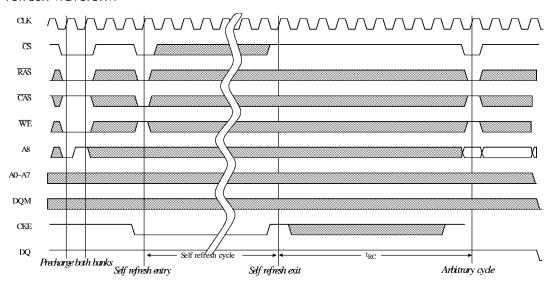

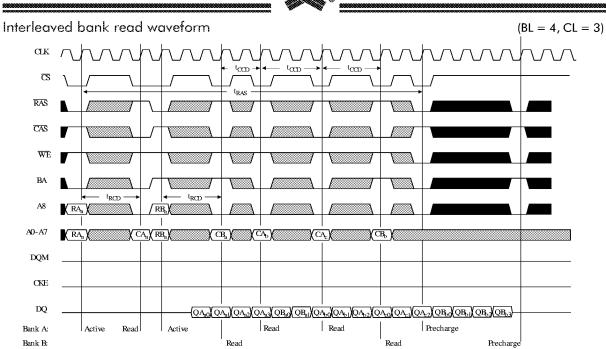

| Auto refresh | $\overline{CS} = \overline{RAS} = \overline{CAS} = low;$ $\overline{WE} = CKE = high;$ $A0 \sim BA = don't care$ | SGRAM storage cells must be refreshed every 64ms to maintain data integrity. Use the Auto Refresh command to accomplish the refreshing of all rows in both banks of the SGRAM. The row address is provided by an internal counter which increments automatically. Auto refresh can only be asserted when both banks are idle and the device is not in the power down mode. The time required to complete the auto refresh operation is $t_{RC}(\min)$ . Use NOPs in the interim until the auto refresh operation is complete. This is the most common refresh mode. It is typically performed once every 15.6us or in a burst of 1024 auto refresh cycles every 64ms. Both banks will be in the idle state after this operation. |

| Self refresh | $\overline{CS} = \overline{RAS} = \overline{CAS} = CKE = low; \overline{WE} = high; A0~BA = don't care$          | Self refresh is another mode for refreshing SGRAM cells. In this mode, refresh address and timing are provided internally. Self refresh entry is allowed only when both banks are idle. The external clock and all input buffers with the exception of CKE are disabled in this mode. Exit self refresh by restarting the external clock and then asserting CKE high. NOP's must follow for a time of $t_{RC}(\min)$ for the SGRAM to reach the idle state where normal operation is allowed. If burst auto refresh is used in normal operation, burst 1024 auto refresh cycles immediately after exiting self refresh.                                                                                                          |

416 ALLIANCE SEMICONDUCTOR DID 11-60002-A 1/12/99

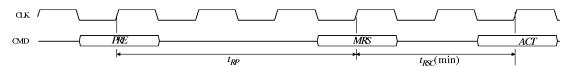

## Mode register set command waveform

MRS can be issued only when both banks are idle.

## Precharge waveforms

Precharge can be asserted after  $t_{RAS}$  (min). The selected bank will enter the idle state after  $t_{RP}$ . The earliest assertion of the precharge command without losing any burst data is show below.

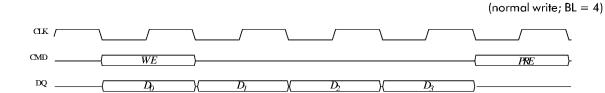

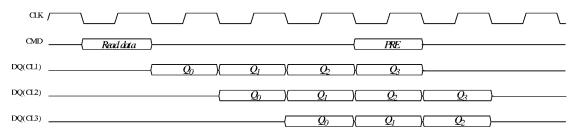

(normal read; BL = 4)

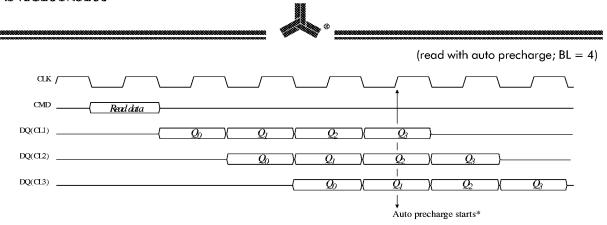

#### Auto precharge waveforms

A8 controls the selection of auto precharge during the read or write command cycle.

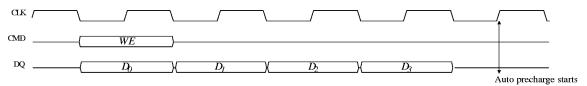

(write with auto precharge; BL = 4)

DID 11-60002-A. 1/12/99

ALLIANCE SEMICONDUCTOR

\*The row active command of the precharge bank can be issued after t<sub>RP</sub> from this point. The new read/ write command of another activated bank can be issued from this point. At burst read/write with auto precharge, CAS interrupt of the same/ another bank is illegal.

418

ALLIANCE SEMICONDUCTOR DID 11-80002-A 1/12/99

# Clock suspension write waveforms

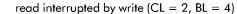

## Read/write interrupt timing

-DI

DQ

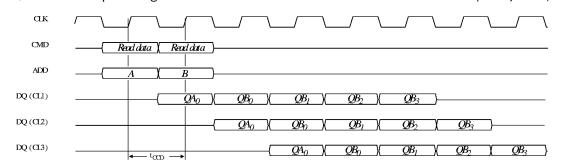

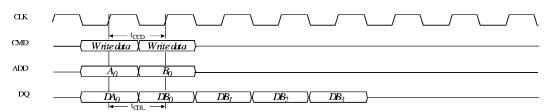

## read interrupted by read (BL = 4)

D4

$t_{CCD} = \overline{CAS}$  to  $\overline{CAS}$  delay (= 1 CLK)

DID 11-60002-A 1/12/99

ALLIANCE SEMICONDUCTOR

$t_{CCD} = \overline{\text{CAS}}$  to  $\overline{\text{CAS}}$  delay (= 1 CLK)

$t_{CDL}$  = last address in to new column addres delay (= 1 CLK)

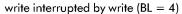

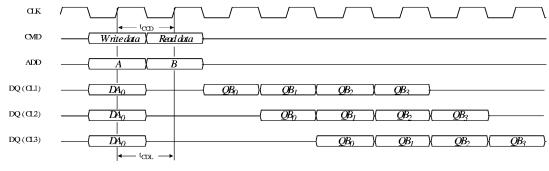

#### write interrupted by read (BL = 4)

$t_{CCD} = \overline{CAS}$  to  $\overline{CAS}$  delay (= 1 CLK)

$t_{\text{CDL}}$  = last address in to new column addres delay (= 1 CLK)

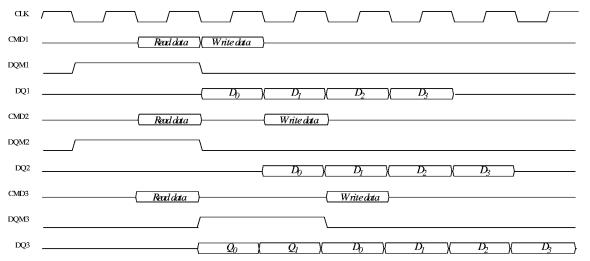

#### read interrupted by write (CL = 1, BL = 4)

To prevent bus contention, maintain a gap between data in and data out.

420

ALLIANCE SEMICONDUCTOR DID 11-80002-A 1/12/99

To prevent bus contention, maintain a gap between data in and data out.

#### read interrupted by write (CL = 3, BL = 4)

To prevent bus contention, maintain a gap between data in and data out.

DID 11-60002-A 1/12/99

ALLIANCE SEMICONDUCTOR

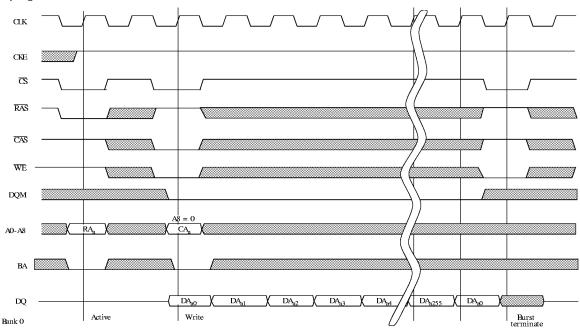

## **Burst termination**

Burst operations may be terminated with a Read, Write, Burst Stop, or Precharge command. When Burst Stop is asserted during the read cycle, burst read data is terminated and the data bus goes to Hi-Z after CAS latency. When Burst Stop is asserted during the write cycle, burst write data is terminated and the databus goes to HI-Z simultaneously.

#### Burst stop command waveform

read cycle

write cycle (BL = 8)

## Precharge termination

A Precharge command terminates a burst read/write operation during the read cycle. The same bank can be activated after meeting t<sub>RP</sub>

## Auto refresh waveform

DID 11-60002-A 1/12/99

ALLIANCE SEMICONDUCTOR

(CL = 3)

Enter power down mode by pulling CKE low.

All input/ output buffers (except CKE buffer) are turned off in power down mode.

When CKE goes high, command input must be equal to no operation at next CLK rising edge.

424

ALLIANCE SEMICONDUCTOR DID 11-80002-A-1/12/99

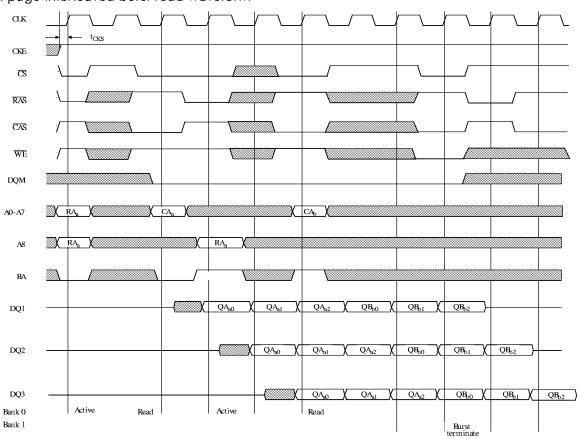

(BL = 4, CL = 3)

DID 11-60002-A. 1/12/99

ALLIANCE SEMICONDUCTOR

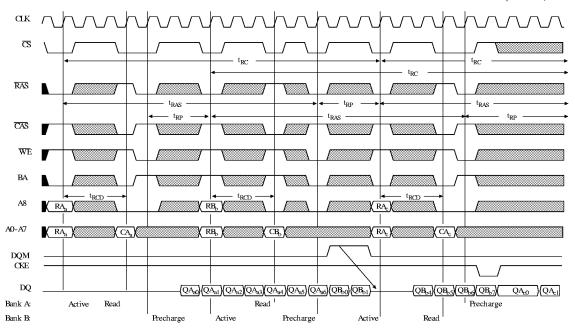

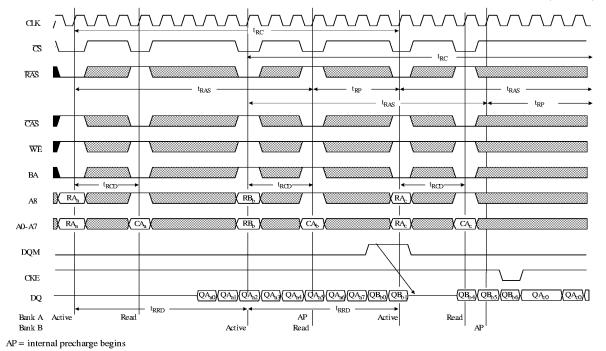

Interleaved bank read waveform

(BL = 4, CL = 3, Autoprecharge)

AP = internal precharge begins

426

ALLIANCE SEMICONDUCTOR

DID 11-60002-A. 1/12/99

Interleaved bank read waveform

(BL = 8, CL = 3)

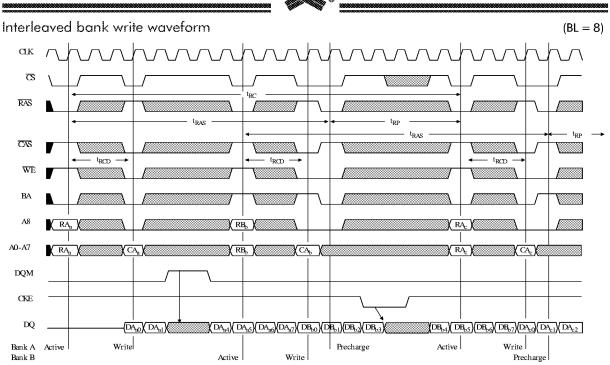

Interleaved bank read waveform

(BL = 8, CL = 3, Autoprecharge)

ALLIANCE SEMICONDUCTOR

AP = internal precharge begins

DID 11-60002-A 1/12/99

ALLIANCE SEMICONDUCTOR

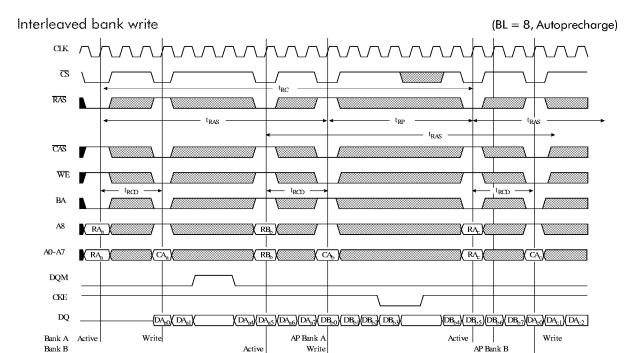

430

ALLIANCE SEMICONDUCTOR DID 11-60002-A. 1/12/99

DID 11-60002-A 1/12/99

ALLIANCE SEMICONDUCTOR

432

ALLIANCE SEMICONDUCTOR DID 11-60002 & 1/12/99

## Block write diagram

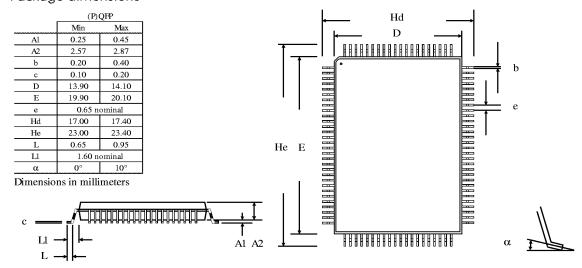

## Package dimensions

DID 11-60002-A. 1/12/99

ALLIANCE SEMICONDUCTOR

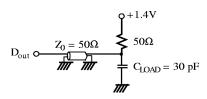

#### AC test conditions

- Input reference levels of  $V_{IH}=2.4V$  and  $V_{IL}\!=0.8V$  - Output reference levels = 1.4V

Symbol

$C_{IN1}$

$C_{IN2}$

$C_{I/O}$

- Input rise and fall times: 1 ns

Figure A: Equivalent output load

DQ0 to DQ31

| Capacitance |

|-------------|

| Parameter   |

Input capacitance

I/O capacitance

|                                                                                        | $f = 1 \text{ MHz}, T_{\alpha} = 25^{\circ}\text{C}, \text{V}$ | $V_{CC} = 3.3V$ |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------|

| Signals                                                                                | Max                                                            | Unit            |

| A0 to BA                                                                               | 5                                                              | pF              |

| DQM, $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ , $\overline{CS}$ , $CLK$ , | CKE, DSF 5                                                     | pF              |

pF

5

# Part numbering system

| AS4            | IC             | XXXS0                                    | -XX          | XX | C                                          |

|----------------|----------------|------------------------------------------|--------------|----|--------------------------------------------|

| DRAM<br>prefix | LC = 3.3V CMOS | Device number<br>for synchronous<br>DRAM | 1/ frequency |    | Commercial temperature range, 0°C to 70 °C |

## Ordering codes

| Package/ Frequency                 | 150 MHz             | 133 MHz             | 100 MHz             |

|------------------------------------|---------------------|---------------------|---------------------|

| Plastic PQFP, 100-pin, 14mm × 20mm | AS4LC256K32S0-150PQ | AS4LC256K32S0-133PQ | AS4LC256K32S0-100PQ |