PLV5000/L

### **DESCRIPTION**

The PLV5000/L is an easy to use, high density programmable logic device. Its simple, regular architecture translates into increased utilization and high performance.

The PLV5000/L has one programmable combinatorial logic array. This guarantees easy interconnection of and uniform performance from all nodes. "Sum terms", which are easy to use groupings of AND-OR gates, provide combinatorial logic blocks. Sum terms can be wire-OR'd together to integrate larger logic blocks. To expand the levels of logic, buried sum terms feed back into the logic array. The 52 I/O pins can each be driven by a register or a sum term. Each I/O pin has an individually enabled input latch.

All 128 registers are configurable as D or T types without using extra logic gates. Individual sum terms, asynchronous presets, resets and clocks give each flip-flop added flexibility. A direct "clock from pin" option guarantees synchronization and fast clock to output performance.

Standard off-the-shelf third party software tools and programmers support the PLV5000/L. This minimizes start-up investment and improves product support.

## **APPLICATIONS**

- High speed microprocesser interface

- Peripheral control

- Bus interface

- Instrumentation control

- Industial process control

- Telecom interface

#### **FEATURES**

- Advanced programmable logic device high gate utilization

- Flexible interconnect architecture universal routing

- Flexible logic cells—128 flip-flops and 52 latches

- Multiple flip-flop types—synchronous or asynchronous registers

- High speed—50MHz operation

- Complete third party software support

- No placement, routing or layout software required

- Proven and reliable high speed CMOS EPROM process

- 2000V ESD protection

- 200mA latchup immunity

- Reprogrammable—tested 100% for programmability

### **PIN DESCRIPTIONS**

| PIN NAME              | FUNCTION                  |

|-----------------------|---------------------------|

| IN                    | Logic and clock inputs    |

| Pins 2, 32,<br>36, 66 | Input/Register Clocks 1–4 |

| Pins 1, 34,<br>35, 68 | Input/Latch Clocks 1-4    |

| 1/0                   | Bi-directional buffers    |

| V <sub>CC</sub>       | +5V Supply                |

| GND                   | Ground                    |

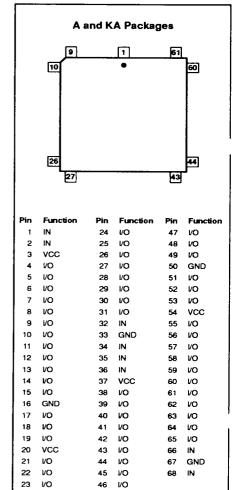

## **PIN CONFIGURATION**

### ORDERING INFORMATION

| DESCRIPTION                                                               | ORDER CODE                 |

|---------------------------------------------------------------------------|----------------------------|

| 68-Pin Cerquad J-Bend Package with Quartz Window (t <sub>PD</sub> = 25ns) | PLV5000-25KA               |

| 68-Pin Plastic Leaded Chip Carrier (t <sub>PD</sub> = 25ns)               | PLV5000-25A                |

| 68-Pin Cerquad J-Bend Package with Quartz Window (tpD = 30ns)             | PLV5000-30KA, PLV5000L30KA |

| 68-Pin Plastic Leaded Chip Carrier (t <sub>PD</sub> = 30ns)               | PLV5000-30A, PLV5000L-30A  |

| 68-Pin Cerquad J-Bend Package with Quartz Window (t <sub>PD</sub> = 35ns) | PLV5000L35KA               |

| 68-Pin Plastic Leaded Chip Carrier (t <sub>PD</sub> = 35ns)               | PLV5000L-35A               |

August 1991

PLV5000/L

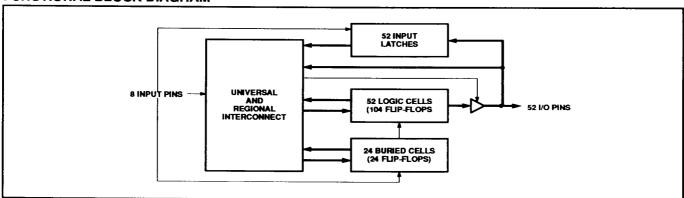

## **FUNCTIONAL BLOCK DIAGRAM**

## **PLV5000 BLOCK DIAGRAM**

## FUNCTIONAL LOGIC DIAGRAM DESCRIPTION

There are 52 identical Input/Output logic cells and 24 identical buried logic cells in the PLV5000. Each I/O cell has 2 flip-flops, up to 3 sum terms, individual clock, reset, and preset terms per flip-flop, and one output enable term. Independent of output configuration, all flip-flops are always usable, and have at least 4 product terms inputs each.

Each I/O pin (52 total) signal or its latched version drives the logic array. There is one latch clock per quadrant.

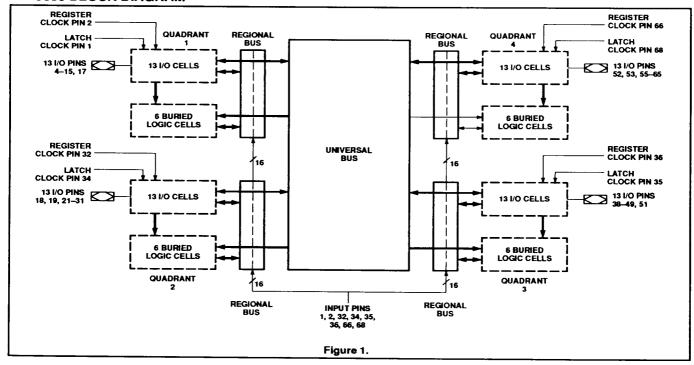

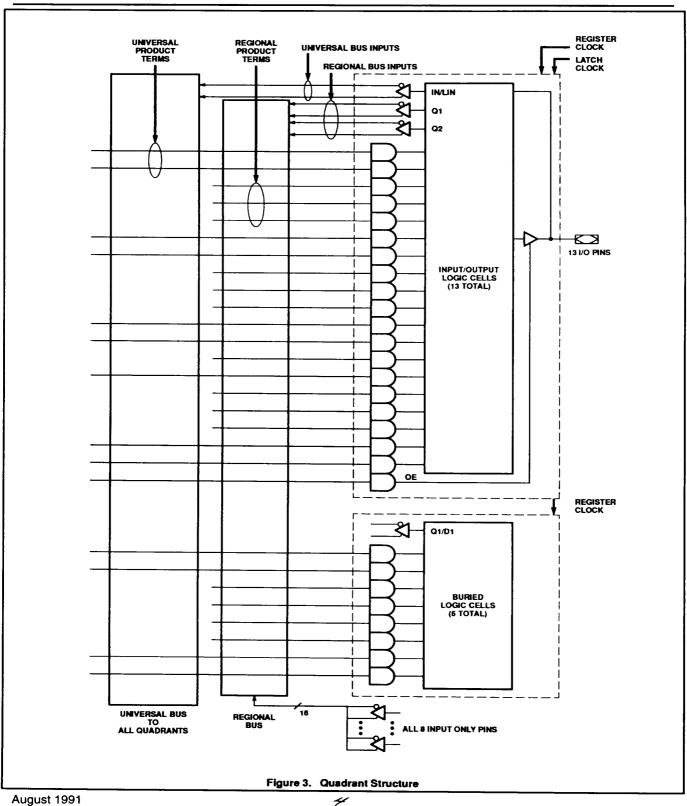

The PLV5000 has 4 identical quadrants (see Figure 1). The Universal Bus routs true and false signals from each of the 52 I/O pins to all four quadrants, regional buses route each quadrant's flip-flop Q and  $\overline{\bf Q}$  locally. The 8 input-only pins are available in all 4 regional buses.

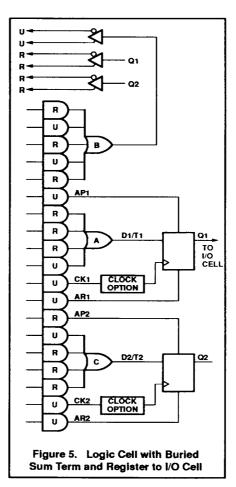

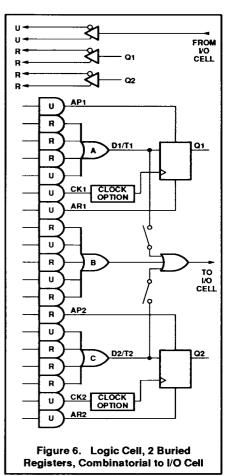

Each logic cell has a number of "regional" and "universal" product terms (see Figure 2). The I/O logic cells contain 3 sum terms, 2 flip-flops, and an I/O buffer.

The buried logic cells each contain 1 flip-flop. In addition, in each buried logic cell the sum term can drive the regional bus. This allows for logic expansion.

Serial register preload and observability simplify testing. All registers automatically clear at power up.

August 1991

2

PLV5000/L

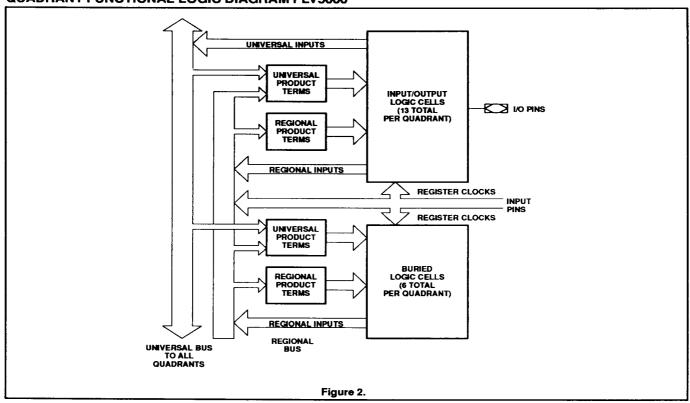

### **QUADRANT FUNCTIONAL LOGIC DIAGRAM PLV5000**

## QUADRANT LOGIC DIAGRAM AND DESCRIPTION

The PLV5000 has: 4 identical quadrants, 52 identical input/output logic cells, and 24 identical buried logic cells. The universal bus routes true and false signals from each of the 52 I/O pins to all four quadrants. Regional buses route each quadrant's flip-flop Q and  $\overline{Q}$  locally. The 8 input-only pins are available in every regional bus.

Each logic cell has a number of "regional" and "universal" product terms (see Figure 3).

Regional product terms have as inputs all quadrant flip-flop outputs (or buried flip-flop inputs) and the 8 dedicated input pins. Universal product terms have the same inputs plus the 52 I/O pins and their complements.

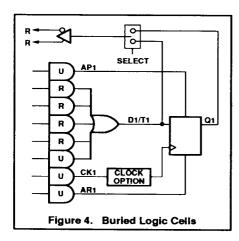

The buried logic cells (Figure 4) each contain 1 flip-flop. The sum term has 1 universal product term and 4 regional product terms for a total of 5. The flip-flop has universal Asynchronous Preset, Reset, and Clock terms. In addition, in each buried logic cell the sum term can be fed back into the regional bus instead of the flip-flop. This allows for logic expansion.

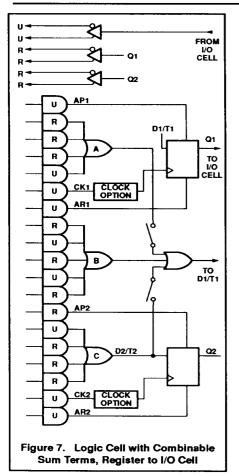

The I/O logic cells (Figure 5, Figure 6, and Figure 7) contain 3 sum terms, 2 flip-flops, and an I/O buffer. Sum term B has 5 product terms – 2 universal and 3 regional. Flip-flop Q1 has global Asynchronous Preset, Reset, and Clock product terms. Flip-flop Q2 has universal Asynchronous Reset and Clock

terms and a regional Asynchronous Preset term. There is 1 universal product term for the I/O pin Output Enable.

## QUADRANT CLOCK PIN ASSIGNMENTS

| QUADRANT<br>NUMBER | REGISTER<br>CLOCK<br>PIN | LATCH<br>CLOCK<br>PIN |

|--------------------|--------------------------|-----------------------|

| 1                  | 2                        | 1                     |

| 2                  | 32                       | 34                    |

| 3                  | 36                       | 35                    |

| 4                  | 66                       | 68                    |

August 1991

3

PLV5000/L

PLV5000/L

### **LOGIC CELL OPTIONS**

The PLV5000 logic cells contain most of the chip's logic options. The standard logic cell contains 2 flip-flops, 3 sum terms and 3 array inputs. the 3 sum terms can be combined to provide sum term options of 4, 5, 9, or 13 product terms. A combinatorial signal or the output of Q1 can be sent to the I/O cell.

The PLV5000 retains the PLV2500's ability to bury both registers in the I/O cell and still output a combinatorial signal (see Figure 6). A new feature, unique to the PLV5000, is the ability to output Q1 and feedback the combinatorial term directly (see Figure 5). this high speed logic expansion term increases the device's flexibility and gate utilization.

#### **BURIED LOGIC CELLS**

Each quadrant has six buried logic cells (see Figure 4). Each cell contains one sum term with 5 product terms, a flip-flop, and individual preset, clear and clock terms. A configuration bit selects either the Q output or the D input for feedback into the regional bus.

## PLV5000/L

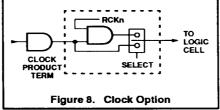

#### **FLIP-FLOP CLOCK OPTIONS**

Each register may be connected to its regional clock to provide fast clock to output timing (see Figure 8). In this "synchronous" mode, the clock is one of four input pins, a unique clock pin for each chip quadrant. One product term defines each flip-flop's clock in the "asynchronous" mode.

In the "synchronous" mode, the regional clock is ANDed with the product term. This provides the fast timing of a synchronous clock with the local control of the product term.

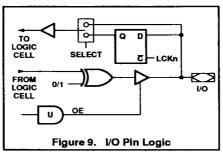

#### I/O PIN LATCHES

Each I/O pin of the PLV5000 has an input latch which can be individually enabled or disabled (see Figure 9). Each chip quadrant has a unique latch clock. When the latch is inactive, pin input flows directly into the array. When activated, the latch is flow-through when the clock signal is LOW, and data is captured on the clock's rising edge.

### **FLIP-FLOP TYPES**

Each flip-flop in the PLV5000 may be configured as either a T or D type flip-flop. A T type flip-flop can also easily be configured into a JK or SR flip-flop.

### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| SYMBOL            | PARAMETER                                                                    | RATINGS       | UNIT                 |

|-------------------|------------------------------------------------------------------------------|---------------|----------------------|

| V <sub>IN</sub>   | Voltage on any pin with respect to ground <sup>2</sup>                       | -2.0 to +7.0  | V <sub>DC</sub>      |

| V <sub>IP</sub>   | Voltage on input pins with respect to ground during programming <sup>2</sup> | -2.0 to +14.0 | V <sub>DC</sub>      |

| V <sub>PP</sub>   | Programming voltage with respect to ground <sup>2</sup>                      | -2.0 to +14.0 | v                    |

| _                 | Integrated UV erase dose                                                     | 7258          | Wsec/cm <sup>2</sup> |

| T <sub>bias</sub> | Temperature under bias                                                       | -55 to +125   | °C                   |

| T <sub>stg</sub>  | Storage temperature                                                          | -65 to +150   | °C                   |

#### NOTES:

- Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- periods may affect device reliability.

2. Minimum voltage is -0.6V<sub>DC</sub> which may undershoot to -2.0V for pulses of less than 20ns. Maximum output pin voltage is V<sub>CC</sub> + 0.75V<sub>DC</sub> which may overshoot to +7.0V for pulses of less than 20ns.

August 1991

PLV5000/L

## DC ELECTRICAL CHARACTERISTICS

$0^{\circ}\text{C} \le \text{T}_{amb} \le 70^{\circ}\text{C}, 4.5\text{V} \le \text{V}_{CC} \le 5.5\text{V}$

|                  |                                                 |                                                                                   |                     | LIMITS |                       |      |  |

|------------------|-------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|--------|-----------------------|------|--|

| SYMBOL           | PARAMETER                                       | TEST CONDITIONS                                                                   | MIN                 | TYP    | MAX                   | UNIT |  |

| l <sub>L1</sub>  | Input load current                              | $V_{IN} = -0.1V$ to $V_{CC} + 1V$                                                 |                     |        | 10                    | μА   |  |

| I <sub>LO</sub>  | Output leakage current                          | $V_{OUT} = -0.1V$ to $V_{CC} + 0.1V$                                              |                     |        | 10                    | μА   |  |

| lcc              | Power supply current, PLV5000                   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = GND or V <sub>CC</sub> ,<br>Outputs Open |                     | 200    | 350                   | mA   |  |

| _                | Power supply current, PLV5000L                  | V <sub>CC</sub> = MAX, V <sub>IN</sub> = GND or V <sub>CC</sub> ,<br>Outputs Open |                     | 20     | 40                    | mA   |  |

| I <sub>CC2</sub> | Clocked power supply current<br>(PLV5000L only) | f = 1MHz, V <sub>CC</sub> = MAX,<br>Outputs Open                                  |                     | 30     | 50                    | mA   |  |

| los              | Output short circuit current <sup>1</sup>       | V <sub>OUT</sub> = 0.5V                                                           |                     |        | -90                   | mA   |  |

| V <sub>IL</sub>  | Input Low voltage                               |                                                                                   | -0.6                |        | 0.8                   | V    |  |

| V <sub>IH</sub>  | Input High voltage                              |                                                                                   | 2.0                 |        | V <sub>CC</sub> +0.75 | V    |  |

| V <sub>OL</sub>  | Output Low voltage                              | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> , I <sub>OL</sub> = 8mA      |                     |        | 0.5                   | V    |  |

| V <sub>OH</sub>  | Output High voltage                             | I <sub>OH</sub> = -100μA                                                          | V <sub>CC</sub> 0.3 |        |                       | V    |  |

|                  |                                                 | I <sub>OH</sub> = -4.0mA                                                          | 2.4                 |        |                       | V    |  |

| C <sub>IN</sub>  | Input capacitance <sup>2</sup>                  | V <sub>IN</sub> = 0V<br>f = 1MHz, T <sub>amb</sub> = 25°C                         |                     | 6      | 8                     | pF   |  |

| C <sub>OUT</sub> | Output capacitance <sup>2</sup>                 | V <sub>OUT</sub> = 0V<br>f = 1MHz, T <sub>amb</sub> = 25°C                        |                     | 8      | 12                    | pF   |  |

## NOTES:

Not more than one output at a time should be shorted. Duration of short circuit test should not exceed 30 seconds.

Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

PLV5000/L

## REGISTER AC ELECTRICAL CHARACTERISTICS, INPUT PIN CLOCK

|                   |                                         | LIMITS |              |     |             |     |      |     |

|-------------------|-----------------------------------------|--------|--------------|-----|-------------|-----|------|-----|

| SYMBOL            | PARAMETER                               | PLV5   | PLV5000/L-30 |     | PLV5000L-35 |     | UNIT |     |

|                   |                                         | MIN    | MAX          | MIN | MAX         | MIN | MAX  |     |

| t <sub>cos</sub>  | Clock to output                         |        | 15           |     | 20          |     | 25   | ns  |

| t <sub>CFS</sub>  | Clock to feedback                       | 0      | 5            | 0   | 7           | 0   | 8    | ns  |

| tsis              | Input setup time <sup>1</sup>           | 16     |              | 17  |             | 20  |      | ns  |

| t <sub>SFS</sub>  | Feedback setup time <sup>1</sup>        | 15     |              | 18  |             | 22  |      | ns  |

| t <sub>HS</sub>   | Hold time                               | 0      |              | 0   |             | 0   |      | ns  |

| tws               | Clock width                             | 10     |              | 12  |             | 15  |      | ns  |

| tes               | Clock period                            | 20     |              | 25  |             | 30  |      | ns  |

| f <sub>MAXS</sub> | Maximum frequency (1/t <sub>PS</sub> )  |        | 50           |     | 40          |     | 33   | MHz |

| tars              | Asynchronous Reset/Preset recovery time | 20     |              | 25  |             | 30  |      | ns  |

NOTES:

## REGISTER AC ELECTRICAL CHARACTERISTICS, PRODUCT TERM CLOCK

|                   |                                         |      |              | LIA | AITS        |     |      |     |

|-------------------|-----------------------------------------|------|--------------|-----|-------------|-----|------|-----|

| SYMBOL            | PARAMETER                               | PLV5 | PLV5000/L-30 |     | PLV5000L-35 |     | UNIT |     |

|                   |                                         | MIN  | MAX          | MIN | MAX         | MIN | MAX  | 1   |

| t <sub>COA</sub>  | Clock to output                         |      | 25           |     | 30          |     | 35   | ns  |

| t <sub>CFA</sub>  | Clock to feedback                       | 7    | 20           | 10  | 25          | 12  | 27   | ns  |

| tsia              | Input setup time <sup>1</sup>           | 10   |              | 12  |             | 15  |      | ns  |

| <sup>t</sup> sfa  | Feedback setup time <sup>1</sup>        | 5    |              | 8   |             | 13  |      | ns  |

| t <sub>HA</sub>   | Hold time                               | 8    |              | 10  |             | 12  |      | ns  |

| t <sub>WA</sub>   | Clock width                             | 12   |              | 15  |             | 15  |      | ns  |

| t <sub>PA</sub>   | Clock period                            | 25   |              | 33  |             | 40  |      | ns  |

| f <sub>MAXA</sub> | Maximum frequency (1/t <sub>PA</sub> )  |      | 40           |     | 30          |     | 25   | MHz |

| t <sub>ARA</sub>  | Asynchronous Reset/Preset recovery time | 15   |              | 20  |             | 25  |      | ns  |

NOTES

<sup>1.</sup> Add 3ns for Universal product terms.

<sup>1.</sup> Add 3ns for Universal product terms.

PLV5000/L

## **AC ELECTRICAL CHARACTERISTICS**

$0^{\circ}C \le T_{amb} \le 70^{\circ}C, 4.5V \le V_{CC} \le 5.5V$

|                  |                                                  |      |        | LIN          | IITS |             |     |      |

|------------------|--------------------------------------------------|------|--------|--------------|------|-------------|-----|------|

| SYMBOL           | PARAMETER                                        | PLV5 | 000-25 | PLV5000/L-30 |      | PLV5000L-35 |     | UNIT |

|                  |                                                  | MIN  | MAX    | MIN          | MAX  | MIN         | MAX |      |

| t <sub>PD1</sub> | Input to non-registered output <sup>1</sup>      |      | 25     |              | 30   |             | 35  | ns   |

| t <sub>PD2</sub> | Feedback to non-registered output <sup>1</sup>   |      | 20     |              | 25   |             | 30  | ns   |

| t <sub>PD3</sub> | Input to non-registered feedback <sup>1</sup>    |      | 20     | 1            | 25   |             | 30  | ns   |

| t <sub>PD4</sub> | Feedback to non-registered feedback <sup>1</sup> |      | 15     |              | 18   | _           | 22  | ns   |

| t <sub>EA1</sub> | Input to Output Enable                           |      | 30     |              | 35   |             | 40  | ns   |

| t <sub>ER1</sub> | Input to Output Disable                          |      | 30     |              | 35   |             | 40  | ns   |

| t <sub>EA2</sub> | Feedback to Output Enable                        |      | 25     |              | 30   |             | 35  | ns   |

| t <sub>ER2</sub> | Feedback to Output Disable                       |      | 25     |              | 30   |             | 35  | ns   |

| t <sub>S</sub>   | Input latch setup time                           | 5    |        | 6            |      | 7           |     | ns   |

| t <sub>H</sub>   | Input latch hold time                            | 5    |        | 5            |      | 5           |     | ns   |

| tw               | Clock width                                      | 10   |        | 12           |      | 12          |     | ns   |

| tр               | Clock period                                     | 20   |        | 25           |      | 30          |     | ns   |

| f <sub>MAX</sub> | Maximum frequency (1/t <sub>P</sub> )            |      | 50     |              | 40   |             | 33  | MHz  |

| t <sub>AW</sub>  | Asynchronous Reset/Preset width                  | 15   |        | 20           |      | 20          |     | ns   |

| t <sub>AP</sub>  | Asynchronous Reset/Preset to Registered Output   |      | 30     |              | 35   |             | 40  | ns   |

| t <sub>APF</sub> | Asynchronous Reset/Preset to Registered Feedback |      | 25     |              | 30   |             | 35  | ns   |

## NOTES:

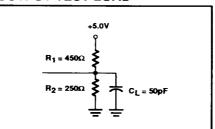

## INPUT TEST WAVEFORMS AND MEASUREMENT LEVELS

### **OUTPUT TEST LOAD**

Add 3ns for Universal product terms.

PLV5000/L

### **TIMING DIAGRAMS**

PLV5000/L

## PRELOAD AND OBSERVABILITY OF REGISTERS

The PLV5000's registers include circuitry to load and unload them serially. This feature simplifies testing. Any state can be forced into the registers to control test sequencing, and all registers may be observed, independent of being buried. A V<sub>IH</sub> level on the Data In pin will force the appropriate register HIGH; a V<sub>IL</sub> will force it LOW, independent of the polarity or other configuration bit settings.

The Preload/Observe state is entered by placing an 11V to 14V signal on Pin 68. when the clock (Pin 1) is pulsed high, data (Pin 2) is clocked serially through all registers in the device, as in the following table. All register contents are also clocked out of the device on Pin 65 in FIFO fashion. If observability only is required, data out should be connected back to data in. If preload only is required, OE (Pin 66) can be held HIGH and data out (Pin 65) will remain high impedance.

Any user contemplating the use of register preload/observability is encouraged to contact Signetics PLD applications group.

NOTE: All register clock terms or pins must be LOW prior to entering the Preload/Observe state, and LOW prior to leaving the Preload/Observe state. Pin 1 must be LOW prior to entering the Preload/Observe state.

## PRELOAD / OBSERVE REGISTER SCAN ORDER

| QUADRANT      | PIN               |           |                |           |            |           |                                                                  |

|---------------|-------------------|-----------|----------------|-----------|------------|-----------|------------------------------------------------------------------|

| Quadrant 1    | Pin               | 4         | 5              | 6         |            | 15        | 17                                                               |

|               | D <sub>IN</sub> → | Q2 → Q1 → | B23 → Q2 → Q1  | → Q2 → Q1 | B18 →      | Q2 → Q1 - | Q2 → Q1 → (Quadrant 2)                                           |

| Quadrant 2    | Pin               | 18        | 19             | 21        | 22         |           | 31                                                               |

| (Quadrant 1)→ |                   | Q2 → Q1 → | Q2 → Q1 → B17  | → Q2 → Q  | I → Q2 → ( | Q1 B12 -  | → Q2 → Q1 → (Quadrant 3)                                         |

| Quadrant 3    | Pin               | 38        | 39             | 40        |            | 49        | 51                                                               |

| (Quadrant 2)→ |                   | Q2 → Q1 → | B11 → Q2 → Q1  | → Q2 → Q1 | B6 →       | Q2 → Q1 - | → Q2 → Q1 → (Quadrant 4)                                         |

| Quadrant 4    | Pin               | 52        | 53             | 55        | 56         |           | 65                                                               |

| (Quadrant 3)→ | 1 .               | Q2 → Q1 → | Q2 → Q1 → B5 - | → Q2 → Q1 | → Q2 → Q   | 1 B0 -    | $\rightarrow$ Q2 $\rightarrow$ Q1 $\rightarrow$ D <sub>OUT</sub> |

PLV5000/L

## **POWER-UP RESET**

The registers in the PLV5000 are designed to reset during power up. At a point delayed slightly from  $V_{CC}$  crossing 3.8V, all registers will be reset to the LOW state. The output state will depend on the polarity of the output buffer.

This feature is critical for state machine initialization. However, due to the asynchronous nature of reset and the uncertainty of how  $V_{CC}$  actually rises in the system, the following conditions are required:

- 1. The V<sub>CC</sub> rise must be monotonic,

- After reset occurs, all input and feedback setup times must be met before driving the clock term HIGH, and

- The signals from which the clock is derived must remain stable during tpR.

| PARAMETER       | DESCRIPTION         | MIN | TYP | MAX  | UNIT |

|-----------------|---------------------|-----|-----|------|------|

| t <sub>PR</sub> | Power-Up Reset time |     | 600 | 1000 | ns   |

PLV5000/L

### **USING THE PLV5000**

The PLV5000's simple, regular architecture means that only simple logic compilers are required to configure the device. No layout or route and place are required. These software tools are readily available from companies such as Data I/O Corporation (ABEL<sup>TM</sup>), Logical Devices (CUPL<sup>TM</sup>), and ISDATA (LOGiC<sup>TM</sup>).

The first step in designing a device as complex as the PLV5000 is to partition your design into manageable blocks. These blocks are then allocated proportionally to each of the four quadrants of the PLV5000. Random gates can be described either with Boolean equations (a behavioral description) or with a schematic editor. Truth table logic and state machines are best described behaviorally and entered with a text editor. The design is then combined into one ASCII file, which is then submitted to the logic compiler. Compilation, logic reduction, simulation, JEDEC file creation and documentation are then completed by all of the popular compilers.

Assignment of signals to pins or buried nodes as well as selecting the various options of the PLV5000 (such as register clocks and input latches) can be done manually in the design data base file, or an automatic fitter may be used.

A logic fitter assigns pins and nodes to make best use of the features in the PLV5000, and frees the designer from being required to learn all of the features of a complex device such as the PLV5000. For further information on fitters for the PLV5000, contact Signetics' PLD applications department.

After correcting any syntax and logic errors discovered by the compiler, the JEDEC file is ready to download to an EPLD programmer. These are available from a number of manufacturers. Programmed devices are usually first tested in the programmer with your supplied test vectors. The next step is to check out your "custom chip" in the target system. When this hardware debug step is complete, your system is ready to go—all in a matter of hours.

### **DESIGN FLOW DIAGRAM**

ABEL™ is a trademark of Data I/O Corporation. CUPL™ is a trademark of Logical Devices, LOGiC™ is a trademark of ISDATA.

August 1991

PLV5000/L

## **OPERATING MODES**

|                 | (68-Lead PLCC or Cerquad J-Bend Packages) PIN # |                 |                 |                 |                             |    |                                 |                      |                  |  |  |

|-----------------|-------------------------------------------------|-----------------|-----------------|-----------------|-----------------------------|----|---------------------------------|----------------------|------------------|--|--|

| MODE            | 1                                               | 2               | 36              | 34              | 68                          | 66 | V <sub>CC</sub> (3, 20, 37, 54) | l/Os                 | I/O<br>Pin 65    |  |  |

| "EPLD"          | X <sup>1</sup>                                  | Х               | Х               | ×               | х                           | ×  | 5V                              | I/O                  | 1/0              |  |  |

| Program         | V <sub>PP</sub>                                 | V <sub>IL</sub> | V <sub>IL</sub> | VH              | V <sub>IH</sub>             | ×  | 6V                              | ADD/D <sub>IN</sub>  | ADD              |  |  |

| PGM Verify      | V <sub>PP</sub>                                 | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub>             | ×  | 6V                              | ADD/D <sub>OUT</sub> | ADD              |  |  |

| PGM Inhibit     | V <sub>PP</sub>                                 | V <sub>IH</sub> | V <sub>IH</sub> | ViH             | V <sub>IH</sub>             | ×  | 6V                              | Hi-Z                 | Hi-Z             |  |  |

| Preload/Observe |                                                 | D <sub>IN</sub> | Х               | ×               | V <sub>H</sub> <sup>2</sup> | ŌE | 5V                              | Hi-Z                 | D <sub>OUT</sub> |  |  |

#### NOTES:

- 1. X can be  $V_{IL}$  or  $V_{IH}$ . 2.  $V_{H}$  = 11.0V to 14.0V.

### **SECURITY FUSE USAGE**

A single fuse is provided to prevent unauthorized copying of the PLV5000 fuse patterns. Once programmed, the outputs appear programmed during verify. The security fuse should be programmed last (after verifying all other programmed bits), as its effect is immediate.

The security fuse also inhibits Preload and Observability.

## **ERASURE CHARACTERISTICS**

The entire memory array of a PLV5000 is erased after exposure to ultraviolet light at a wavelength of 2537Å. Complete erasure is assured after a minimum of 20 minutes exposure using 12,000 μW/cm<sup>2</sup> intensity lamps spaced one inch away from the chip. Minimum erase time for lamps at other intensity ratings can be calculated from the minimum integrated erasure dose of 15W-sec/cm<sup>2</sup>. To prevent unintentional erasure, an opaque label is recommended to cover the clear window on any UV erasable PLD which will be subjected to continuous fluorescent indoor lighting or sunlight.

PLV5000/L

|                           | DEFINITIONS            |                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|---------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Data Sheet Identification | Product Status         | Definition                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Objective Specification   | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                            |  |  |  |  |  |  |  |

| Preliminary Specification | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |  |  |  |  |  |

| Product Specification     | Full Production        | This data sheet contains Final Specifications. Signetics reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |  |  |  |  |  |  |  |

Signetics reserves the right to make changes without notice in the products, including circuits, standard cells, and/or software, described or contained herein, in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

## LIFE SUPPORT APPLICATIONS

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics Products for use in such applications do so at their own risk, and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

## Philips – a worldwide company

Argentina: PHILIPS ARGENTINA S.A., Div. Philips Components, Vedia 3892, 1430 BUENOS AIRES, Tel. (01) 541-4261.

Australia: PHILIPS COMPONENTS PTY Ltd, 34 Waterloo Road, NORTH RYDE NSW 2113, Tel. (02) 805 4455. Fax. (02) 805 4466.

Austria: ÖSTERREICHISCHE PHILIPS INDUSTRIE G.m.b.H.,

UB Bauelemente, Triester Str. 64, 1101 WIEN Tel. (0222) 60 101-820.

Belgium: N.V PHILIPS PROF. SYSTEMS – Components Div., 80 Rue Des Deux Gares, B-1070 BRUXELLES, Tel. (02) 52 56 111.

Brazil: PHILIPS COMPONENTS (Active Devices & LCD)

Rua do Rocio 220, SAO PAULO-SP, CEP 4552, P.O. Box 7383

Tel. (416) 292-5161. (IC Products) PHILIPS COMPONENTS – Signetics Canada LTD., 1 Eva Road, Suite 411, ETOBICOKE, Ontario, M9C 425, Tel. (416) 626-6676. Chile: PHILIPS CHILENA S.A., Av. Santa Maria 0760, SANTIAGO,

Tel. (02) 7738 16.

Colombia: IPRELENSO LTDA., Carrera 21 No. 56-17, BOGOTA, D.E.,

P.O. Box 77621, Tel. (01) 249 7624.

Denmark: PHILIPS COMPONENTS A/S, Prags Boulevard 80, PB1919, DK-2300 COPENHAGEN S, Tel. 32-883333.

Finland: PHILIPS COMPONENTS, Sinikalliontie 3,

SF-2630 ESPOO, Tel. 358-0-50261.

France: PHILIPS COMPOSANTS, 117 Quai du Président Roosevelt, 92134 ISSY-LES-MOULINEAUX Cedex, Tel. (01) 40938000, Fax 01 409 386 92

Germany: PHILIPS COMPONENTS UB der Philips G.m.b.H., Burchardstrasse 19, D-2 HAMBURG 1, Tel. (040) 3296-0, Fax. 040 329 69 12.

Greece: PHILIPS HELLENIQUE S.A., Components Division, No. 15, 25th March Street, GR 17778 TAVROS, Tel (01) 4894 339/4894 911

Hong Kong: PHILIPS HONG KONG LTD., Components Div. 15/F Philips Ind. Bldg., 24-28 Kung Yip St., KWAI CHUNG, Tel. (0)-4245 121. Fax. 0 480 69 60.

lel. (U)-4245 121. Fax. 0.4806950.

India: PEICO ELECTRONICS & ELECTRICALS LTD., Components Dept., Shivsagar Estate 'A'Block, P.O. Box 6598, 254-D Dr. Annie Besant Rd., BOMBAY – 40018, Tel. (022) 4921 500-4921 515. Fax. 022 494 19063.

Indonesia: P.T. PHILIPS-RALIN ELECTRONICS, Components Div., Setiabudi II Building, 6th Fl., Jalan H.R. Rasuna Said (P.O. Box 223/KBY) Kuningan, JAKARTA 12910, Tel. (021) 51 7995.

Ireland: PHILIPS ELECTRONICS (IRELAND) LTD., Components

Division, Newstead, Clonskeagh, DUBLIN 14, Tel. (01) 693355.

taly: PHILIPS S.p.A., Philips Components, Piazza IV Novembre 3, I-20124 MILANO, Tel. (02) 6752.1, Fax. 02 67522642.

Japan: PHILIPS JAPAN LTD., Components Division, Philips Bldg 13-37, Kohnan 2-chome, Minato-ku, TOKYO 108, Tel. (03) 813-3740-5030. Fax. 03 81337400570.

Korea (Republic of): PHILIPS ELECTRONICS (KOREA) LTD. Components Division, Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL, Tel. (02) 794-5011.

Malaysia: PHILIPS MALAYSIA SDN BHD, Components Div., 3 Jalan SS15/2A SUBANG, 47500 PETALING JAYA,

Tel (03) 7345 511

Mexico: PHILIPS COMPONENTS, Paseo Triunfo de la Republica, No 215 Local 5, Cd Juarez CHI HUA HUA 32340 MEXICO Tel. (16) 18-67-01/02.

Netherlands: PHILIPS NEDERLAND B.V., Marktgroep Philips Components, Postbus 90050, 5600 PB EINDHOVEN, Tel. (040) 783749. New Zealand: PHILIPS NEW ZEALAND LTD., Components Division

110 Mt. Eden Road, C.P.O. Box 1041, AUCKLAND, Tel. (09) 605-914

Norway: NORSK A/S PHILIPS, Philips Components, Box 1, Manglerud 0612, OSLO, Tel. (02) 74 10 10.

Pakistan: PHILIPS ELECTRICAL CO. OF PAKISTAN LTD., Philips Markaz, M.A. Jinnah Rd., KARACHI-3, Tel. (021) 725772.

Peru: CADESA, Carretera Central 6.500, LIMA 3, Apartado 5612,

Tel. 51-14-35 00 59.

Philippines: PHILIPS Semiconductors Philippines Inc., 106 Valero St. Salcedo Village, P.O. Box 911, MAKATI, Metro MANILA, Tel. (63-2) 810-0161. Fax. 632 817 3474.

Tel. (63-2)810-0161. Fax. 632 8173474.

Portugal: PHILIPS PORTUGUESA S.A.R.L., Av. Eng. Duarte

Pacheco 6, 1009 LISBOA Codex, Tel. (019) 6831 21.

Singapore: PHILIPS SINGAPORE, PTE LTD., Components Div.,

Lorong 1, Toa Payoh, SINGAPORE 1231. Tel. 3502000.

South Africa: S.A. PHILIPS PTY LTD., Components Division,

195-215 Main Road, JOHANNESBURG 2000, P.O. Box 7430,

Tel. (011) 470-5434. Fax. (011) 4705494.

Spain: PHILIPS COMPONENTS, Balmes 22, 08007 BARCELONA,

Tel. (03) 301 6312, Eav. 03.301 4243.

Spain: PHILIPS COMPONENTS, Balmes 22, 08007 BARCELONA, Tel. (03) 301 63 12. Fax. 03 301 42 43.

Sweden: PHILIPS COMPONENTS, A.B., Tegeluddsvägen 1, S-11584 STOCKHOLM, Tel. (0)8-7821 000.

Switzerland: PHILIPS A.G., Components Dept., Allmendstrasse 140-142, CH-8027 ZÜRICH, Tel. (01) 488 22 11.

Taiwan: PHILIPS TAIWAN LTD., 581 Min Sheng East Road, P.O. Box 22978, TAIPEI 10446, Taiwan, Tel. 886-2-509 7666.

Exercise 2 E006290

Fax. 886 2 500 58 99.

Thailand: PHILIPS ELECTRICAL CO. OF THAILAND LTD., 283 Silom

Road, P.O. Box 961, BANGKOK, Tel. (02) 233-6330-9.

Turkey: TURK PHILIPS TICARET A. S., Philips Components, Talatpasa Cad. No. 5, 80640 LEVENT/ISTANBUL, Tel. (01) 179 27 70.

United Kingdom: PHILIPS COMPONENTS LTD., Mullard House,

Torrington Place, LONDON WC1E 7HD, Tel. (071) 580 6633, Fax. 071 436 21 96.

Fax. 071 43621 96.

United States: (Colour picture tubes – Monochrome & Colour Display Tubes) PHILIPS DISPLAY COMPONENTS COMPANY, 1600 Huron Parkway, P.O. Box 963, ANN ARBOR, Michigan 48106, Tel. 313996-9400. Fax. 313 761 2886. (IC Products) PHILIPS COMPONENTS Signetics, 811 East Arques Avenue, SUNNYVALE, CA 94088-3409, Tel. (800) 227-1817. (Passive Components, Discrete Semiconductors, Materials and Professional Components & LCD) PHILIPS COMPONENTS. Discrete Products Physician. Semiconductors, Materials and Professional Components & LCD PHLIPS COMPONENTS, Discrete Products Division, 2001 West Blue Heron Blvd., P.O. Box 10330, RIVIERA BEACH, Florida 33404, Tel. (407) 881-3200.

Uruguay: PHILIPS COMPONENTS, Coronel Mora 433, MONTEVIDEO, Tel. (02) 70-4044.

Venezuela: MAGNETICAS.A., Calle 6, Ed. Las Tres Jotas, CARACAS 1074A, App. Post. 78117, Tel. (02) 241 75 09.

Zimbabwe: PHILIPS ELECTRICAL (PVT) LTD., 600 March 25e4 LADAME.

62 Mutare Road, HARARE, P.O. Box 994, Tel. 47211.

For all other countries apply to: Philips Components, Marketing Communications, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Telex 35000 phtcnl, Fax. +31-40-724825

ADS91

© Philips Export B.V. 1991

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

9397 329 80011

## **Philips Semiconductors**

**PHILIPS**

16

027331 2 \_ \_