# 30 W Quad Half-Bridge Digital Amplifier Power Stage

#### **Features**

- ♦ Configurable Outputs (10% THD+N)

- 2 x 15 W into 8  $\Omega$ , Full-Bridge

- 1 x 30 W into 4  $\Omega$ , Parallel Full-Bridge

- 4 x 7 W into 4  $\Omega$ , Half-Bridge

- 2 x 7 W into 4 Ω, Half-Bridge + 1 x 15 W into 8 Ω, Full-Bridge

- ♦ Space-Efficient Thermally-Enhanced QFN

- No External Heat Sink Required

- ♦ > 100 dB Dynamic Range System Level

- ♦ < 0.1% THD+N @ 1 W System Level

- Built-In Protection with Error Reporting

- Over-Current

- Thermal Warning and Overload

- Under-Voltage

- ♦ +8 V to +18 V High Voltage Supply

- ♦ PWM Popguard® for Quiet Startup

- ♦ No Bootstrap Required

- ♦ Low Quiescent Current

- Low Power Standby Mode

## **Common Applications**

- ♦ Integrated Digital Televisions

- ♦ Portable Media Player Docking Stations

- ♦ Mini/Micro Shelf Systems

- ♦ Powered Desktop Speakers

## **General Description**

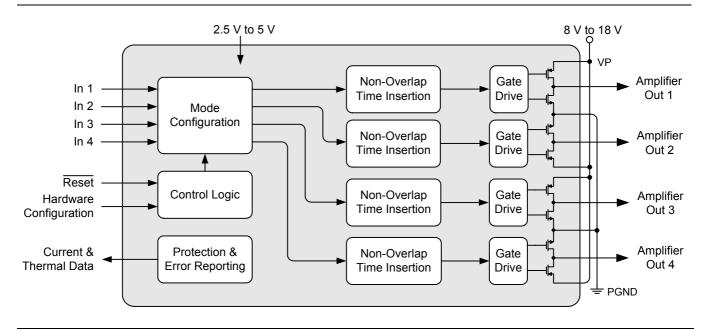

The CS4412A is a high-efficiency power stage for digital Class-D amplifiers designed to input PWM signals from a modulator such as the CS4525. The power stage outputs can be configured as four half-bridge channels, two half-bridge channels and one full-bridge channel, two full-bridge channels, or one parallel full-bridge channel.

The CS4412A integrates on-chip over-current, undervoltage, over-temperature protection and error reporting as well as a thermal warning indicator. The low  $R_{\rm DS(ON)}$  outputs can source up to 2.5 A peak current, delivering high efficiency which allows small device package and lower power supplies.

The CS4412A is available in a 48-pin QFN package in Commercial grade (-10 to +70° C). The CRD4412A customer reference design is also available. Please refer to "Ordering Information" on page 24 for complete ordering information.

Advance Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

# TABLE OF CONTENTS

|      | 1. PIN DESCRIPTION                                            | •  |

|------|---------------------------------------------------------------|----|

|      | 2. CHARACTERISTICS AND SPECIFICATIONS                         |    |

|      | RECOMMENDED OPERATING CONDITIONS                              |    |

|      |                                                               |    |

|      | ABSOLUTE MAXIMUM RATINGS PWM POWER OUTPUT CHARACTERISTICS     |    |

|      |                                                               |    |

|      | DC ELECTRICAL CHARACTERISTICS                                 |    |

|      | DIGITAL IVO PIN CHARACTERISTICS                               |    |

|      | DIGITAL I/O PIN CHARACTERISTICS                               |    |

|      | 3. TYPICAL CONNECTION DIAGRAMS                                |    |

|      | 4. APPLICATIONS                                               |    |

|      | 4.1 Overview                                                  |    |

|      | 4.2 Reset and Power-Up                                        |    |

|      | 4.2.1 PWM Popguard Transient Control                          |    |

|      | 4.2.2 Initial Pulse Edge Delay                                |    |

|      | 4.2.3 Recommended Power-Up Sequence                           |    |

|      | 4.2.4 Recommended Power-Down Sequence                         |    |

|      | 4.3 Output Mode Configuration                                 |    |

|      | 4.4 Output Filters                                            |    |

|      | 4.4.1 Half-Bridge Output Filter                               |    |

|      | 4.4.2 Full-Bridge Output Filter (Stereo or Parallel)          |    |

|      | 4.5 Device Protection and Error Reporting                     |    |

|      | 4.5.1 Over-Current Protection                                 |    |

|      | 4.5.2 Thermal Warning, Thermal Error, and Under-Voltage Error |    |

|      | 5. POWER SUPPLY, GROUNDING, AND PCB LAYOUT                    |    |

|      | 5.1 Power Supply and Grounding                                |    |

|      | 5.1.1 Integrated VD Regulator                                 |    |

|      | 5.2 QFN Thermal Pad                                           |    |

|      | 6. PARAMETER DEFINITIONS                                      |    |

|      | 7. PACKAGE DIMENSIONS                                         |    |

|      | 8. THERMAL CHARACTERISTICS                                    |    |

|      | 8.1 Thermal Flag                                              |    |

|      | 9. ORDERING INFORMATION                                       |    |

|      | 10. REVISION HISTORY                                          | 24 |

| _IST | T OF FIGURES                                                  |    |

|      |                                                               |    |

|      | Figure 1.Stereo Full-Bridge Typical Connection Diagram        |    |

|      | Figure 2.2.1 Channel Typical Connection Diagram               |    |

|      | Figure 3.4 Channel Half-Bridge Typical Connection Diagram     |    |

|      | Figure 4.Parallel Full-Bridge Typical Connection Diagram      |    |

|      | Figure 5.Output Filter - Half-Bridge                          |    |

|      | Figure 6.Output Filter - Full-Bridge                          | 18 |

| ICT  | T OF TABLES                                                   |    |

| _131 | I OF TABLES                                                   |    |

|      | Table 1. I/O Power Rails                                      | 8  |

|      | Table 2. Typical Ramp Times for Typical VP Voltages           | 13 |

|      | Table 3. Output Mode Configuration Options                    |    |

|      | Table 4. Low-Pass Filter Components - Half-Bridge             |    |

|      | Table 5. DC-Blocking Capacitors Values - Half-Bridge          |    |

|      | Table 6. Low-Pass Filter Components - Full-Bridge             |    |

|      | Table 7. Over-current Error Conditions                        |    |

|      | Table 8. Thermal and Under-Voltage Error Conditions           |    |

|      | Table 9. Power Supply Configuration and Settings              |    |

|      |                                                               |    |

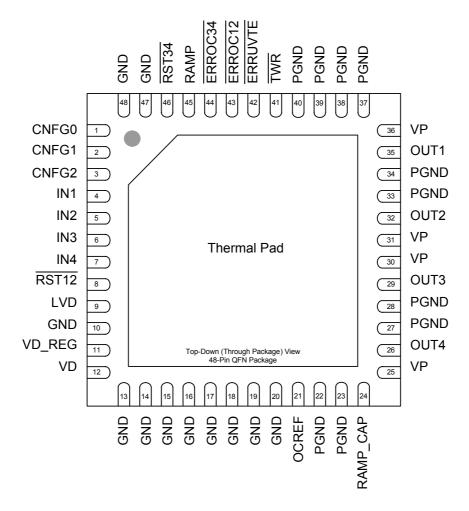

# 1. PIN DESCRIPTION

| Pin Name | Pin# | Pin Description                                                                                                                                                                                                         |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNFG0    | 1    | Out Configuration Colort (Innut) Head to get the DIAM output configuration made Con "Output                                                                                                                             |

| CNFG1    | 2    | <b>Out Configuration Select</b> ( <i>Input</i> ) - Used to set the PWM output configuration mode. See "Output Mode Configuration" on page 15.                                                                           |

| CNFG2    | 3    | wode Configuration on page 15.                                                                                                                                                                                          |

| IN1      | 4    |                                                                                                                                                                                                                         |

| IN2      | 5    | <b>PWM Input</b> ( <i>Input</i> ) - Logic-level switching inputs from a PWM modulator.                                                                                                                                  |

| IN3      | 6    | PVVM IIIput (IIIput) - Logic-level Switching IIIputs Iroth a PVVM Iriodulator.                                                                                                                                          |

| IN4      | 7    |                                                                                                                                                                                                                         |

| RST12    | 8    | Reset Input (Input) - Reset inputs for channels 1/2 and 3/4 respectively. Active low.                                                                                                                                   |

| RST34    | 46   | reset input (input) - Neset inputs for channels 1/2 and 5/4 respectively. Active low.                                                                                                                                   |

| LVD      | 9    | <b>VD Voltage Level Indicator</b> ( <i>Input</i> ) - Identifies the voltage level attached to VD. When applying 5.0 V to VD, LVD must be connected to VD. When applying 2.5 V or 3.3 V to VD, LVD must be GND.          |

| VD_REG   | 11   | Core Digital Power (Output) - Internally generated low voltage power supply for digital logic.                                                                                                                          |

| VD       | 12   | Digital Power (Input) - Positive power supply for the internal regulators and digital I/O.                                                                                                                              |

| OCREF    | 21   | <b>Over-current Reference</b> ( <i>Input</i> ) - Sets over-current trigger level. Connect pin through a resistor to GND. See "Device Protection and Error Reporting" on page 19. This pins should not be left floating. |

| Pin Name                     | Pin#                                            | Pin Description                                                                                                                                                                                     |

|------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAMP_CAP                     | 24                                              | <b>Output Ramp Capacitor</b> ( <i>Input</i> ) - Used by the PWM PopGuard Transient Control to suppress the initial pop in half-bridge-configured outputs.                                           |

| GND                          | 10,13<br>14,15<br>16,17<br>18,19<br>20,47<br>48 | <b>Ground</b> ( <i>Input</i> ) - Ground for the internal logic and I/O. These pins should be connected to the common system ground.                                                                 |

| VP                           | 25,30<br>31,36                                  | <b>High Voltage Output Power</b> ( <i>Input</i> ) - High voltage power supply for the individual output power half-bridge devices.                                                                  |

| PGND                         | 22,23<br>27,28<br>33,34<br>37,38<br>39,40       | <b>Power Ground</b> ( <i>Input</i> ) - Ground for the individual output power half-bridge devices. These pins should be connected to the common system ground.                                      |

| OUT4<br>OUT3<br>OUT2<br>OUT1 | 26<br>29<br>32<br>35                            | PWM Output (Output) - Amplified PWM power outputs.                                                                                                                                                  |

| TWR                          | 41                                              | <b>Thermal Warning Output</b> ( <i>Output</i> ) - Thermal warning output. Open drain, active low. See "Device Protection and Error Reporting" on page 19.                                           |

| ERRUVTE                      | 42                                              | <b>Thermal and Under-voltage Error Output</b> ( <i>Output</i> ) - Error flag for thermal shutdown and under-voltage. Open drain, active low. See "Device Protection and Error Reporting" on page 19 |

| ERROC12<br>ERROC34           | 43<br>44                                        | <b>Over-current Error Output</b> ( <i>Output</i> ) - Over-current error flag for the associated outputs. Open drain, active low. See "Device Protection and Error Reporting" on page 19.            |

| RAMP                         | 45                                              | Ramp-up/down Select ( <i>Input</i> ) - Set high to enable ramping. When set low, ramping is disabled. See "PWM Popguard Transient Control" on page 13.                                              |

| Thermal Pad                  | -                                               | <b>Thermal Pad</b> - Thermal relief pad for optimized heat dissipation. See "QFN Thermal Pad" on page 20 for more information.                                                                      |

## 2. CHARACTERISTICS AND SPECIFICATIONS

## RECOMMENDED OPERATING CONDITIONS

GND = PGND = 0 V, all voltages with respect to ground.

| Parameters                    | Symbol           | Min   | Nom | Max   | Units |

|-------------------------------|------------------|-------|-----|-------|-------|

| DC Power Supply               | •                |       |     |       |       |

| Digital Core                  | VD               | 2.375 | 2.5 | 2.625 | V     |

|                               | VD               | 3.135 | 3.3 | 3.465 | V     |

|                               | VD               | 4.75  | 5.0 | 5.25  | V     |

| Power Stage                   | VP               | 8.0   |     | 18.0  | V     |

| Temperature                   | •                | •     |     |       |       |

| Ambient Temperature Commercia | I T <sub>A</sub> | -10   | -   | +70   | °C    |

| Junction Temperature          | T <sub>J</sub>   | -10   | -   | +125  | °C    |

## **ABSOLUTE MAXIMUM RATINGS**

GND = PGND = 0 V; all voltages with respect to ground.

|                        | Parameters                       | Symbol           | Min  | Max      | Units |

|------------------------|----------------------------------|------------------|------|----------|-------|

| DC Power Supply        | ,                                |                  |      |          |       |

| Power Stage            | Outputs Switching and Under Load | VP               | -0.3 | 19.8     | V     |

| Power Stage            | No Output Switching              | VP               | -0.3 | 23.0     | V     |

| Digital Core           |                                  | VD               | -0.3 | 6.0      | V     |

| Inputs                 | <u>'</u>                         |                  |      |          |       |

| Input Current          | (Note 1)                         | l <sub>in</sub>  | -    | ±10      | mA    |

| Digital Input Voltage  | (Note 2)                         | $V_{IND}$        | -0.3 | VD + 0.4 | V     |

| Temperature            |                                  |                  |      |          |       |

| Ambient Operating Temp | perature - Power Applied         |                  |      |          |       |

|                        | Commercial                       | T <sub>A</sub>   | -20  | +85      | °C    |

| Storage Temperature    |                                  | T <sub>stg</sub> | -65  | +150     | °C    |

**WARNING:** Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

Notes:

- 1. Any pin except supplies. Transient currents of up to  $\pm 100$  mA on the PWM input pins will not cause SCR latch-up.

- 2. The maximum over/under voltage is limited by the input current.

## PWM POWER OUTPUT CHARACTERISTICS

Test Conditions (unless otherwise specified): GND = PGND = 0 V; All voltages with respect to ground;  $T_A$  = 25° C; VD = 3.3 V; VP = 18 V;  $R_L$  = 8  $\Omega$  for full-bridge,  $R_L$  = 4  $\Omega$  for half-bridge and parallel full-bridge; PWM Switch Rate = 384 kHz; 10 Hz to 20 kHz Measurement Bandwidth; Input source is CS4525 PWM\_SIG outputs; Performance measurements taken with a full-scale 997 Hz sine wave, an AES17 measurement filter; Half-Bridge measurements taken through the Half-Bridge Output Filter shown in Figure 5; Stereo Full-Bridge and Parallel Full-Bridge measurements taken through the Full-Bridge Output Filter shown in Figure 6;.

| Parameters                                   | Symbol              | Conditions                                      | Min | Тур  | Max | Units |

|----------------------------------------------|---------------------|-------------------------------------------------|-----|------|-----|-------|

| Power Output per Channel                     |                     |                                                 |     |      |     |       |

| Stereo Full-Bridge                           |                     | THD+N < 10%                                     | -   | 15   | -   | W     |

|                                              |                     | THD+N < 1%                                      | -   | 12   | -   | W     |

| Half-Bridge                                  | Po                  | THD+N < 10%                                     | -   | 7    | -   | W     |

|                                              |                     | THD+N < 1%                                      | -   | 5.5  | -   | W     |

| Parallel Full-Bridge                         |                     | THD+N < 10%                                     | -   | 30   | -   | W     |

|                                              |                     | THD+N < 1%                                      | -   | 23.5 | -   | W     |

| Total Harmonic Distortion + Noise            |                     |                                                 |     |      |     |       |

| Stereo Full-Bridge                           |                     | P <sub>O</sub> = 1 W                            | -   | 0.05 | -   | %     |

|                                              |                     | $P_{O} = 0 \text{ dBFS} = 11.3 \text{ W}$       | -   | 0.10 | -   | %     |

| Half-Bridge                                  | THD+N               | P <sub>O</sub> = 1 W                            | -   | 0.12 | -   | %     |

|                                              |                     | $P_{O} = 0 \text{ dBFS} = 5.0 \text{ W}$        | -   | 0.28 | -   | %     |

| Parallel Full-Bridge                         |                     | $P_0 = 1 W$                                     | -   | 0.1  | -   | %     |

|                                              |                     | P <sub>O</sub> = 0 dBFS = 22.6 W                | -   | 0.3  | -   | %     |

| Dynamic Range                                |                     |                                                 |     |      |     |       |

| Stereo Full-Bridge                           |                     | $P_O = -60 \text{ dBFS}$ , A-Weighted           |     | 102  | -   | dB    |

|                                              |                     | $P_O$ = -60 dBFS, Unweighted                    | -   | 99   | -   | dB    |

| Half-Bridge                                  | DYR                 | $P_O = -60$ dBFS, A-Weighted                    | -   | 102  | -   | dB    |

| 5 ".5"5                                      |                     | $P_O = -60$ dBFS, Unweighted                    | -   | 99   | -   | dB    |

| Parallel Full-Bridge                         |                     | P <sub>O</sub> = -60 dBFS, A-Weighted           | -   | 102  | -   | dB    |

|                                              |                     | P <sub>O</sub> = -60 dBFS, Unweighted           | -   | 99   | -   | dB    |

| MOSFET On Resistance                         | R <sub>DS(ON)</sub> | $I_d = 0.5 \text{ A}, T_J = 50^{\circ}\text{C}$ | -   | 280  | -   | mΩ    |

| Efficiency                                   | h                   | $P_0 = 2 \times 15 \text{ W}, R_L = 8 \Omega$   | -   | 85   | -   | %     |

| Minimum Output Pulse Width                   | PW <sub>min</sub>   | No Load                                         | -   | 50   | -   | ns    |

| Rise Time of OUTx                            | t <sub>r</sub>      | Resistive Load                                  | -   | 20   | -   | ns    |

| Fall Time of OUTx                            | t <sub>f</sub>      | Resistive Load                                  | -   | 20   | -   | ns    |

| PWM Output Over-Current Error Trigger Point  |                     | $T_A = 25^{\circ}C$ , OCREF = 16.2 k $\Omega$   | -   | 2.5  | -   | Α     |

|                                              | I <sub>CE</sub>     | $T_A = 25$ °C, OCREF = 18 k $\Omega$            | -   | 2.1  | -   | Α     |

|                                              |                     | $T_A = 25^{\circ}C$ , OCREF = 22 k $\Omega$     | -   | 1.7  | -   | Α     |

| Junction Thermal Warning Trigger Point       | $T_TW$              |                                                 | -   | 105  | -   | °C    |

| Junction Thermal Error Trigger Point         | T <sub>TE</sub>     |                                                 | -   | 125  | -   | °C    |

| VP Under-Voltage Error Falling Trigger Point | V <sub>UVFALL</sub> | T <sub>A</sub> = 25°C                           | -   | 4.7  | 4.9 | V     |

| VP Under-Voltage Error Rising Trigger Point  | V <sub>UVRISE</sub> | T <sub>A</sub> = 25°C                           | -   | 4.95 | 5.4 | V     |

## DC ELECTRICAL CHARACTERISTICS

GND = PGND = 0 V; All voltages with respect to ground; PWM switch rate = 384 kHz; Unless otherwise specified.

| Parameters                        |              | Min  | Тур | Max       | Units   |

|-----------------------------------|--------------|------|-----|-----------|---------|

| Normal Operation                  | (Notes 3, 5) |      |     |           |         |

| Power Supply Current              | VD = 3.3 V   | -    | 20  | -         | mA      |

| Power Dissipation                 | VD = 3.3 V   | -    | 66  | -         | mW      |

| Power-Down Mode                   | (Note 4)     |      |     |           |         |

| Power Supply Current              | VD = 3 .3 V  | -    | 2   | -         | mA      |

| VD_REG Characteristics            |              |      |     |           |         |

| Nominal Voltage DC current source |              | 2.25 | 2.5 | 2.75<br>3 | V<br>mA |

- **Notes:** 3. Normal operation is defined as  $\overline{RST12}$  and  $\overline{RST34}$  = HI.

- 4. Power-Down Mode is defined as  $\overline{RST12}$  and  $\overline{RST34}$  = LOW with all input lines held static.

- 5. Power supply current increases with increasing PWM switching rates.

## **DIGITAL INTERFACE SPECIFICATIONS**

GND = PGND = 0 V; All voltages with respect to ground; Unless otherwise specified.

| Parameters                                     | Symbol          | Min        | Max         | Units |

|------------------------------------------------|-----------------|------------|-------------|-------|

| High-Level Input Voltage                       | $V_{IH}$        | 0.7*VD_REG | VD          | V     |

| Low-Level Input Voltage                        | $V_{IL}$        | -          | 0.20*VD_REG | V     |

| High-Level Output Voltage $I_0 = 2 \text{ mA}$ | V <sub>OH</sub> | 0.90*VD    | -           | V     |

| Input Leakage Current                          | I <sub>in</sub> | -          | ±10         | μΑ    |

| Input Capacitance                              |                 | -          | 8           | pF    |

## **DIGITAL I/O PIN CHARACTERISTICS**

The logic level for each input is set by its corresponding power supply and should not exceed the maximum ratings.

| Power Supply | Pin<br>Number | Pin Name | I/O    | Driver                    | Receiver      |

|--------------|---------------|----------|--------|---------------------------|---------------|

| VD           | 1             | CNFG0    | Input  | -                         | 2.5 V - 5.0 V |

|              | 2             | CNFG1    | Input  | -                         | 2.5 V - 5.0 V |

|              | 3             | CNFG2    | Input  | -                         | 2.5 V - 5.0 V |

|              | 4             | IN1      | Input  | -                         | 2.5 V - 5.0 V |

|              | 5             | IN2      | Input  | -                         | 2.5 V - 5.0 V |

|              | 6             | IN3      | Input  | -                         | 2.5 V - 5.0 V |

|              | 7             | IN4      | Input  | -                         | 2.5 V - 5.0 V |

|              | 8             | RST12    | Input  | -                         | 2.5 V - 5.0 V |

|              | 9             | LVD      | Input  | -                         | 2.5 V - 5.0 V |

|              | 41            | TWR      | Output | 2.5 V - 5.0 V, Open Drain | -             |

|              | 42            | ERRUVTE  | Output | 2.5 V - 5.0 V, Open Drain | -             |

|              | 43            | ERROC12  | Output | 2.5 V - 5.0 V, Open Drain | -             |

|              | 44            | ERROC34  | Output | 2.5 V - 5.0 V, Open Drain | -             |

|              | 45            | RAMP     | Input  | -                         | 2.5 V - 5.0 V |

|              | 46            | RST34    | Input  | -                         | 2.5 V - 5.0 V |

| VP           | 35            | OUT1     | Output | 8 V - 18 V Power MOSFET   | -             |

|              | 32            | OUT2     | Output | 8 V - 18 V Power MOSFET   | -             |

|              | 29            | OUT3     | Output | 8 V - 18 V Power MOSFET   | -             |

|              | 26            | OUT4     | Output | 8 V - 18 V Power MOSFET   | -             |

Table 1. I/O Power Rails

## 3. TYPICAL CONNECTION DIAGRAMS

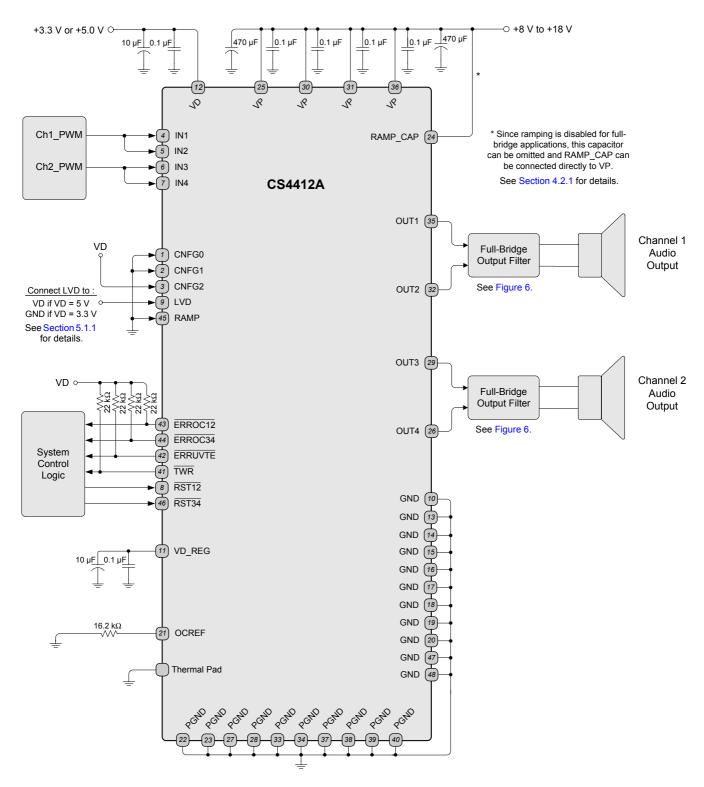

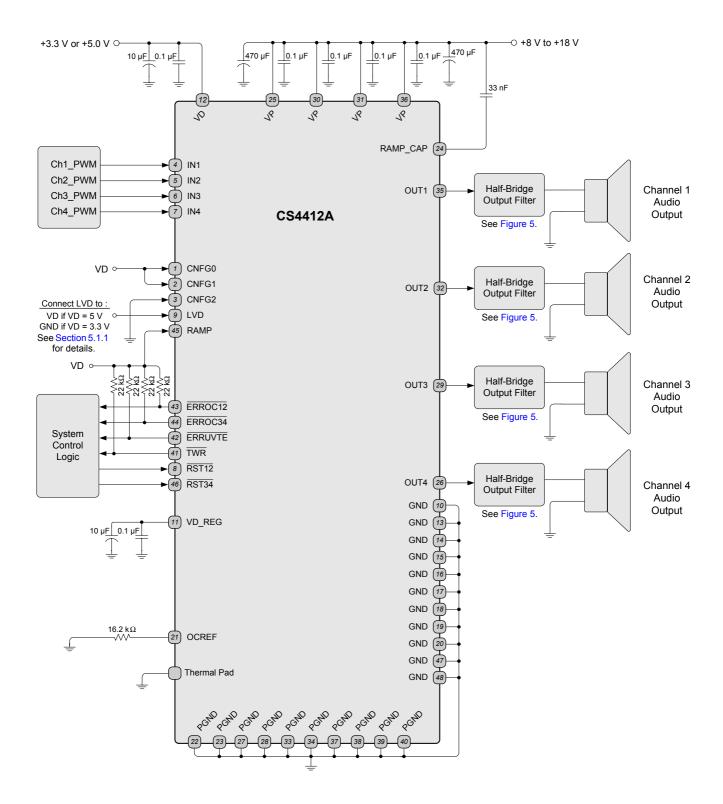

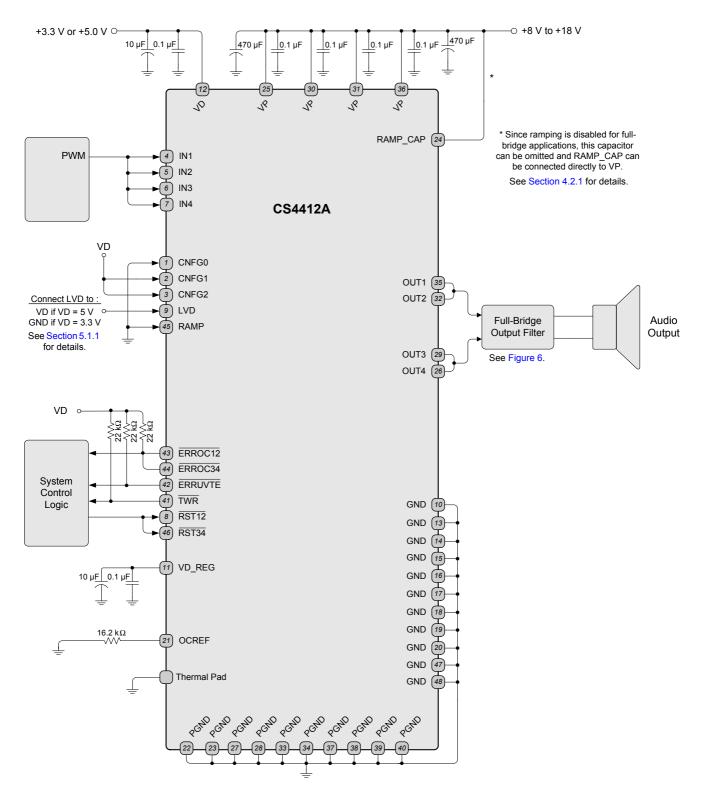

Figure 1. Stereo Full-Bridge Typical Connection Diagram

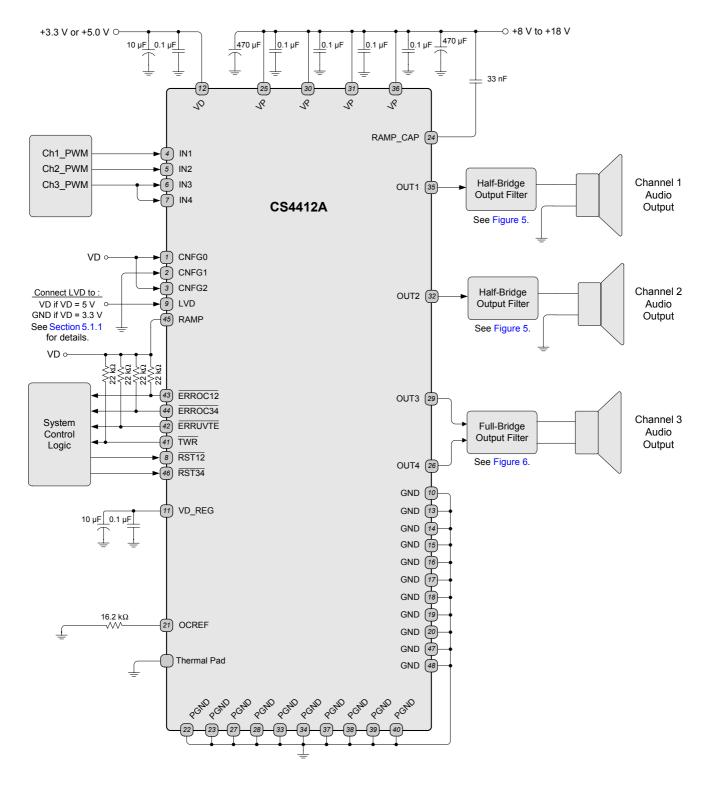

Figure 2. 2.1 Channel Typical Connection Diagram

Figure 3. 4 Channel Half-Bridge Typical Connection Diagram

Figure 4. Parallel Full-Bridge Typical Connection Diagram

## 4. APPLICATIONS

#### 4.1 Overview

The CS4412A is a high-efficiency power stage for digital Class-D amplifiers designed to be configured as four half-bridge channels, two half-bridge channels and one full-bridge channel, two full-bridge channels, or one parallel full-bridge channel.

The CS4412A integrates on-chip over-current, under-voltage, over-temperature protection and error reporting as well as a thermal warning indicator. The low  $R_{DS(ON)}$  outputs can source up to 2.5 A peak current, delivering 85% efficiency. This efficiency provides for smaller device package, no external heat sink requirements, and smaller power supplies.

## 4.2 Reset and Power-Up

Reliable power-up can be accomplished by keeping the <u>device</u> in reset until the power supplies and configuration pins are stable. It is also recommended that the <u>RST12</u> and <u>RST34</u> pins be activated if the voltage supplies drop below the recommended operating condition to prevent power-glitch related issues.

When the RST12 or RST34 are low, the corresponding channels of the CS4412A enter a low-power mode; all of the channels' internal states are reset and the corresponding power output pins are held in a high-impedance state. When RST12 or RST34 are high, the corresponding outputs will begin normal operation according to the RAMP, CNFG[2:0], and IN1 - IN4 pins.

## 4.2.1 PWM Popguard Transient Control

The CS4412A uses PWM Popguard technology to minimize the effects of output transients during power-up and power-down for half-bridge configurations. This technique reduces the audio transients commonly produced by half-bridge, single-supply amplifiers when implemented with external DC-blocking capacitors connected in series with the audio outputs.

When the device is configured for ramping (RAMP set high) and  $\overline{RST12}$  or  $\overline{RST34}$  is set high, the corresponding power outputs will ramp-up to the bias point (VP/2). This gradual voltage ramping allows time for the external DC-blocking capacitor to charge to the quiescent voltage, minimizing the power-up transient. The corresponding outputs will not begin normal operation until the ramp has reached the bias point. The time it takes to complete a ramp-up sequence will vary slightly from the applied VP voltage; typical ramp-up speeds achieved with a 1000  $\mu F$  DC blocking capacitor are listed in Table 2. These times will scale with the value of the capacitor.

| VP Voltage | Typical Ramp Time* |

|------------|--------------------|

| 12 V       | 1.25 seconds       |

| 15 V       | 0.95 seconds       |

| 18 V       | 0.80 seconds       |

<sup>\*</sup> With 1000 μF DC Blocking Capacitor.

Table 2. Typical Ramp Times for Typical VP Voltages

When the device is configured for ramping (RAMP set high) and RST12 or RST34 is set low, the corresponding outputs will begin to slowly ramp down from the bias point to PGND, allowing the DC-blocking capacitor to discharge.

The ramp feature is intended for use with half-bridge outputs. For "2.1 channel" applications with stereo half-bridge and mono full-bridge (CNFG[2:0] = 001 or 101), the ramp will only be applied to OUT1 and OUT2 (the half-bridge channels); OUT3 and OUT4 (the full-bridge channel) will not ramp.

The ramp feature requires a 33 nF capacitor on the RAMP\_CAP pin to VP. For applications that do not enable the ramping feature, RAMP\_CAP can be connected directly to VP.

It is not necessary to complete a ramp-up/down sequence before ramping up/down again.

#### 4.2.2 Initial Pulse Edge Delay

After RST12 or RST34 is released, the CS4412A will continue to hold the corresponding power output pins in a high-impedance state until a pulse edge is sensed on a corresponding PWM input pin. This is done to prevent a possible DC output condition on the speakers if the PWM inputs are not yet modulating immediately following the release of the corresponding reset signal. This initial transition delay is independent for each input/output pin pair; each output corresponding to an inactive input will remain in a high-impedance state until its input receives a pulse edge even if other inputs are activated. The pulse edge must be from a digital low state to a digital high state. Once a pulse edge is detected, the corresponding output pin will activate and switch as dictated by the output mode configuration as described in section 4.3 on page 15 until either an error condition is detected or until its reset pin is set low.

If the outputs are configured for ramping the CS4412A will perform a ramp-up sequence on OUT1/2 immediately following the release of RST12 and a ramp sequence on OUT3/4 immediately following the release of RST34. See section 4.2.1 on page 13 for more information on output ramping. If a pulse edge is detected on an input before the ramp-up sequence finishes on its corresponding output pin, the CS4412A will continue the ramp sequence and begin normal output operation immediately following its completion. If a pulse edge is not detected on an input by the time the ramp-up sequence has finished on its corresponding output pin, the output pin will be placed into and remain in a high-impedance state until a pulse edge is detected on the corresponding input.

#### 4.2.3 Recommended Power-Up Sequence

- 1. Turn on the system power.

- 2. Hold RST12 and RST34 low until the power supply is stable. In this state, all associated outputs are held in a high-impedance state.

- 3. Release  $\overline{RST12}$  and  $\overline{RST34}$  high.

- 4. Start the PWM modulator output.

#### 4.2.4 Recommended Power-Down Sequence

- 1. Mute the logic-level PWM inputs present on IN1 IN4 by applying 50 % duty-cycle input signals.

- 2. Hold RST12 and RST34 low.

- 3. Power down the remainder of the system.

## 4.3 Output Mode Configuration

Each OUTx pin will switch in association with the corresponding INx pin. For most configurations, OUTx will be non-inverted from INx; however, some INx pins can be configured for internal inversion to allow one PWM input to drive both the positive and negative sides of a full-bridge output. Unused OUTx pins must have their corresponding INx pin tied to ground.

Table 3 shows the setting of the CNFG[2:0] inputs and the corresponding mode of operation. These pins should remain static during operation (RST12 or RST34 set high).

| CNFG2 | CNFG1 | CNFG0 | Description                                                               | Necessary Input Connections                                                                                                                                                                                                                                  |

|-------|-------|-------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | 0     | Stereo Full-Bridge<br>Tied Loads                                          | IN1 must provide the PWM data for the first full-bridge. IN2 must be inverted from IN1 for full-bridge operation. IN3 must provide the PWM data for the second full-bridge. IN4 must be inverted from IN3 for full-bridge operation.                         |

| 0     | 0     | 1     | Stereo Half-Bridge<br>& Mono Full-Bridge<br>Tied Loads*                   | IN1 must provide the PWM data for the first half-bridge. IN2 must provide the PWM data for the second half-bridge. IN3 must provide the PWM data for the mono full-bridge. IN4 must be inverted from IN3 for full-bridge operation.                          |

| 0     | 1     | 0     | Mono Parallel Full-<br>Bridge Tied Load                                   | IN1 must provide the PWM data for the mono full-bridge. IN2 must be wired directly to IN1 for parallel full-bridge operation. IN3 must be inverted from IN1 for parallel full-bridge operation. IN4 must be wired to IN3 for parallel full-bridge operation. |

| 0     | 1     | 1     | Quad Half-Bridge<br>Tied Loads                                            | IN1 must provide the PWM data for the first half-bridge. IN2 must provide the PWM data for the second half-bridge. IN3 must provide the PWM data for the third half-bridge. IN4 must provide the PWM data for the fourth half-bridge.                        |

| 1     | 0     | 0     | Stereo Full-Bridge<br>Tied Loads<br>With Inversion                        | IN1 must provide the PWM data for the first full-bridge. IN2 must be wired to IN1; the CS4412A will internally invert IN2. IN3 must provide the PWM data for the second full-bridge. IN4 must be wired to IN3; the CS4412A will internally invert IN4.       |

| 1     | 0     | 1     | Stereo Half-Bridge<br>& Mono Full-Bridge<br>Tied Loads<br>With Inversion* | IN1 must provide the PWM data for the first half-bridge. IN2 must provide the PWM data for the second half-bridge. IN3 must provide the PWM data for the mono full-bridge. IN4 must be wired to IN3; the CS4412A will internally invert IN4.                 |

| 1     | 1     | 0     | Mono Parallel Full-<br>Bridge Tied Load<br>With Inversion                 | IN1 must be provided for half-bridge operation. IN2 must be wired to IN1 for parallel full-bridge operation. IN3 must be wired to IN1; the CS4412A will internally invert IN3. IN4 must be wired to IN1; the CS4412A will internally invert IN4.             |

| 1     | 1     | 1     | Reserved                                                                  | The input connections are not applicable.                                                                                                                                                                                                                    |

<sup>\*</sup> PWM Popguard Transient Control only affects OUT1 and OUT2.

**Table 3. Output Mode Configuration Options**

In Stereo Half-Bridge & Mono Full-Bridge configurations, the PWM Popguard Transient Control will only affect the two half-bridge outputs, OUT1 and OUT2. The full-bridge output will not ramp regardless of the state of the RAMP pin. See Section 4.2.1 on page 13 for more details about PWM Popguard Transient Control.

## 4.4 Output Filters

The filter placed after the PWM outputs can greatly affect the output performance. The filter not only reduces radiated EMI (snubber filter), but also filters high frequency content from the switching output before going to the speaker (low-pass LC filter).

#### 4.4.1 Half-Bridge Output Filter

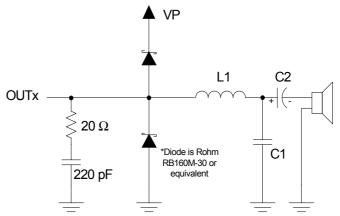

Figure 5 shows the output filter for a half-bridge configuration. The transient-voltage suppression circuit (snubber circuit) is comprised of a resistor (20  $\Omega$ , ¼ W) and capacitors (220 pF) and should be placed as close as possible to the corresponding PWM output pin to greatly reduce radiated EMI.

Each output pin must be connected to two Schottky diodes—one to ground and one to the VP supply. These diodes should be placed within 12 mm of the corresponding OUTx pin. The requirements of this diode are:

- 1. Rated  $I_F$  (average rectifier forward current) is greater than or equal to 1.0 A.

- 2. Support up to  $80^{\circ}$  C of lead temperature with  $V_F$  drop (forward voltage) less than or equal to 480 mV at the corresponding  $I_F$ .

- 3.  $V_R$  (reverse voltage) is greater than or equal to 20 V.

Figure 5. Output Filter - Half-Bridge

The inductor, L1, and capacitor, C1, comprise the low-pass filter. Along with the nominal load impedance of the speaker, these values set the cutoff frequency of the filter. Table 4 shows the component values for L1 and C1 based on nominal speaker (load) impedance for a corner frequency (-3 dB point) of approximately 35 kHz.

| Load | L1    | C1      |

|------|-------|---------|

| 4 Ω  | 22 µH | 1.0 µF  |

| 6 Ω  | 33 µH | 0.68 μF |

| 8 Ω  | 47 µH | 0.47 μF |

Table 4. Low-Pass Filter Components - Half-Bridge

C2 is the DC-blocking capacitor. Table 5 shows the component values for C2 based on corner frequency (-3 dB point) and a nominal speaker (load) impedances of 4  $\Omega$ , 6  $\Omega$ , and 8  $\Omega$ . This capacitor should also be chosen to have a ripple current rating above the amount of current that will passed through it.

| Load | Corner Frequency | C2      |

|------|------------------|---------|

| 4 Ω  | 40 Hz            | 1000 μF |

|      | 58 Hz            | 680 μF  |

|      | 120 Hz           | 330 µF  |

| 6 Ω  | 39 Hz            | 680 μF  |

|      | 68 Hz            | 390 µF  |

|      | 120 Hz           | 220 μF  |

| 8 Ω  | 42 Hz            | 470 µF  |

|      | 60 Hz            | 330 µF  |

|      | 110 Hz           | 180 μF  |

Table 5. DC-Blocking Capacitors Values - Half-Bridge

## 4.4.2 Full-Bridge Output Filter (Stereo or Parallel)

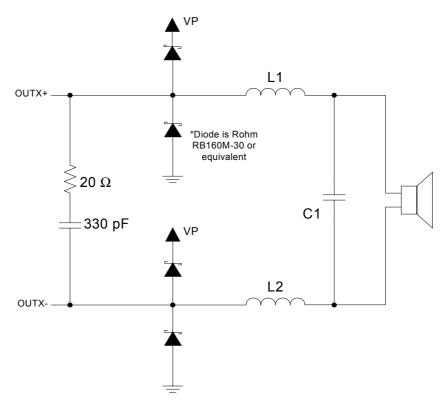

Figure 6 shows the output filter for a full-bridge configuration. The transient-voltage suppression circuit (snubber circuit) is comprised of a resistor (20  $\Omega$ ) and capacitor (330 pF) and should be placed as close as possible to the corresponding PWM output pins to greatly reduce radiated EMI. The inductors, L1 and L2, and capacitor, C1, comprise the low-pass filter. Along with the nominal load impedance of the speaker, these values set the cutoff frequency of the filter. Table 6 shows the component values based on nominal speaker (load) impedance for a corner frequency (-3 dB point) of approximately 35 kHz.

Each output pin must be connected to two Schottky diodes—one to ground and one to the VP supply. These diodes should be placed within 12 mm of the corresponding OUTx pin. The requirements of this diode are:

- 1. Rated I<sub>F</sub> (average rectifier forward current) is greater than or equal to 1.0 A.

- 2. Support up to  $80^{\circ}$  C of lead temperature with  $V_F$  drop (forward voltage) less than or equal to 480 mV at the corresponding  $I_F$ .

- 3. V<sub>R</sub> (reverse voltage) is greater than or equal to 20 V.

Figure 6. Output Filter - Full-Bridge

| Load | L1, L2 | C1      |

|------|--------|---------|

| 4 Ω  | 10 μH  | 1.0 µF  |

| 6 Ω  | 15 µH  | 0.47 μF |

| 8 Ω  | 22 µH  | 0.47 µF |

Table 6. Low-Pass Filter Components - Full-Bridge

## 4.5 Device Protection and Error Reporting

The CS4412A has built-in protection circuitry for over-current, under-voltage, and thermal warning/over-load conditions. The levels of the over-current error, thermal error, and VP under-voltage trigger points are listed in the PWM Power Output Characteristics table on page 6. Automatic shut-down will occur whenever any of these preset thresholds other than thermal warning are crossed.

Each error and warning pin implements an active-low open-drain driver and requires an external 22 k $\Omega$  pull-up resistor for proper operation.

#### 4.5.1 Over-Current Protection

An over-current error condition will occur if the peak output current exceeds the Over-Current Error trigger point. Over-current errors for OUT1/2 and OUT3/4 are reported on the ERROC12 and ERROC34 pins respectively. The power output of the channel which is reporting the over-current condition will be set to high-impedance until the error condition has been removed and the reset signal for that channel has been toggled from low to high.

| ERROCxy Reported Condition |                                                               |  |

|----------------------------|---------------------------------------------------------------|--|

| 0                          | Over-current error on channel x or channel y.                 |  |

| 1                          | Operating current of channel x and y within allowable limits. |  |

**Table 7. Over-current Error Conditions**

### 4.5.2 Thermal Warning, Thermal Error, and Under-Voltage Error

Table 8 shows the behavior of the TWR and ERRUVTE pins. When the junction temperature exceeds the junction thermal warning trigger point, the TWR pin will be set low. If the junction temperature continues to increase beyond the junction thermal error trigger point, the ERRUVTE pin will be set low. If the voltage on VP falls below the VP under-voltage error trigger point, ERRUVTE will be set low.

When the thermal error or VP under-voltage trigger point is crossed, all power outputs will be set in a high-impedance state until the error condition has been removed and both the RST12 and RST34 signals have been toggled from low to high.

| TWR | ERRUVTE | Reported Condition                                            |

|-----|---------|---------------------------------------------------------------|

| 0   | 0       | Thermal warning and thermal error and/or under-voltage error. |

| 0   | 1       | Thermal warning only.                                         |

| 1   | 0       | Under-voltage error.                                          |

| 1   | 1       | Junction temperature and VP voltage within normal limits.     |

Table 8. Thermal and Under-Voltage Error Conditions

# 5. POWER SUPPLY, GROUNDING, AND PCB LAYOUT

### 5.1 Power Supply and Grounding

The CS4412A requires careful attention to power supply and grounding arrangements if its potential performance is to be realized.

Extensive use of power and ground planes, ground plane fill in unused areas and surface mount decoupling capacitors are recommended. It is necessary to decouple the power supply by placing capacitors directly between the power and ground of the CS4412A. Decoupling capacitors should be as close to the pins of the CS4412A as possible. The lowest value ceramic capacitor should be closest to the pin and should be mounted on the same side of the board as the CS4412A to minimize inductance effects. The CRD4412A reference design demonstrates the optimum layout and power supply arrangements.

## 5.1.1 Integrated VD Regulator

The CS4412A includes an internal linear regulator to provide a fixed 2.5 V supply from the VD supply voltage for its internal digital logic. The LVD pin must be set to indicate the voltage present on the VD pin as shown in Table 9 below.

| VD Connection | VD_REG Connection        | LVD Connection |

|---------------|--------------------------|----------------|

| 5 V Supply    | Bypass Capacitors Only   | VD             |

| 3.3 V Supply  | Bypass Capacitors Only   | GND            |

| 2.5 V Supply  | VD and Bypass Capacitors | GND            |

**Table 9. Power Supply Configuration and Settings**

The output of the digital regulator is presented on the VD\_REG pin and may be used to provide an external device with up to 3 mA of current at its nominal output voltage of 2.5 V.

If a nominal supply voltage of 2.5 V is used as the VD supply (see the Recommended Operating Conditions table on page 5), the VD and VD\_REG must be connected to the VD supply source. In this configuration, the internal regulator is bypassed and the external supply source is used to directly drive the internal digital logic.

## 5.2 QFN Thermal Pad

The CS4412A is available in a compact QFN package. The underside of the QFN package reveals a large metal pad that serves as a thermal relief to provide for maximum heat dissipation. This pad must mate with an equally dimensioned copper pad on the PCB and must be electrically connected to ground. A series of thermal vias should be used to connect this copper pad to one or more larger ground planes on other PCB layers; the copper in these ground planes will act as a heat sink for the CS4412A. The CRD4412A reference design demonstrates the optimum thermal pad and via configuration.

## 6. PARAMETER DEFINITIONS

## **Dynamic Range (DYR)**

The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified bandwidth, typically 20 Hz to 20 kHz. Dynamic Range is a signal-to-noise ratio measurement over the specified band width made with a -60 dBFS signal. 60 dB is then added to the resulting measurement to refer the measurement to full-scale. This technique ensures that the distortion components are below the noise level and do not effect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17-1991, and the Electronic Industries Association of Japan, EIAJ CP-307. Expressed in decibels.

#### **Total Harmonic Distortion + Noise (THD+N)**

The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified band width (typically 10 Hz to 20 kHz), including distortion components. Expressed in decibels. Measured at -1 and -20 dBFS as suggested in AES17-1991 Annex A.

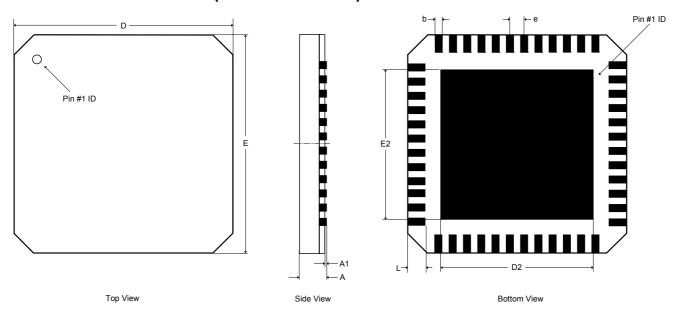

## 7. PACKAGE DIMENSIONS

# 48L QFN (9 $\times$ 9 MM BODY) PACKAGE DRAWING

|     | INCHES     |        |          |          | MILLIMETERS |      | NOTE |

|-----|------------|--------|----------|----------|-------------|------|------|

| DIM | MIN        | NOM    | MAX      | MIN      | NOM         | MAX  |      |

| Α   |            |        | 0.0354   |          |             | 0.90 | 1    |

| A1  | 0.0000     |        | 0.0020   | 0.00     |             | 0.05 | 1    |

| b   | 0.0118     | 0.0138 | 0.0157   | 0.30     | 0.35        | 0.40 | 1,2  |

| D   | 0.3543 BSC |        | 9.00 BSC |          |             | 1    |      |

| D2  | 0.2618     | 0.2677 | 0.2736   | 6.65     | 6.80        | 6.95 | 1    |

| Е   | 0.3543 BSC |        |          | 9.00 BSC |             | 1    |      |

| E2  | 0.2618     | 0.2677 | 0.2736   | 6.65     | 6.80        | 6.95 | 1    |

| е   | 0.0256 BSC |        |          | 0.65 BSC |             | 1    |      |

| L   | 0.0177     | 0.0217 | 0.0276   | 0.45     | 0.55        | 0.70 | 1    |

JEDEC #: MO-220

Controlling Dimension is Millimeters.

Notes: 1. Dimensioning and tolerance per ASME Y4.5M - 1994.

2. Dimensioning lead width applies to the plated terminal and is measured between 0.20 mm and 0.25 mm from the terminal tip.

## 8. THERMAL CHARACTERISTICS

| Parameter                          | Symbol        | Min | Тур | Max | Units   |

|------------------------------------|---------------|-----|-----|-----|---------|

| Junction to Case Thermal Impedance | $\theta_{JC}$ | -   | 1   | -   | °C/Watt |

## 8.1 Thermal Flag

This device is designed to have the metal flag on the bottom of the device soldered directly to a metal plane on the PCB. To enhance the thermal dissipation capabilities of the system, this metal plane should be coupled with vias to a large metal plane on the backside (and inner ground layer, if applicable) of the PCB.

In either case, it is beneficial to use copper fill in any unused regions inside the PCB layout, especially those immediately surrounding the CS4412A. In addition to improving in electrical performance, this practice also aids in heat dissipation.

The heat dissipation capability required of the metal plane for a given output power can be calculated as follows:

$$\theta_{CA} = [(T_{J(MAX)} - T_A) / P_D] - \theta_{JC}$$

where,

$\theta_{CA}$  = Thermal resistance of the metal plane in °C/Watt

T<sub>J(MAX)</sub> = Maximum rated operating junction temperature in °C, equal to 150 °C

$T_A = Ambient temperature in °C$

$P_D$  = RMS power dissipation of the device, equal to 0.15\* $P_{RMS}$  (assuming 85% efficiency)

$\theta_{JC}$  = Junction-to-case thermal resistance of the device in °C/Watt

## 9. ORDERING INFORMATION

| Product  | Description                                | Package | Pb-Free | Grade      | Temp Range    | Container        | Order#           |

|----------|--------------------------------------------|---------|---------|------------|---------------|------------------|------------------|

|          | 30 W Quad Half-Bridge                      |         |         |            |               | Rail             | CS4412A-CNZ      |

| CS4412A  | Digital Amplifier Power Stage              | 48-QFN  | Yes     | Commercial | -10° to +70°C | Tape and<br>Reel | CS4412A-<br>CNZR |

| CRD4412A | 1 x 30 W Reference Design<br>Daughter Card | -       | -       | -          | -             | -                | CRD4412A         |

| CRD4525  | 2 x 15 W Reference Design<br>Main Board    | -       | -       | -          | -             | -                | CRD4525          |

#### 10.REVISION HISTORY

| Release | Changes         |

|---------|-----------------|

| A1      | Initial Release |

#### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative. To find one nearest you, go to www.cirrus.com.

#### **IMPORTANT NOTICE**

"Advance" product information describes products that are in development and subject to development changes. Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, and Popguard are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.