WHITE ELECTRONIC DESIGNS \_\_\_\_\_ WME128K8-XXX

## 128Kx8 CMOS MONOLITHIC EEPROM, SMD 5962-96796

FIG. 1

| PIN CONFIGURATION<br>32 DIP<br>32 CSOJ<br>TOP VIEW |    |           |  |  |  |

|----------------------------------------------------|----|-----------|--|--|--|

| NC 🗌                                               | 1  | 32 🗌 Vcc  |  |  |  |

| A16                                                | 2  | 31 🗌 WE   |  |  |  |

| A15 🗌                                              | 3  | 30 🗌 NC   |  |  |  |

| A12 🗌                                              | 4  | 29 🗌 A14  |  |  |  |

| A7 🗌                                               | 5  | 28 🗌 A13  |  |  |  |

| A6 🗌                                               | 6  | 27 🗌 A8   |  |  |  |

| A5 🗌                                               | 7  | 26 🗌 A9   |  |  |  |

| A4 🗌                                               | 8  | 25 🗌 A11  |  |  |  |

| A3 🗌                                               | 9  | 24 🗌 🔁    |  |  |  |

| A2 🗌                                               | 10 | 23 🗌 A10  |  |  |  |

| A1 🗌                                               | 11 | 22 🗌 CS   |  |  |  |

| A0 🗌                                               | 12 | 21 🔲 1/07 |  |  |  |

| I/O0 🗌                                             | 13 | 20 🗌 1/06 |  |  |  |

| I/O1 🗌                                             | 14 | 19 🗌 I/O5 |  |  |  |

| I/O2                                               | 15 | 18 🗌 1/04 |  |  |  |

| Vss 🗌                                              | 16 | 17 🗌 1/03 |  |  |  |

|                                                    |    |           |  |  |  |

#### **PIN DESCRIPTION**

| Address Inputs    |

|-------------------|

| Data Input/Output |

| Chip Select       |

| Output Enable     |

| Write Enable      |

| +5.0V Power       |

| Ground            |

|                   |

## **FEATURES**

- Read Access Times of 120, 140, 150, 200, 250, 300ns

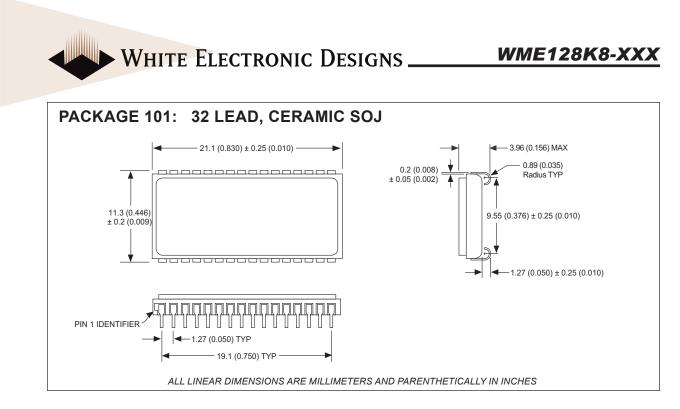

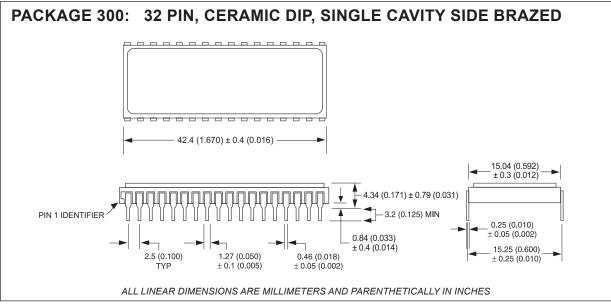

- JEDEC Approved Packages

- 32 pin, Hermetic Ceramic, 0.600" DIP (Package 300)

- 32 lead, Hermetic Ceramic, 0.400" SOJ (Package 101)

- Commercial, Industrial and Military Temperature Ranges

- MIL-STD-883 Compliant Devices Available

- Write Endurance 10,000 Cycles

- Data Retention at 25°C, 10 Years

- Low Power CMOS Operation

- Automatic Page Write Operation

- · Internal Address and Data Latches for 128 Bytes

- Internal Control Timer

- Page Write Cycle Time 10ms Max.

- Data Polling for End of Write Detection

- Hardware and Software Data Protection

- TTL Compatible Inputs and Outputs

## WME128K8-XXX

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter              | Symbol |                | Unit |

|------------------------|--------|----------------|------|

| Operating Temperature  | TA     | -55 to +125    | °C   |

| Storage Temperature    | Tstg   | -65 to +150    | °C   |

| Signal Voltage Any Pin | Vg     | -0.6 to + 6.25 | V    |

| Voltage on OE and A9   |        | -0.6 to +13.5  | V    |

#### NOTE:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter              | Symbol | Min  | Max     | Unit |

|------------------------|--------|------|---------|------|

| Supply Voltage         | Vcc    | 4.5  | 5.5     | V    |

| Input High Voltage     | VIH    | 2.0  | Vcc+0.3 | V    |

| Input Low Voltage      | VIL    | -0.3 | +0.8    | V    |

| Operating Temp. (Mil.) | TA     | -55  | +125    | °C   |

| Operating Temp. (Ind.) | TA     | -40  | +85     | °C   |

#### **TRUTH TABLE**

| cs | ŌĒ | WE | Mode        | Data I/O        |

|----|----|----|-------------|-----------------|

| Н  | Х  | Х  | Standby     | High Z          |

| L  | L  | Н  | Read        | Data Out        |

| L  | Н  | L  | Write       | Data In         |

| Х  | Н  | Х  | Out Disable | High Z/Data Out |

| Х  | Х  | Н  | Write       |                 |

| Х  | L  | x  | Inhibit     |                 |

# CAPACITANCE $(T_A = +25^{\circ}C)$

| Parameter          | Sym  | Condition           |     | Unit |

|--------------------|------|---------------------|-----|------|

|                    |      |                     | Max |      |

| Input Capacitance  | CIN  | VIN = 0V, f = 1MHz  | 20  | pF   |

| Output Capacitance | Соит | VI/O = 0V, f = 1MHz | 20  | pF   |

This parameter is guaranteed by design but not tested.

#### DC CHARACTERISTICS (Vcc = 5.0V, Vss = 0V, TA = -55°C to +125°C)

| Parameter              | Symbol | Conditions                                                        |     |       | Unit |

|------------------------|--------|-------------------------------------------------------------------|-----|-------|------|

|                        |        |                                                                   | Min | Max   |      |

| Input Leakage Current  | Li     | Vcc = 5.5, VIN = GND to Vcc                                       |     | 10    | μA   |

| Output Leakage Current | ILO    | $\overline{CS}$ = VIH, $\overline{OE}$ = VIH, VOUT = GND to VCC   |     | 10    | μA   |

| Dynamic Supply Current | Icc    | $\overline{CS}$ = VIL, $\overline{OE}$ = VIH, f = 5MHz, Vcc = 5.5 |     | 80    | mA   |

| Standby Current        | lsв    | $\overline{CS}$ = VIH, $\overline{OE}$ = VIH, f = 5MHz, Vcc = 5.5 |     | 0.625 | mA   |

| Output Low Voltage     | Vol    | IoL = 2.1mA, Vcc = 4.5V                                           |     | .45   | V    |

| Output High Voltage    | Vон    | Іон = -400µA, Vcc = 4.5V                                          | 2.4 |       | V    |

NOTE: DC test conditions: VIH = Vcc -0.3V, VIL = 0.3V

## READ

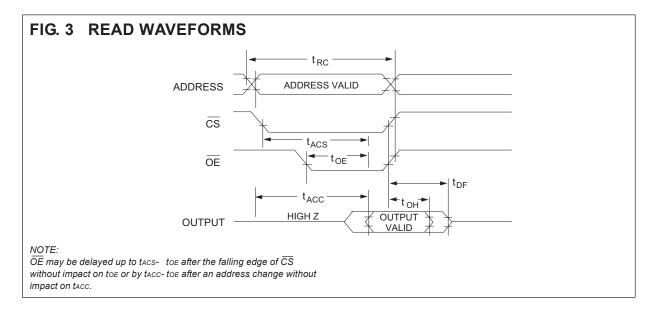

Figure 3 shows Read cycle waveforms. A read cycle begins with selection address, chip select and output enable. Chip select is accomplished by placing the  $\overline{CS}$  line low. Output enable is done by placing the  $\overline{OE}$  line low. The memory places the selected data byte on I/Oo through I/O7 after the access time. The output of the memory is placed in a high impedance state shortly after either the  $\overline{OE}$  line or  $\overline{CS}$  line is returned to a high level.

### AC READ CHARACTERISTICS (SEE FIGURE 3) (Vcc = 5.0V, Vss = 0V, Ta = -55°C to +125°C)

| Parameter                                                           | Symbol | -1  | 20  | -1  | 40  | -1  | 50  | -2  | 00  | -2  | 50  | -3  | 00  | Unit |

|---------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

|                                                                     |        | Min | Мах | Min | Мах | Min | Max | Min | Max | Min | Мах | Min | Мах |      |

| Read Cycle Time                                                     | trc    | 120 |     | 140 |     | 150 |     | 200 |     | 250 |     | 300 |     | ns   |

| Address Access Time                                                 | tacc   |     | 120 |     | 140 |     | 150 |     | 200 |     | 250 |     | 300 | ns   |

| Chip Select Access Time                                             | tacs   |     | 120 |     | 140 |     | 150 |     | 200 |     | 250 |     | 300 | ns   |

| Output Hold from Address Change, $\overline{OE}$ or $\overline{CS}$ | tон    | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

| Output Enable to Output Valid                                       | toe    |     | 50  |     | 55  |     | 55  |     | 55  |     | 85  |     | 85  | ns   |

| Chip Select or Output Enable to High Z Output                       | t DF   |     | 60  |     | 70  |     | 70  |     | 70  |     | 70  |     | 70  | ns   |

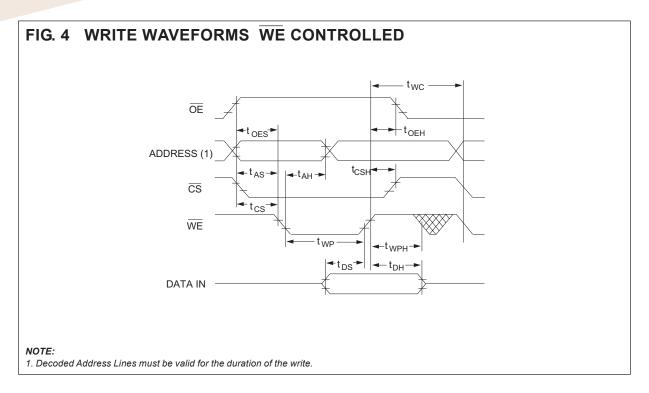

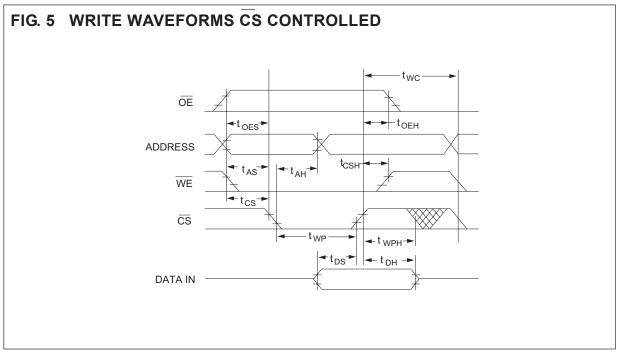

## WRITE

Write operations are initiated when both  $\overline{CS}$  and  $\overline{WE}$  are low and  $\overline{OE}$  is high. The EEPROM devices support both a  $\overline{CS}$  and  $\overline{WE}$  controlled write cycle. The address is latched by the falling edge of either  $\overline{CS}$  or  $\overline{WE}$ , whichever occurs last.

The data is latched internally by the rising edge of either  $\overline{CS}$  or  $\overline{WE}$ , whichever occurs first. A byte write operation will automatically continue to completion.

## WRITE CYCLE TIMING

Figures 4 and 5 show the write cycle timing relationships. A write cycle begins with address application, write enable and chip select. Chip select is accomplished by placing the  $\overline{\text{CS}}$  line low. Write enable consists of setting the  $\overline{\text{WE}}$  line low. The write cycle begins when the last of either  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  goes low.

The WE line transition from high to low also initiates an internal 150 $\mu$ sec delay time<u>r</u> to permit page mode operation. Each subsequent WE transition from high to low that occurs before the completion of the 150 $\mu$ sec time out will restart the timer from zero. The operation of the timer is the same as a retriggerable one-shot.

#### AC WRITE CHARACTERISTICS (Vcc = 5.0V, Vss = 0V, $Ta = -55^{\circ}C$ to $+125^{\circ}C$ )

| Parameter                                                | Symbol | 128 | 128Kx8 |    |  |

|----------------------------------------------------------|--------|-----|--------|----|--|

|                                                          |        | Min | Max    |    |  |

| Write Cycle Time, TYP = 6ms                              | twc    |     | 10     | ms |  |

| Address Set-up Time                                      | tas    | 10  |        | ns |  |

| Write Pulse Width ( $\overline{WE}$ or $\overline{CS}$ ) | twp    | 100 |        | ns |  |

| Chip Select Set-up Time                                  | tcs    | 0   |        | ns |  |

| Address Hold Time                                        | tан    | 100 |        | ns |  |

| Data Hold Time                                           | tон    | 10  |        | ns |  |

| Chip Select Hold Time                                    | tсн    | 0   |        | ns |  |

| Data Set-up Time                                         | tos    | 50  |        | ns |  |

| Output Enable Set-up Time                                | toes   | 0   |        | ns |  |

| Output Enable Hold Time                                  | tоен   | 0   |        | ns |  |

| Write Pulse Width High                                   | twpн   | 50  |        | ns |  |

## WME128K8-XXX

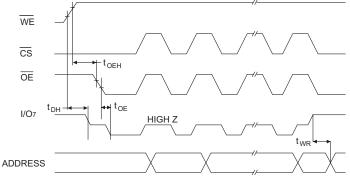

## DATA POLLING

The WME128K8-XXX offers a data polling feature which allows a faster method of writing to the device. Figure 6 shows the timing diagram for this function. During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data on I/O7. Once the write cycle has been completed, true data is valid on all outputs and the next cycle may begin. Data polling may begin at any time during the write cycle.

### DATA POLLING CHARACTERISTICS (Vcc = 5.0V, Vcc = 0V, TA = -55°C to +125°C)

| Parameter           | Symbol | Min | Max | Unit |

|---------------------|--------|-----|-----|------|

| Data Hold Time      | tон    | 10  |     | ns   |

| OE Hold Time        | tоен   | 10  |     | ns   |

| OE To Output Valid  | toe    |     | 55  | ns   |

| Write Recovery Time | twr    | 0   |     | ns   |

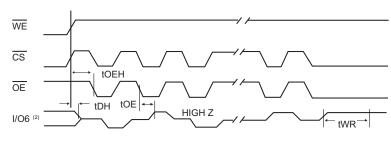

**TOGGLE BIT:** In addition to DATA Polling another method for determining the end of a write cycle is provided . During the write operation, successive attempts to read data from the device will result in I/O<sub>6</sub> toggling between one and zero. Once the write has completed, I/O<sub>6</sub> will stop toggling and valid data will be read. Reading the toggle bit may begin at any time during the write cycle. Toggle But Characteristics<sup>(1)</sup>

| Symbol | Parameter           | Min | Max | Units |

|--------|---------------------|-----|-----|-------|

| tон    | Data Hold Time      | 10  |     | ns    |

| tоен   | OE Hold Time        | 10  |     | ns    |

| toe    | OE to Output Delay  |     |     | ns    |

| toeнр  | OE High Pulse       | 150 |     | ns    |

| twr    | Write Recovery Time | 0   |     | ns    |

#### NOTE:

1. Toggling either  $\overline{OE}$  or  $\overline{CS}$  or both  $\overline{OE}$  and  $\overline{CS}$  will operate toggle bit.

3. Any address location may be used but the address should not vary.

<sup>2.</sup> Beginning and ending state of I/O6 will vary

## PAGE WRITE OPERATION

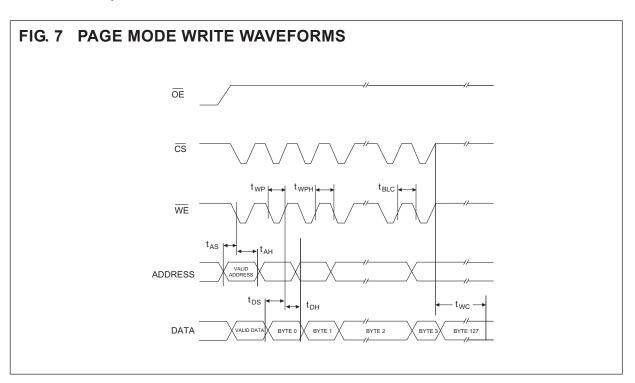

The WME128K8-XXX has a page write operation that allows one to 128 bytes of data to be written into the device and consecutively loads during the internal programming period. Successive bytes may be loaded in the same manner after the first data byte has been loaded. An internal timer begins a time out operation at each write cycle. If another write cycle is completed within 150 $\mu$ s or less, a new time out period begins. Each write cycle restarts the delay period. The write cycles can be continued as long as the interval is less than the time out period.

The usual procedure is to increment the least significant address lines from A0 through A6 at each write cycle. In this manner a page of up to 128 bytes can be loaded in to the EEPROM in a burst mode before beginning the relatively long interval programming cycle.

After the 150µs time out is completed, the EEPROM begins an internal write cycle. During this cycle the entire page of bytes will be written at the same time. The internal programming cycle is the same regardless of the number of bytes accessed.

## PAGE WRITE CHARACTERISTICS (Vcc = 5.0V, Vss = 0V, T<sub>A</sub> = -55°C to +125°C)

| Page Mode Write Characteristics | Symbol       |     |     | Unit |

|---------------------------------|--------------|-----|-----|------|

| Parameter                       |              | Min | Max |      |

| Write Cycle Time, TYP = 6ms     | twc          |     | 10  | ms   |

| Address Set-up Time             | tas          | 10  |     | ns   |

| Address Hold Time (1)           | tан          | 100 |     | ns   |

| Data Set-up Time                | tos          | 50  |     | ns   |

| Data Hold Time                  | toн          | 10  |     | ns   |

| Write Pulse Width               | twp          | 100 |     | ns   |

| Byte Load Cycle Time            | <b>t</b> BLC |     | 150 | μs   |

| Write Pulse Width High          | twpн         | 50  |     | ns   |

1. Page address must remain valid for duration of write cycle.

7

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com

WHITE ELECTRONIC DESIGNS \_\_\_\_\_\_

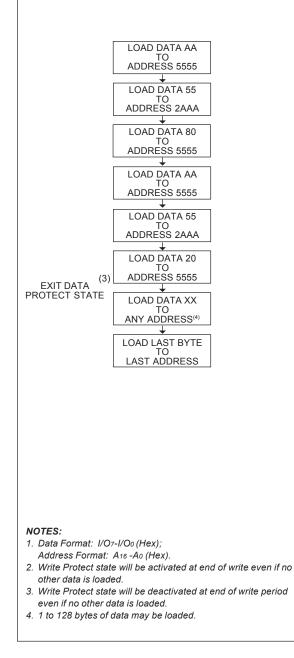

## FIG. 9 SOFTWARE BLOCK DATA PROTECTION DISABLE ALGORITHM

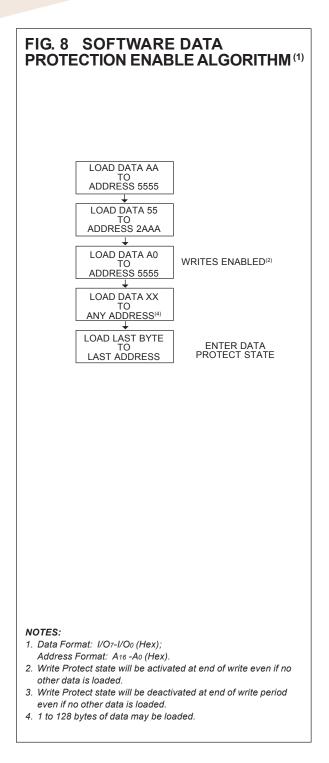

## SOFTWARE DATA PROTECTION

A software write protection feature may be enabled or disabled by the user. When shipped by White Microelectronics, the WME128K8-XXX has the feature disabled. Write access to the device is unrestricted.

To enable software write protection, the user writes three access code bytes to three special internal locations. Once write protection has been enabled, each write to the EEPROM must use the same three byte write sequence to permit writing. After setting software Data protection, any attempt to write to the device without the three-byte command sequence will start the internal write timers. No Data will be written to the device; however, for the duration of tWC. The write protection feature can be disabled by a six byte write sequence of specific data to specific locations. Power transitions will not reset the software write protection.

The software write protection guards against inadvertent writes during power transitions or unauthorized modification using a PROM programmer.

## HARDWARE DATA PROTECTION

These features protect against inadvertent writes to the WME128K8-XXX. These are included to improve reliability during normal operation:

a) VCC power on delay

As VCC climbs past 3.8V typical the device will wait 5msec typical before allowing write cycles.

b) VCC sense

While below 3.8V typical write cycles are inhibited.

c) Write inhibiting

Holding  $\overrightarrow{OE}$  low and either  $\overrightarrow{CS}$  or  $\overrightarrow{WE}$  high inhibits write cycles.

d) Noise filter

Pulses of <15ns (typ) on  $\overline{WE}$  or  $\overline{CS}$  will not initiate a write cycle.

# WHITE ELECTRONIC DESIGNS \_\_\_\_\_ WME128K8-XXX

| DEVICE TYPE                | SPEED | PACKAGE          | SMD NO.          |

|----------------------------|-------|------------------|------------------|

| 128K x 8 EEPROM Monolithic | 300ns | 32 pin DIP (C)   | 5962-96796 01HYX |

| 128K x 8 EEPROM Monolithic | 250ns | 32 pin DIP (C)   | 5962-96796 02HYX |

| 128K x 8 EEPROM Monolithic | 200ns | 32 pin DIP (C)   | 5962-96796 03HYX |

| 128K x 8 EEPROM Monolithic | 150ns | 32 pin DIP (C)   | 5962-96796 04HYX |

| 128K x 8 EEPROM Monolithic | 140ns | 32 pin DIP (C)   | 5962-96796 05HYX |

| 128K x 8 EEPROM Monolithic | 120ns | 32 pin DIP (C)   | 5962-96796 06HYX |

| 128K x 8 EEPROM Monolithic | 300ns | 32 lead SOJ (DE) | 5962-96796 01HXX |

| 128K x 8 EEPROM Monolithic | 250ns | 32 lead SOJ (DE) | 5962-96796 02HXX |

| 128K x 8 EEPROM Monolithic | 200ns | 32 lead SOJ (DE) | 5962-96796 03HXX |

| 128K x 8 EEPROM Monolithic | 150ns | 32 lead SOJ (DE) | 5962-96796 04HXX |

| 128K x 8 EEPROM Monolithic | 140ns | 32 lead SOJ (DE) | 5962-96796 05HXX |

| 128K x 8 EEPROM Monolithic | 120ns | 32 lead SOJ (DE) | 5962-96796 06HXX |