March 1997

## **High-Reliability CMOS 8-Bit Microprocessor**

#### Features

- For Use In Aerospace, Military, and Critical Industrial Equipment

- Minimum Instruction Fetch-Execute Time of 4.5μs (Maximum Clock Frequency of 3.6MHz) at V<sub>DD</sub> = 5V, T<sub>A</sub> = +25°C

- Operation Over the Full Military

Temperature Range . . . . . . . -55°C to +125°C

- Any Combination of Standard RAM and ROM Up to 65,536 Bytes

- 8-Bit Parallel Organization With Bidirectional Data Bus and Multiplexed Address Bus

- 16 x 16 Matrix of Registers for Use as Multiple Program Counters, Data Pointers, or Data Registers

- On-Chip DMA, Interrupt, and Flag Inputs

## Ordering Information

| PACKAGE | TEMP. RANGE<br>(°C) | 5V - 3.2MHz | PKG<br>NO. |

|---------|---------------------|-------------|------------|

| SBDIP   | -55 to 125          | CDP1802ACD3 | D40.6      |

## Description

The CDP1802A/3 High-Reliability LSI CMOS 8-bit register oriented Central-Processing Unit (CPU) is designed for use as a general purpose computing or control element in a wide range of stored-program systems or products.

The CDP1802A/3 includes all of the circuits required for fetching, interpreting, and executing instructions which have been stored in standard types of memories. Extensive input/output (I/O) control features are also provided to facilitate system design.

The 1800 Series Architecture is designed with emphasis on the total microcomputer system as an integral entity so that systems having maximum flexibility and minimum cost can be realized. The 1800 Series CPU also provides a synchronous interface to memories and external controllers for I/O devices, and minimizes the cost of interface controllers. Further, the I/O interface is capable of supporting devices operating in polled, interrupt-driven, or direct memory-access modes.

The CDP1802AC/3 is functionally identical to its predecessor, the CDP1802. The "A" version includes some performance enhancements and can be used as a direct replacement in systems using the CDP1802.

This type is supplied in 40 lead dual-in-line sidebrazed ceramic packages (D suffix).

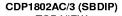

#### **Pinout**

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. Copyright © Harris Corporation 1997

File Number 1441.2

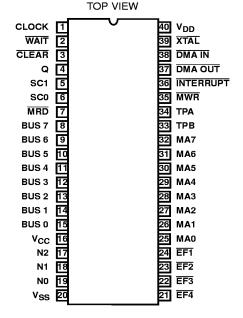

FIGURE 1. TYPICAL CDP1802A/3 SMALL MICROPROCESSOR SYSTEM

#### **Absolute Maximum Ratings**

DC Supply Voltage Range, ( $V_{DD}$ ) (All Voltages Referenced to  $V_{SS}$  Terminal) CDP1802AC/3 .....-0.5V to +7V Input Voltage Range, All Inputs ....-0.5V to  $V_{DD}$  +0.5V DC Input Current, any One Input .......±10mA

#### **Thermal Information**

| Thermal Resistance (Typical)                                      | $\theta_{JA}$ (oC/W) | $\theta_{JC}$ (oC/W) |

|-------------------------------------------------------------------|----------------------|----------------------|

| SBDIP Package                                                     | 55                   | 15                   |

| Device Dissipation Per Output Transistor                          |                      |                      |

| T <sub>A</sub> = Full Package Temperature Range                   |                      | 100mW                |

| Operating Temperature Range (T <sub>A</sub> )                     |                      |                      |

| Package Type D                                                    |                      |                      |

| Storage Temperature Range (T <sub>STG</sub> )                     | 65 <sup>0</sup>      | C to +150°C          |

| Lead Temperature (During Soldering)                               |                      |                      |

| At distance $1/16 \pm 1/32 \text{ In.} (1.59 \pm 0.79 \text{ m})$ | ım)                  |                      |

| from case for 10s max                                             |                      | +265 <sup>0</sup> C  |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

**Recommended Operating Conditions** T<sub>A</sub> = Full Package Temperature Range. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges

| PARAMETER                             | MIN             | MAX               | UNITS |

|---------------------------------------|-----------------|-------------------|-------|

| DC Operating Voltage Range            | 4               | 6.5               | V     |

| Input Voltage Range                   | V <sub>SS</sub> | $V_{\mathrm{DD}}$ | V     |

| Maximum Clock Input Rise or Fall Time | =               | 1                 | μs    |

## **Performance Specifications**

| PARAMETER                                                                                    | V <sub>DD</sub> (V) | -55°C TO +25°C | +125°C | UNITS    |

|----------------------------------------------------------------------------------------------|---------------------|----------------|--------|----------|

| Minimum Instruction Time (Note 1)                                                            | 5                   | 4.5            | 5.9    | μs       |

| Maximum DMA Transfer Rate                                                                    | 5                   | 450            | 340    | Kbytes/s |

| Maximum Clock Input Frequency,<br>Load Capacitance (C <sub>L</sub> ) = 50pF, f <sub>CL</sub> | 5                   | DC-3.6         | DC-2.7 | MHz      |

#### NOTE:

#### Static Electrical Specifications All Limits are 100% Tested

|                                                                      | CONDITIONS              |                      |                                      | -55 <sup>0</sup> C, | +25°C | +125 | o°C   |       |

|----------------------------------------------------------------------|-------------------------|----------------------|--------------------------------------|---------------------|-------|------|-------|-------|

| PARAMETER                                                            | V <sub>OUT</sub><br>(V) | V <sub>IN,</sub> (V) | V <sub>CC,</sub> V <sub>DD</sub> (V) | MIN                 | МАХ   | MIN  | MAX   | UNITS |

| Quiescent Device Current, I <sub>DD</sub>                            | -                       | -                    | 5                                    | -                   | 100   | -    | 250   | μΑ    |

| Output Low Drive (Sink) Current (Except XTAL), I <sub>OL</sub>       | 0.4                     | 0, 5                 | 5                                    | 1.20                | 1     | 0.90 | 1     | mA    |

| XTAL                                                                 | 0.4                     | 5                    | 5                                    | 185                 | -     | 140  | -     | μΑ    |

| Output High Drive (Source)<br>Current (Except XTAL), I <sub>OH</sub> | 4.6                     | 0, 5                 | 5                                    | 1                   | -0.30 | 1    | -0.20 | mA    |

| XTAL                                                                 | 4.6                     | 0                    | 5                                    | -                   | -135  | -    | -100  | μΑ    |

| Output Voltage Low-Level, V <sub>OL</sub>                            | -                       | 0, 5                 | 5                                    | -                   | 0.1   | -    | 0.2   | ٧     |

| Output Voltage High-Level, V <sub>OH</sub>                           | -                       | 0, 5                 | 5                                    | 4.9                 | -     | 4.8  | -     | ٧     |

<sup>1.</sup> Equals 2 machine cycles - one Fetch and one Execute operation for all instructions except Long Branch and Long Skip, which require 3 machine cycles - one Fetch and two Execute operations.

## Static Electrical Specifications All Limits are 100% Tested (Continued)

|                                                         | CONDITIONS              |                      |                                      | CONDITIONS |     | -55 <sup>o</sup> C, | +25°C | +125  | °C |  |

|---------------------------------------------------------|-------------------------|----------------------|--------------------------------------|------------|-----|---------------------|-------|-------|----|--|

| PARAMETER                                               | V <sub>OUT</sub><br>(V) | V <sub>IN,</sub> (V) | V <sub>CC,</sub> V <sub>DD</sub> (V) | MIN        | МАХ | MIN                 | мах   | UNITS |    |  |

| Input Low Voltage, V <sub>IL</sub>                      | 0.5, 4.5                | -                    | 5                                    | -          | 1.5 | -                   | 1.5   | V     |    |  |

| Input High Voltage, V <sub>IH</sub>                     | 0.5, 4.5                | -                    | 5                                    | 3.5        | -   | 3.5                 | -     | V     |    |  |

| Input Leakage Current, I <sub>IN</sub>                  | Any<br>Input            | 0, 5                 | 5                                    | -          | ±1  | -                   | ±5    | μА    |    |  |

| Three-State Output Leakage<br>Current, I <sub>OUT</sub> | 0, 5                    | 0, 5                 | 5                                    | -          | ±1  | -                   | ±5    | μА    |    |  |

#### NOTE:

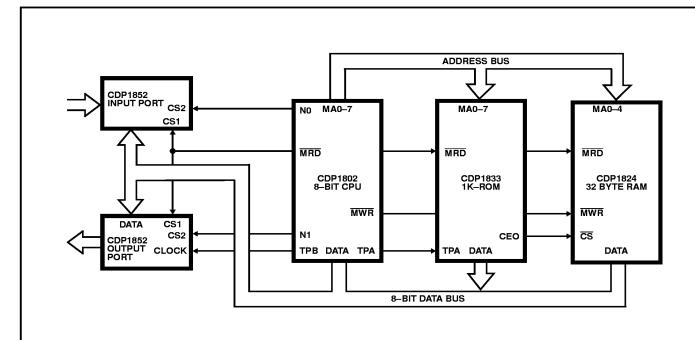

## **Timing Specifications** As a Function of T (T = 1/fCLOCK), $C_L = 50 pF$

|                                                                     |                     | LIMITS (NOTE 3) |        |       |

|---------------------------------------------------------------------|---------------------|-----------------|--------|-------|

| PARAMETER                                                           | V <sub>DD</sub> (V) | -55°C, +25°C    | +125°C | UNITS |

| High-Order Memory-Address Byte Setup to TPA — Time, t <sub>SU</sub> | 5                   | 2T-450          | 2T-580 | ns    |

| High-Order Memory-Address Byte Hold After TPA Time, t <sub>H</sub>  | 5                   | T/2 +0          | T/2 +0 | ns    |

| Low-Order Memory-Address Byte Hold After WR Time, t <sub>H</sub>    | 5                   | T-30            | T-40   | ns    |

| CPU Data to Bus Hold After WR Time, t <sub>H</sub>                  | 5                   | T-170           | T-250  | ns    |

| Required Memory Access Time Address to Data, t <sub>ACC</sub>       | 5                   | 5T-300          | 5T-400 | ns    |

#### NOTE:

## Implicit Specifications (Note 4) $T_A = -55^{\circ}C$ to $+25^{\circ}C$

| PARAMETER                                                                   |          | SYMBOL          | V <sub>DD</sub> (V) | TYPICAL<br>VALUES | UNITS |

|-----------------------------------------------------------------------------|----------|-----------------|---------------------|-------------------|-------|

| Typical Total Power Dissipation Idle "00" at M(0000), C <sub>L</sub> = 50pF | f = 2MHz | -               | 5                   | 4                 | mW    |

| Effective Input Capacitance any Input                                       | -        | C <sub>IN</sub> | -                   | 5                 | pF    |

| Effective Three-State Terminal Capacitance Data Bus                         | -        |                 | -                   | 7.5               | pF    |

| Minimum Data Retention Voltage                                              | -        | V <sub>DR</sub> | -                   | 2.4               | V     |

| Data Retention Current                                                      | -        | I <sub>DR</sub> | 2.4                 | 10                | μА    |

#### NOTE:

<sup>2. 5</sup>V level characteristics apply to Part No. CDP1802AC/3, and 5V and 10V level characteristics apply to part No. CDP1802A/3.

<sup>3.</sup> These limits are not directly tested.

$<sup>{\</sup>bf 4. \ \, These \ \, specifications \ \, are \ \, not \ \, tested. \ \, Typical \ \, values \ \, are \ \, provided \ \, for \ \, guidance \ \, only.}$

# $\textbf{Dynamic Electrical Specifications} \quad \text{C}_{L} = 50 \text{pF, Timing Measurement at } 0.5 \text{ V}_{DD} \text{ Point}$

|                                                                                |                     | -55°C TO +25°C |     | +125 | °C  |       |

|--------------------------------------------------------------------------------|---------------------|----------------|-----|------|-----|-------|

| PARAMETERS                                                                     | V <sub>DD</sub> (V) | MIN            | МАХ | MIN  | MAX | UNITS |

| Progagation Delay Times, t <sub>PLH</sub> , t <sub>PHL</sub> Clock to TPA, TPB | 5                   | -              | 275 | -    | 370 | ns    |

| Clock-to-Memory High Address Byte, t <sub>PLH</sub> , t <sub>PHL</sub>         | 5                   | -              | 725 | -    | 950 | ns    |

| Clock-to-Memory Low Address Byte Valid, t <sub>PLH</sub> , t <sub>PHL</sub>    | 5                   | -              | 340 | -    | 425 | ns    |

| Clock to MRD, t <sub>PLH</sub> , t <sub>PHL</sub>                              | 5                   | -              | 340 | -    | 425 | ns    |

| Clock to MWR, t <sub>PLH</sub> , t <sub>PHL</sub>                              | 5                   | -              | 275 | -    | 370 | ns    |

| Clock to (CPU DATA to BUS) Valid, t <sub>PLH</sub> , t <sub>PHL</sub>          | 5                   | -              | 430 | -    | 550 | ns    |

| Clock to State Code, t <sub>PLH</sub> , t <sub>PHL</sub>                       | 5                   | -              | 440 | -    | 550 | ns    |

| Clock to Q, t <sub>PLH</sub> , t <sub>PHL</sub>                                | 5                   | -              | 375 | -    | 475 | ns    |

| Clock to N (0 - 2), t <sub>PLH</sub> , t <sub>PHL</sub>                        | 5                   | -              | 400 | -    | 525 | ns    |

| Interface Timing Requirements (Note 5)  Data Bus Input Setup, t <sub>SU</sub>  | 5                   | 10             | -   | 10   | -   | ns    |

| Data Bus Input Hold, t <sub>H</sub>                                            | 5                   | 175            | -   | 230  | -   | ns    |

| DMA Setup, t <sub>SU</sub>                                                     | 5                   | 10             | -   | 10   | -   | ns    |

| DMA Hold, t <sub>H</sub>                                                       | 5                   | 200            | -   | 270  | -   | ns    |

| Interrupt Setup, t <sub>SU</sub>                                               | 5                   | 10             | -   | 10   | -   | ns    |

| Interrupt Hold, t <sub>H</sub>                                                 | 5                   | 175            | -   | 230  | -   | ns    |

| WAIT Setup, t <sub>SU</sub>                                                    | 5                   | 30             | -   | 30   | -   | ns    |

| EF1-4 Setup, t <sub>SU</sub>                                                   | 5                   | 20             | -   | 20   | -   | ns    |

| EF1-4 Hold, t <sub>H</sub>                                                     | 5                   | 100            | -   | 135  | -   | ns    |

| Required Pulse Width Times  CLEAR Pulse Width, t <sub>WL</sub>                 | 5                   | 150            | -   | 200  | -   | ns    |

| CLOCK Pulse Width, t <sub>WL</sub>                                             | 5                   | 140            | -   | 185  | -   | ns    |

#### NOTE:

5. Minimum input setup and hold times required by Part CDP1802AC/3.

## Performance Curves

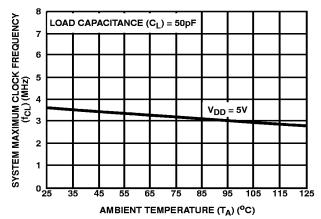

FIGURE 3. TYPICAL MAXIMUM CLOCK FREQUENCY AS A FUNCTION OF TEMPERATURE

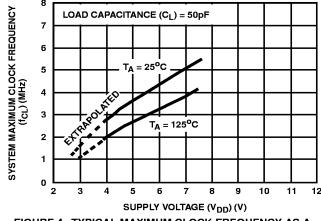

FIGURE 4. TYPICAL MAXIMUM CLOCK FREQUENCY AS A FUNCTION OF SUPPLY VOLTAGE

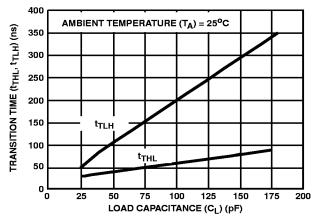

FIGURE 5. TYPICAL TRANSITION TIME vs LOAD CAPACITANCE

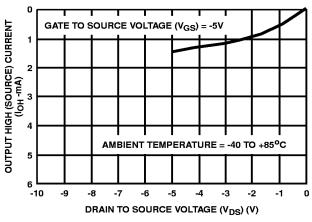

FIGURE 6. MINIMUM OUTPUT HIGH (SOURCE) CURRENT CHARACTERISTICS

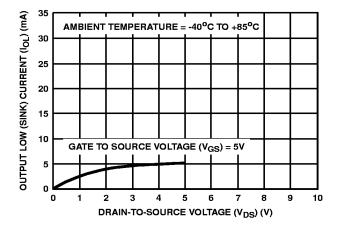

FIGURE 7. MINIMUM OUTPUT LOW (SINK) CURRENT CHARACTERISTICS

NOTES:

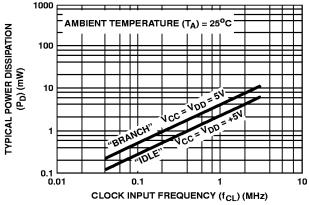

- 9. Idle = "00" at M (0000)

- 10. Branch = "3707" at M (8107)

FIGURE 8. TYPICAL POWER DISSIPATION AS A FUNCTION OF CLOCK FREQUENCY FOR BRANCH INSTRUCTION AND IDLE INSTRUCTION

## Performance Curves (Continued)

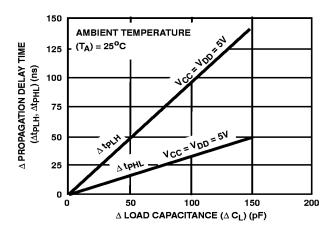

NOTE: Any output except  $\overline{\text{XTAL}}.$

FIGURE 9. TYPICAL CHANGE IN PROPAGATION DELAY AS A FUNCTION OF A CHANGE IN LOAD CAPACITANCE

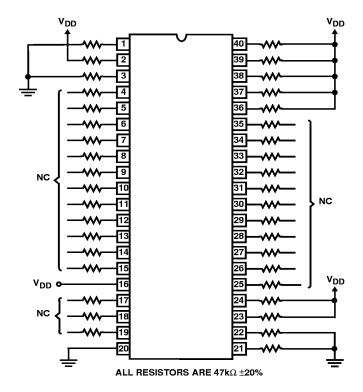

## **Burn-In Circuit**

| ТҮРЕ      | V <sub>DD</sub> | TEMPERATURE         | TIME      |

|-----------|-----------------|---------------------|-----------|

| CDP1802AC | 7V              | +125 <sup>0</sup> C | 160 Hours |

FIGURE 10. BIAS/STATIC BURN-IN CIRCUIT