# 8/16-bit Data Bus Flash Memory Card

Connector Type

Two-piece 68-pin

MF82M1-G7DATXX MF84M1-G7DATXX MF88M1-G7DATXX MF810M-G7DATXX MF816M-G7DATXX MF820M-G7DATXX

#### DESCRIPTION

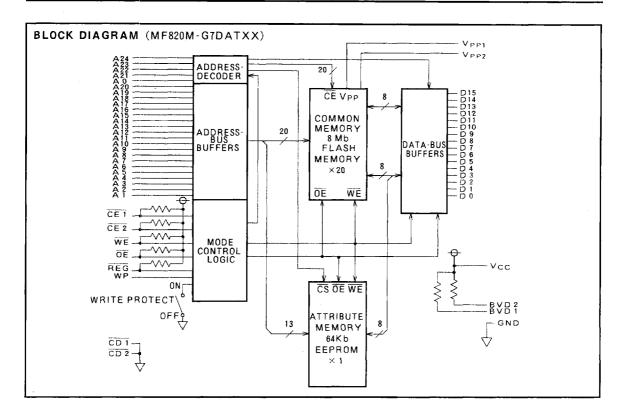

The MF8XXX-G7DATXXX is a flash memory card which uses eight-megabit flash electrically erasable and programmable read only memory IC's as common memory and a 64-kilobit electrically erasable and programmable read only memory as attribute memory.

#### **FEATURES**

- ■68 pin JEIDA/PCMCIA

- 8 /16 controllable data bus width

- Buffered interface

- TTL interface level

- Program/erase operation by software command control

- Program/erase voltage 12V (common memory)

- 100, 000 program/erase cycles

- Write protect switch

## APPLICATIONS

- Notebook computers

- Printers

- Industrial machines

## PRODUCT LIST

| Type name         | Memory capacity                                                                                                   | Data bus<br>width (bits) | Access time<br>(ns) | Number of pins | Outline<br>drawing |

|-------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------|----------------|--------------------|

| MF82M1-G7DATXX    | 2 M B                                                                                                             |                          |                     |                |                    |

| MF84M1-G7DATXX    | 4MB                                                                                                               |                          |                     | l              |                    |

| MF88M1-G7DATXX ★★ | Capacity           TXX         2MB           TXX         4MB           TXX         ★★           10MB         16MB | 0.440                    | 200                 | 68             | 68P-002            |

| MF810M-G7DATXX ★★ | 10MB                                                                                                              | 8 /16                    | 200                 |                | 081-002            |

| MF816M-G7DATXX ** | 16MB                                                                                                              |                          |                     |                |                    |

| MF820M-G7DATXX ★★ | 20MB                                                                                                              |                          |                     |                |                    |

★★: Under development

## PIN ASSIGNMENT

| Pin<br>Nα | Symbol | Function                     | Pin<br>Na | Symbol | Function                                     |

|-----------|--------|------------------------------|-----------|--------|----------------------------------------------|

| 1         | GND    | Ground                       | 35        | GND    | Ground                                       |

| 2         | D 3    | 1                            | 36        | CD 1   | Card detect 1                                |

| 3         | D 4    |                              | 37        | D11    | )                                            |

| 4         | D 5    | Data I/0                     | 38        | D12    |                                              |

| 5         | D 6    |                              | 39        | D13    | Data I/O                                     |

| 6         | D7     |                              | 40        | D14    |                                              |

| 7         | CE I   | Card enable 1                | 41        | D15    | ]                                            |

| 8         | A10    | Address input                | 42        | CE 2   | Card enable 2                                |

| 9         | ŌĒ     | Output enable                | 43        | NC     |                                              |

| 10        | A11    | <u> </u>                     | 44        | NC     | No connection                                |

| 11        | A 9    |                              | 45        | NC     |                                              |

| 12        | A 8    | Address input                | 46        | A17    | }                                            |

| 13        | A13    |                              | 47        | A18    |                                              |

| 14        | A14    | J                            | 48        | A19    | Address input                                |

| 15        | WE     | Write enable                 | 49        | A20    |                                              |

| 16        | NC     | No connection                | 50        | A21    | A21 (NC for ≤ 2 MB types)                    |

| 17        | Vcc    | Power supply voltage         | 51        | Vcc    | Power supply voltage                         |

| 18        | VPP1   | Programming supply voltage 1 | 52        | VPP 2  | Programming supply voltage 2                 |

| 19        | A16    | l l                          | 53        | A22    | A22 (NC for $\leq$ 4 MB types) Address input |

| 20        | A15    |                              | 54        | A23    | A23 (NC for ≤ 8 MB types) Address input      |

| 21        | A12    |                              | 55        | A24    |                                              |

| 22        | A 7    |                              | 56        | NC     | 1                                            |

| 23        | A 6    |                              | 57        | NC     |                                              |

| 24        | A 5    | Address input                | 58        | NC     | No connection                                |

| 25        | A 4    |                              | 59        | NC     |                                              |

| 26        | A 3    |                              | 60        | NC     | )                                            |

| 27        | A 2    |                              | 61        | REG    | Attribute memory select                      |

| 28        | A 1    |                              | 62        | BVD2   | Battery voltage detect 2                     |

| 29        | A 0    | ] )                          | 63        | BVD1   | Battery voltage detect 1                     |

| 30        | D 0    |                              | 64        | D 8    |                                              |

| 31        | D 1    | Data I/O                     | 65        | D 9    | Data I/0                                     |

| 32        | D 2    | []                           | 66        | D10    | J                                            |

| 33        | WP     | Write protect                | 67        | CD 2   | Card detect 2                                |

| 34        | GND    | Ground                       | 68        | GND    | Ground                                       |

## **FUNCTIONAL DESCRIPTION**

The operating mode of the card is determined by five active low control signals (REG, CE1, CE2, OE, WE), three supply voltages (VCC, VPP1, VPP2) and control registers located in each memory IC.

## Common memory function

When the  $\overline{REG}$  signal is set to a high level common memory is selected.

#### Read only mode

When the voltages applied to both Vpp1 and Vpp2 are less than the voltage applied to VCC (i. e. Vpp = 0 Vto V<sub>CC</sub>), the control registers of each memory IC are set to read only mode.

Operation of the card then depends on the four possible combinations of CE1 and CE2 (note WE should be set to a high level when the device is in read only mode except during combination (4) where it's condition is unimportant):

(1) If CE1 is set to a low level and CE2 is set to a high level, the card will work as an eight bit data

bus width card. Data can be accessed via the lower half of the data bus (D0 to D7).

- (2) If both  $\overline{CE1}$  and  $\overline{CE2}$  are set to a low level, data will be accessible via the full sixteen bit data bus width of the card. In this mode LSB of address bus (A0) is ignored.

- (3) If CE1 is set to a high level and CE2 is set to a low level the odd bytes (only) can be accessed through upper half of the data bus (D8 to D15). This mode is useful when handling the odd (upper) bytes in a sixteen bit interface system. Note that A0 is also ignored in this operating condition.

- (4) If CE1 and CE2 are set to a high level, the card will be in standby mode where it consumes low power. The data bus is kept high impedance.

When  $\overline{OE}$  is set to a low level data can be read from the card, depending on the address applied and the setting of  $\overline{CE1}$  and  $\overline{CE2}$  as mentioned above, except under combination (4).

When  $\overline{OE}$  is set to a high level and  $\overline{WE}$  is set to a high level the card is in an output disable mode and the data bus will be in a high impedance state regardless of the condition of  $\overline{CE1}$  and  $\overline{CE2}$ .

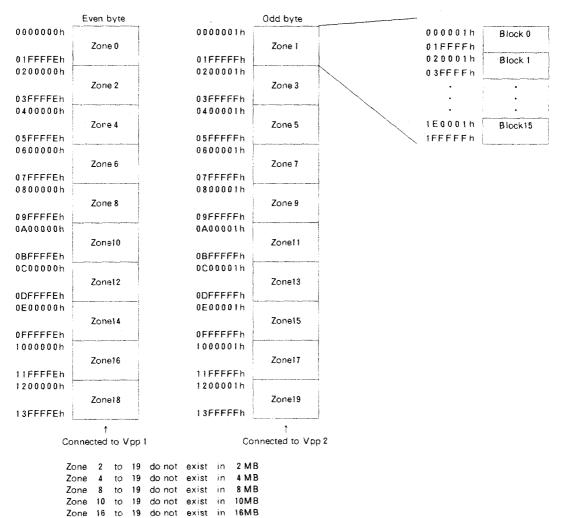

#### Read/write mode

When a programming voltage (VPPH) is applied to either or both of VPP1 and VPP2, read/write mode is enabled for the corresponding banks of memory IC's inside the card. VPP1 enables the Even Byte bank and VPP2 enables the Odd Byte bank.

By using the 4 combinations of CE1 and CE2 as described under Read only mode above the appropriate Data Out and Command/Data In bus selection can be made

If  $\overline{OE}$  is set to a high level and  $\overline{WE}$  set to a low level, the control register will latch command data applied at the rising edge of the  $\overline{WE}$  signal. Note that more than one bus cycle may be required to latch the command and/or the related data—please refer to the Command Definition table

If  $\overline{OE}$  is set to a low level and  $\overline{WE}$  is set to a high level the card data can be read from the card depending on the condition of the control register.

After latching the command data, the card will go into programming, erasure or other operation mode. For details plese refer to the Command Definition table, each individual command's definition and the programming and erasure algorithms.

#### Attribute memory

When the REG signal is set to a low level attribute memory is selected.

The card includes a byte wide attribute memory consisting of 8K bytes of EEPROM located at the even addresses when the card is in the 8 bit operating mode. It is located at sequential addresses on the lower half of the data bus when the card is in 16 bit operating mode i.e. A0 is ignored.

To access the attribute memory, first set CE1 and CE2. Set CE1 to low level and CE2 to high level for 8 bit mode or CE1 and CE2 to low level for 16 bit mode. Then select the required address. Note please take care that in 8 bit mode A0 must be set low for attribute memory access i.e. an even address is applied. In 16

bit mode it is not important whether A0 is high or low. Data can then be read by setting  $\overline{OE}$  to a low level with  $\overline{WE}$  set to a high level.

Writing to the attribute memory can be achieved in one of two ways, in byte mode or in page mode. The page mode write is a function which allows up to 32 bytes of data to be written in a single cycle. A page is defined as a block of 32 even bytes selected by addresses A6 through A13.

To write to attribute memory set  $\overline{OE}$  to high level and  $\overline{WE}$  to low level. The data to be written will be latched at the rising edge of  $\overline{WE}$ . Then, unless  $\overline{WE}$  changes back from high level to low level within 30  $\mu$ s an automatic erase/program operation starts which will complete within 10ms.

If  $\overline{\text{WE}}$  makes a transition back from high to low level within 30  $\mu s$  of the first data being latched then further bytes from a page of up to 32 bytes can be latched with further  $\overline{\text{WE}}$  low to high transitions. The latching operation is repeated until all bytes are loaded at which point holding  $\overline{\text{WE}}$  high for greater than 30 $\mu s$  will initiate execution of a page erase/program operation which will complete within 10ms.

During page write data loading operations all data must be addressed within one 32 byte page i.e. the page address which is selected by A6 through A13 and must remain constant throughout the data load. Please also remember that for attribute memory A0 is not applicable and it should be set to low, even addressing only, in 8 bit mode or ignored for 16 bit mode.

#### Write protect mode

The card has a write protect switch on the opposite edge to the connector edge. When it is switched on, the card will be placed into a write protect mode, where data can be read from the card but it cannot be written to it. The WP output pin is set to a high level when the card is in write protect mode and  $V_{\rm CC}$  is applied. When the card is not in write protect mode the WP output pin is set to a low level when  $V_{\rm CC}$  is applied. By reading the state of the WP output the host system can easily check whether the card is in write protect mode or not.

## FUNCTION TABLE (COMMON MEMORY) READ ONLY MODE

| Mode            | REG | CE 2 | CEI | ŌĒ | WE | Α0 | VPP 2 | Vpp 1 | I/O<br>(D15-D8)   | 1/0<br>(D7-D0)     |

|-----------------|-----|------|-----|----|----|----|-------|-------|-------------------|--------------------|

| Standby         | Н   | Н    | Н   | Х  | Х  | X  | VPPL  | VPPL  | High-Z            | High-Z             |

| Read A (16-bit) | Н   | L    | L   | L  | Н  | ×  | VPPL  | VPPL  | Odd byte data out | Even byte data out |

| Read B (8-bit)  | Н   | Н    | L   | L  | Н  | L  | VPPL  | VPPL  | High-Z            | Even byte data out |

| nead B (6 -DII) | Н   | Н    | L   | L  | Н  | Н  | 'VPPL | VPPL  | High-Z            | Odd byte deta out  |

| Read C (8-bit)  | Н   | L    | н   | L  | Н  | ×  | VPPL  | VPPL  | Odd byte data out | High-Z             |

| Output disable  | Н   | Х    | X   | Н  | Н  | X  | VPPL  | VPPL  | High-Z            | High-Z             |

Note1: H=VIH, L=VIL, X=VIH or VIL

## FUNCTION TABLE (COMMON MEMORY) READ/WRITE MODE

| Mode             | REG | CE 2 | CE 1 | ŌĒ | WE | Α0 | Vpp2 | Vpp 1 | 1/0<br>(D15-D8)                | 1/0<br>(D7-D0)                 |

|------------------|-----|------|------|----|----|----|------|-------|--------------------------------|--------------------------------|

| Ctanally.        | Н   | Н    | Н    | Х  | X  | Х  | VPPX | VPPH  | High-Z                         | High-Z                         |

| Standby          | Н   | Н    | Н    | Х  | Х  | Х  | VppH | VPPX  | High-Z                         | High-Z                         |

| Read A (16-bit)  | Н   | L    | L    | L  | Н  | Х  | VPPH | VppH  | Odd byte data out              | Even byte data out             |

| D D (0 bit)      | Н   | Н    | L    | L  | Н  | L  | VPPX | VppH  | High-Z                         | Even byte data out             |

| Read B (8-bit)   | Н   | Н    | L    | L  | Н  | Н  | VPPH | VPPX  | High-Z                         | Odd byte data out              |

| Read C (8-bit)   | Н   | L    | Н    | L  | Н  | Х  | VPPH | VPPX  | Odd byte data out              | High-Z                         |

| Write A (16-bit) | Н   | L    | L    | Н  | L  | Х  | VPPH | VppH  | Command or odd<br>byte data in | Command or even byte data in   |

| W.:. D (0 1::)   | Н   | Н    | L    | Н  | L  | L  | VPPX | VppH  | High-Z                         | Command or even byte data in   |

| Write B (8-bit)  | Н   | Н    | L    | Н  | L  | Н  | VppH | VPPX  | High-Z                         | Command or odd<br>byte data in |

| Write C (8-bit)  | Н   | L    | Н    | Н  | L  | х  | VppH | VPPX  | Command or odd<br>byte data in | High-Z                         |

| 0                | Н   | Х    | Х    | Н  | Н  | Χ  | VppH | VPPX  | High-Z                         | High-Z                         |

| Output disable   | H.  | X    | Х    | Н  | Н  | X  | VPPX | VPPH  | High-Z                         | High-Z                         |

Note 2 :  $H = V_{1H}$ ,  $L = V_{1L}$ ,  $X = V_{1H}$  or  $V_{1L}$ ,  $V_{PP}X = V_{PP}L$  or  $V_{PP}H$ To operate refer to the command definition, algorithms and so on.

## FUNCTION TABLE (ATTRIBUTE MEMORY)

| Mode              | REG | CE 2 | CEI | ŌĒ | WĒ | Α0 | VPP2 | Vpp1 | I/O<br>(D15-D8)              | I/O<br>(D7-D0)               |

|-------------------|-----|------|-----|----|----|----|------|------|------------------------------|------------------------------|

| Standby           | L   | Н    | Н   | Х  | X  | X  | Vcc  | Vcc  | High-impedance               | High-impedance               |

| Read A (16-bit)   | L   | L    | L   | L  | Н  | X  | Vcc  | Vcc  | Data out (not valid)         | Even byte data out           |

| D - 1 D / D 1 1 1 | L   | Н    | L   | L  | Н  | L  | Vcc  | Vcc  | High-impedance               | Even byte data out           |

| Read B (8-bit)    | L   | H    | L   | L  | Н  | Н  | Vcc  | Vcc  | High-impedance               | Data out (not valid)         |

| Read C (8-bit)    | L   | L    | Н   | L  | Н  | X  | Vcc  | Vcc  | Data out (not valid)         | High-impedance               |

| Write A (16-bit)  | L   | L    | L   | Н  | L  | х  | Vcc  | Vcc  | Odd byte data in (not valid) | Even byte data in            |

|                   | L   | Н    | L   | Н  | L  | L  | Vcc  | Vcc  | High impedance               | Even byte data in            |

| Write B (8-bit)   | L   | Н    | L   | Н  | L  | Н  | Vcc  | Vcc  | High impedance               | Odd byte data in (not valid) |

| Write C (8-bit)   | L   | L    | Н   | Н  | L  | ×  | Vcc  | Vcc  | Odd byte data in (not valid) | High impedance               |

| Output disable    | L   | Х    | Х   | Н  | Н  | ×  | Vcc  | Vcc  | High Impedance               | High Impedance               |

## COMMAND DEFINITION

When either or both VPP1 and VPP2 are applied the programming voltage (VPPH) the corresponding

memories of the card are set to read/write mode and the operation is controlled by the software command written in the control register.

## COMMAND DEFINITION TABLE

| 0                              | Bus    |       | First bus | cycle               | Second bus cycle |         |             |          |  |

|--------------------------------|--------|-------|-----------|---------------------|------------------|---------|-------------|----------|--|

| Command                        | cycles | Mode  | Address   | Data in             | Mode             | Address | Data in     | Data out |  |

| Read / Reset                   | 1      | Write | ZA        | FFh (FFFFh)         |                  | -       |             | _        |  |

| Programme Setup / Programme    | 2      | Write | PA        | 40h (4040h)         | Write            | PA      | PD          |          |  |

| Erase Setup/<br>Erase Confirm  | 2      | Write | ВА        | 20h (2020h)         | Write            | ВА      | D0h (DD00h) | :        |  |

| Erase Suspend/<br>Erase Resume | 2      | Write | ВА        | B0h (B0B0h)         | Write            | ВА      | D0h (D0D0h) |          |  |

| Read Status Register           | 2      | Write | ZA        | 70h (7070h)         | Read             |         | -           | RD       |  |

| Clear Status Register          | 1      | Write | ZA        | <b>50</b> h (5050h) |                  | _       |             | _        |  |

| Read Device<br>Identifier Code | 2      | Write | ZA        | 90h (9090h)         | Read             | DIA     |             | DID      |  |

Note 3. Indicates the basic functions of commands. Refer to the algorithms to operate.

Signal status is defined in function table and bus status.

Parenthesized data shows the data for 16 bit mode operation,

ZA = an address of a memory zone (Please reser to the memory zone)

PA = Programming address

PD = Programming data

BA = An address of a memory block (Please refer to the memory block)

RD = Data of status Register

DIA = Device identifier address

000000h for manufacturer code

000002h for device code

DID = Device identifier data

manufacturer code: 89h (8989h)

device code

: A2h (A2A2h)

#### Read/Reset

The memory in the card is switched to read mode by writing FFh (FFFFh for 16 bit operation) into the control resister. This mode is maintained until the contents of register are changed. This mode have nothing to do with the voltage of VPP.

This mode needs to be written to every memory zone to which access is required.

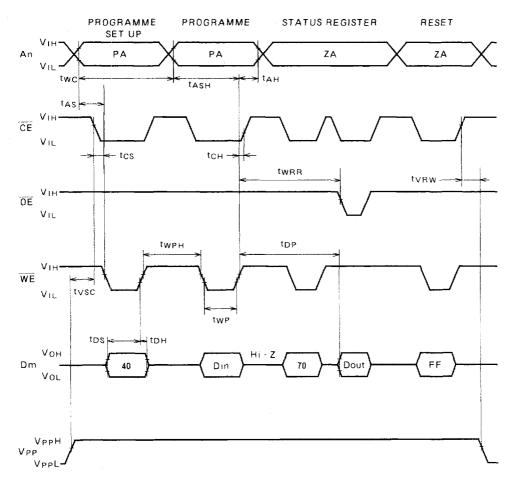

## Programme Setup/Programme

The setup programme command sets up the card for programming. It is applied when 40h (4040h for 16 bit operation) is written to control register. Programming will take place automatically after latching the address and data which are applied at the rising edge of WE.

The completion of programme can be confirmed by reading status register, after writing Read status register command 70h (7070h for 16 bit operation) to control register.

(For details please refer to the algorithm)

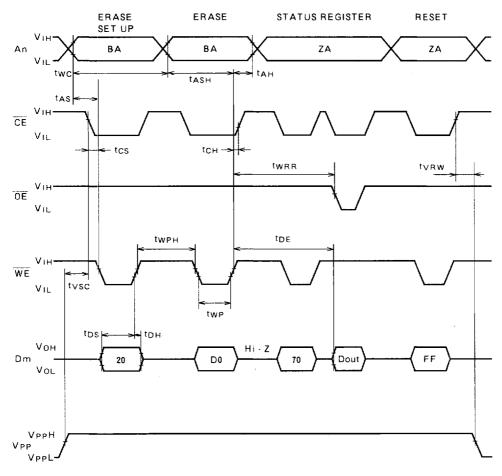

#### Erase Setup/Erase confirm

The erase setup is a command to set up the memory block for erasure. Writing setup erase command 20h (2020h for 16 bit operation) in the control register fol lowed by erase confirm command D0h (D0D0h for 16 bit operation) will initiate a erasure opertion. Eraseing will take place automatically after the rising edge of WE controlled by a internal timer.

The completion of erase can be confirmed by reading status register, after writing read status register command 70h (7070h for 16 bit operation) to control register.

(For details please refer to the algorithm)

These commands will not erase all the data of a memory card and should be repeated for all the required memory blocks. At an eight bit access mode it should be noticed that the erasure of a memory block will result in odd byte or even byte erasure.

#### Erase Suspend/Erase Resume

The erase suspend command B0h (B0B0h for 16 bit operation) is a command to generate erase interruption and to read data from another block of selected memory zone.

By writing in the control register erase resume command D0h (D0D0h for 16 bit operation), the memory block will continue the erase operation.

These commands must be executed in erase algo-

rithm.

(For details please refer to the algorithm)

#### Read Status Register

The Read status register is a command to read the status register's data and to make sure programme or earse operations complete successfully. The data of status register can be read after writing 70h (7070h for 16 bit operation) in the control register. The register's read data is latched on the falling edge of  $\overline{OE}$ . At programme or erase, the status register's data must be read to verify the results.

#### Clear Status Register

The clear status register command will clear data of status register. It is applied when 50h (5050h for 16 bit operation) is written to the control register. If an error occured during programme or erase, the status register must be cleared before retrying programme or erase.

#### Read Device Identifier Codes

The read device identifier codes command is implemented by writing 90h (9090h for 16 bit operation) to the command register. After writing the command, manufacturer code can be read at the address of 000000h of the zone and device code can be read at the address 000002h of the zone. Each card uses the same type of memory throughout and each memory zone will respond the same code.

(Do not apply high voltage to A10 pin in order to try and read the device identifier codes as this will result in the card being destroyed.)

## STATUS REGISTER

When operating programme or erase, it is necessary to read status register data and to transact

these bit. Each memory IC used in this card has internal status register to make sure programme or erase operations complete successfully.

| 7 (15) BIT                  | 6 (14) BIT    | 5 (13) BIT  | 4 (12) BIT         | 3 (11) BIT | 2~0 (10~8) BIT |

|-----------------------------|---------------|-------------|--------------------|------------|----------------|

| Programme /<br>Erase Status | Erase Suspend | Erase Error | Programme<br>Error | Vpp Error  | Reserved       |

| Bit                         | Bit           | Bit         | Bit                | Bit        |                |

Note 4, (); for 16 bit operation

Bit; Field name

7(15) BIT; Programme/Erase Status Bit

0=Busy (in programming/erasing)

1 = Ready

6(14) BIT; Erase Suspend Bit

1 = Erase Suspended

5(13) BIT; Erase Error Bit

1 = Erase Error

4(12) BIT ; Programme Error Bit

1 = Programme Error

3(11) BIT; VPP Error

I = Error of voltage at Vpp

2(10) BIT

0(8) BIT; Reserved for future

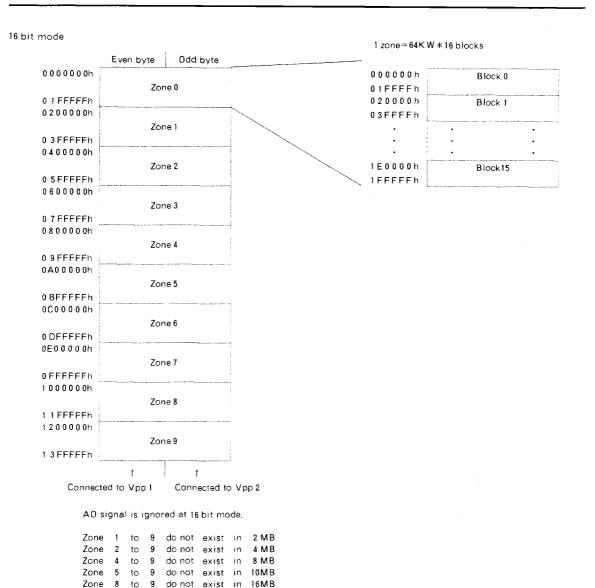

## **MEMORY ZONE AND BLOCK**

8 bit mode

1 zone = 64KB \* 16 blocks

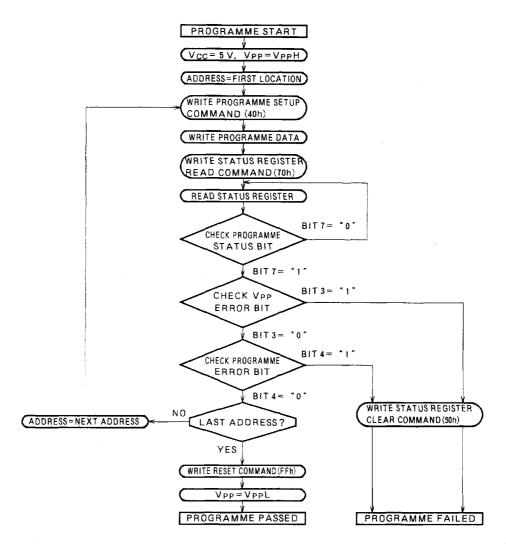

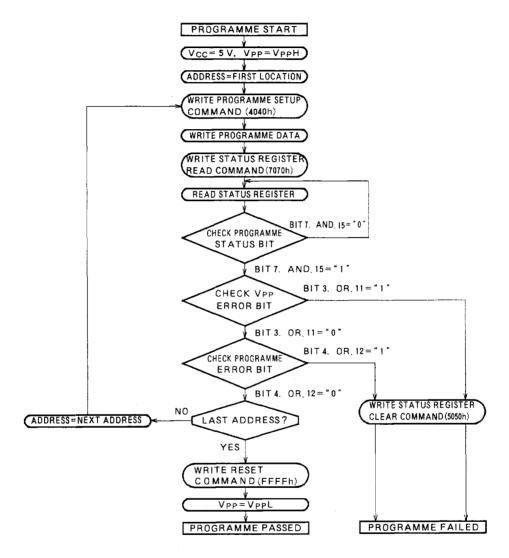

#### PROGRAMME SEQUENCE

#### 8 bit Operation

First apply VPPH to VPP1 and/or VPP2. Then the write programme setup command (40 h) to the address to be programmed. The next write sequence will initiate the programming operation which will end automatically as this period being controlled by an internal timer and the data will be programmed. To make sure that the data is programmed correctly write a read status register command (70 h) and read data. (Reading should be waited more than  $6\mu s$  after the programme setup command)

If the data is programed step address and program me data according to the above sequence.

The next address to be programmed should be writt en with in a memory zone whose Vpp voltage is set to VppH. If not write the reset command (FFh) an d then drop the Vpp voltage to VppL.

Then apply VPP for the desired memory zone and proceed with programming.

In applications where VPP1 and VPP2 are shorted together all addresses can be programmed without there being any need for the programming algorithm to take account of the cards memory zone architecture

## 16 bit operation

The algorithm of 16 bit programming is almost same as the 8 bit programming. (Please refer to the algorithm and the status of bus at programming)

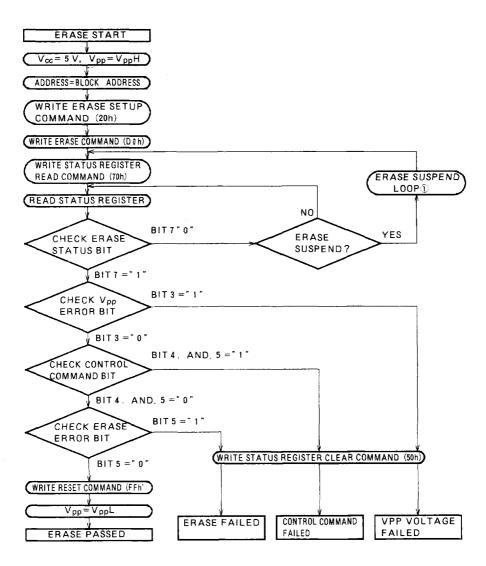

## **ERASE SEQUENCE**

## ERASE

#### 8 bit Operation

First apply VPPH to VPP1 and/or VPP2. Then write the erase setup command (20h) and erase cofirm command (D0h) for the applicable block address.

An erasure operation will then commence which will be finished in 1.6s typical or less this being automatically controlled by an internal timer.

To make sure that the data is erased correctly write the read status register command (70h) and read data (Reading should be waited more than 300ms after the erase confirm command). After erasure has been completed write the reset command (FFh) to the control register, set Vpp1 and/or Vpp2 to VppL as applicable and proceed with the erase operation for the next memory block.

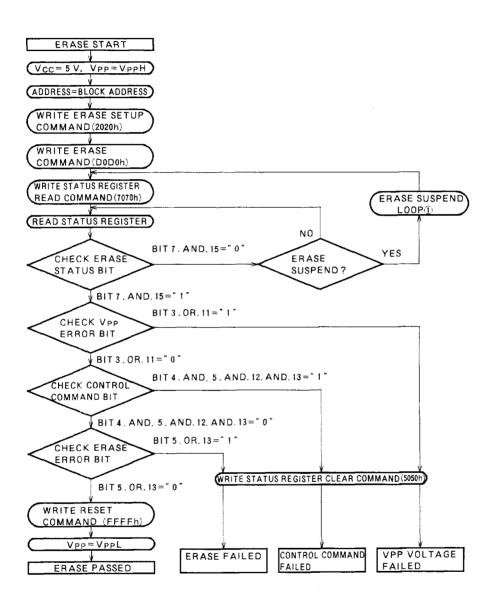

#### 16 bit Operation

Most of the algorithm of 16 bit erasure is same as the one of the 8 bit erasure.

(Please refer to the algorithm and the state of bus at erasure.)

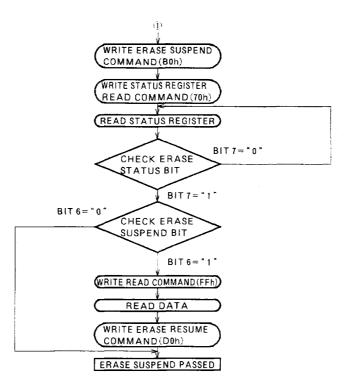

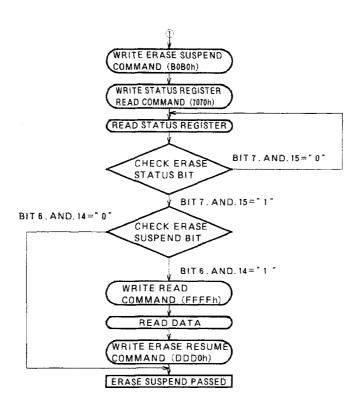

#### **ERASE SUSPEND**

#### 8 bit Operation

The erase suspend is a command to generate block erase interruption in order to read data from another block of the selected memory zone. It is necessary to write the erase suspend command (B0h) in the erase algorithm. The excecution of the erase suspend can be confirmed by reading data of the status register, after writing the read status register command (70h).

Then it is necessary to write the read command (FFh) in control register in order to read data, after reading the status register's data.

After the erase resume command (D0h) is written in the control register, the memory block will continue erase operation.

#### 16 bit Operation

Most of the algorithm of 16 bit erase suspending is same as the one of the 8 bit erase suspending. (Please refer to the algorithm and the state of bus at erase suspending.)

## PROGRAMME ALGORITHM

8 bit mode

Note 5. This is programme algorithm for a memory zone and not for a card.

. If Vpp error bit is detected, try to programme again at VppH level.

#### PROGRAMME ALGORITHM

16 bit mode

Note 6. If VPP error bit is detected, try to programme again at VPPH level.

This is programme algorithm for a memory zone and not for a card.

..OR.:=Logical or ; .AND.:=Logical and

# ERASE ALGORITHM

8 bit mode

Note 7 . If  $V_{pp}$  error bit is detected, try to programme again at VppH level.

. This is an erase algorithm for a memory block and not for a card.

.. OR. : = Logical or

Note 8. Reading data from block other than the suspended block the in zone generating erase suspend.

## **ERASE ALGORITHM**

16 bit mode

Note 9. If VPP error bit is detected, try to programme again at VPPH level.

- . This is an erase algorithm for a memory block and not for a card,

- .. OR. : = Logical or ; . AND. : = Logical and

Note 10, Reading data from block other than the suspended block the in zone generating erase suspend. . AND. : = Logical and

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter             | Conditions           | Ratings      | Unit |  |

|------------------|-----------------------|----------------------|--------------|------|--|

| Vcc              | Vcc Supply voltage    |                      | -0.5~6.0     | V    |  |

| VPP              | Vpp Supply voltage    | Wish                 | -0.5~14.0    | V    |  |

| Vı               | Input voltage         | With respect to GND  | -0.3~Vcc+0.3 | V    |  |

| Vo               | Output voltage        |                      | 0~Vcc        | V    |  |

| Topr             | Operating temperature | Read/Write Operation | 0 ~70        | °C   |  |

| T <sub>stg</sub> | Storage temperature   |                      | -40~80       | ℃    |  |

## **RECOMMENDED OPERATING CONDITIONS** (Ta= $0 \sim 55 \, \text{C}$ , unless otherwise noted)

| 0      |                                          |           |       | Limits |         | I I a la |

|--------|------------------------------------------|-----------|-------|--------|---------|----------|

| Symbol | Parameter                                |           | Min.  | Typ.   | Max.    | Unit     |

| Vcc    | VCC supply voltage                       |           | 4. 75 | 5. 0   | 5. 25   | V        |

| VPPL   | VPP supply voltage during READ only mode |           | 0     | Vcc    | Vcc+1.0 | V        |

| VppH   | VPP supply voltage during READ WRITE mo  | 11.4      | 12. 0 | 12. 6  | V       |          |

| VIH    | High input voltage                       |           | 2. 4  |        | Vcc     | ٧        |

| VIL    | Low input voltage                        |           | 0     |        | 0.8     | V        |

| A.I    | Number of simultaneous activated         | Programme |       |        | 1       | Zone     |

| NACT   | memory zones/blocks                      | Erase     | :     |        | 1       | Block    |

## ELECTRICAL CHARACTERISTICS (Ta=0~55°C, VCC=5 V±5 %, VPP=VPPL or VPPH, unless otherwise noted)

| Symbol           | Parameter                           | Con                                                                                                  | ditions                                                                                                  |      |        | Limits |        | – Uni      |

|------------------|-------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|--------|--------|--------|------------|

|                  | T di billetei                       |                                                                                                      | ~                                                                                                        |      | Min.   | Тур.   | Max.   | 7 011      |

| Vон              | High output voltage                 | $I_{OH} = -0.1 \text{mA}, BVDn$                                                                      |                                                                                                          |      | 2. 4   |        |        | V          |

| * UN             | Tingir Culput Voltage               | IOH = -1.0mA, Other                                                                                  | outputs                                                                                                  |      | 2. 4   |        |        |            |

| VoL              | Low output voltage                  | IOL=2mA                                                                                              |                                                                                                          |      | 0      |        | 0.4    | V          |

| ПН               | High input current                  | VI=VCC V                                                                                             |                                                                                                          |      |        |        | 10     | 11.1       |

| HL               | Low input current                   | VI= 0 V                                                                                              | , CE 2 , OE, WE, F                                                                                       | REG  | 10     |        | - 70   |            |

| 111              | Low input current                   | Othe                                                                                                 | r inputs                                                                                                 |      |        |        | -10    | ų į        |

| lozн             | High output current in off state    | $\overline{CE 1} = \overline{CE 2} = V_{1H} \text{ or } \overline{O}$                                | $\overline{CE} = \overline{CE} = V_{IH} \text{ or } \overline{OE} = V_{IH}, V_{O}(Dm)$                   |      |        |        | 10     | μ F        |

| lozu             | Low output current in off state     | $\overline{CE1} = \overline{CE2} = V_{1H} \text{ or } \overline{O}$                                  | $\overline{CE1} = \overline{CE2} = V_{1H} \text{ or } \overline{OE} = V_{1H}, \ V_{O}(Dm) = 0 \text{ V}$ |      |        |        | -10    | u A        |

| lcc1 · 1         | Active VCC supply current 1         | CE 1 = CE 2 = V <sub>IL</sub> , Oth Outputs = open                                                   |                                                                                                          |      |        | 100    | 200    | m A        |

| lcc1 · 2         | Active VCC supply current 2         | $\overline{CE1} = \overline{CE2} \le 0.2V$ , Other inputs $\le 0.2V$ or $\ge -0.2V$ , Outputs = open |                                                                                                          |      |        | 90     | 180    | m/         |

|                  |                                     |                                                                                                      |                                                                                                          |      |        |        | 9. 0   |            |

|                  |                                     |                                                                                                      | Ī                                                                                                        | 4 MB |        |        | 13     | 1          |

| lcc 2 · 1        | Standby VCC                         | CE 1 = CE 2 = VIH, Oth                                                                               | ner inputs=Vıн∫                                                                                          | 8 MB |        |        | 21     | ] m/       |

| supply current 1 | or VIL                              | 1                                                                                                    | 10MB                                                                                                     |      |        | 25     | - (11) |            |

|                  |                                     | 16MB                                                                                                 |                                                                                                          |      |        |        | 37     | 7          |

|                  |                                     |                                                                                                      |                                                                                                          | 20MB |        |        | 45     | 7          |

|                  |                                     |                                                                                                      | 2 MB                                                                                                     |      | 0. 1   | 1, 2   |        |            |

|                  |                                     |                                                                                                      |                                                                                                          | 4 MB | 0.2 1. | 1.4    | T      |            |

| CC 2 · 2         | Standby Vcc                         | <u>CE 1</u> = <u>CE 2</u> ≥ V <sub>CC</sub> - 0.2                                                    | 2V.                                                                                                      | 8 MB |        | 0.4    | 1.8    | m A        |

| 1002 - 2         | supply current 2                    | Other inputs ≤ 0.2V or ≥                                                                             |                                                                                                          | 10MB |        | 0, 5   | 2.0    |            |

|                  |                                     |                                                                                                      |                                                                                                          | 16MB |        | 0.7    | 2. 6   | 1          |

|                  |                                     |                                                                                                      |                                                                                                          | 20MB |        | 0.8    | 3. 0   |            |

|                  |                                     |                                                                                                      |                                                                                                          | 2 MB |        | 10     | 20     |            |

|                  |                                     |                                                                                                      |                                                                                                          | 4 MB |        | 20     | 30     | 1          |

|                  | V pp supply current 1               | 14 14 1-14                                                                                           |                                                                                                          | 8 MB |        | 30     | 50     | 1          |

| Ірр 1            | (each Vpp pin)                      | V <sub>PP</sub> =V <sub>PP</sub> L≦V <sub>CC</sub>                                                   | <u> </u>                                                                                                 | 10MB |        | 40     | 60     | <i>µ I</i> |

|                  | *                                   |                                                                                                      |                                                                                                          | 16MB |        | 50     | 90     | 1          |

|                  |                                     |                                                                                                      | Ī                                                                                                        | 20MB |        | 70     | 110    | 1          |

|                  |                                     |                                                                                                      | 1                                                                                                        | 2 MB |        |        | 0. 3   |            |

|                  |                                     |                                                                                                      | ľ                                                                                                        | 4 MB |        |        | 0. 5   | 1          |

|                  | Vpp supply current 2                |                                                                                                      |                                                                                                          | 8 MB |        |        | 0.9    | 1          |

| IPP 2            | (each Vpp pin)                      | Vpp=VppH (standby,                                                                                   | read)                                                                                                    | 10MB |        |        | 1.1    | m/         |

|                  | (each vpppm)                        |                                                                                                      | 16N                                                                                                      |      |        |        | 1.7    |            |

|                  |                                     |                                                                                                      | .                                                                                                        | 20MB |        |        | 2. 1   | 1          |

| lpp3             | Vpp supply current 3 (each Vpp pin) | Vpp=VppH (program                                                                                    | me,erase)                                                                                                |      |        | 10     | 35     | m/         |

Note 11. Currents flowing into the card are taken as positive (unsigned).

Typical values are measured at  $V_{CC} = 5.0 \text{ V}$ ,  $V_{PPL} = 5 \text{ V}$ ,  $V_{PPH} = 12 \text{ V}$ ,  $T_a = 25 ^{\circ}\text{C}$ .

The card consumes active current at programming, erasure

even if both CE1 and CE2 are high level.

## CAPACITANCE

| Symbol   | Parameter          | Test conditions                                                           |      | Unit |      |      |

|----------|--------------------|---------------------------------------------------------------------------|------|------|------|------|

| 39111001 | raianieter         | rest conditions                                                           | Min. | Тур. | Мах. | Onit |

| Ci       | Input capacitance  | V₁=GND, v₁=25mVrms, f= 1 MHz, Ta=25°C                                     |      |      | 45   | pF   |

| Co       | Output capacitance | V <sub>O</sub> =GND, v <sub>o</sub> =25mVrms, f=1MHz, T <sub>e</sub> =25℃ |      |      | 45   | pF   |

Note 12 : These parameters are not 100% tested.

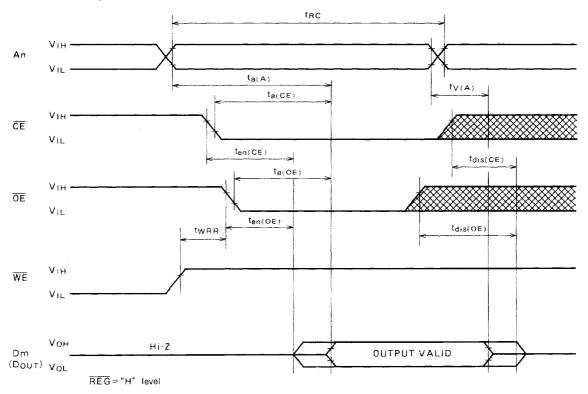

## SWITCHING CHARACTERISTICS (COMMON MEMORY)

Read Cycle (Ta=0~55°C, Vcc=5 V±5%, Vpp=VppL or VppH, unless otherwise noted)

| C. mahad | Pausanan                                           |      | Limits |      |      |  |  |  |

|----------|----------------------------------------------------|------|--------|------|------|--|--|--|

| Symbol   | Parameter                                          | Min. | Тур.   | Max. | Unit |  |  |  |

| tRC      | Read cycle time                                    | 200  |        |      | ns   |  |  |  |

| ta(A)    | Address access time                                |      |        | 200  | ns   |  |  |  |

| ta(CE)   | Card enable access time                            |      |        | 200  | ns   |  |  |  |

| ta(OE)   | Output enable access time                          |      |        | 100  | ns   |  |  |  |

| tdis(CE) | Output disable time (from CE)                      |      |        | 90   | ns   |  |  |  |

| tdis(OE) | Output disable time (from $\overline{\text{OE}}$ ) |      |        | 90   | ns   |  |  |  |

| ten(CE)  | Output enable time (from CE)                       | 5    |        |      | ns   |  |  |  |

| ten(OE)  | Output enable time (from $\overline{OE}$ )         | 5    |        |      | ns   |  |  |  |

| tV(A)    | Data valid time after address change               | 0    |        |      | ns   |  |  |  |

## TIMING REQUIREMENTS (COMMON MEMORY)

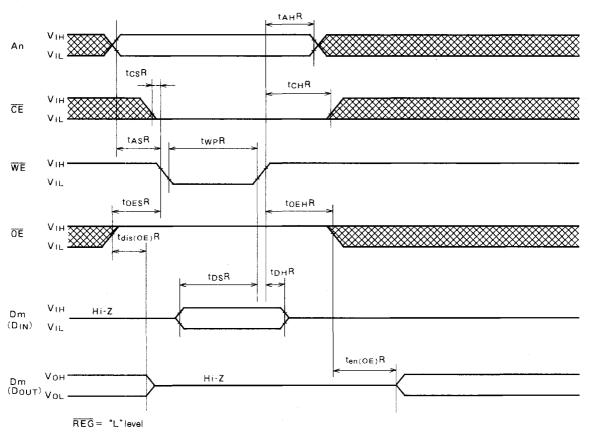

Write Cycle (T<sub>8</sub>= 0  $\sim$ 55%, V<sub>CC</sub>= 5 V  $\pm$  5 %, V<sub>PP</sub>=V<sub>PP</sub>H, unless otherwise noted)

| Symbol |                                         | Limits |      | Uni: |      |

|--------|-----------------------------------------|--------|------|------|------|

|        | Parameter                               | Min.   | Тур. | Max. | Unii |

| twc    | Write cycle time                        | 200    |      |      | ns   |

| tAS    | Address setup time                      | 20     |      |      | ns   |

| tAH    | Address hold time                       | 30     |      |      | ns   |

| tDS    | Data setup time                         | 60     |      |      | ns   |

| tDH    | Data hold time                          | 30     |      |      | ns   |

| twrr   | Write recovery time before read         | 10     |      |      | ns   |

| tcs    | Card enable setup time before write     | 20     |      |      | ns   |

| tch    | Card enable hold time                   | 30     |      |      | ns   |

| twp    | Write pulse width                       | 120    |      |      | ns   |

| twph   | Write pulse width high                  | 40     |      |      | ns   |

| tDP    | Duration of programming operation       | 6      |      |      | μs   |

| tDE    | Duration of erase operation             | 300    |      |      | ms   |

| tvsc   | VPP setup time to card enable low       | 1      |      |      | u s  |

| tvRW   | VPP recovery time to card enable high   | 150    |      |      | ns   |

| tash   | Address setup time to write enable high | 140    |      |      | ns   |

Note 13: Refer to switching characteritics for read parameters

## TIMING DIAGRAM Common Memory Read

Note 14: Indicates the don't care input.

# TIMING DIAGRAM (COMMON MEMORY) Programme Mode

REG = "H" level

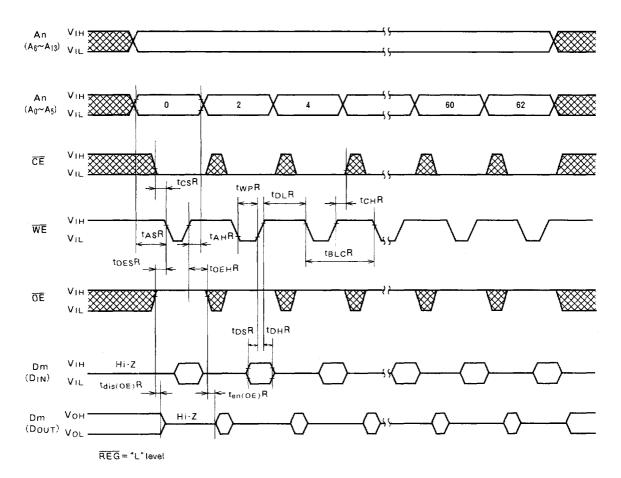

# TIMING DIAGRAM (COMMON MEMORY) Erase Mode

REG="H" level

## SWITCHING CHARACTERISTICS

**Read Cycle** ( $T_a = 0 \sim 55\%$ ,  $V_{CC} = 5 V \pm 5\%$ ,  $V_{PP} = V_{CC}$ , unless otherwise noted)

| Symbol    | D                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Limits         |     |      |

|-----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|------|

|           | Parameter                            | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Min. Typ. Max. |     | Unit |

| tRCR      | Read cycle time                      | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |     | ns   |

| ta(A)R    | Address access time                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 300 | ns   |

| ta(CE)R   | Card enable access time              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 300 | ns   |

| ta(OE)R   | Output enable access time            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 150 | ns   |

| tdis(CE)R | Output disable time (from CE)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 100 | ns   |

| tdis(OE)R | Output disable time (from OE)        | 100 mm 10 |                | 100 | ns   |

| ten(CE)R  | Output enable time (from CE)         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |     | ns   |

| ten(OE)R  | Output enable time (from OE)         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |     | ns   |

| tv(A)R    | Data valid time after address change | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |     | ns   |

## TIMING REQUIREMENTS (ATTRIBUTE MEMORY)

Write Cycle (Ta= 0~55°C, VCC=5V±5%, Vpp=Vcc, unless otherwise noted)

| Symbol    | Povemeter                                  | Limits | Limits       |     |      |

|-----------|--------------------------------------------|--------|--------------|-----|------|

|           | Parameter                                  | Min.   | Min. Typ. Ma |     | Unit |

| tasR      | Address setup time                         | 30     |              |     | ns   |

| tahR      | Address hold time                          | 30     |              |     | ns   |

| tcsR      | CE setup time                              | 40     |              |     | ns   |

| tcHR      | CE hold time                               | 30     |              |     | ns   |

| tosR      | Data setup time                            | 120    |              |     | ns   |

| tDHR      | Data hold time                             | 40     |              |     | ns   |

| tOESR     | OE setup time                              | 30     |              |     | ns   |

| tOEHR     | OE hold time                               | 40     |              |     | ns   |

| twpR      | Write pulse width                          | 170    |              |     | ns   |

| tDLR      | Data latch time                            | 120    |              |     | ns   |

| tBLCR     | Byte load cycle time                       | 0.3    | !            | 30  | μs   |

| twcR      | Write cycle time                           | 10     |              |     | ms   |

| ten(OE)R  | Output enable time (from $\overline{0E}$ ) | 5      |              | 1   | ns   |

| tdis(OE)R | Output disable time (from OE)              | 0      |              | 100 | ns   |

## TIMING DIAGRAM (Attribute Memory)

Read tRCR Αn ta(A)R ta(CE)R ĈĒ ten(CE)R tdis(CE)A ta(OE)R ŌĒ tdis(OE)R ten(OE)R Vон Hi-Z **OUTPUT VALID** Dm (DOUT) VOL WE = "H" level, REG = "L" level

## Byte Write

#### Page Mode Write

Note 15: AC Test Conditions

Input pulse levels : VIL = 0.4V, VIH = 2.8V Input pulse rise, fall time :  $t_r = t_f = 10$ ns Reference voltage

Input:  $V_{1L} = 0.8V$ ,  $V_{1H} = 2.4V$ Output:  $V_{0L} = 0.8V$ ,  $V_{0H} = 2.9V$

(ten and tais are measured when output voltage is ±500mV from steady state.)

100pF + 1 TTL gate Load:

5 pF + 1 TTL gate (at ten and tois measuring)

16 : The data write is performed during the interval when both  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  are "L" level.

17: Do not apply inverted phase signal externally when Dm pin is in output mode.

18: CE is indicated as follows:

Read A/Write A:  $\overline{CE} = \overline{CE} \ 1 = \overline{CE} \ 2 = "H"$  level Read B/Write B:  $\overline{CE} = \overline{CE} \ 1$ ,  $\overline{CE} \ 2 = "H"$  level Read C/Write C:  $\overline{CE} = \overline{CE} \ 2$ ,  $\overline{CE} \ 1 = "H"$  level

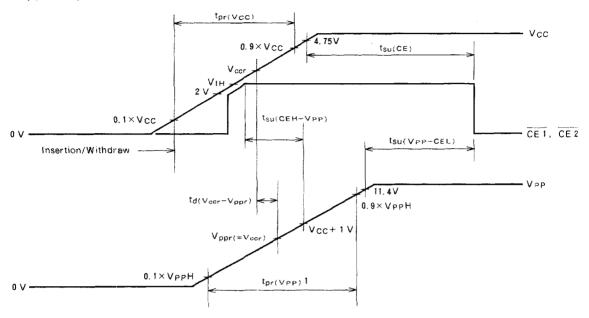

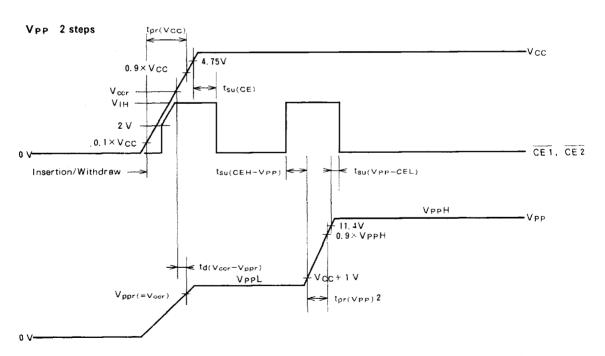

## **RECOMMENDED POWER UP/DOWN CONDITIONS** ( $T_a = 0 \sim 55\%$ , unless otherwise noted)

| Symbol              | Parameter                     | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Limits         |      |         |      |