## **Preliminary**

Notice: This is not a final specification. Some parametric limits are subject to change.

### M6MGE13VW34DWG

134,217,728-BIT (8,388,608-WORD BY 16-BIT) CMOS FLASH MEMORY & 33,554,432-BIT (2,097,152-WORD BY 16-BIT) CMOS MOBILE RAM

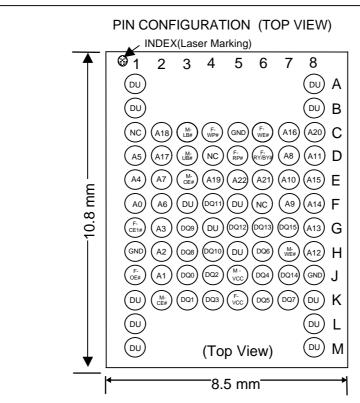

Stacked-CSP (Chip Scale Package)

#### **Description**

The M6MGE13VW34DWG is a Stacked Chip Scale Package (S-CSP) that contents 128M-bit Flash memory and 32M-bit Mobile RAM in a 72-pin Stacked CSP for lead free use.

128M-bit Flash memory is a 8,388,608 words, single power supply and high performance non-volatile memory fabricated by CMOS technology for the peripheral circuit and DINOR IV (Divided bit-line NOR IV) architecture for the memory cell. All memory blocks are locked and can not be programmed or erased, when F-WP# is Low. Using Software Lock Release function, program or erase operation can be executed.

32M-bit Mobile RAM is a 2,097,152 words high density RAM fabricated by CMOS technology for the peripheral circuit and DRAM cell for the memory array. The interface is compatible to Package an asynchronous SRAM.

The cells are automatically refreshed and the refresh control is not required for system. The device also has the partial block refresh scheme and the power down mode by writing the command.

The M6MGE13VW34DWG is suitable for a high performance cellular phone and a mobile PC that are required to be small mounting area, weight and small power dissipation.

#### **Features**

Access Time Random Access/ Page Access

Flash 70ns (Max.) Mobile RAM 80ns (Max.)

Supply Voltage F-VCC=2.7 ~ 3.0V

M-VCC=2.7 ~ 3.0V

Ambient Temperature Ta= -40 ~ 85 degree

Package 72pin S-CSP,

Ball pitch 0.80mm

Outer-ball:Sn-Ag-Cu

### **Application**

Mobile communication products

F-VCC : VCC for Flash F-RP# : Reset power down for Flash M-VCC : VCC for Mobile RAM F-WP# : Write protect for Flash **GND** : GND for Flash / Mobile RAM F-RY/BY# : Flash Memory Ready /Busy A0-A20 : Common address for Flash/Mobile RAM M-CE# : Mobile RAM chip enable : Address for Flash A21/A22 M-OE# : Output enable for Mobile RAM DQ0-DQ15: Data I/O M-WF# : Write enable for Mobile RAM F-CE1# : Flash chip enable M-LB# : Lower byte control for Mobile RAM F-OE# : Output enable for Flash Memory M-UB# : Upper byte control for Mobile RAM

F-WE# : Write enable for Flash Memory NC : Non Connection

DU : Don't Use

## **Preliminary**

Notice: This is not a final specification.

Some parametric limits are subject to change.

## M6MGE13VW34DWG

134,217,728-BIT (8,388,608-WORD BY 16-BIT) CMOS FLASH MEMORY & 33,554,432-BIT (2,097,152-WORD BY 16-BIT) CMOS MOBILE RAM

Stacked-CSP (Chip Scale Package)

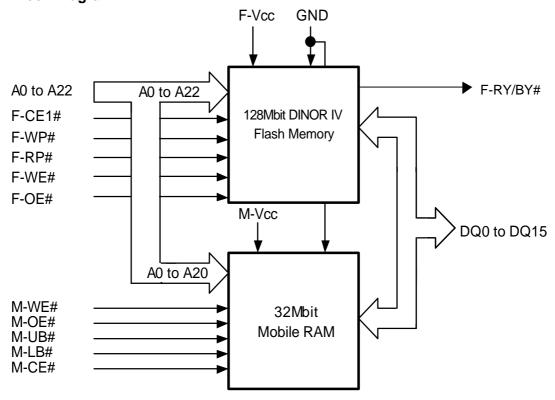

### **MCP Block Diagram**

Note: In the Flash Memory part they mean OE# and WE# are F-OE# and F-WE#.

In the Mobile RAM part UB#, LB#, OE# and WE# are M-UB#, M-DE# and M-WE#, respectively.

#### Capacitance

| Symbol     | Parameter             |                                                                                             | Conditions                      | Limits |      |      | Unit |

|------------|-----------------------|---------------------------------------------------------------------------------------------|---------------------------------|--------|------|------|------|

| <b>C</b> y |                       |                                                                                             |                                 | Min.   | Тур. | Max. | 01   |

| CIN        | Input capacitance     | A21-A0, F-OE#, F-WE#, F-CE1#,<br>F-CE2#, F-WP#, F-RP#, M-OE#,<br>M-WE#, M-CE#, M-LB#, M-UB# | Ta=25°C, f=1MHz,<br>Vin=Vout=0V |        |      | 26   | pF   |

| COUT       | Output<br>Capacitance | DQ15-DQ0, F-RY/BY#                                                                          |                                 |        |      | 34   | pF   |

## **Preliminary**

Notice: This is not a final specification. Some parametric limits are subject to change.

## M6MGE13VW34DWG

134,217,728-BIT (8,388,608-WORD BY 16-BIT) CMOS FLASH MEMORY & 33,554,432-BIT (2,097,152-WORD BY 16-BIT) CMOS MOBILE RAM

Stacked-CSP (Chip Scale Package)

# Renesas Technology Corp.

Nippon Bldg.,6-2,Otemachi 2-chome,Chiyoda-ku,Tokyo,100-0004 Japan

Keep safety first in your circuit designs!

Notes regarding these materials -

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual

- Inese materials are intended as a reference to assist our customers in the selection of the kenesas Technology Corporation or or a third party.

Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors.

- The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular,

- medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved

- uesuitation.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.