# AmPAL18P8

20-Pin IMOX™ Programmable Array Logic

### **Distinctive Characteristics**

- Individually programmable output polarity on each output

- Pin compatible superset of most combinatorial 20-pin PAL devices

- Eight logical product terms per output for increased logic power

- Increased input/output flexibility

- 18 possible array inputs

- Eight bidirectional I/Os with individually controllable output enable

- Ultra high-speed version tpD = 15 ns maximum

- Superior quality

- AC and DC parametric testing performed on every part

- Extensive on-chip test circuitry ensures post-programming functional yield (PPFY) of 99.9%

- Platinum-Silicide fuses ensure high programming yield > 98%, fast programming and unsurpassed reliability

- · Replaces 13 combinatorial 20-Pin PAL devices

# **General Description**

The AmPAL18P8 is an ultra high-performance, functionally enhanced 20-pin Programmable Array Logic element. It utilizes the familiar sum-of-products (AND-OR) structure allowing users to program custom logic functions to precisely fit their application.

The AmPAL18P8 offers significantly enhanced functional capabilities when compared to other combinatorial 20-pin PAL devices. These include two additional bidirectional I/O pins as well as additional product terms (bringing each output to eight logical and one three-state control product

term) for extra logic power. The device also features individually user programmable output polarity, giving the designer the capability to handle both active HIGH and active LOW outputs on the same device.

A wide variety of speed/power selections is available, allowing precise matching to system requirements. The ultra high-speed version offers 15 ns maximum input to output propagation delay, opening up many new applications for the use of programmable logic.

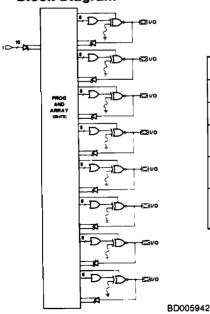

#### **Block Diagram**

#### PRODUCT SELECTOR GUIDE

| Family<br>Part No.                   |            | AmPAL18P8                             |             |     |     |               |           |     |                        |     |  |  |  |

|--------------------------------------|------------|---------------------------------------|-------------|-----|-----|---------------|-----------|-----|------------------------|-----|--|--|--|

| Power<br>Grade                       | Qua        |                                       |             | Pov |     | Full<br>Power |           |     |                        |     |  |  |  |

| Ordering<br>Part No.                 | 18P8Q 18P8 |                                       |             |     | 18P | 8AL           | 18F       | P8A | 18P8B                  |     |  |  |  |

| Speed<br>Grade                       |            |                                       | dard<br>bed |     |     |               | gh<br>eed | :   | Ultra<br>High<br>Speed |     |  |  |  |

| Max.                                 | STD        | STD APL STD APL STD<br>35 40 35 40 25 |             |     |     | APL           | STD       | APL | STD                    | APL |  |  |  |

| Access<br>Time (ns)                  | 35         |                                       |             |     |     | 30            | 25        | 30  | 15                     | 20  |  |  |  |

| Max.<br>Operating<br>Current<br>(mA) | 5          | 5                                     |             | 9   | Ю   |               |           | 14  | 80                     |     |  |  |  |

STD = AMD "Standard" products

APL = AMD "Approved Products List" products

05799E/0 JANUARY 1968

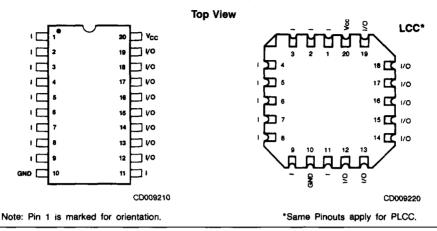

# **Connection Diagrams**

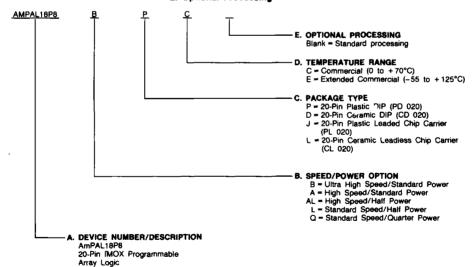

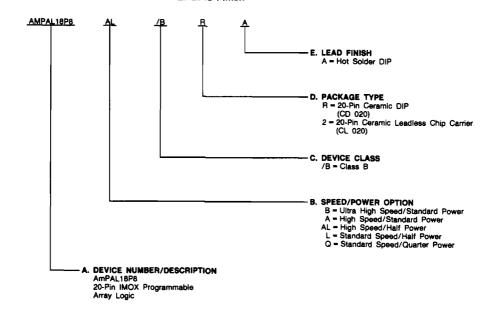

# **Ordering Information**

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

- B. Speed/Power Option

- C. Package Type

- D. Temperature Range

- E. Optional Processing

| AMPAL18P8B AMPAL18P8A AMPAL18P8AL AMPAL18P8L AMPAL18P8L AMPAL18P8C |  |  |  |

|--------------------------------------------------------------------|--|--|--|

| AMPAL18P88                                                         |  |  |  |

| AMPAL18P8A                                                         |  |  |  |

| AMPAL18P8AL                                                        |  |  |  |

| AMPAL18P8L                                                         |  |  |  |

| AMPAL18P8Q                                                         |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

# **Ordering Information** (Cont'd.)

#### **APL Products**

AMD products for Aereospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-833C requirements. The order number (Valid Combination) for APL products is formed by a combination of:

- A. Device Number B. Speed/Power Option

- C. Device Class D. Package Type

- E. Lead Finish

| Valid Co    | mbinations |

|-------------|------------|

| AMPAL18P8B  |            |

| AMPAL18P8A  |            |

| AMPAL18PBAL | /BRA, /B2A |

| AMPAL18P8L  |            |

| AMPAL18P8Q  | 7          |

PAL12L6

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11

The AmPAL18P8 can be used as a functional and pin-for-pin replacement for each of the following 20-pin devices:

| PAL10H8 | PAL14L4 |

|---------|---------|

| PAL12H6 | PAL16L2 |

| PAL14H4 | PAL16P8 |

| PAL16H2 |         |

| PAL10L8 |         |

# 7

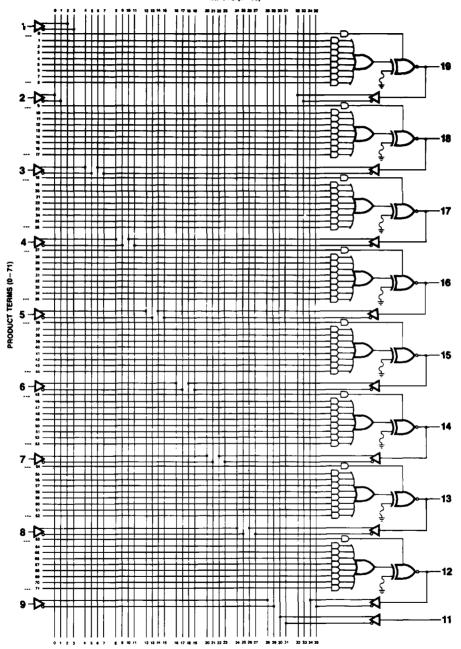

# **Logic Diagram**

INPUTS (0-35)

### Eighteen Array Inputs

- 10 dedicated

- 8 bidirectional I/O

#### Eight 8-Wide AND-OR Structures

- Combinatorial outputs

- Programmable output enable for each output

- Programmable polarity on each output

LD000040

# **Functional Description**

The AmPAL18P8 is a functionally enhanced Programmable Array Logic (PAL) device. The Block Diagram on page ?? shows the basic architecture of the AmPAL18P8. There are up to eighteen inputs and eight outputs available. The inputs are connected to a programmable AND array which contains 72 logical product terms. Initially the AND gates are connected, via fuses, to both the true and complement of every input. By selective programming of fuses, the AND gates may be "connected" to only the true input (by blowing the complement fuse) to only the complement input (by blowing the true fuse), or to neither type of input (by blowing both fuses), establishing a logical "don't care." When both the true and complement fuses are left intact, a logical false results on the output of the AND gate. An AND gate with all fuses blown will assume the logical true state.

The AmPAL18P8 has a possible maximum of 18 input pins, two more than previous 20-pin PAL devices. The extra inputs extend the functional capabilities of the device, which reduces design limitations, making it easier to design with and more flexible.

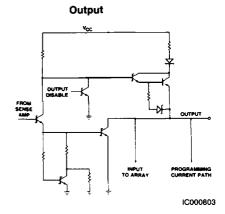

The AmPAL18P8 can be programmed with more complex logic equations due to the eight product terms and one control term for each output. The control terms also allow for each of the eight bi-directional I/Os to be three-stated, greatly expanding the realm of design possibilities.

The eight bi-directional I/O pins enhance the usefulness of the AmPAL18P8 by allowing for greater complexity of logic equations and hence more logic power.

The AmPAL18P8 also has programmable output polarity,

giving the designer the choice of either active HIGH or active LOW on each of the eight outputs. This simplifies the task of programming the AmPAL18P8 and allows more freedom in optimizing the logic functions. The high-speed version of the AmPAL18P8 boasts 15 ns maximum input-to-output propagation delay, and creates new possibilities for the use of programmable logic devices in a wide variety of applications.

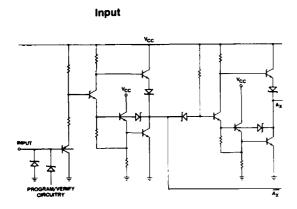

The AmPAL18P8 is manufactured using Advanced Micro Devices' IMOX oxide isolation process. This advanced process permits an increase in density and a decrease in internal capacitance, resulting in the fastest possible programmable logic devices. The AmPAL18P8 is fabricated with AMD's fast-programming, highly reliable Platinum-Silicide Fuse technology. Utilizing an easily implemented programming algorithm, these products can be rapidly programmed to any customized pattern.

Platinum-Silicide was selected as the fuse-link material to achieve a well-controlled melt rate, resulting in large non-conductive gaps that ensure very stable, long-term reliability. Extensive operating testing has proven that this low-field, large gap technology offers high reliability.

The AmPAL18P8 has been designed with extensive internal test circuitry that allows the programming and operating circuitry in the part to be thoroughly tested at the factory before programming. This assures excellent programming yield and functional performance to data sheet parameters after programming. The Post-Programming Functional Yield (PPFY) for this device is consistently better than 99.9%.

# **Programmer/Development Systems**

Refer to Programmer Reference Guide

# Input/Output Diagrams

# **Absolute Maximum Ratings**

| Storage Temperature65 to +150°C Supply Voltage          |

|---------------------------------------------------------|

| with Respect to Ground0.5 to +7.0 V                     |

| DC Voltage Applied to Outputs                           |

| (except during programming)0.5 to +V <sub>CC</sub> Max. |

| DC Voltage Applied to                                   |

| Outputs During Programming 16 V                         |

| Output Current Into Outputs                             |

| During Programming                                      |

| (Maximum duration of 1 second) 200 mA                   |

| DC Input Voltage0.5 to +5.5 V                           |

| DC Input Current30 to +5.0 mA                           |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **Operating Ranges**

| -                                                                                                                                 |                |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|

| Commercial (C) Devices Temperature (T <sub>A</sub> ) Supply Voltage (V <sub>CC</sub> )+4.                                         |                |

| Extended Commercial (E) Devices Temperature (T <sub>A</sub> ) Temperature (T <sub>C</sub> ) Supply Voltage (V <sub>CC</sub> )+4.5 | . + 125°C Max. |

| Military (M) Devices Temperature (T <sub>A</sub> ) Temperature (T <sub>C</sub> ) Supply Voltage (V <sub>CC</sub> )+4.5            | + 125°C Max.   |

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### DC Characteristics over operating range unless otherwise specified; included in Group A, Subgroup 1, 2, 3 tests unless otherwise noted

| Parameter<br>Symbol         | Parameter<br>Description     |                                              | Test Co                                              | nditions               |       | Min. | Typ.<br>(Note 1) | Max. | Units |

|-----------------------------|------------------------------|----------------------------------------------|------------------------------------------------------|------------------------|-------|------|------------------|------|-------|

|                             |                              |                                              |                                                      | 18P8A, 18P8B           |       |      |                  |      |       |

|                             |                              |                                              | I <sub>OH</sub> = -3.2 mA                            | 18P8L, 18P8AL          | COM'L | 2.4  | 3.5              |      | Volts |

| V <sub>OH</sub>             | Output HIGH Voltage          |                                              | I <sub>OH</sub> = -2 mA                              | 18P8Q                  | 1     |      |                  |      |       |

|                             |                              | 1                                            | I <sub>OH</sub> = -2 mA                              | (all versions)         | MIL   | 1    |                  |      |       |

|                             |                              | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = |                                                      | 18P8A, 18P8B           |       |      |                  |      |       |

|                             |                              | V <sub>IH</sub> or                           | I <sub>OL</sub> = 24 mA                              | 18P8L, 18P8AL          | COM.F |      |                  |      | Volts |

| VOL                         | Output LOW Voltage           | VIL                                          | I <sub>OL</sub> = 12 mA                              | 18P8Q                  | 1     |      |                  | 0.50 |       |

|                             |                              |                                              | I <sub>OL</sub> = 12 mA                              | A, B. AL. L            |       | 1    |                  |      |       |

|                             |                              |                                              | IOL = 8 mA                                           | 18P8Q                  | MIL   |      |                  |      |       |

| V <sub>IH</sub><br>(Note 2) | Input HIGH level             | Guaranteed                                   | Guaranteed Input Logical HIGH Voltage for All Inputs |                        |       |      |                  |      | Volts |

| V <sub>IL</sub><br>(Note 2) | Input LOW level              | Guaranteed                                   | Input Logical LO                                     |                        |       | 0.8  | Volts            |      |       |

| l <sub>IL</sub>             | Input LOW Current            | V <sub>CC</sub> = Max.,                      | V <sub>CC</sub> = Max., V <sub>IN</sub> = 0.40 V     |                        |       |      |                  | 100  | μА    |

| liH                         | Input HIGH Current           | V <sub>CC</sub> = Max.,                      | V <sub>CC</sub> = Max., V <sub>IN</sub> = 2.7 V      |                        |       |      |                  | 25   | μА    |

| կ                           | Input HIGH Current           | V <sub>CC</sub> = Max.,                      | V <sub>IN</sub> = 5.5 V                              |                        |       |      |                  | 1.0  | mA    |

| Isc                         | Output Short Circuit Current | V <sub>CC</sub> = Max.,                      | V <sub>OUT</sub> = 0.5 V (N                          |                        | -30   | -60  | -90              | mA   |       |

|                             |                              |                                              |                                                      | 18P8A, 18P8B           |       |      |                  | 180  |       |

| Icc                         | Power Supply Current         | V <sub>CC</sub> = Max.                       |                                                      | 18P8L, 18P8AL          |       |      | 90               | mA   |       |

|                             |                              | ·                                            | 18P8Q                                                |                        |       |      |                  | 55   | 1     |

| ٧ı                          | Input Clamp Voltage          | V <sub>CC</sub> = Min.,                      | I <sub>IN</sub> = -18 mA                             |                        |       |      | -0.9             | -1.2 | Volts |

| Гозн                        |                              |                                              |                                                      | V <sub>O</sub> = 2.7 V |       |      |                  | 100  |       |

| lozu                        | Output Leakage Current       | VCC = Max.,                                  | AIN - AIFor AIH                                      | V <sub>O</sub> = 0.4 V |       | i -  |                  | ~250 | μΑ    |

Notes: 1. Typical limits are at  $V_{CC} = 5.0 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second.

VOUT = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

#### Capacitance

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions                      | Тур. | Units |

|---------------------|--------------------------|--------------------------------------|------|-------|

| CIN                 | Input Capacitance        | V <sub>IN</sub> = 2.0 V @ f = 1 MHz  | 6    | nF    |

| C <sub>OUT</sub>    | Output Capacitance       | V <sub>OUT</sub> = 2.0 V @ f = 1 MHz | 9    | ا ا   |

Note: These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

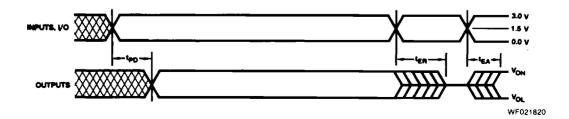

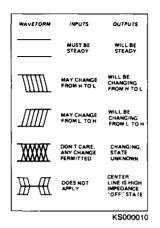

# **Key to Switching Waveforms**

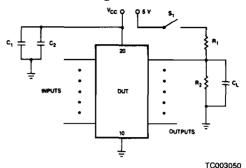

# **Switching Test Circuit**

Note: C1 and C2 are to bypass VCC to ground during testing.

| TEST OUTPUT LOADS     |                |     |                |            |                     |                     |                     |  |  |  |  |  |

|-----------------------|----------------|-----|----------------|------------|---------------------|---------------------|---------------------|--|--|--|--|--|

| Power                 | R <sub>1</sub> | (Ω) | R <sub>2</sub> | $(\Omega)$ | C <sub>L</sub> (pF) | C <sub>1</sub> (µF) | C <sub>2</sub> (µF) |  |  |  |  |  |

| Grade                 | STD            | APL | STD            | APL        | STD/APL             | STD/APL             | STD/APL             |  |  |  |  |  |

| 18P8B<br>A<br>AL<br>L | 200            | 390 | 390            | 750        | 50                  | 0.1                 | 0.01                |  |  |  |  |  |

| 18P8Q                 | 390            | 600 | 750            | 1200       | 50                  | 0.1                 | 0.01                |  |  |  |  |  |

STD = AMD "Standard" products

APL = AMD "Approved Products List" products

# Switching Characteristics over operating range unless otherwise specified; included in Group A, Subgroup 9, 10, 11 tests unless otherwise noted

|                 |                         |      | Commercial |      |                |      |             |      | Military/Extended |      |          |      |         |       |

|-----------------|-------------------------|------|------------|------|----------------|------|-------------|------|-------------------|------|----------|------|---------|-------|

|                 |                         | 181  | 18P8B      |      | 18P8B 18P8A/AL |      | 18P8L/Q 188 |      | 18P8B             |      | 18P8A/AL |      | 18P8L/Q |       |

| Parameter       | Description             | Тур. | Max.       | Тур. | Max.           | Тур. | Max.        | Тур. | Max.              | Тур. | Max.     | Тур. | Max.    | Units |

| teo             | input to Output Delay   | 12   | 15         | 15   | 25             | 25   | 35          | 12   | 20                | 15   | 30       | 25   | 40      | ns    |

| t <sub>EA</sub> | Input to Output Enable  | 12   | 15         | 15   | 25             | 25   | 35          | 12   | 20                | 15   | 30       | 25   | 40      | ns    |

| ten             | Input to Output Disable | 12   | 15         | 15   | 25             | 25   | 35          | 12   | 20                | 15   | 30       | 25   | 40      | ns    |

Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0 V and T<sub>A</sub> = 25°C.

2. tp<sub>D</sub> is tested with switch S<sub>1</sub> closed and C<sub>L</sub> = 50 pF.

3. For three-state output, output enable times are tested with C<sub>L</sub> = 50 pF to the 1.5 V level; S<sub>1</sub> is open for high-impedance to HIGH tests and closed for high-impedance to LOW tests. Output disable times are tested with C<sub>L</sub> = 5 pF. HIGH to high-impedance tests are made to an output voltage of VOH - 0.5 V with S1 open; LOW to high-impedance tests are made to the VOL + 0.5 V level with S<sub>1</sub> closed.

# **Switching Waveform**