# Mosaic

Semiconductor

inc.

131,072 x 8 CMOS High Speed Static RAM

#### **Features**

Fast Access Times of 85/100/120 ns JEDEC Standard 32 pin DIL footprint VIL™ High Density Package Available Low Power Standby 3mW (typ.) 10μW (typ.)(suffix - L)

Low Power Operation 75mW(typ.) 2.0V Data Retention Mode Completely Static Operation **Equal Access and Cycle Times** Battery back-up capability Directly TTL compatible Common data inputs & outputs MIL-STD-883 compliant version available.

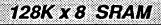

#### **Block Diagram**

# MSM8128-85/10/12

Issue 3.0 : October 1992

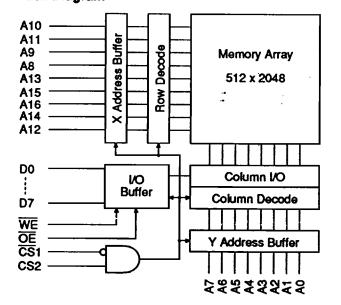

#### Package Details

| Pin Count    | Description                        | Package Type | Material | Pin Out       |

|--------------|------------------------------------|--------------|----------|---------------|

| 32           | 0.6" Dual-in-Line (DIP)            | S            | Ceramic  | JEDEC         |

| 32           | 0.4" Dual-in-Line (DIP)            | Κ            | Ceramic  | JEDEC         |

| 32           | 0.1" Vertical-in-Llne (VIL™)       | V            | Ceramic  | JEDEC         |

| 32           | Bottom Brazed Flat Pack            | G            | Ceramic  | JEDEC         |

| 32           | Extended Leadless Chip Carrier (LC | C) W         | Ceramic  | JEDEC PENDING |

| 32           | J-Leaded Chip Carrier (JLCC)       | J            | Ceramic  | JEDEC PENDING |

| Package deta | nils on nages 687                  |              |          |               |

VIL™ is a trademark of Mosaic Semiconductor Inc. (U.S. Patent Des. 316,251),

# Absolute Maximum Ratings (1)

| Voltage on any pin relative to V <sub>ss</sub> <sup>(2)</sup> | $V_{\tau}$       | -0.5V to +7 | ٧        |

|---------------------------------------------------------------|------------------|-------------|----------|

| Power Dissipation                                             | P <del>,</del>   | 1           | W        |

| Storage Temperature                                           | T <sub>stg</sub> | -55 to +150 | <b>℃</b> |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

(2) Pulse width: - 3.0V for less than 30ns.

## **Recommended Operating Conditions**

|                       |                  | min  | typ | max |                           |

|-----------------------|------------------|------|-----|-----|---------------------------|

| Supply Voltage        | V <sub>∞</sub>   | 4.5  | 5.0 | 5.5 | V                         |

| Input High Voltage    | V <sub>H</sub>   | 2.2  | -   | 5.8 | V                         |

| Input Low Voltage     | V <sub>a</sub> . | -0.3 | -   | 0.8 | V                         |

| Operating Temperature | TÃ               | 0    | -   | 70  | ℃                         |

|                       | T <sub>AL</sub>  | -40  | •   | 85  | °C (8128I)                |

|                       | TAM              | -55  | -   | 125 | °C (8128M,8128MB, 8128MC) |

# DC Electrical Characteristics ( $V_{\infty} = 5.0V \pm 10\%$ , $T_{A} = -55$ °C to +125°C)

| Parameter                      | Symbol                             | Test Condition                                                                                                                                                                                                           | min      | typ  | max        | Unit |

|--------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------------|------|

| Input Leakage Current          | l <sub>u</sub>                     | V <sub>N</sub> =0V to V <sub>cc</sub>                                                                                                                                                                                    | -        | -    | 2          | μА   |

| Output Leakage Current         | ابه                                | CS1=V <sub>H</sub> , CS2=V <sub>R</sub> , V <sub>IO</sub> =0V to V <sub>CC</sub> , OE=V <sub>H</sub>                                                                                                                     | -        | -    | 2          | μΑ   |

| <b>Operating Supply Curren</b> | t I <sub>cc</sub>                  | CS1=V <sub>II</sub> , CS2=V <sub>III</sub> , I <sub>IO</sub> =0mA, I/P's Static                                                                                                                                          | •        | 15   | 30         | mA   |

| Average Supply Current         | <sub>CC1</sub><br>  <sub>CC2</sub> | Min. Cycle, $\overline{\text{CS}}=\text{V}_{\text{E}}$ , $\text{CS2}=\text{V}_{\text{H}}$ , $\text{V}_{\text{N}}=\text{V}_{\text{E}}$ or $\text{V}_{\text{H}}$ 1µs cycle, Duty=100%, $\text{I}_{\text{IO}}=\text{0mA}$ , | •        | 45   | 70         | mA   |

| ,                              |                                    | <u>CS1</u> ≤0.2V, CS2≥V <sub>cc</sub> -0.2V, 0.2V≥V <sub>m</sub> ≥V <sub>cc</sub> -0.2V                                                                                                                                  | •        | 15   | 30         | mΑ   |

| Standby Supply Current         | l <sub>se</sub>                    | CS1=V <sub>H</sub> , CS2=V <sub>L</sub> , I/P's static                                                                                                                                                                   | <b>-</b> | 1    | 3          | mΑ   |

|                                | SB1                                | <u>CS1</u> ≥V <sub>cc</sub> -0.2V, 0.2V≥CS2≥V <sub>cc</sub> -0.2V, V <sub>n</sub> ≥0V                                                                                                                                    | -        | 0.02 | 2          | mΑ   |

| -L Part                        | I <sub>S82</sub>                   | <u>CS1</u> ≥V <sub>∞</sub> -0.2V, 0.2V≥CS2≥V <sub>∞</sub> -0.2V, V <sub>M</sub> ≥0V                                                                                                                                      | -        | 2    | <b>750</b> | μА   |

| Output Voltage                 | Voc                                | l <sub>ot</sub> =2.1mA                                                                                                                                                                                                   | -        | -    | 0.4        | ٧    |

|                                | V <sub>OH</sub>                    | I <sub>oH</sub> =-1.0mA                                                                                                                                                                                                  | 2.4      | -    | -          | V    |

Typical values are at V<sub>cc</sub>=5.0V,T<sub>A</sub>=25°C and specified loading.

# Capacitance (V\_=5V±10%,T\_=25°C)

| Parameter                           | Symbol          | Test Condition            | typ | max     | Unit     |   |

|-------------------------------------|-----------------|---------------------------|-----|---------|----------|---|

| Input Capacitance: I/O Capacitance: | C <sub>IN</sub> | $V_{N} = 0V$ $V_{N} = 0V$ | -   | 8<br>10 | pF<br>pF | - |

Note: This parameter is sampled and not 100% tested.

#### **AC Test Conditions**

- \* Input pulse levels: 0V to 3.0V

- \* Input rise and fall times: 5ns

- \* Input and Output timing reference levels: 1.5V

- \* Output load: 1 TTL gate + 100pF

- \* V\_=5V±10%

**Electrical Characteristics & Recommended AC Operating Conditions**

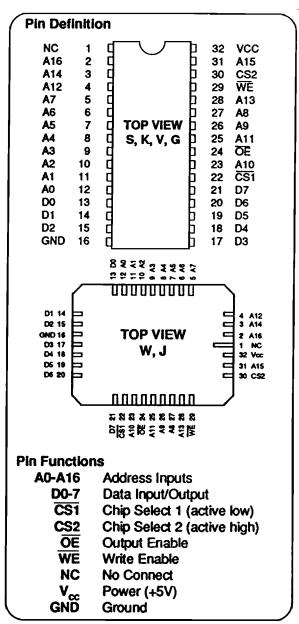

| Read | Cycle |

|------|-------|

|------|-------|

| -                                    |                  | 85  |             | 10  |     | 12  |     | -    |       |

|--------------------------------------|------------------|-----|-------------|-----|-----|-----|-----|------|-------|

| Parameter                            | Symbol           | min | max         | min | max | min | max | Unit | Notes |

| Read Cycle Time                      | t <sub>RC</sub>  | 85  | -           | 100 | -   | 120 | -   | ns   |       |

| Address Access Time                  | t                | -   | 85          | -   | 100 | -   | 120 | ns   |       |

| Chip Selection (CS1) Access Time     | t <sub>co1</sub> | -   | 85          | •   | 100 | -   | 120 | ns   |       |

| Chip Selection (CS2) Access Time     | tcoe             | -   | 85          | •   | 100 | -   | 120 | ns   |       |

| Output Enable to Output Valid        | to∈              | -   | 45          | •   | 50  | -   | 60  | ns   |       |

| Output Hold from Address Change      | toH              | 10  | -           | 15  | -   | 15  | -   | ns   |       |

| Chip Selection (CS1) to O/P in low Z | t <sub>LZ1</sub> | 10  | -           | 10  | -   | 10  | -   | ns   | 2     |

| Chip Selection (CS2) to O/P in low Z | t <sub>LZ2</sub> | 10  | -           | 10  | -   | 10  | -   | ns   | 2     |

| Output Enable to Output in Low Z     | toz              | 5   | -           | 5   | -   | 5   | -   | ns   | 2     |

| Chip Deselection (CS1) to O/P high Z | t <sub>HZ1</sub> | 0   | 30          | 0   | 35  | 0   | 45  | ns   | 2     |

| Chip Deselection (CS2) to O/P high Z | t <sub>HZ2</sub> | 0   | <b>30</b> · | 0   | 35  | 0   | 45  | ns   | 2     |

| Output Disable to Output in High Z   | toHZ             | 0   | 30          | 0   | 35  | 0   | 45  | ns   | 2     |

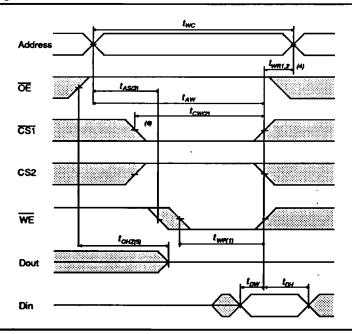

## Read Cycle Timing Waveform (1)

#### Notes:

- (1) WE is High for Read Cycle.

- (2) t<sub>tZ</sub> and t<sub>OtZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels. At any given temperature and voltage condition, t<sub>tZ</sub> max is less than t<sub>tZ</sub> min both for a given device and from device to device. This parameter is sampled and not 100% tested.

| Write Cycle                     |                   | •   |     |     |     |     |     |        |       |

|---------------------------------|-------------------|-----|-----|-----|-----|-----|-----|--------|-------|

|                                 |                   | 85  |     | 10  |     | 12  |     |        |       |

| Parameter                       | Symbol            | min | max | min | max | min | max | Unit I | Notes |

| Write Cycle Time                | t <sub>wc</sub>   | 85  | -   | 100 | -   | 120 | -   | ns     |       |

| Chip Selection to End of Write  | t <sub>cw</sub>   | 75  | -   | 90  | -   | 100 | -   | ns     |       |

| Address Valid to End of Write   | t <sub>AW</sub>   | 75  | -   | 90  | -   | 100 | -   | ns     |       |

| Address Setup Time              | t <sub>AS</sub> " | 0   | -   | 0   | -   | 0   | -   | ∙ns    |       |

| Write Pulse Width               | t <sub>we</sub>   | 65  | -   | 75  | -   | 90  | -   | ns     |       |

| Write Recovery Time             | t <sub>wn</sub>   | 5   | -   | 5   | -   | 10  | -   | ns     |       |

| •                               | t <sub>wr2</sub>  | 10  | -   | 10  | -   | 15  | -   | ns (   | (11)  |

| Write to Output in High Z       | twiz              | 0   | 30  | 0   | 35  | 0   | 40  | ns (   | 10)   |

| Data to Write Time Overlap      | t <sub>DW</sub>   | 35  | •   | 40  | -   | 50  | -   | ns     | ,     |

| Data Hold from Write Time       | t <sub>DH</sub>   | 0   | -   | 0   | -   | 0   | -   | ns     |       |

| Output Active from End of Write | tow               | 5   | -   | 10  | -   | 10  | -   | ns (   | (10)  |

# Write Cycle No.1 Timing Waveform

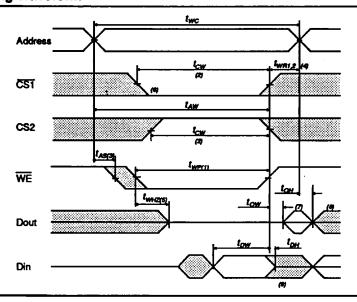

# Write Cycle No.2 Timing Waveform (12)

### **AC Characteristics Notes**

(1) Awrite occurs during the overlap of a low CS1, a high CS2 and a low WE. A write begins at the latest transition among  $\overline{\text{CS1}}$  going low, CS2 going high and  $\overline{\text{WE}}$  going low. A write ends at the earliest transition among  $\overline{\text{CS1}}$  going high, CS2 going low and WE going high. two is measured from the beginning of write to the end of write.

(2) t<sub>cw</sub> is measured from the later of CS1 going low or CS2 going high to the end of write.

(3) tas is measured from the address valid to the beginning of write.

(4) t<sub>wn</sub> is measured from the earlier of CS1 or WE going high or CS2 going high to the end of write cycle.

(5) During this period, I/O pins are in the output state. Input signals out of phase must not be applied.

(6) If CSI goes low simultaneously with WE going low or after WE going low, outputs remain in high impedance state.

(7) Dout is in the same phase as written data of this write cycle.

(8) Dout is the read data of next address.

(9) If CS1 is low and CS2 is high during this period, I/O pins are in the output state. Input signals out of phase must not be applied to I/O pins.

(10) This parameter is sampled and not 100% tested.

(11) This value is measured from CS2 going low to the end of the write cycle.

(12) OE is continuously low. (OE=V.,)

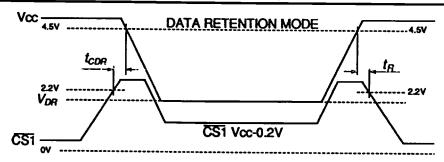

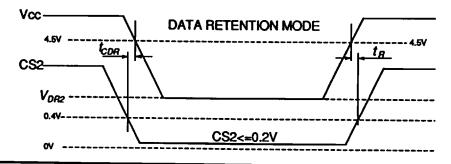

Low V Data Retention Characteristics - L Version Only (T\_=-55°C to +125°C) Parameter Symbol Test Condition min Unit typ max V<sub>∞</sub> for Data Retention  $\overline{CS1} \ge V_{cc}$ -0.2V,  $CS2 \ge V_{cc}$ -0.2V or 0V ≤ CS2 ≤ 0.2V. V<sub>w</sub> ≥ 0V 2.0 ٧ **Data Retention Current**  $V_{cc}=3.0V, V_{N} \ge 0V, \overline{CS1} \ge V_{cc}-0.2V,$ CCDR  $CS2 \ge V_{cc}$ -0.2V or 0V  $\le CS2 \le 0.2$ V. 350 μΑ Chip Deselect to Data Retention  $t_{CDR}$ See Retention Waveform 0 ns **Operation Recovery Time** See Retention Waveform 5 ms

Notes (1) 20µA max at T,=0 to 40°C.

(2) CS2 controls address buffer, WE buffer, CS1 buffer and OE buffer. If CS2 controls data retention mode, Vin levels (WE,OE,CS1,IO) can be in the high impedance state. If CS1 controls Data Retention mode, CS2 must be  $\geq V_{cc}$  - 0.2V or 0V  $\leq$  CS2  $\leq$  0.2V. The other input levels (address,  $\overline{WE}, \overline{OE}, VO$ ) can be in the high impedance state.

# Low V Data Retention Timing Waveform 1 (CS1 controlled)

# Low V<sub>∞</sub> Data Retention Timing Waveform 2 (CS2 controlled)

ISSUE 3.0 : OCTOBER 1992 MSM8128-85/10/12

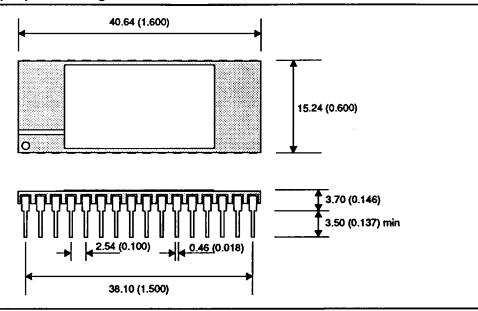

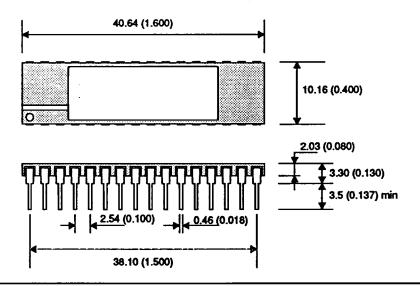

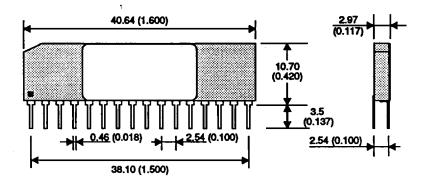

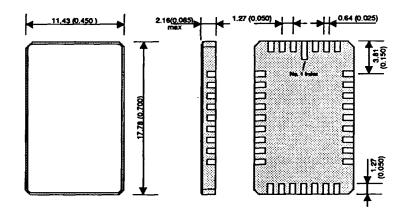

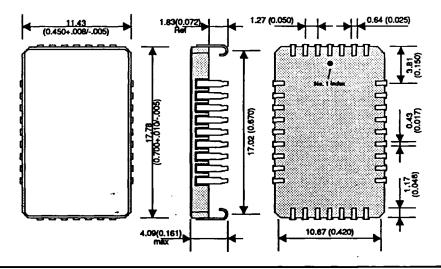

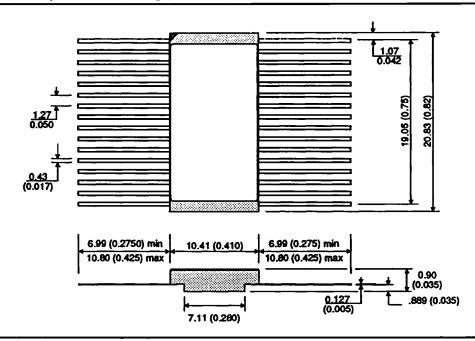

## Package Details Dimensions in mm (inches.) Tolerance on all dimensions ± 0.254 (0.010)

# 32 pin 0.6" Dual-in-Line (DIP) - 'S' Package

32 pin 0.4" Dual-in-Line (DIP) - 'K' Package

32 pin 0.1" Vertical-in-Line (VIL™) - "V" Package

## 32 pin Extended Leadless Chip Carrier (LCC) - 'W' Package

## 32 pin Extended 'J' Leaded Chip Carrier (JLCC) - 'J' Package

# 32 pin Ceramic Flatpack - 'G' Package

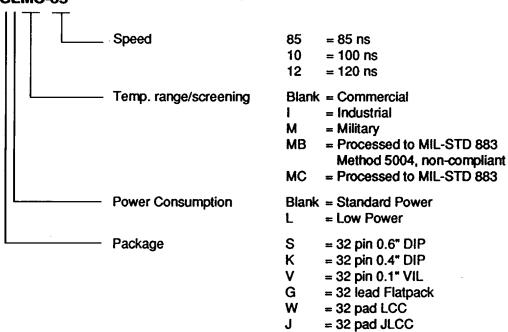

## Ordering Information

## MSM8128SLMC-85

Note: For more information regarding screening flows contact Mosaic Semiconductor Inc. for a 'Screening Flow **Applications Note.**'

Semiconductor

Inc.