### PA7540 PEEL™ Array

### **Programmable Electrically Erasable Logic Array**

### Most Powerful 24-pin PLD Available

- 20 I/Os, 2 inputs/clocks, 40 registers/latches

- 40 logic cell output functions

- PLA structure with true product-term sharing

- Logic functions and registers can be I/O-buried

### Ideal for Combinatorial, Synchronous and Asynchronous Logic Applications

- Integration of multiple PLDs and random logic

- Buried counters, complex state-machines

- Comparators, decoders, multiplexers and other widegate functions

#### **High-Speed Commercial and Industrial Versions**

- As fast as 10ns/15ns (tpdi/tpdx), 71.4MHz (f<sub>MAX</sub>)

- Industrial grade available for 4.5 to 5.5V V<sub>CC</sub> and -40 to +85 °C temperatures

### **General Description**

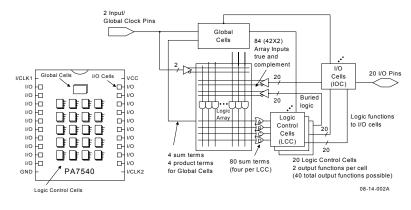

The PA7540 is a member of the Programmable Electrically Erasable Logic (PEEL™) Array family based on ICT's CMOS EEPROM technology. PEEL™ Arrays free designers from the limitations of ordinary PLDs by providing the architectural flexibility and speed needed for today's programmable logic designs. The PA7540 is by far the most powerful 24-pin PLD available today with 20 I/O pins, 2 input/global-clocks and 40 registers/latches (20 buried logic cells and 20 I/O registers/latches). Its logic array implements 84 sum-of-products logic functions. The PA7540's logic and I/O cells (LCCs, IOCs) are extremely flexible offering two output functions per cell (a total of 40 for all 20 logic cells). Logic cells are configurable as D, T, and JK registers with independent or global clocks, resets,

#### **CMOS Electrically Erasable Technology**

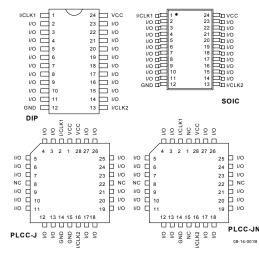

- Reprogrammable in 24-pin DIP, SOIC and 28-pin PLCC packages

- Optional JN package for 22V10 power/ground compatibility

#### Flexible Logic Cell

- 2 output functions per logic cell

- D,T and JK registers with special features

- Independent or global clocks, resets, presets, clock polarity and output enables

- Sum-of-products logic for output enables

#### **Development and Programmer Support**

- Anachip's WinPLACE Development Software

- Fitters for ABEL, CUPL and other software

- Programming support by popular third-party programmers

presets, clock polarity, and other features, making the PA7540 suitable for a variety of combinatorial, synchronous and asynchronous logic applications. With pin compatibility and super-set functionality to most 24-pin PLDs, (22V10, EP610/630, GAL6002), the PA7540 can implement designs that exceed the architectures of such devices. The PA7540 supports speeds as fast as 10ns/15ns (tpdi/tpdx) and 71.46MHz ( $f_{MAX}$ ) at moderate power consumption 80mA (55mA typical). Packaging includes 24-pin DIP, SOIC and 28-pin PLCC (see Figure 1). Anachip and popular third-party development tool manufacturers provide development and programming support for the PA7540.

Figure 1. Pin Configuration

Figure 2. Block Diagram

### Inside the Logic Array

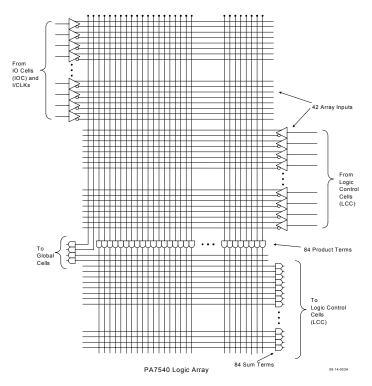

The heart of the PEEL™ Array architecture is based on a logic array structure similar to that of a PLA (programmable AND, programmable OR). The logic array implements all logic functions and provides interconnection and control of the cells. In the PA7540 PEEL™ Array, 42 inputs are available into the array from the I/O cells and input/global-clock pins.

All inputs provide both true and complement signals, which can be programmed to any product term in the array. The PA7540 PEEL™ Arrays contains 84 product terms. All product terms (with the exception of certain ones fed to the global cells) can be programmably connected to any of the sum-terms of the logic control cells (four sum-terms per logic control cell). Product-terms and sum-terms are also routed to the global cells for control purposes. Figure 3 shows a detailed view of the logic array structure.

Figure 3 PA7540 Logic Array

### **True Product-Term Sharing**

The PEEL™ logic array provides several advantages over common PLD logic arrays. First, it allows for true product-term sharing, not simply product-term steering, as commonly found in other CPLDs. Product term sharing ensures that product-terms are used where they are

needed and not left unutilized or duplicated. Secondly, the sum-of-products functions provided to the logic cells can be used for clocks, resets, presets and output enables instead of just simple product-term control.

The PEEL™ logic array can also implement logic functions with many product terms within a single-level delay. For example a 16-bit comparator needs 32 shared product terms to implement 16 exclusive-OR functions. The PEEL™ logic array easily handles this in a single level delay. Other PLDs/CPLDs either run out of product-terms or require expanders or additional logic levels that often slow performance and skew timing.

### Logic Control Cell (LCC)

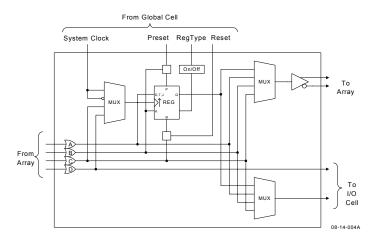

Logic Control Cells (LCC) are used to allocate and control the logic functions created in the logic array. Each LCC has four primary inputs and three outputs. The inputs to each LCC are complete sum-of-product logic functions from the array, which can be used to implement combinatorial and sequential logic functions, and to control LCC registers and I/O cell output enables.

Figure 4. Logic Control Cell Block Diagram

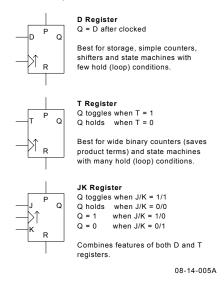

As shown in Figure 4, the LCC is made up of three signal routing multiplexers and a versatile register with synchronous or asynchronous D, T, or JK registers (clocked-SR registers, which are a subset of JK, are also possible). See Figure 5. EEPROM memory cells are used for programming the desired configuration. Four sum-of-product logic functions (SUM terms A, B, C and D) are fed into each LCC from the logic array. Each SUM term can be selectively used for multiple functions as listed below.

Sum-A = D, T, J or Sum-A Sum-B = Preset, K or Sum-B Sum-C = Reset, Clock, Sum-C Sum-D = Clock, Output Enable

### Figure 5. LCC Register Types

SUM-A can serve as the D, T, or J input of the register or a combinatorial path. SUM-B can serve as the K input, or the preset to the register, or a combinatorial path. SUM-C can be the clock, the reset to the register, or a combinatorial path. SUM-D can be the clock to the register or the output enable for the connected I/O cell. Note that the sums controlling clocks, resets, presets and output enables are complete sum-of-product functions, not just product terms as with most other PLDs. This also means that any input or I/O pin can be used as a clock or other control function.

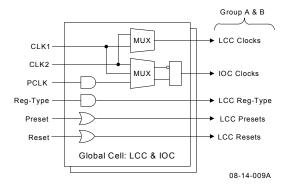

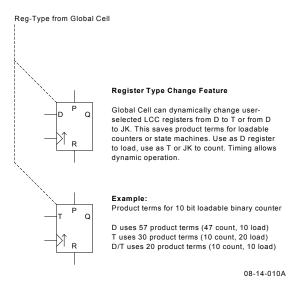

Several signals from the global cell are provided primarily for synchronous (global) register control. The global cell signals are routed to all LCCs. These signals include a high-speed clock of positive or negative polarity, global preset and reset, and a special register-type control that selectively allows dynamic switching of register type. This last feature is especially useful for saving product terms when implementing loadable counters and state machines by dynamically switching from D-type registers to load and T-type registers to count (see Figure 10).

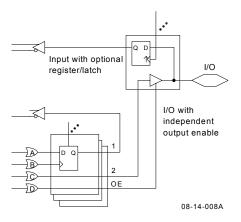

### **Multiple Outputs Per Logic Cell**

An important feature of the logic control cell is its capability to have multiple output functions per cell, each operating independently. As shown in Figure 4, two of the three outputs can select the Q output from the register or the Sum A, B or C combinatorial paths. Thus, one LCC output

can be registered, one output can be combinatorial and the third, an output enable. The multi-function PEEL™ Array logic cells are equivalent to two or three macrocells of other PLDs, which have only one output per cell. They also allow registers to be truly buried from I/O pins without limiting them to input-only (see Figure 8).

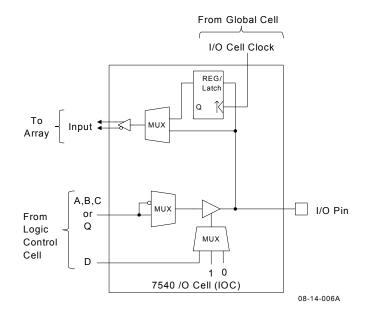

Figure 6. I/O Cell Block Diagram

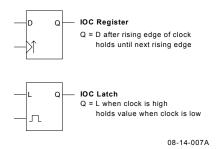

Figure 7. IOC Register Configurations

### I/O Cell (IOC)

All PEEL™ Arrays have I/O cells (IOC) as shown above in Figure 6. Inputs to the IOCs can be fed from any of the LCCs in the array. Each IOC consists of routing and control multiplexers, an input register/transparent latch, a three-state buffer and an output polarity control. The register/ latch can be clocked from a variety of sources determined by the global cell. It can also be bypassed for a non-registered input. The combination of LCC and IOC allows for multiple buried registers and logic paths. (See Figure 8).

Figure 8. LCC & IOC With Two Outputs

### **Global Cells**

The global cells, shown in Figure 9, are used to direct global clock signals and/or control terms to the LCCs and IOCs. The global cells allow a clock to be selected from the CLK1 pin, CLK2 pin, or a product term from the logic array (PCLK). They also provide polarity control for IOC clocks enabling rising or falling clock edges for input registers/latches. Note that each individual LCC clock has its own polarity control. The global cell includes sum-ofproducts control terms for global reset and preset, and a fast product term control for LCC register-type, used to save product terms for loadable counters and state machines (see Figure 10). The PA7540 provides two global cells that divides the LCC and IOCs into two groups, A and B. Half of the LCCs and IOCs use global cell A, half use global cell B. This means, for instance, two high-speed global clocks can be used among the LCCs.

### **PEEL™ Array Development Support**

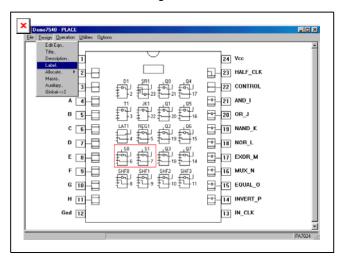

Development support for PEEL™ Arrays is provided by Anachip and manufacturers of popular development tools. Anachip offers the powerful WinPLACE Development Software (free to qualified PLD designers).

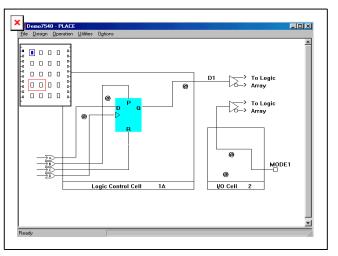

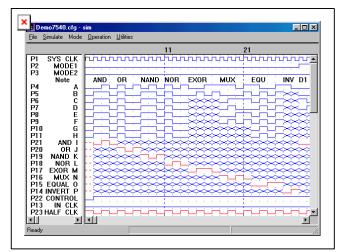

The PLACE software includes an architectural editor, logic compiler, waveform simulator, documentation utility and a programmer interface. The PLACE editor graphically illustrates and controls the PEEL™ Array's architecture, making the overall design easy to understand, while allowing the effectiveness of boolean logic equations, state machine design and truth table entry. The PLACE compiler performs logic transformation and reduction, making it possible to specify equations in almost any fashion and fit the most logic possible in every design. PLACE also provides a multi-level logic simulator allowing external and

Figure 9. Global Cells

Figure 10. Register Type Change Feature

internal signals to be simulated and analyzed via a waveform display.(See Figures 10)

PEEL™ Array development is also supported by popular development tools, such as ABEL via Anachip's PEEL™ Array fitters. A special smart translator utility adds the capability to directly convert JEDEC files for other devices into equivalent JEDEC files for pin-compatible PEEL™ Arrays.

### **Programming**

PEEL™ Arrays are EE-reprogrammable in all package types, plastic-DIP, PLCC and SOIC. This makes them an ideal development vehicle for the lab. EE - reprogrammability is also useful for production, allowing

reprogrammability is also useful for production, allowing unexpected changes to be made quickly and without waste.

Programming of PEEL™ Arrays is supported by many popular third party programmers.

### **Design Security and Signature Word**

The PEEL™ Arrays provide a special EEPROM security bit that prevents unauthorized reading or copying of designs. Once set, the programmed bits of the PEEL™ Arrays cannot be accessed until the entire chip has been electrically erased. Another programming feature, signature word, allows a user-definable code to be programmed into the PEEL™ Array. The code can be read back even after the security bit has been set. The signature word can be used to identify the pattern programmed in the device or to record the design revision.

Figure 11 - WinPLACE Architectural Editor for PA7540

Figure 12 - WinPLACE LCC and IOC screen

Figure 13 - WinPLACE waveform and simulator screen

This device has been designed and tested for the specified operating ranges. Improper operation outside of these levels is not guaranteed. Exposure to absolute maximum ratings may cause permanent damage.

**Table 1. Absolute Maximum Ratings**

| Symbol                          | Parameter                  | Conditions                                   | Ratings                       | Unit |

|---------------------------------|----------------------------|----------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>                 | Supply Voltage             | Relative to Ground                           | -0.5 to + 7.0                 | V    |

| V <sub>I</sub> , V <sub>O</sub> | Voltage Applied to Any Pin | Relative to Ground <sup>1</sup>              | -0.5 to V <sub>CC</sub> + 0.6 | V    |

| Io                              | Output Current             | Per pin (I <sub>OL</sub> , I <sub>OH</sub> ) | ±25                           | mA   |

| T <sub>ST</sub>                 | Storage Temperature        |                                              | -65 to + 150                  | °C   |

| T <sub>LT</sub>                 | Lead Temperature           | Soldering 10 seconds                         | +300                          | °C   |

### **Table 2. Operating Ranges**

| Symbol            | Parameter                 | Conditions | Min  | Max  | Unit |

|-------------------|---------------------------|------------|------|------|------|

| V                 | Supply Voltage —          | Commercial | 4.75 | 5.25 | V    |

| V <sub>cc</sub>   |                           | Industrial | 4.5  | 5.5  |      |

| т                 | Ambient Temperature -     | Commercial | 0    | +70  | °C   |

| T <sub>A</sub>    |                           | Industrial | -40  | +85  |      |

| T <sub>R</sub>    | Clock Rise Time           | See Note 2 |      | 20   | ns   |

| T <sub>F</sub>    | Clock Fall Time           | See Note 2 |      | 20   | ns   |

| T <sub>RVCC</sub> | V <sub>CC</sub> Rise Time | See Note 2 |      | 250  | ms   |

#### Table 3. D.C. Electrical Characteristics

### Over the Operating Range

| Symbol                        | Parameter                                    | Conditions                                                                         |      | Min                     | Max                   | Unit |

|-------------------------------|----------------------------------------------|------------------------------------------------------------------------------------|------|-------------------------|-----------------------|------|

| V <sub>OH</sub>               | Output HIGH Voltage - TTL                    | V <sub>CC</sub> = Min, I <sub>OH</sub> = -4.0mA                                    |      | 2.4                     |                       | V    |

| V <sub>OHC</sub>              | Output HIGH Voltage -<br>CMOS                | V <sub>CC</sub> = Min, I <sub>OH</sub> = -10μA                                     |      | V <sub>CC</sub> - 0.3   |                       | V    |

| V <sub>OL</sub>               | Output LOW Voltage - TTL                     | V <sub>CC</sub> = Min, I <sub>OL</sub> = 16mA                                      |      |                         | 0.5                   | V    |

| V <sub>OLC</sub>              | Output LOW Voltage -<br>CMOS                 | $V_{CC}$ = Min, $I_{OL}$ = -10 $\mu$ A                                             |      |                         | 0.15                  | V    |

| V <sub>IH</sub>               | Input HIGH Level                             |                                                                                    |      | 2.0                     | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>               | Input LOW Level                              |                                                                                    |      | -0.3                    | 0.8                   | V    |

| I <sub>IL</sub>               | Input Leakage Current                        | $V_{CC}$ = Max, GND $\leq V_{IN} \leq V_{CC}$                                      |      |                         | ±10                   | μΑ   |

| l <sub>oz</sub>               | Output Leakage Current                       | I/O = High-Z, GND ≤V <sub>O</sub> ≤V <sub>CC</sub>                                 |      |                         | ±10                   | μΑ   |

| I <sub>sc</sub>               | Output Short Circuit<br>Current <sup>4</sup> | V <sub>CC</sub> = 5V, V <sub>O</sub> = 0.5V, TA= 25°C                              |      | -30                     | -120                  | mA   |

| I <sub>cc</sub> <sup>11</sup> |                                              | $V_{IN}$ = 0V or $V_{CC}^{3,11}$<br>f = 25MHz<br>All outputs disabled <sup>4</sup> | -15  | 55 (typ.) <sup>18</sup> | 80                    | - mA |

| Icc                           | V <sub>CC</sub> Current                      |                                                                                    | I-15 |                         | 90                    |      |

| C <sub>IN</sub> <sup>7</sup>  | Input Capacitance⁵                           | T <sub>A</sub> = 25°C, V <sub>CC</sub> = 5.0V @ f = 1 MHz                          |      |                         | 6                     | pF   |

| C <sub>OUT</sub> <sup>7</sup> | Output Capacitance <sup>5</sup>              |                                                                                    |      |                         | 12                    | pF   |

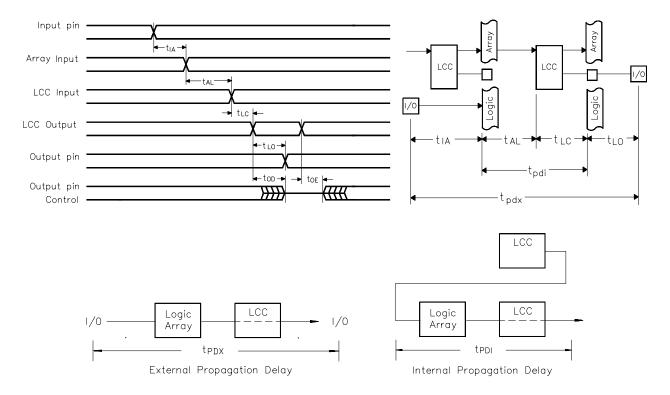

**Table 4. A.C Electrical Characteristics Combinatorial**

### Over the Operating Range

| Symbol                            | Parameter <sup>6,12</sup>                                                                          |     | -15/I-15 |      |

|-----------------------------------|----------------------------------------------------------------------------------------------------|-----|----------|------|

| Зушьог                            | raiailietei                                                                                        | Min | Max      | Unit |

| t <sub>PDI</sub>                  | Propagation delay Internal (t <sub>AL</sub> + t <sub>LC</sub> )                                    |     | 10       | ns   |

| t <sub>PDX</sub>                  | Propagation delay External (t <sub>IA</sub> + t <sub>AL</sub> +t <sub>LC</sub> + t <sub>LO</sub> ) |     | 15       | ns   |

| t <sub>IA</sub>                   | Input or I/O pin to array input                                                                    |     | 2        | ns   |

| t <sub>AL</sub>                   | Array input to LCC                                                                                 |     | 9        | ns   |

| tLC                               | LCC input to LCC output <sup>10</sup>                                                              |     | 1        | ns   |

| t <sub>LO</sub>                   | LCC output to output pin                                                                           |     | 3        | ns   |

| t <sub>OD</sub> , t <sub>OE</sub> | Output Disable, Enable from LCC output <sup>7</sup>                                                |     | 3        | ns   |

| t <sub>OX</sub>                   | Output Disable, Enable from input pin <sup>7</sup>                                                 |     | 15       | ns   |

This device has been designed and tested for the recommended operating conditions. Proper operation outside of these levels is not guaranteed. Exposure to absolute maximum ratings may cause permanent damage

Figure 14. Combinatorial Timing - Waveforms and Block Diagram

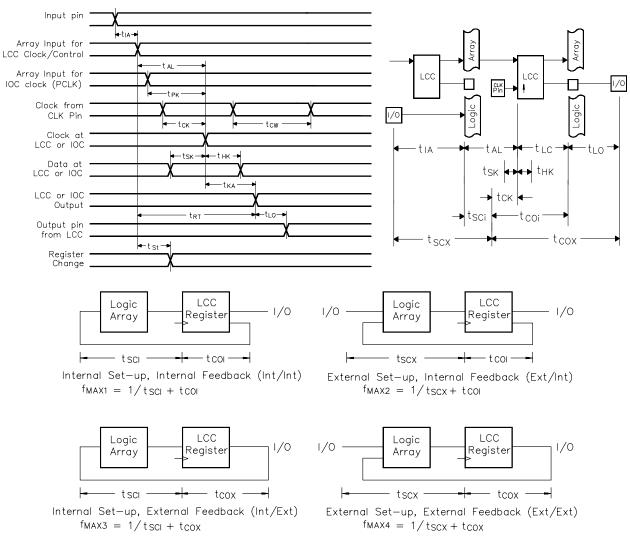

### Table 5. A.C. Electrical Characteristics Sequential

| Cumbal             | Parameter <sup>6,1</sup>                                                                                | -15 | -15/I-15 |      |

|--------------------|---------------------------------------------------------------------------------------------------------|-----|----------|------|

| Symbol             |                                                                                                         | Min | Max      | Unit |

| tscı               | Internal set-up to system clock <sup>8</sup> - LCC <sup>14</sup> $(t_{AL} + t_{SK} + t_{LC} - t_{CK})$  | 6   |          | ns   |

| t <sub>SCX</sub>   | Input <sup>16</sup> (EXT.) set-up to system clock, - LCC ( $t_{IA}$ + $t_{SCI}$ )                       | 8   |          | ns   |

| tcoı               | System-clock to Array Int LCC/IOC/INC <sup>14</sup> (t <sub>CK</sub> +t <sub>LC</sub> )                 |     | 8        | ns   |

| t <sub>COX</sub>   | System-clock to Output Ext LCC (t <sub>COI</sub> + t <sub>LO</sub> )                                    |     | 12       | ns   |

| t <sub>HX</sub>    | Input hold time from system clock - LCC                                                                 | 0   |          | ns   |

| tsĸ                | LCC Input set-up to async. clock <sup>13</sup> - LCC                                                    | 3   |          | ns   |

| t <sub>AK</sub>    | Clock at LCC or IOC - LCC output                                                                        | 1   |          | ns   |

| t <sub>HK</sub>    | LCC input hold time from system clock - LCC                                                             | 4   |          | ns   |

| t <sub>SI</sub>    | Input set-up to system clock - IOC/INC <sup>14</sup> (t <sub>SK</sub> - t <sub>CK</sub> )               | 0   |          | ns   |

| t <sub>HI</sub>    | Input hold time from system clock - IOC/INC (t <sub>SK</sub> - t <sub>CK</sub> )                        | 4   |          | ns   |

| t <sub>PK</sub>    | Array input to IOC PCLK clock                                                                           |     | 6        | ns   |

| t <sub>SPI</sub>   | Input set-up to PCLK clock <sup>17</sup> - IOC/INC (t <sub>SK</sub> -t <sub>PK</sub> -t <sub>IA</sub> ) | 0   |          | ns   |

| t <sub>HPI</sub>   | Input hold from PCLK clock <sup>17</sup> - IOC/INC (t <sub>PK</sub> +t <sub>IA</sub> -t <sub>SK</sub> ) | 5   |          | ns   |

| tck                | System-clock delay to LCC/IOC/INC                                                                       |     | 7        | ns   |

| t <sub>CW</sub>    | System-clock low or high pulse width                                                                    | 7   |          | ns   |

| f <sub>MAX1</sub>  | Max. system-clock frequency Int/Int $1/(t_{SCI} + t_{COI})$                                             |     | 71.4     | MHz  |

| f <sub>MAX2</sub>  | Max. system-clock frequency Ext/Int 1/(t <sub>SCX</sub> + t <sub>COI</sub> )                            |     | 62.5     | MHz  |

| f <sub>MAX3</sub>  | Max. system-clock frequency Int/Ext 1/(t <sub>SCI</sub> + t <sub>COX</sub> )                            |     | 55.5     | MHz  |

| f <sub>MAX4</sub>  | Max. system-clock frequency Ext/Ext 1/(t <sub>SCX</sub> + t <sub>COX</sub> )                            |     | 50.0     | MHz  |

| f <sub>TGL</sub>   | Max. system-clock toggle frequency 1/(t <sub>CW</sub> + t <sub>CW</sub> ) <sup>9</sup>                  |     | 71.4     | MHz  |

| t <sub>PR</sub>    | LCC presents/reset to LCC output                                                                        |     | 1        | ns   |

| tsT                | Input to Global Cell present/reset (t <sub>IA</sub> + t <sub>AL</sub> + t <sub>PR</sub> )               |     | 12       | ns   |

| t <sub>AW</sub>    | Asynch. preset/reset pulse width                                                                        | 8   |          | ns   |

| t <sub>RT</sub>    | Input to LCC Reg-Type (RT)                                                                              |     | 6        | ns   |

| t <sub>RTV</sub>   | LCC Reg-Type to LCC output register change                                                              |     | 1        | ns   |

| t <sub>RTC</sub>   | Input to Global Cell register-type change (t <sub>RT</sub> + t <sub>RTV</sub> )                         |     | 7        | ns   |

| t <sub>RW</sub>    | Asynch. Reg-Type pulse width                                                                            | 10  |          | ns   |

| t <sub>RESET</sub> | Power-on reset time for registers in clear state <sup>2</sup>                                           |     | 5        | μs   |

Figure 15. Sequential Timing – Waveforms and Block Diagram

#### **Notes**

- Minimum DC input is -0.5V, however inputs may under-shoot to -2.0V for periods less than 20ns.

- 2.Test points for Clock and Vcc in  $t_{\text{R}},t_{\text{F}},t_{\text{CL}},t_{\text{CH}},$  and  $t_{\text{RESET}}$  are referenced at 10% and 90% levels.

- 3. I/O pins are 0V or Vcc.

- 4. Test one output at a time for a duration of less than 1 sec.

- 5. Capacitances are tested on a sample basis.

- Test conditions assume: signal transition times of 5ns or less from the 10% and 90% points, timing reference levels of 1.5V (unless otherwise specified).

- toe is measured from input transition to V<sub>REF</sub> ±0.1V (See test loads at end of Section 6 for V<sub>REF</sub> value). tod is measured from input transition to V<sub>OH</sub> -0.1V or V<sub>OL</sub> +0.1V.

- 8. DIP: "System-clock" refers to pin 1/13 high speed clocks. PLCC: "System-clock" refers to pin 2/16 high speed clocks.

- 9. For T or JK registers in toggle (divide by 2) operation only.

- 10. For combinatorial and async-clock to LCC output delay.

- 11. ICC for a typical application: This parameter is tested with the device programmed as a 10-bit D-type counter.

- 12. Test loads are specified in Section 5 of the Products Data Book (1999/2000).

- 13. "Async. Clock" refers to the clock from the Sum term (OR gate).

- 14. The "LCC" term indicates that the timing parameter is applied to the LCC register. The "LCC/IOC" term indicates that the timing parameter is applied to both the LCC and IOC registers.

- 16. The term "input" without any reference to another term refers to an (external) input pin.

- 17. The parameter t<sub>SPI</sub> indicates that the PCLK signal to the IOC register is always slower than the data from the pin or input by the absolute value of (t<sub>SK</sub> -t<sub>PK</sub> -t<sub>IA</sub>). This means that no set-up time for the data from the pin or input is required, i.e. the external data and clock can be sent to the device simultaneously. Additionally, the data from the pin must remain stable for t<sub>HPI</sub> time, i.e. to wait for the PCLK signal to arrive at the IOC register.

- 18. Typical (typ) ICC is measured at  $T_A$  = 25° C, freq = 25MHZ,  $V_{CC}$  = 5V

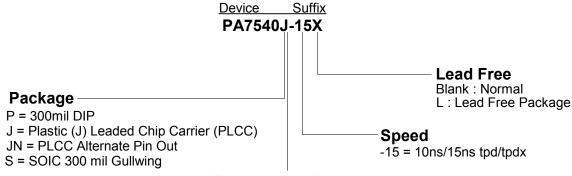

**Table 6. Ordering Information**

| Part Number      | Speed   | Temperature | Package |

|------------------|---------|-------------|---------|

| PA7540P-15 (L)   |         |             | P24     |

| PA7540J-15 (L)   | 10/15ns | С           | J28     |

| PA7540JN-15 (L)  |         | C           | JN28    |

| PA7540S-15 (L)   |         |             | S24     |

| PA7540PI-15 (L)  | 10/15ns |             | P24     |

| PA7540JI-15 (L)  |         | ı           | J28     |

| PA7540JNI-15 (L) |         | '           | JN28    |

| PA7540SI-15 (L)  |         |             | S24     |

Figure 16. Part Number

**Temperature Range**

(Blank) = Commercial 0 to 70°C I = Industrial -40 to +85°C

Anachip Corp. Head Office, 2F, No. 24-2, Industry E. Rd. IV, Science-Based Industrial Park, Hsinchu, 300, Taiwan

Tel: +886-3-5678234 Fax: +886-3-5678368

Email: <u>sales\_usa@anachip.com</u>

Website: <u>http://www.anachip.com</u>

Anachip USA 780 Montague Expressway, #201 San Jose, CA 95131

Tel: (408) 321-9600 Fax: (408) 321-9696

©2004 Anachip Corp.

Anachip reserves the right to make changes in specifications at any time and without notice. The information furnished by Anachip in this publication is believed to be accurate and reliable. However, there is no responsibility assumed by Anachip for its use nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Anachip. Anachip's products are not authorized for use as critical components in life support devices or systems.

Marks bearing <sup>©</sup> or <sup>™</sup> are registered trademarks and trademarks of Anachip Corp.