## Contents

| Page                                                           | Section                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                                              | 1.                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>6</b> 6 6                                                   | 2. 2.1. 2.2. 2.3.                                                                                    | Features of the MSP 3400C Features of the Demodulator and Decoder Sections Features of the DSP-Section Features of the Analog Section                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>7</b><br>7                                                  | <b>3.</b> 3.1.                                                                                       | Application Fields of the MSP 3400C<br>German 2-Carrier System (DUAL FM System)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9 9 9 10 10 10 10 10 10 11 11 11 11 13 13 14 15                | 4. 4.1. 4.1.1. 4.1.2. 4.1.3. 4.1.4. 4.1.5. 4.1.6. 4.1.7. 4.1.8. 4.2. 4.3. 4.3.1. 4.4. 4.5. 4.6. 4.7. | Architecture of the MSP 3400C  Demodulator Block  Analog Sound IF – Input Section  Quadrature Mixers  Lowpass Filtering Block for Mixed Sound IF Signals  Phase and AM Discrimination  Differentiators  Lowpass Filter Block for Demodulated Signals  High Deviation FM Mode  MSPC-Mute Function in the Dual Carrier FM Mode  Analog Section and SCART Switching Facilities  MSP 3400C Audio Baseband Processing  Dual Carrier FM Stereo/Bilingual Detection  Audio PLL and Crystal Specifications  ADR Bus  S-Bus Interface  I <sup>2</sup> S Bus Interface |

| 16<br>17<br>18<br>18<br>18<br>18<br>18<br>19<br>20<br>20<br>21 | 5. 5.1. 5.2. 5.2.1. 5.2.2. 5.2.3. 5.2.4. 5.3. 6. 6.1. 6.2.                                           | I <sup>2</sup> C Bus Interface: Device and Subaddresses Protocol Description Proposal for MSP 3400C I <sup>2</sup> C Telegrams Symbols Write Telegrams Read Telegrams Examples Start Up Sequence  Programming the Demodulator Part Registers: Table and Addresses Registers: Functions and Values                                                                                                                                                                                                                                                            |

| 21<br>23<br>24<br>24<br>26                                     | 6.2.1.<br>6.2.2.<br>6.2.3.<br>6.2.4.<br>6.2.5.                                                       | Setting of Parameter AD_CV Control Register 'MODE_REG' FIR-Filter Switches FIR-Parameter DCO-Increments                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Contents, continued

| Page | Section | Title                                                               |

|------|---------|---------------------------------------------------------------------|

| 27   | 6.3.    | Sequences to Transmit Parameters and to Start Processing            |

| 27   | 6.4.    | Software Proposals for Multistandard TV-Sets                        |

| 27   | 6.4.1.  | Multistandard System B/G German DUAL FM                             |

| 28   | 6.4.2.  | Satellite Mode                                                      |

| 28   | 6.4.3.  | Automatic Search Function for FM-Carrier Detection                  |

| 28   | 6.4.4.  | Automatic Standard Detection                                        |

| 29   | 7.      | Programming the Audio Processing Part                               |

| 29   | 7.1.    | Summary of the DSP Control Registers                                |

| 31   | 7.1.1.  | Volume Loudspeaker Channel and Headphone Channel                    |

| 32   | 7.1.2.  | Balance Loudspeaker and Headphone Channel                           |

| 33   | 7.1.3.  | Bass Loudspeaker and Headphone Channel                              |

| 33   | 7.1.4.  | Treble Loudspeaker and Headphone Channel                            |

| 34   | 7.1.5.  | Loudness Loudspeaker and Headphone Channel                          |

| 34   | 7.1.6.  | Spatial Effects Loudspeaker Channel                                 |

| 35   | 7.1.7.  | Volume SCART                                                        |

| 35   | 7.1.8.  | Channel Source Modes                                                |

| 36   | 7.1.9.  | Channel Matrix Modes                                                |

| 36   | 7.1.10. | SCART Prescale                                                      |

| 36   | 7.1.11. | FM Prescale                                                         |

| 37   | 7.1.12. | FM Matrix Modes                                                     |

| 37   | 7.1.13. | FM Fixed Deemphasis                                                 |

| 37   | 7.1.14. | FM Adaptive Deemphasis                                              |

| 37   | 7.1.15. | I <sup>2</sup> S1 and I <sup>2</sup> S2 Prescale                    |

| 37   | 7.1.16. | ACB Register, Definition of the SCART-Switches and DIG_CTR_OUT Pins |

| 38   | 7.1.17. | Beeper                                                              |

| 38   | 7.1.18. | Identification Mode                                                 |

| 38   | 7.1.19. | FM DC Notch                                                         |

| 38   | 7.1.20. | Mode Tone Control                                                   |

| 39   | 7.1.21. | Equalizer Loudspeaker Channel                                       |

| 39   | 7.1.22. | Automatic Volume Correction (AVC)                                   |

| 40   | 7.1.23. | Subwoofer on Headphone Output                                       |

| 40   | 7.2.    | Exclusions                                                          |

| 41   | 7.3.    | Summary of Readable Registers                                       |

| 41   | 7.3.1.  | Stereo Detection Register                                           |

| 41   | 7.3.2.  | Quasi Peak Detector                                                 |

| 42   | 7.3.3.  | DC Level Register                                                   |

| 42   | 7.3.4.  | MSP Hardware Version Code                                           |

| 42   | 7.3.5.  | MSP Major Revision Code                                             |

| 42   | 7.3.6.  | MSP Product Code                                                    |

| 42   | 7.3.7.  | MSP ROM Version Code                                                |

## Contents, continued

| Page           | Section           | Title                                                                 |  |  |  |  |  |  |  |

|----------------|-------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|--|

| 43             | 8.                | Specifications                                                        |  |  |  |  |  |  |  |

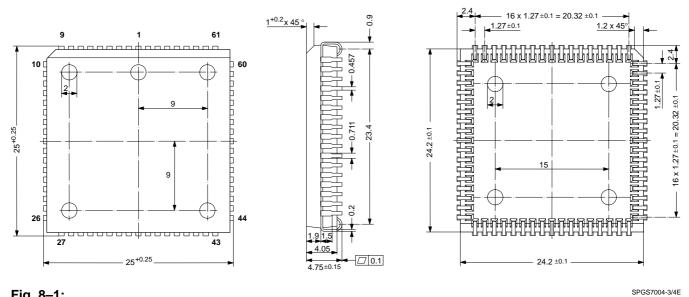

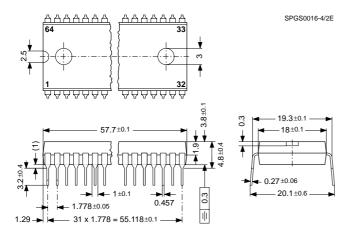

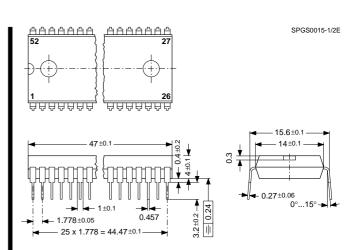

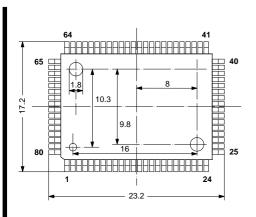

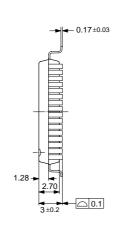

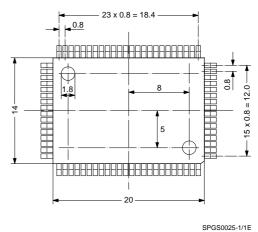

| 43             | 8.1.              | Outline Dimensions                                                    |  |  |  |  |  |  |  |

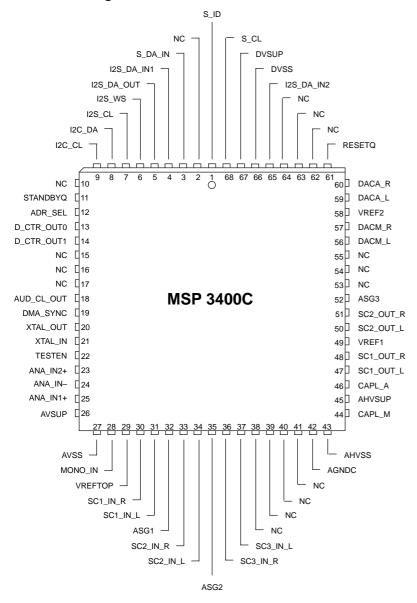

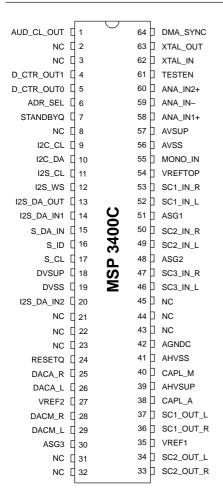

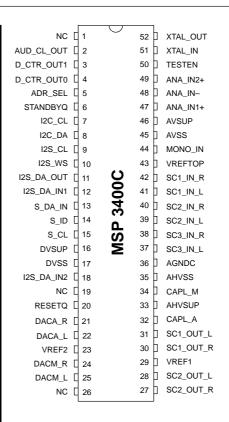

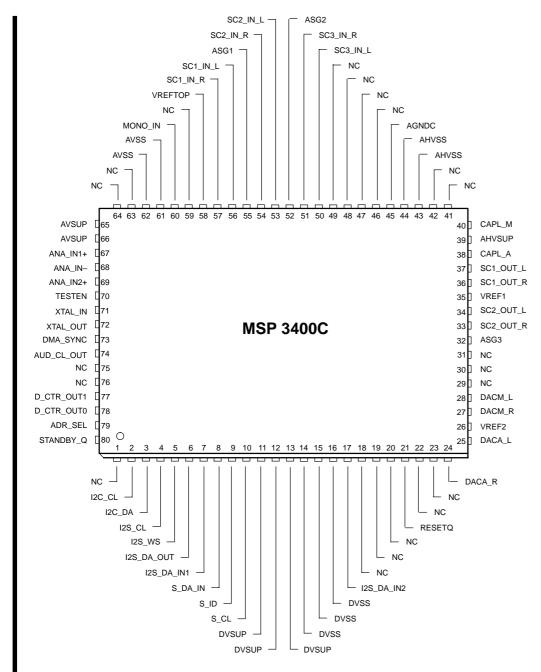

| 44             | 8.2.              | Pin Connections and Descriptions                                      |  |  |  |  |  |  |  |

| 48             | 8.3.              | Pin Configuration                                                     |  |  |  |  |  |  |  |

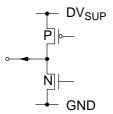

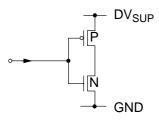

| 51             | 8.4.              | Pin Circuits                                                          |  |  |  |  |  |  |  |

| 53             | 8.5.              | Electrical Characteristics                                            |  |  |  |  |  |  |  |

| 53             | 8.5.1.            | Absolute Maximum Ratings                                              |  |  |  |  |  |  |  |

| 54             | 8.5.2.            | Recommended Operating Conditions                                      |  |  |  |  |  |  |  |

| 58             | 8.5.3.            | Characteristics                                                       |  |  |  |  |  |  |  |

|                |                   |                                                                       |  |  |  |  |  |  |  |

| 64             | 9.                | Application of the MSP 3400C                                          |  |  |  |  |  |  |  |

| 64<br>65       | 9.<br>10.         | Application of the MSP 3400C  DMA Application                         |  |  |  |  |  |  |  |

|                |                   | ••                                                                    |  |  |  |  |  |  |  |

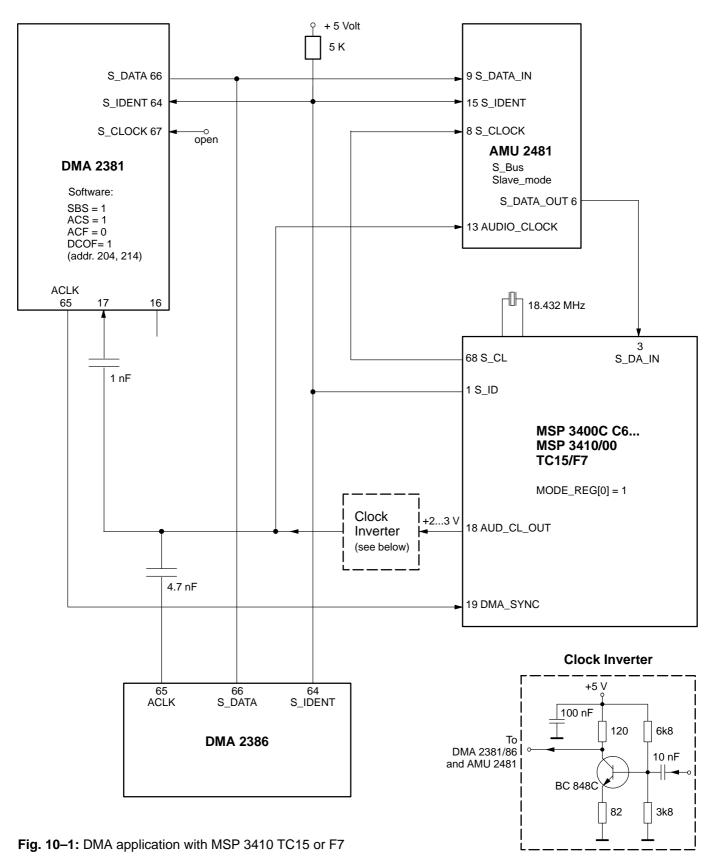

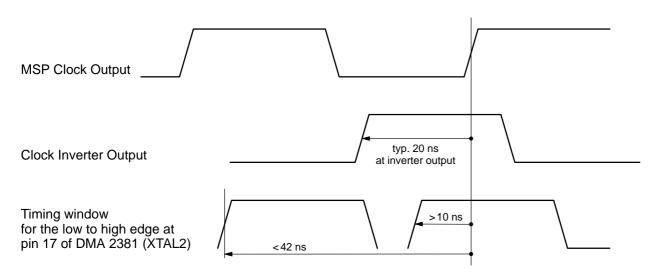

| 65             | 10.               | DMA Application                                                       |  |  |  |  |  |  |  |

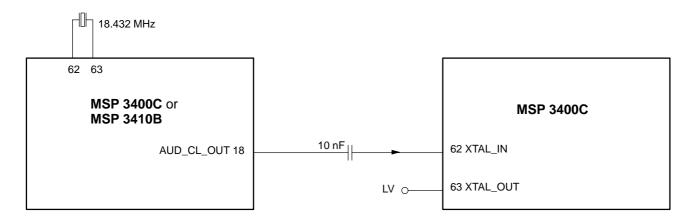

| 65<br>67       | 10.<br>11.        | DMA Application  MSP Application with External Clock                  |  |  |  |  |  |  |  |

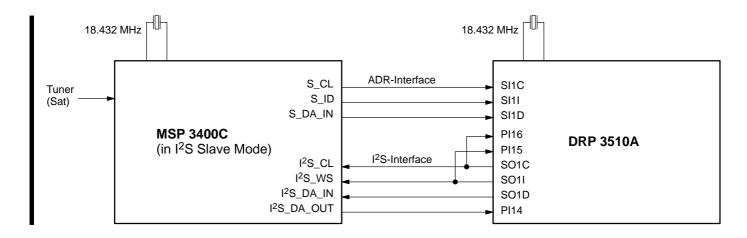

| 65<br>67<br>67 | 10.<br>11.<br>12. | DMA Application  MSP Application with External Clock  ADR Application |  |  |  |  |  |  |  |

#### **Multistandard Sound Processor**

Release Notes: The hardware description in this document is valid for the MSP 3400C – C8 and newer codes. Revision bars indicate significant changes to the previous version.

#### 1. Introduction

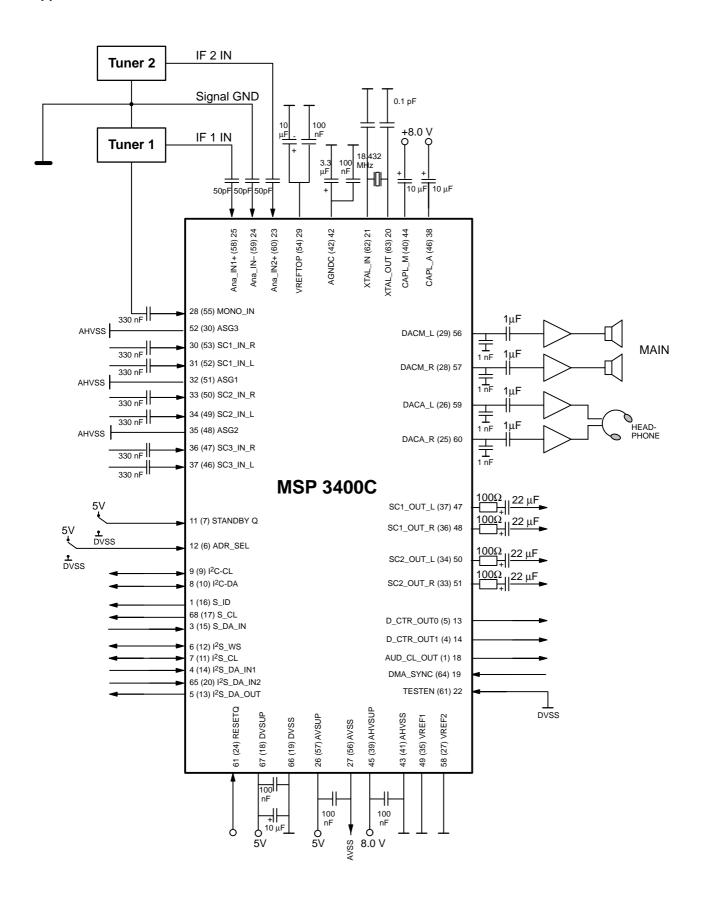

The **MSP 3400C** is designed as single-chip Multistandard Sound Processor for applications in analog and digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates the progressive development towards highly integrated multi-functional ICs.

The **MSP 3400C**, again, improves function integration: The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is performed in a single chip. The IC is produced in 0.8  $\mu$ m CMOS technology, combined with high performance digital signal processing.

The MSP 3400C 0.8  $\mu$  CMOS version is fully pin and software compatible to the 1.0  $\mu$  MSP 3400 and MSP 3410. The main difference between the MSP 3400C and the MSP 3410, consists of the MSP 3410 being able to decode NICAM signals.

The MSP 3400C is available in PLCC68, PSDIP64, PSDIP52, and PQFP80 package.

**Note:** To achieve compatibility with the functions of MSP 3400 and MSP 3410 (except NICAM), the load sequences must be programmed as described in the data sheet of MSP 3410.

## MSP 3400C Integrated Functions:

- FM-demodulation of all terrestrial standards (incl. identification decoding)

- FM-demodulation of all satellite standards

- various deemphasis types (incl. Panda1)

- volume, balance, bass, treble, loudness for loudspeaker and headphone output

- automatic volume correction (A.V.C.)

- 5 band graphic equalizer

- subwoofer output alternatively with headphone output

- spatial effect (pseudostereo/basewidth enlargement)

- ADR together with DRP 3510 A

- Dolby ProLogic together with DPL 3418/19/20 A

- 3 pairs of D/A converters

- 1 pair of A/D converters

- SCART switches

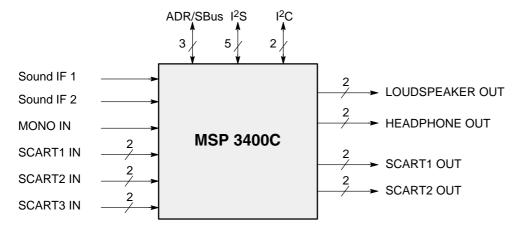

Fig. 1-1: Main I/O Signals MSP 3400C

#### 2. Features of the MSP 3400C

## 2.1. Features of the Demodulator and Decoder Sections

The MSP 3400C is designed to perform demodulation of FM-mono TV sound and two carrier FM systems according to the German or Korean terrestrial specs. With certain constraints, it is also possible to do AM-demodulation according to the SECAM system. Alternatively, the satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation offers a powerful feature to calculate the carrier field strength, which can be used for automatic search algorithms. So, the IC facilitates a first step towards multistandard capability with its very flexible application and may be used in TV-sets, satellite tuners, and video recorders.

The MSP 3400C facilitates profitable multistandard capability, offering the following advantages:

- two selectable analog inputs (TV and SAT-IF sources)

- Automatic Gain Control (AGC) for analog input: input range: 0.14 – 3 Vpp

- integrated A/D converter for sound-IF inputs

- all demodulation and filtering is performed on chip and is individually programmable

- no external filter hardware is required

- only one crystal clock (18.432 MHz) is necessary

- FM carrier level calculation for automatic search algorithms and carrier mute function

- high deviation FM-mono mode (max. deviation: approx. ± 360 kHz)

#### 2.2. Features of the DSP-Section

- flexible selection of audio sources to be processed

- digital input and output interfaces via I<sup>2</sup>S-Bus for external DSP-processors, surround sound, ADR etc.

- digital interface to process ADR (Astra Digital Radio) together with DRP 3510 A

- performance of all deemphasis systems including adaptive Wegener Panda 1 without external components or controlling

- digitally performed FM-identification decoding and dematrixing

- digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth enlargement

- simple controlling of volume, bass, treble, equalizer etc.

- increased audio bandwidth for FM-Audio-signals

(20 Hz 15 kHz, ±1 dB)

#### 2.3. Features of the Analog Section

three selectable analog pairs of audio baseband inputs (= three SCART inputs) input level: ≤2 V RMS,

input impedance:  $\geq$ 25 k $\Omega$

- one selectable analog mono input (i.e. AM sound), input level:  $\leq$ 2 V RMS, input impedance:  $\geq$ 10 k $\Omega$

- two high quality A/D converters, S/N-Ratio: ≥85 dB

- 20 Hz to 20 kHz Bandwidth for SCART-to-SCART-Copy facilities

- MAIN (loudspeaker) and AUX (headphones): two pairs of 4-fold oversampled D/A-converters output level per channel: max. 1.4 V RMS output resistance: max. 5 kΩ S/N-Ratio: ≥85 dB at maximum volume max. noise voltage in mute mode: ≤10 μV (BW: 20 Hz ...16 kHz)

- one pair of four-fold oversampled D/A-converters supplying two selectable pairs of SCART-Outputs. Output level per channel: max. 2 V RMS, output resistance: max. 0.5 kΩ, S/N-Ratio: ≥85 dB

(20 Hz...16 kHz)

## 3. Application Fields of the MSP 3400C

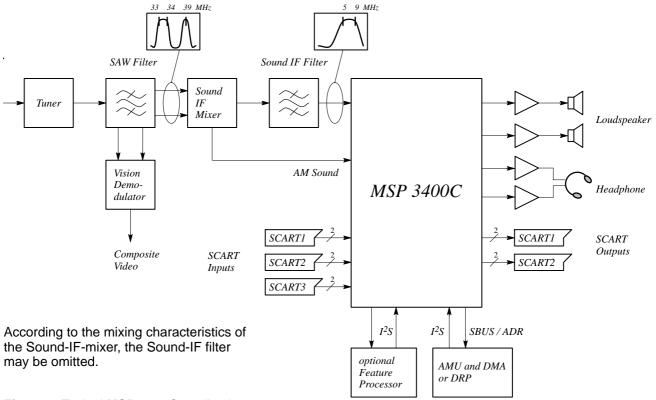

The **MSP 3400C** processes TV sound according to the German and Korean two carrier system and the commonly used satellite systems. In the following sections, a brief overview on the German FM-Stereo system shows what is required of a multistandard audio IC.

## 3.1. German 2-Carrier System (DUAL FM System)

Since September 1981, stereo and dual sound programs have been transmitted in Germany using the 2-carrier system. Sound transmission consists of the already existing first sound carrier and a second sound carrier additionally containing an identification signal. More details of this standard are given in Table 3–1.

Table 3-1: European TV standards

| TV-System              | Position of Sound<br>Carrier /MHz                              | Sound<br>Modulation        | Color System | Country                          |  |  |

|------------------------|----------------------------------------------------------------|----------------------------|--------------|----------------------------------|--|--|

| B/G                    | 5.5/5.7421875                                                  | FM-Stereo                  | PAL          | Germany                          |  |  |

| B/G                    | 5.5/5.85                                                       | FM-Mono/NICAM              | PAL          | Scandinavia,Spain                |  |  |

| L                      | 6.5/5.85                                                       | AM-Mono/NICAM              | SECAM-L      | France                           |  |  |

| 1                      | 6.0/6.552                                                      | FM-Mono/NICAM              | PAL          | UK                               |  |  |

| D/K                    | 6.5/6.2578125 D/K1<br>6.5/6.7421875 D/K2<br>6.5/5.85 D/K-NICAM | FM-Stereo<br>FM-Mono/NICAM | SECAM-East   | USSR<br>Hungary                  |  |  |

| M<br>M-Korea           | 4.5<br>4.5/4.724212                                            | FM-Mono<br>FM-Stereo       | NTSC         | USA<br>Korea                     |  |  |

| Satellite<br>Satellite | 6.5<br>7.02/7.2                                                | FM-Mono<br>FM-Stereo       | PAL<br>PAL   | Europe (ASTRA)<br>Europe (ASTRA) |  |  |

Fig. 3-1: Typical MSP 3400C application

## ■ Table 3–2: Key parameters for B/G, D/K, and M 2-carrier sound system

| Sound Carriers                    | Carrier FI   | W1         |          | Carrier FM2 |                                  |                      |  |  |

|-----------------------------------|--------------|------------|----------|-------------|----------------------------------|----------------------|--|--|

|                                   | B/G          | D/K        | М        | B/G         | D/K                              | М                    |  |  |

| Vision/sound power difference     |              | 13 dB      |          |             | 20 dB                            |                      |  |  |

| Sound bandwidth                   |              |            | 40 Hz to | 15 kHz      |                                  |                      |  |  |

| Pre-emphasis                      | 50           | μs         | 75 μs    | 50          | μs                               | 75 μs                |  |  |

| Frequency deviation               | ±50          | kHz        | ±25 kHz  | ±50         | kHz                              | ±25 kHz              |  |  |

| Sound Signal Components           |              |            |          |             |                                  |                      |  |  |

| Mono transmission                 |              | mono       |          | mono        |                                  |                      |  |  |

| Stereo transmission               | (L+I         | R)/2       | (L+R)/2  | F           | (L-R)/2                          |                      |  |  |

| Dual sound transmission           |              | language A |          | language B  |                                  |                      |  |  |

| Identification of Transmission Mo | de on Carrie | er FM2     |          |             |                                  |                      |  |  |

| Pilot carrier frequency in kHz    |              |            |          | 54.6        | 875                              | 55.0699              |  |  |

| Type of modulation                |              |            |          | AM          |                                  |                      |  |  |

| Modulation depth                  |              |            |          |             | 50%                              |                      |  |  |

| Modulation frequency              |              |            |          | stereo: 1   | nmodulated<br>17.5 Hz<br>74.1 Hz | 149.9 Hz<br>276.0 Hz |  |  |

**Note:** NICAM decoding can be achieved by using the MSP 3410 instead of the MSP 3400C. Since the MSP 3400C and the MSP 3410 are fully pin and software downwards compatible (concerning all features of MSP 3410), it is possible to decide in the assembly line, whether the application should be able to decode NICAM or not.

#### 4. Architecture of the MSP 3400C

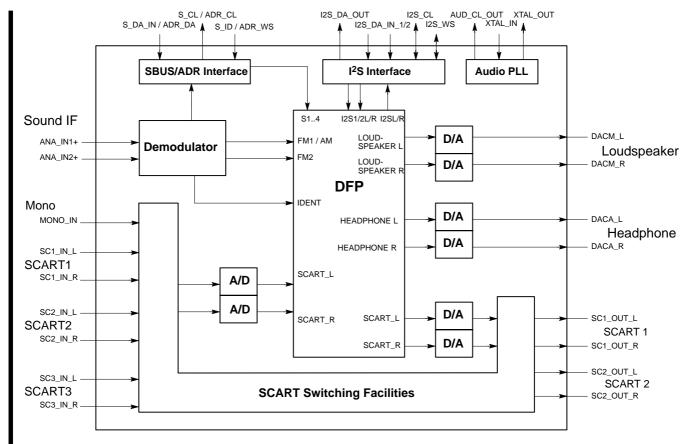

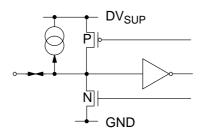

Fig. 4–1 shows a simplified block diagram of the IC. Its architecture is split into three functional blocks:

- 1. demodulator section

- 2. digital signal processing (DSP) section performing audio baseband processing

- 3. analog section containing two A/D-converters, 6 D/A-converters, and SCART switching facilities

#### 4.1. Demodulator Block

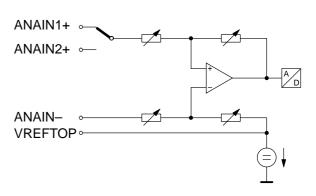

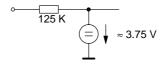

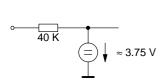

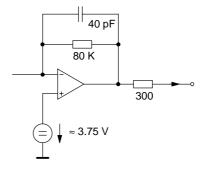

## 4.1.1. Analog Sound IF - Input Section

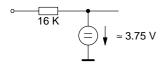

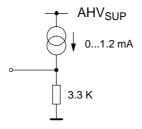

The input pins ANA\_IN1+, ANA\_IN2+, and ANA\_IN-offer the possibility to connect two different sound IF sources to the MSP 3400C. By means of bit [8] of AD\_CV (see Table 6–3), either terrestrial or satellite sound IF signals can be selected. The analog-to-digital conversion of the preselected sound IF signal is done by a flash-converter, whose output can be used to control an automatic gain circuit (AGC), providing optimum level for a wide range of input levels. It is possible to switch between automatic gain control and a fixed (setable) input gain. In the optimum case, the input range of the A/D converter is completely covered by the sound IF source.

Some combinations of SAW filters and sound IF mixer ICs, however, show large picture components on their outputs. In this case, filtering is recommended. It was found that the high pass filters formed by the coupling capacitors at pins ANA\_IN1+ and ANA\_IN2+ as shown in the application diagram are sufficient in most cases.

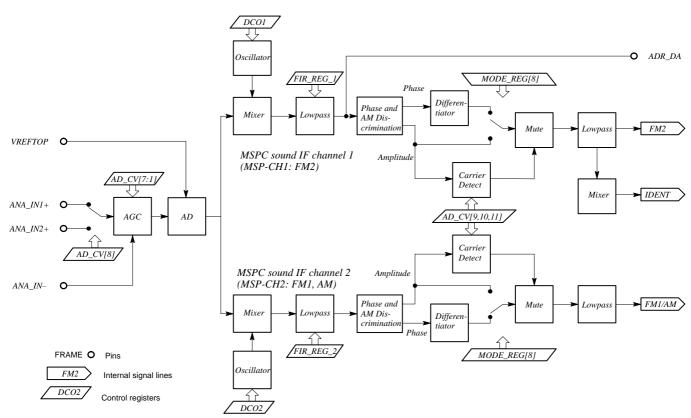

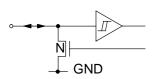

#### 4.1.2. Quadrature Mixers

The digital input coming from the integrated A/D converter may contain audio information at a frequency range of theoretically 0 to 9 MHz corresponding to the selected standards. By means of two programmable quadrature mixers two different audio sources, for example FM1 and FM2, may be shifted into baseband position. In the following, the two main channels are provided to process either:

- FM mono (channel 2) or

- FM2 (channel 1) and FM1 (channel 2).

Two independent digital oscillators are provided to generate two pairs of sin/cos-functions. Two programmable increments, to be divided up into Low- and High Part, determine frequency of the oscillator, which corresponds to the frequency of the desired audio carrier. In section 6.1., format and values of the increments are listed.

Fig. 4-1: Architecture of the MSP 3400C

Fig. 4-2: Demodulator architecture

## 4.1.3. Lowpass Filtering Block for Mixed Sound IF Signals

FM bandwidth limitation is performed by a linear phase Finite Impulse Response (FIR-filter). Just like the oscillators' increments, the filter coefficients are programmable and are written into the IC by the CCU via the control bus. Two not necessarily different sets of coefficients are required, one for channel 1 (FM2) and one for channel 2 (FM1=FM-mono). In section 6.2.4., several coefficient sets are proposed.

#### 4.1.4. Phase and AM Discrimination

The filtered sound IF signals are demodulated by means of the phase and amplitude discriminator block. On the output, the phase and amplitude is available for further processing. AM signals are derived from the amplitude information, whereas the phase information serves for FM demodulation.

## 4.1.5. Differentiators

FM demodulation is completed by differentiating the phase information output.

# 4.1.6. Lowpass Filter Block for Demodulated Signals

The demodulated FM and AM signals are further lowpass filtered and decimated to a final sampling frequency of 32 kHz. The usable bandwidth of the final baseband signals is about 15 kHz.

#### 4.1.7. High Deviation FM Mode

By means of MODE\_REG [9], the maximum FM-deviation can be extended to approximately  $\pm$  360 kHz. Since this mode can be applied only for the MSPC sound IF channel 2, the corresponding matrices in the baseband processing must be set to sound A. Apart from this, the coefficient sets 380 kHz FIR\_REG2 or 500 kHz FIR\_REG2 must be chosen for the FIR\_REG\_2. For a given deviation, in relation to the normal FM-mode, the audio level of the high-deviation mode is reduced by 6 dB.

## 4.1.8. MSPC-Mute Function in the Dual Carrier FM Mode

To prevent noise effects or FM identification problems in the absence of one of the two FM carriers, the MSP 3400 C offers a carrier detection feature, which must be activated by means of AD\_CV[9]. The mute level may be programmed by means of AD\_CV[10,11]. (see section 6.2.1.) If no FM carrier is available at the MSPC channel 1, the corresponding channel FM2 is muted. If no FM carrier is available at the MSPC channel 2, the corresponding channel FM1 is muted. In case of the absence of both FM carriers, pure noise will be amplified by the input AGC. Therefore, a proper mute function depends on the noise quality of the TV set's IF part and cannot be guaranteed. The mute function is not recommended for the satellite mode.

#### 4.2. Analog Section and SCART Switching Facilities

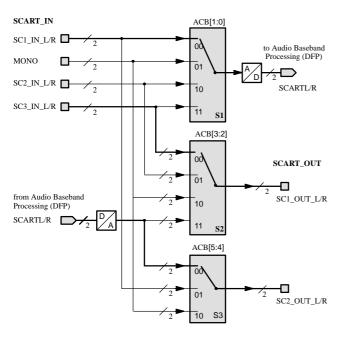

The analog input and output sections offer a wide range of switching facilities, which are shown in Fig. 4–3. To design a TV-set with 3 pairs of SCART-inputs and two pairs of SCART-outputs, no external switching hardware is required.

The switches are controlled by the ACB bits defined in the audio processing interface (see section 7. Programming the Audio Processing Part).

If the MSP 3400C is switched off by first pulling STAND-BYQ low, and then disconnecting the 5 V, but keeping the 8 V power supply ('**Standby'-mode**), the switches S1, S2, and S3 maintain their position and function. This facilitates the copying from selected SCART-inputs to SCART-outputs in the TV-sets standby mode.

Fig. 4–3: SCART-Switching Facilities

Bold lines determine the default configuration

In case of power-on start or starting from standby, the IC switches automatically to the default configuration, shown in Fig. 4–3. This takes place after the first I<sup>2</sup>C transmission into the DFP part. By transmitting the ACB register first, the default setting mode can be changed.

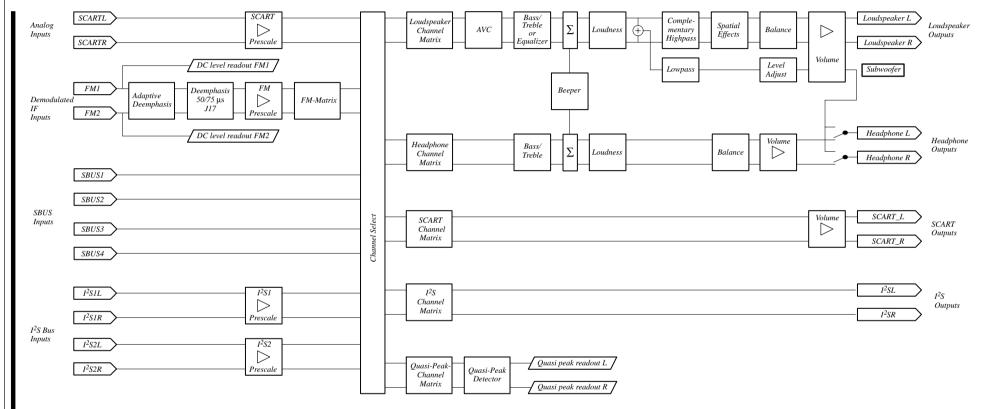

#### 4.3. MSP 3400C Audio Baseband Processing

By means of the DFP processor, all audio baseband functions are performed by digital signal processing (DSP). The DSP functions are grouped into three processing parts: input preprocessing, channel selection, and channel postprocessing.

The input preprocessing is intended to prepare the various signals of all input sources in order to form a standardized signal at the input to the channel selector. The signals can be adjusted in volume, are processed with the appropriate deemphasis, and are dematrixed if necessary.

Having prepared the signals that way, the channel selector makes it possible to distribute all possible source signals to the desired output channels.

The ability to route in an external coprocessor for special effects like surround and sound field processing is of special importance. Routing can be done with each input source and output channel via the I<sup>2</sup>S inputs and outputs.

All input and output signals can be processed simultaneously. Note that the NICAM input signals are only available in the MSP 3410 version. While processing the adaptive deemphasis, no dual carrier stereo (German or Korean) is possible. Identification values are not valid either.

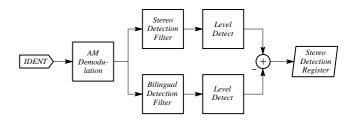

### 4.3.1. Dual Carrier FM Stereo/Bilingual Detection

In the German and Korean TV standard, audio information can be transmitted in three modes: mono, stereo, or bilingual. To obtain information about the current audio operation mode, the MSP 3400C detects the so-called identification signal. Information is supplied via the Stereo Detection Register to an external CCU.

Fig. 4-4: Stereo/bilingual detection

Fig. 4–5: Audio baseband processing (DSP-Firmware)

Table 4-1: Several examples for recommended channel assignments for demodulator and audio processing part

| Mode                                     | MSPC Sound IF-<br>Channel 1 / FM2 | MSPC Sound IF-<br>Channel 2 / FM1 | FM-<br>Matrix | Channel<br>Select            | Channel<br>Matrix                       |

|------------------------------------------|-----------------------------------|-----------------------------------|---------------|------------------------------|-----------------------------------------|

| B/G-Stereo                               | FM2 (5.74 MHz): R                 | FM1 (5.5 MHz): (L+R)/2            | B/G Stereo    | Speakers: FM                 | Stereo                                  |

| B/G-Bilingual                            | FM2 (5.74 MHz): Sound B           | FM1 (5.5 MHz): Sound A            | No Matrix     | Speakers: FM<br>H.Phone : FM | Speakers: Sound A<br>H.Phone : Sound B  |

| Sat-Mono                                 | not used                          | FM (6.5 MHz): mono                | No Matrix     | Speakers: FM                 | Sound A                                 |

| Sat-Stereo                               | 7.20 MHz: R                       | 7.02 MHz: L                       | No Matrix     | Speakers: FM                 | Stereo                                  |

| Sat-Bilingual                            | 7.38 MHz: Sound C                 | 7.02 MHz: Sound A                 | No Matrix     | Speakers: FM<br>H.Phone : FM | Speakers: Sound A<br>H.Phone :Sound B=C |

| Sat High Dev.<br>Mode (e.g.<br>EutelSat) | don't care                        | 6.552 MHz                         | No Matrix     | Speakers: FM<br>H.Phone : FM | Speakers: Sound A<br>H.Phone : Sound A  |

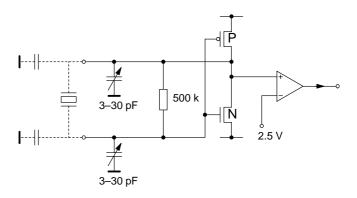

## 4.4. Audio PLL and Crystal Specifications

The MSP 3400C runs at 18.432 MHz. A detailed specification of the required crystal for different packages and master/slave applications can be found in Table 8.5.2. The clock supply of the entire system depends on the MSP 3400C operation mode:

1. FM-Stereo/I<sup>2</sup>S Master operation: The system clock runs free on the crystal's 18.432 MHz.

### 2. I<sup>2</sup>S Slave operation:

In this case, the system clock is synchronizing on the  $I^2S_WS$  signal, which is fed into the MSP 3400C (Mode\_Reg[3] = 1).

## 3. D2-MAC operation:

In this case, the system clock is locked to a synchronizing signal (DMA\_SYNC) supplied by the D2-MAC chip (Mode\_Reg[0] = 1). The DMA and the AMU chips can be driven by the MSP 3400C audio clock (AUD\_CL\_OUT).

#### Remark on using the crystal:

External capacitors at each crystal pin to ground are required. They are necessary for tuning the open-loop frequency of the internal PLL and for stabilizing the frequency in closed-loop operation. The higher the capacitors, the lower the clock frequency results. The

nominal free running frequency should match the center of the tolerance range between 18.433 and 18.431 MHz as closely as possible. Due to different layouts of customer PCBs, the matching capacitor size should be defined in the application (see also Table 8.5.2.).

#### 4.5. ADR Bus

To be able to process ADR, the MSPC has a special designed interface to work together with DRP 3510A. To be prepared for an upgrade to ADR with an additional DRP board, the following lines of MSP 3400C should be provided on a feature connector:

- AUD CL OUT

- $-I^2S_DA_IN1$  or  $I^2S_DA_IN2$

- I<sup>2</sup>S\_DA\_OUT

- I2S WS

- I2S CLK

- $S_CL = ADR_CL$

- $-S_ID = ADR_WS$

- -S DA IN = ADR DA

#### 4.6. S-Bus Interface

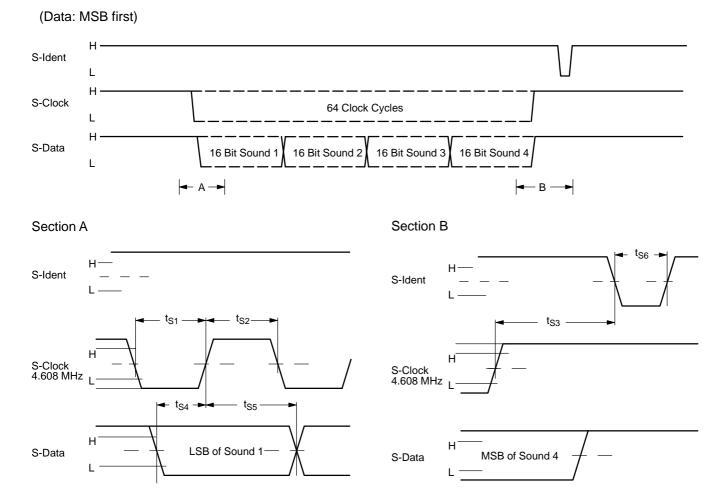

Digital audio information provided by the DMA 2381 via the AMU is serially transmitted to the MSP 3400C via the S-Bus. The MSP 3400C is always in S-Bus master mode.

The S-Bus interface consists of three pins:

#### 1. S DA IN:

Four channels (4\*16 bits) per sampling cycle (32 kHz) are transmitted.

### 2. S\_CL:

Gives the timing for the transmission of S-DATA (4.608 MHz).

## 3. S\_ID:

After 64 S-CLOCK cycles, the S\_ID determines the end of one sampling period.

A detailed timing diagram is shown in Fig. 4-6.

Fig. 4-6: S-Bus timing diagram

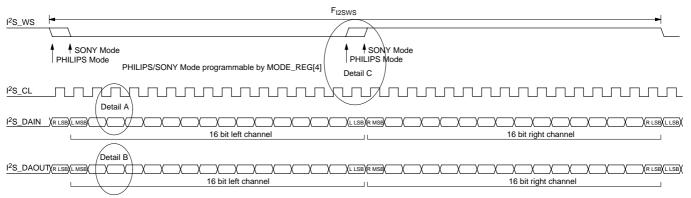

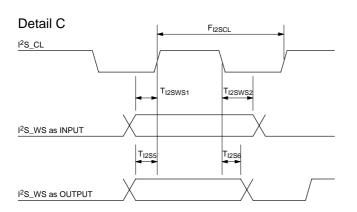

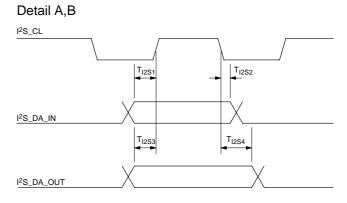

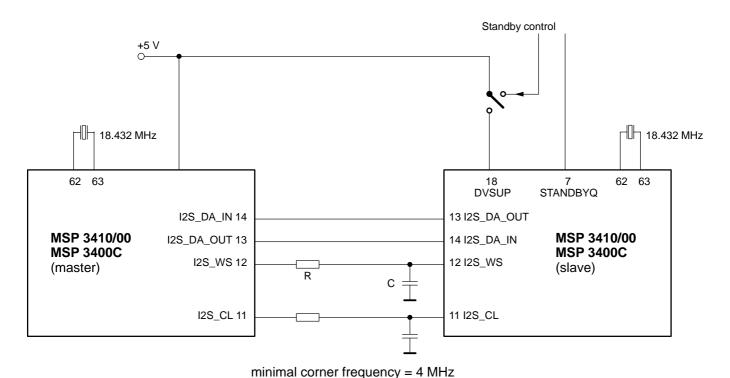

### 4.7. I<sup>2</sup>S Bus Interface

By means of this standardized interface, additional feature processors can be connected to the MSP 3400C. Two possible formats are supported: The standard mode (MODE\_REG[4]=0) selects the SONY format, where the I2S\_WS signal changes at the word boundaries. The so-called PHILIPS format, which is characterized by a change of the I2S\_WS signal, one I2S\_CL period before the word boundaries, is selected by setting MODE\_REG[4]=1.

The MSP 3400C normally serves as the master on the I $^2$ S interface. Here, the clock and word strobe lines are driven by the MSP 3400C. By setting MODE\_REG[3]=1, the MSP 3400C is switched to a slave mode. Now, these lines are input to the MSP 3400 C, and the master clock is synchronized to 576 times the I2S\_WS rate (32 kHz). No D2MAC operation is possible in this mode.

The I<sup>2</sup>S bus interface consists of five pins:

#### 1. I2S DA IN1:

For input, two channels (2\*16 bits) per sampling cycle (32 kHz) are transmitted.

### 2. I2S\_DA\_IN2:

For input, two channels (2\*16 bits) per sampling cycle (32 kHz) are transmitted.

#### 3. I2S\_DA\_OUT:

For output, two channels (2\*16 bits) per sampling cycle (32 kHz) are transmitted.

#### 4. I2S CL:

Gives the timing for the transmission of I<sup>2</sup>S serial data (1.024 MHz).

#### 5. I2S\_WS:

The I2S\_WS word strobe line defines the left and right sample.

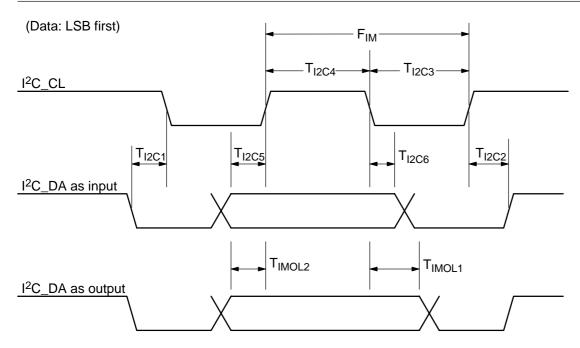

A detailed timing diagram is shown in Fig. 4-7.

#### Data: MSB first)

Fig. 4–7: I<sup>2</sup>S Bus timing diagram

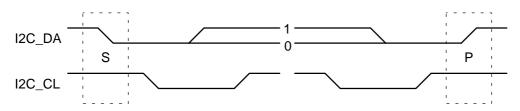

#### 5. I<sup>2</sup>C Bus Interface: Device and Subaddresses

As a slave receiver, the MSP 3400C can be controlled via I<sup>2</sup>C bus. Access to internal memory locations is achieved by subaddressing. The demodulator part and the audio processor part (DFP) have two separate subaddressing register banks.

In order to allow for more MSP 3400C ICs to be connected to the control bus, an ADR\_SEL pin has been implemented. With ADR\_SEL pulled to high, the MSP 3400C responds to changed device addresses, thus two identical devices can be selected. Other devices of the same family will have different subaddresses (e.g. 34x0)

By means of the RESET bit in the CONTROL register, all devices with the same device address are reset.

The IC is selected by asserting a special device address in the address part of an I<sup>2</sup>C transmission. A device address pair is defined as a write address (80 hex or 84 hex) and a read address (81 hex or 85 hex). Writing is done by sending the device write address first, followed by the subaddress byte, two address bytes, and two data bytes. For reading, the read address has to be transmitted first by sending the device write address (80 hex or 84 hex), followed by the subaddress byte, and two address bytes. Without sending a stop condition, reading of the addressed data is done by sending the device read address (81 hex or 85 hex) and reading two bytes

of data. Refer to Fig. 5–1 I<sup>2</sup>C Bus Protocol and section 5.2. Proposal for MSP 3400C I<sup>2</sup>C Telegrams.

Due to the internal architecture of the MSP 3400C, the IC cannot react immediately to an I $^2$ C request. The typical response time is about 0.3 ms. If the addressed processor is not ready for further transmissions on the I $^2$ C bus, the clock line I2C\_CL is pulled low. This puts the current transmission into a wait state. After a certain period of time, the MSP 3400C releases the clock, and the interrupted transmission is carried on.

The I<sup>2</sup>C Bus lines can be set tristate by switching the IC into "Standby"-mode.

#### I<sup>2</sup>C-Bus error conditions:

In case of any internal error, the MSP's wait-period is extended to 1.77 ms. Afterwards, the MSP does not acknowledge (NAK) the device address. The data line will be left HIGH by the MSP, and the clock line will be released. The master can then generate a STOP condition to abort the transfer.

By means of NAK, the master is able to recognize the error state and to reset the IC via I<sup>2</sup>C-Bus. While transmitting the reset protocol (section. 5.2.4.) to 'CONTROL', the master must ignore the not acknowledge bits (NAK) of the MSP.

A detailed timing diagram is shown in Fig. 5–1 and Fig. 5–2.

**■ Table 5–1:** I<sup>2</sup>C Bus Device Addresses

| ADR_SEL            | Lo     | )W     | Hiç    | gh     | Left Open |        |  |

|--------------------|--------|--------|--------|--------|-----------|--------|--|

| Mode               | Write  | Read   | Write  | Read   | Write     | Read   |  |

| MSP device address | 80 hex | 81 hex | 84 hex | 85 hex | 88 hex    | 89 hex |  |

Table 5-2: I<sup>2</sup>C Bus Device and Subaddresses

| Name    | Binary Value | Hex Value | Function                  |  |  |  |  |

|---------|--------------|-----------|---------------------------|--|--|--|--|

| CONTROL | 0000 0000    | 00        | software reset            |  |  |  |  |

| TEST1   | 0000 0001    | 01        | only for internal use     |  |  |  |  |

| TEST2   | 0000 0010    | 02        | only for internal use     |  |  |  |  |

| WR_DEM  | 0001 0000    | 10        | write address demodulator |  |  |  |  |

| RD_DEM  | 0001 0001    | 11        | read address demodulator  |  |  |  |  |

| WR_DFP  | 0001 0010    | 12        | write address DFP         |  |  |  |  |

| RD_DFP  | 0001 0011    | 13        | read address DFP          |  |  |  |  |

| AGC     | 0001 1110    | 1E        | read AGC RMS              |  |  |  |  |

| PLL_CAP | 0001 1111 1F |           | read / write PLL_Cap      |  |  |  |  |

#### Table 5-3: Control Register

| Name    | 15    | 140 |

|---------|-------|-----|

| CONTROL | RESET | 0   |

## 5.1. Protocol Description

## Write to DFP or Demodulator Part (long protocol)

| S daw Wait ACK sub-addr ACK addr-byte low high | S | daw Wait A | ACK sub-addr | ACK addr-by high | te ACK addr-byte low | ACK d | data-byte high | ACK data-byte low | ACK | Р |

|------------------------------------------------|---|------------|--------------|------------------|----------------------|-------|----------------|-------------------|-----|---|

|------------------------------------------------|---|------------|--------------|------------------|----------------------|-------|----------------|-------------------|-----|---|

## Read from DFP Part (long protocol)

| s | daw | Wait | ACK | sub-addr | ACK | addr-byte<br>high | ACK | addr-byte<br>low | ACK | s | dar | Wait | ACK | data-byte<br>high | AC | X  | data-byte<br>low | NAK  | Р   |

|---|-----|------|-----|----------|-----|-------------------|-----|------------------|-----|---|-----|------|-----|-------------------|----|----|------------------|------|-----|

|   |     | l    |     |          |     |                   |     |                  |     |   |     |      |     |                   | 1  | // |                  | 11/1 | 4 I |

## Write to Control / Test / AGC / PLL\_Cap Registers (short protocol)

| S | daw | Wait | ACK | sub-addr | ACK | data-byte high | ACK | data-byte low | ACK | Р |  |

|---|-----|------|-----|----------|-----|----------------|-----|---------------|-----|---|--|

|---|-----|------|-----|----------|-----|----------------|-----|---------------|-----|---|--|

## Read from Control / Test / AGC / PLL\_Cap Registers (short protocol)

| S | daw | Wait | ACK | sub-addr | ACK | s | dar | Wait | ACK | data-byte high | ACK | data-byte low | NAK | Р |

|---|-----|------|-----|----------|-----|---|-----|------|-----|----------------|-----|---------------|-----|---|

|---|-----|------|-----|----------|-----|---|-----|------|-----|----------------|-----|---------------|-----|---|

**Note:**  $S = I^2C$ -Bus Start Condition from master

$P = I^2C$ -Bus Stop Condition from master

daw = Device Address Write dar = Device Address Read

ACK = Acknowledge-Bit: LOW on I2C\_DA from slave (= MSPC, grey)

or master (= CCU, hatched)

NAK = Not Acknowledge-Bit: HIGH on I2C\_DA from master (= CCU, hatched) to indicate

'End of Read' or from MSPC indicating internal error state (not illustrated)

Wait = I<sup>2</sup>C-Clock line held low by the slave (= MSPC) while interrupt is serviced (<1.77 ms)

Fig. 5–1: I<sup>2</sup>C bus protocol

(MSB first; data must be stable while clock is high)

Fig. 5–2: I<sup>2</sup>C bus timing diagram

## 5.2. Proposal for MSP 3400C I<sup>2</sup>C Telegrams

## **5.2.1. Symbols**

daw device address write

dar device address read

< Start Condition

> Stop Condition

aa Address Byte

dd Data Byte

## 5.2.2. Write Telegrams

| <daw< th=""><th>00</th><th>aa</th><th>da:</th><th>&gt;</th><th></th><th>Software RESET</th></daw<>                          | 00 | aa | da: | >  |     | Software RESET                       |

|-----------------------------------------------------------------------------------------------------------------------------|----|----|-----|----|-----|--------------------------------------|

| <daw< td=""><td>10</td><td>aa</td><td>aa</td><td>dd</td><td>dd&gt;</td><td>write data into demodulator register</td></daw<> | 10 | aa | aa  | dd | dd> | write data into demodulator register |

| <daw< td=""><td>12</td><td>aa</td><td>aa</td><td>dd</td><td>dd&gt;</td><td>write data into DFP register</td></daw<>         | 12 | aa | aa  | dd | dd> | write data into DFP register         |

## 5.2.3. Read Telegrams

<daw 11 aa aa <dar dd dd> read data from demodulator

<daw 13 aa aa <dar dd dd> read data from DSP

## 5.2.4. Examples

| <daw 00="" 80=""></daw>             | RESET MSPC statically          |

|-------------------------------------|--------------------------------|

| <daw 00=""></daw>                   | clear RESET                    |

| <daw 00="" 08="" 12="" 20=""></daw> | set loudspeaker channel source |

|                                     | to FM and Matrix to STEREO     |

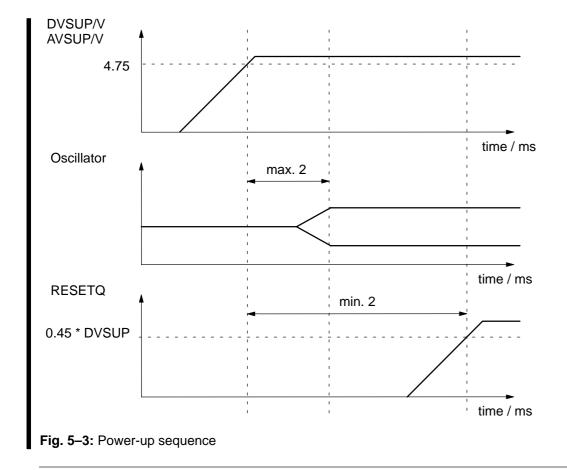

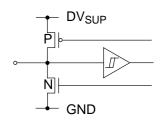

### 5.3. Start Up Sequence

After power on or RESET, the IC is in an inactive state. The CCU has to transmit the required coefficient set for a given operation via the I<sup>2</sup>C bus. Initialization must start with the demodulator part. If required for any reason, the audio processing part can be loaded before the demodulator part.

The reset pin should not be >0.45 DVSUP (see recommended operation conditions) before the 5 Volt digital power supply (DVSUP) and the analog power supply (AVSUP) are >4.75 Volt **and** the MSP-Clock is running (Delay: 2 ms max, 0.5 ms typ.).

This means, if the reset low-high edge starts with a delay of 2 ms after DVSUP>4.75 Volt and AVSUP>4.75 Volt, even under worst case conditions, the reset is ok.

**Note:** The reset should not reach high level before the oscillator has started. This requires a reset delay of >2 ms

#### 6. Programming the Demodulator Part

## 6.1. Registers: Table and Addresses

In Table 6–1, all Write Registers are listed.

All transmissions on the control bus are 16 bits wide. Data for the demodulator part has 8 or 12 significant bits. These data have to be inserted LSB bound and filled with zero bits into the 16 bit transmission word. If channel 1 or channel 2 is selected in the channel matrix while any of the parameters are changed, the corresponding output must be muted. Click and crack noise may occur during coefficient changes. Table 4–1 explains how to assign FM carriers to the MSPC-Sound IF channels and the corresponding matrix modes in the audio processing part.

Table 6–1: MSP 3400C demodulator write registers

| Register                                 | Protocol                     | Write<br>Address<br>(hex)    | Function                                                                                                                                                              |

|------------------------------------------|------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD_CV                                    | long                         | 00BB                         | input selection, configuration of AGC and Mute Function, and selection of A/D-converter                                                                               |

| MODE_REG                                 | long                         | 0083                         | mode register                                                                                                                                                         |

| FIR_REG_1<br>FIR_REG_2                   | long<br>long                 | 0001<br>0005                 | serial shift register for $6 \cdot 8$ bit, filter coefficient channel 1 (48 bit) serial shift register for $6 \cdot 8$ bit, $+ 2 \cdot 12$ bit off set (total 72 bit) |

| DCO1_LO<br>DCO1_HI<br>DCO2_LO<br>DCO2_HI | long<br>long<br>long<br>long | 0093<br>009B<br>00A3<br>00AB | increment channel 1 Low Part<br>increment channel 1 High Part<br>increment channel 2 Low Part<br>increment channel 2 High Part                                        |

| PLL_CAP1)                                | short                        | 1F                           | switchable PLL capacities                                                                                                                                             |

Table 6-2: MSP 3400C demodulator read registers

| Register              | Protocol | Read<br>Address<br>(hex) | Function                                                                                                                                                         |

|-----------------------|----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL_CAP1)             | short    | 1F                       | switchable PLL capacities                                                                                                                                        |

| AGC_RMS <sup>1)</sup> | short    | 1E                       | RMS value, comparable with reference value                                                                                                                       |

| C_AD_BITS             | long     | 0023                     | A read from this address always responds with 0. This ensures software compatibility with the MSP 3410 readout. Reading 0 from this register signals "No NICAM". |

<sup>&</sup>lt;sup>1)</sup> The registers PLL\_CAP and AGC\_RMS are only available in MSP 3400C. In MSP 3410 and MSP 34x0D, this register cannot be accessed.

## 6.2. Registers: Functions and Values

In the following, the functions of several registers are explained and their (default) values are defined.

## 6.2.1. Setting of Parameter AD\_CV

Table 6-3: AD\_CV Register

| AD_CV Bit Range | Meaning                                                                                                          | Settings                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| AD_CV [0]       | not used                                                                                                         | must be set to 0                                      |

| AD_CV [6:1]     | Reference level in case of Automatic Gain Control = on. Constant gain factor when Automatic Gain Control = off . | see Table 6–5<br>see Table 6–6                        |

| AD_CV [7]       | Determination of Automatic Gain or Constant<br>Gain                                                              | 0 = constant gain<br>1 = automatic gain               |

| AD_CV [8]       | Selection of analog input                                                                                        | 0 = ANALOG IN1<br>1 = ANALOG IN2                      |

| AD_CV [9]       | MSPC-Carrier-Mute Function                                                                                       | 0 = off: no mute<br>1 = on: mute (see section 4.1.8.) |

| AD_CV [11-10]   | Programmable Carrier-Mute Level                                                                                  | see Table 6–4                                         |

| AD_CV [15-12]   | not used                                                                                                         | must be set to 0                                      |

Table 6-4: Carrier Mute Level

| Step        | AD_CV [11:10]<br>binary | AD_CV [11:10]<br>decimal | Internal reference level for mute active (dBr: relative to MSP 3410 ) |

|-------------|-------------------------|--------------------------|-----------------------------------------------------------------------|

| 0<br>1<br>2 | 00<br>01<br>10          | 0<br>1<br>2              | 0 dBr<br>-3 dBr<br>-6 dBr                                             |

| 3           | 11                      | 3                        | –12 dBr                                                               |

**Table 6–5:** Reference values AD\_CV [6:1] for active AGC (AD\_CV[7] = 1)

| Application    | Input Signal Contains                               | Ref. Value<br>binary | Ref. Value<br>decimal | Range of Input Signal at pin ANA_IN_1+ and ANA_IN_2+ |

|----------------|-----------------------------------------------------|----------------------|-----------------------|------------------------------------------------------|

| Terrestrial TV | 2 FM Carriers                                       | 101000               | 40                    | $0.14 - 3 V_{pp}^{1)}$                               |

| SAT            | 1 or more FM Carriers                               | 100011               | 35                    | 0.14 – 3 V <sub>pp</sub> <sup>1)</sup>               |

| ADR            | 1 or more FM Carriers and<br>1 or more ADR Carriers | 010100               | 20                    | 0.14 – 3 V <sub>pp</sub> <sup>1)</sup>               |

<sup>&</sup>lt;sup>1)</sup> For signals above 1.4 Vpp, the minimum gain of 3 dB is switched and overflow of the AD converter may result. Due to the robustness of the internal processing in FM mode, the IC works properly up to and even more than 3 Vpp. In AM mode, of course, no AD converter overflow is allowed. As a consequence, in the AM-mode, the maximum input at pins 41 or 43 must not exceed 1.4 Vpp.

**Table 6–6:** AD\_CV parameters for constant input gain (AD\_CV[7]=0)

| Step | AD_CV [6:1]<br>Constant Gain | Gain     | Input Level at pin ANA_IN1+ and ANA_IN2+                                               |

|------|------------------------------|----------|----------------------------------------------------------------------------------------|

| 0    | 000000                       | 3.00 dB  | maximum input level <sup>1)</sup> : 3 V <sub>pp</sub> (FM) or 1.4 V <sub>pp</sub> (AM) |

| 1    | 000001                       | 3.85 dB  |                                                                                        |

| 2    | 000010                       | 4.70 dB  |                                                                                        |

| 3    | 000011                       | 5.55 dB  |                                                                                        |

| 4    | 000100                       | 6.40 dB  |                                                                                        |

| 5    | 000101                       | 7.25 dB  |                                                                                        |

| 6    | 000110                       | 8.10 dB  |                                                                                        |

| 7    | 000111                       | 8.95 dB  |                                                                                        |

| 8    | 001000                       | 9.80 dB  |                                                                                        |

| 9    | 001001                       | 10.65 dB |                                                                                        |

| 10   | 001010                       | 11.50 dB |                                                                                        |

| 11   | 001011                       | 12.35 dB |                                                                                        |

| 12   | 001100                       | 13.20 dB |                                                                                        |

| 13   | 001101                       | 14.05 dB |                                                                                        |

| 14   | 001110                       | 14.90 dB |                                                                                        |

| 15   | 001111                       | 15.75 dB |                                                                                        |

| 16   | 010000                       | 16.60 dB |                                                                                        |

| 17   | 010001                       | 17.45 dB |                                                                                        |

| 18   | 010010                       | 18.30 dB |                                                                                        |

| 19   | 010011                       | 19.15 dB |                                                                                        |

| 20   | 010100                       | 20.00 dB | maximum input level: 0.14 V <sub>pp</sub> 1)                                           |

<sup>1)</sup> For signals above 1.4 Vpp, the minimum gain of 3 dB is switched and overflow of the AD converter may result. Due to the robustness of the internal processing in FM mode, the IC works properly up to and even more than 3 Vpp. In AM mode, of course, no AD converter overflow is allowed. As a consequence, in the AM-mode, the maximum input at pins 41 or 43 must not exceed 1.4 Vpp.

## 6.2.2. Control Register 'MODE\_REG'

The register 'MODE\_REG' contains the control bits determining the operation mode of the MSP 3400C; Table 6–7 explains all bit positions.

Table 6-7: Control word 'MODE\_REG': All bits are "0" after power-on-reset

| Bit  | Function                                 | Comment                                                        | Definition                                 | Recom-<br>mendation |  |  |  |

|------|------------------------------------------|----------------------------------------------------------------|--------------------------------------------|---------------------|--|--|--|

| [0]  | DMA_SYNC <sup>1)</sup>                   | Synchronization to DMA                                         | 0 : off<br>1 : on                          | Х                   |  |  |  |

| [1]  | DCTR_TRI                                 | Digital control out 0/1 tristate                               | 0 : active<br>1 : tristate                 | 0                   |  |  |  |

| [2]  | I2S_TRI                                  | I <sup>2</sup> S outputs tristate (I2S_CL, I2S_WS, I2S_DA_OUT) | 0 : active<br>1 : tristate                 | 0                   |  |  |  |

| [3]  | I <sup>2</sup> S Mode <sup>1)</sup>      | Master/Slave mode of the I <sup>2</sup> S bus                  | 0 : Master<br>1 : Slave                    | Х                   |  |  |  |

| [4]  | I <sup>2</sup> S_WS Mode                 | WS due to the Sony or Philips-Format                           | 0 : Sony<br>1 : Philips                    | Х                   |  |  |  |

| [5]  | Audio_CL_OUT                             | switch Audio_Clock_Output to tristate                          | 0 : on<br>1 : tristate                     | Х                   |  |  |  |

| [6]  | not used                                 |                                                                | must be 0                                  | 0                   |  |  |  |

| [7]  | FM1 FM2                                  | MSPC-channel 1 mode                                            |                                            | s.Table 6-8         |  |  |  |

| [8]  | AM                                       | MSPC-channel 1/2 mode                                          | 0 : FM<br>1 : AM                           | s.Table 6–8         |  |  |  |

| [9]  | HDEV                                     | High Deviation Mode<br>(channel matrix must be<br>sound A)     | 0 : normal mode<br>1 : high deviation mode | s.Table 6–8         |  |  |  |

| [10] | not used                                 |                                                                | must be 1                                  | 1                   |  |  |  |

| [11] | S-Bus Mode <sup>2)</sup>                 | mode of Pins S_CL and S_ID                                     | 0 : Tristate<br>1 : Active                 | 0                   |  |  |  |

| [12] | FM2 FIR Filter Gain<br>(FM2 = Ch1)       | see table 6–10                                                 | 0 : Gain = 6 dB<br>1 : Gain = 0 dB         | 0                   |  |  |  |

| [13] | FM2 FIR Filter Coeff. Set<br>(FM2 = Ch1) | see table 6–10                                                 | 0 : use FIR_REG_1<br>1 : use FIR_REG_2     | 0                   |  |  |  |

| [14] | ADR                                      | Mode of ADR Interface                                          | 0 : normal mode<br>1 : ADR mode            | Х                   |  |  |  |

| [15] | AM-Gain                                  | additional gain in AM-mode                                     | 0 : 0 dB<br>1 : +12 dB                     | 0                   |  |  |  |

| In c |                                          |                                                                |                                            |                     |  |  |  |

Table 6-8: Channel modes 'MODE\_REG [7-9]'

| FM1 FM2<br>bit[7] | AM<br>bit[8] | HDEV<br>bit[9] | channel 1                | channel 2                |

|-------------------|--------------|----------------|--------------------------|--------------------------|

| 0                 | 0            | 0              | mute                     | FM-Mono (FM1)            |

| 1                 | 0            | 0              | FM2                      | FM1                      |

| Х                 | 1            | 0              | AM                       | AM                       |

| Х                 | X            | 1              | FM-Mono (high deviation) | FM-Mono (high deviation) |

#### 6.2.3. FIR-Filter Switches

To simplify programming of the MSP 3400C, two additional switches have been implemented.

The FIR filter for channel1/FM2 can use either FIR\_REG\_1 coefficients or FIR\_REG\_2 coefficients by means of MODE\_REG[13]. Herewith, it is no longer necessary to transmit both coefficient sets in FM-terrestrial mode. The loading sequence for FIR\_REG\_2 is sufficient.

The additional gain of +6 dB in channel1/FM2 can be switched to 0 dB by means of MODE\_REG[12]. Together with MODE\_REG[13] set to 1, in satellite mode, it is no longer necessary to transmit both FIR filter coefficient sets. The loading sequence for FIR\_REG\_2 is sufficient.

## 6.2.4. FIR-Parameter

The following data values (see Table 6–9) are to be transferred 8 bits at a time embedded LSB-bound in a 16 bit word. These sequences must be obeyed. To change a coefficient set, the complete block FIR\_REG\_1 or FIR\_REG\_2 must be transmitted. The new coefficient set will be active without a load\_reg routine.

Table 6-9: Loading sequence for FIR-coefficients

| WRITE_ADR = FIR_REG_1(Channel 1: FM2) |                |      |                 |  |  |  |

|---------------------------------------|----------------|------|-----------------|--|--|--|

| No.                                   | Symbol Name    | Bits | Value           |  |  |  |

| 1                                     | FM2_Coeff. (5) | 8    | see Table 6-10. |  |  |  |

| 2                                     | FM2_Coeff. (4) | 8    |                 |  |  |  |

| 3                                     | FM2_Coeff. (3) | 8    |                 |  |  |  |

| 4                                     | FM2_Coeff. (2) | 8    |                 |  |  |  |

| 5                                     | FM2_Coeff. (1) | 8    |                 |  |  |  |

| 6                                     | FM2_Coeff. (0) | 8    |                 |  |  |  |

| WRITE_ADR = FIR_REG_2 (Channel 2: FM1/FM mono) |                                        |      |                 |  |  |

|------------------------------------------------|----------------------------------------|------|-----------------|--|--|

| No.                                            | Symbol Name                            | Bits | Value           |  |  |

| 1                                              | * IMREG1 (8 LSBS)                      | 8    | 04 HEX          |  |  |

| 2                                              | * IMREG1 / IMREG2<br>(4 MSBs / 4 LSBs) | 8    | 40 HEX          |  |  |

| 3                                              | * IMREG2 (8 MSBs)                      | 8    | 00 HEX          |  |  |

| 4                                              | FM_Coef (5)                            | 8    | see Table 6-10. |  |  |

| 5                                              | FM_Coef (4)                            | 8    |                 |  |  |

| 6                                              | FM_Coef (3)                            | 8    |                 |  |  |

| 7                                              | FM_Coef (2)                            | 8    |                 |  |  |

| 8                                              | FM_Coef (1)                            | 8    |                 |  |  |

| 9                                              | FM_Coef (0)                            | 8    |                 |  |  |

| * IMREG_1/2: Two 12-bit off-set constants      |                                        |      |                 |  |  |

Table 6-10: 8-bit FIR-coefficients (decimal integer) for MSP 3410D; reset status: all coefficients are "0"

| Coefficients for | FIR1 0001 <sub>hex</sub> and FIR2 0005 | hex      |                                                      |         |         |                     |             |            |

|------------------|----------------------------------------|----------|------------------------------------------------------|---------|---------|---------------------|-------------|------------|

|                  | Terrestrial TV-Standards               | bandpass | ellite<br>corresponds<br>with a band<br>= 130 to 500 |         |         | f <sub>c</sub> free | _<br>quency |            |

|                  | B/G-,D/K-,M-Dual FM                    | 130 kHz  | 180 kHz                                              | 200 kHz | 280 kHz | 380 kHz             | 500 kHz     | Autosearch |

| Coef(i)          | FIR2                                   | FIR2     | FIR2                                                 | FIR2    | FIR2    | FIR2                | FIR2        | FIR2       |

| 0                | 3                                      | 73       | 9                                                    | 3       | -8      | -1                  | -1          | 75         |

| 1                | 18                                     | 53       | 18                                                   | 18      | -8      | -9                  | -1          | 19         |

| 2                | 27                                     | 64       | 28                                                   | 27      | 4       | -16                 | -8          | 36         |

| 3                | 48                                     | 119      | 47                                                   | 48      | 6       | 5                   | 2           | 35         |

| 4                | 66                                     | 101      | 55                                                   | 66      | 78      | 65                  | 59          | 39         |

| 5                | 72                                     | 127      | 64                                                   | 72      | 107     | 123                 | 126         | 40         |

| MODE-REG[12]     | 0                                      | 1        | 1                                                    | 1       | 1       | 1                   | 1           | 0          |

| MODE-REG[13]     | 1                                      | 1        | 1                                                    | 1       | 1       | 1                   | 1           | 0          |

MODE\_REG[12] should be set to 0 (= 6 dB gain) if the level of the FM2-carrier processed in MSP-Ch1 is appr. 7 dB below the FM1-carrier of MSP-Ch2. If both carriers have the same level, MODE\_REG[12] must be set to 1 (=0 dB gain).

$MODE\_REG[13]: If in MSP-Channel 1 and 2 the same bandwidth is required, it is sufficient to transmit FIR\_REG2 only and to set \\ MODE\_REG[13] to 1.$

For compatibility (besides the above programming), the FIR-filter programming as used for the MSP 3410B is also possible.

ADR coefficients are listed in the DRP-data sheet.

The 130 kHz coefficients are based on subcarriers, which are 7 dB below an existent main carrier.

#### 6.2.5. DCO-Increments

For a chosen TV standard, a corresponding set of 24-bit increments determining the mixing frequencies of the quadrature mixers, has to be written into the IC. In Table 6–11, several examples of DCO increments are listed. It is necessary to divide them into low part and high part. The formula for the calculation of the increments for any chosen IF-Frequency is as follows:

$INCR_{dez} = int(f/fs \cdot 2^{24})$

with: int = integer function

f = IF-frequency in MHz

f<sub>S</sub> = sampling frequency (18.432 MHz)

Conversion of INCR into hex-format and separation of the 12-bit low and high parts lead to the required increments. (DCO1\_HI or \_LO for channel 1, DCO2\_HI or LO for channel 2).

Table 6-11: DCO increments for the MSP 3400C; frequency in MHz, increments in Hex

| Frq. MHz                         | DCO_HI                       | DCO_LO                       | Frq. MHz             | DCO_HI               | DCO_LO               |

|----------------------------------|------------------------------|------------------------------|----------------------|----------------------|----------------------|

| 4.5                              | 03E8                         | 0000                         |                      |                      |                      |

| 5.04<br>5.5<br>5.58<br>5.7421875 | 0460<br>04C6<br>04D8<br>04FC | 0000<br>038E<br>0000<br>00AA | 5.76<br>5.85<br>5.94 | 0500<br>0514<br>0528 | 0000<br>0000<br>0000 |

| 6.0<br>6.2<br>6.5<br>6.552       | 0535<br>0561<br>05A4<br>05B0 | 0555<br>0C71<br>071C<br>0000 | 6.6<br>6.65<br>6.8   | 05BA<br>05C5<br>05E7 | 0AAA<br>0C71<br>01C7 |

| 7.02                             | 0618                         | 0000                         | 7.2                  | 0640                 | 0000                 |

| 7.38                             | 0668                         | 0000                         | 7.56                 | 0690                 | 0000                 |

## 6.3. Sequences to Transmit Parameters and to Start Processing

After having been switched on, the MSPC must be initialized by transmitting the parameters according to the LOAD\_SEQ\_1/2 of Table 6–12. In the MSPC, the initialization sequence must no longer be terminated by transmitting LOAD\_REG\_1/2. The transmitted data are active as soon as the corresponding I<sup>2</sup>C telegram has finished. Therefore, while changing parameters of the demodulator section, a mute is recommended for the affected channel (LOAD\_SEQ\_1/2: mute all FM, LOAD\_SEQ\_1: switch audio processing to channel2/FM1 or mute channel1/FM2). Otherwise, distorted sound may occur while switching.

For FM-stereo operation, the evaluation of the identification signal must be performed. For positive identification check, the MSP 3400C sound channels have to be switched corresponding to the detected operation mode.

## 6.4. Software Proposals for Multistandard TV-Sets

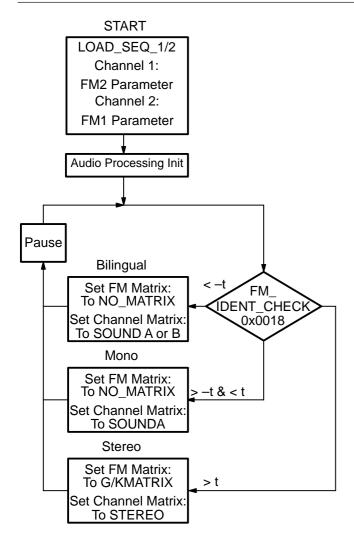

To familiarize the reader with the programming scheme of the MSP 3400C, two examples in the shape of flow diagrams are shown in the following sections.

## 6.4.1. Multistandard System B/G German DUAL FM

Fig. 6–1 shows a flow diagram for the CCU software, applied for the MSP 3400C in a TV set, which facilitates all standards according to System B/G. For the instructions used in the diagram, please refer to Table 6–12.

After having switched on the TV-set and having initialized the MSP 3400C (LOAD\_SEQ\_1/2), FM-mono sound is available.

Fig. 6–1 shows how to check for any stereo or bilingual audio information in channel 1. If successful, the MSP 3400C must be switched to the desired audio mode.

Table 6–12: Sequences to initialize and start the MSP 3400C

## LOAD\_SEQ\_1/2: General Initialization

- 1. AD\_CV

- 2. FIR\_REG\_1

- 3. FIR\_REG\_2

- 4. MODE\_REG

- 5. DCO1\_LO

- 6. DCO1\_HI

- 7. DCO2 LO

- 8. DCO2\_HI

## FM\_IDENT\_CHECK: Decoding of the identification signal

- 1. Evaluation of the stereo detection register (DFP register 0018<sub>hex</sub>, high part)

- 2. If necessary, switch the corresponding sound channels within the audio processing part

### LOAD\_SEQ\_1: Reinitialization of Channel 1 without affecting Channel 2

1. FIR\_REG\_1 (6 · 8 bit)

2. MODE\_REG (12 bit)

3. DCO1\_LO (12 bit)

4. DCO1\_HI

**Fig. 6–1:** CCU software flow diagram: Standard B/G, t = threshold value for stereo/bilingual detection

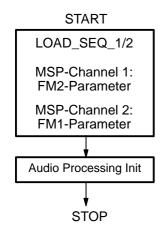

Fig. 6-2: CCU software flow diagram: SAT-mode

## 6.4.2. Satellite Mode

Fig. 6–2 shows the simple flow diagram to be used for the MSP 3400C in a satellite receiver. For FM-mono operation, the corresponding FM carrier should preferably be processed at the MSPC-channel 2 or at the MSPC-channel 1 with FIR gain = 0 dB.

## 6.4.3. Automatic Search Function for FM-Carrier Detection

The AM demodulation ability of the MSP 3400C offers the possibility to calculate the "field strength" of the momentarily selected FM carrier, which can be read out by the CCU. In SAT receivers, this feature can be used to make automatic FM carrier search possible.

Therefore, the MSPC has to be switched to AM-mode (MODE\_REG[8]), FM-Prescale must be set to  $7F_{hex}$ =+127<sub>dez</sub>, and the FM DC Notch must be switched off. The sound-IF frequency range must now be "scanned" in the MSPC-channel 2 by means of the programmable quadrature mixer with an appropriate incremental frequency (i.e. 10 kHz).

After each incrementation, a field strength value is available at the quasi-peak detector output (quasi-peak detector source must be set to FM), which must be examined for relative maxima by the CCU. This results in either continuing search or switching the MSP 3400C back to FM demodulation mode.

During the search process, the FIR\_REG\_2 must be loaded with the coefficient set "AUTOSEARCH", which enables small bandwidth, resulting in appropriate field strength characteristics. The absolute field strength value (can be read out of "quasi peak detector output FM1") also gives information on whether a main FM carrier or a subcarrier was detected, and as a practical consequence, the FM bandwidth (FIR\_REG\_1/2) and the deemphasis (50  $\mu s$  or adaptive) can be switched automatically.

Due to the fact that a constant demodulation frequency offset of a few kHz, leads to a DC-level in the demodulated signal, a further fine tuning of the found carrier can be achieved by evaluating the "DC Level Readout FM1". Therefore, the FM DC Notch must be switched on, and the demodulator part must be switched back to FM-demodulation mode.

For a detailed description of the automatic search function, please refer to the corresponding MSP 3400C Windows software.

**Note:** The automatic search is still possible by evaluating only the DC Level Readout FM1 (DC Notch On) as it is described with the MSP 3410, but the above mentioned method is faster.

### 6.4.4. Automatic Standard Detection

The AM demodulation ability of the MSP 3400 C enables a simple method of deciding between standard B/G (FM-carrier at 5.5 MHz) and standard I (FM-carrier at 6.0 MHz). It is achieved by tuning the MSP 3400C in the AM-mode to the two discrete frequencies and evaluating the field strength via the DC level register or the quasi-peak detector output (Mode\_Reg, DC Notch, FM Prescale as described in section 6.4.3.).

## 7. Programming the Audio Processing Part

## 7.1. Summary of the DSP Control Registers

Control registers are 16 bit wide. Transmissions via I<sup>2</sup>C bus have to take place in 16 bit words. Single data entries are 8 bit. Some of the defined 16 bit words are divided into low and high byte, thus holding two different control entities. All control registers are readable. Note: Unused parts of the 16 bit registers must be zero.

Table 7-1: DSP Control Registers

| Name                                    | I <sup>2</sup> C Bus<br>Address | High/<br>Low | Adjustable Range, Operational Modes                           | Reset Mode        |

|-----------------------------------------|---------------------------------|--------------|---------------------------------------------------------------|-------------------|

| Volume loudspeaker channel              | 0000 <sub>hex</sub>             | Н            | [+12 dB –114 dB, MUTE]                                        | MUTE              |

| Volume / Mode loudspeaker channel       |                                 | L            | 1/8 dB Steps, Reduce Volume / Tone Control                    | 00 <sub>hex</sub> |

| Balance loudspeaker channel [L/R]       | 0001 <sub>hex</sub>             | Н            | [0100 / 100 % and vv][-1270 / 0 dB and vv]                    | 100%/100%         |

| Balance Mode loudspeaker                |                                 | L            | [Linear mode / logarithmic mode]                              | linear mode       |

| Bass loudspeaker channel                | 0002 <sub>hex</sub>             | Н            | [+20 dB –12 dB]                                               | 0 dB              |

| Treble loudspeaker channel              | 0003 <sub>hex</sub>             | Н            | [+15 dB –12 dB]                                               | 0 dB              |

| Loudness loudspeaker channel            | 0004 <sub>hex</sub>             | Н            | [0 dB +17 dB]                                                 | 0 dB              |