# **ELPIDA**

### PRELIMINARY DATA SHEET

# 512M bits DDR3 SDRAM

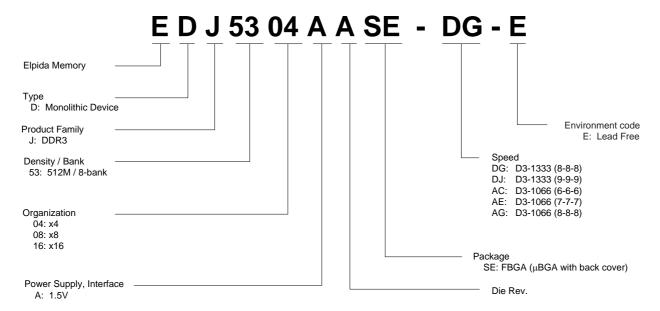

# EDJ5304AASE (128M words × 4 bits) EDJ5308AASE (64M words × 8 bits) EDJ5316AASE (32M words × 16 bits)

#### **Description**

The EDJ5304AASE is a 512M bits DDR3 SDRAM organized as 16,777,216 words  $\times$  4 bits  $\times$  8 banks.

The EDJ5308AASE is a 512M bits DDR3 SDRAM organized as 8,388,608 words  $\times$  8 bits  $\times$  8 banks.

They are packaged in 78-ball FBGA ( $\mu$ BGA $^{\$}$ ) package. The EDJ5316AASE is a 512M bits DDR3 SDRAM organized as 4,194,304 words  $\times$  16 bits  $\times$  8 banks.

It is packaged in 96-ball FBGA (μBGA®) package.

#### **Features**

- Power supply: VDD, VDDQ =  $1.5V \pm 0.075V$

- Data rate: 1333Mbps/1066Mbps (max.)

- Double-data-rate architecture: two data transfers per clock cycle

- Bi-directional, differential data strobe (DQS and /DQS) is transmitted/received with data, to be used in capturing data at the receiver

- DQS is edge aligned with data for READs: centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge: data and data mask referenced to both edges of DQS

- 8 internal banks for concurrent operation

- Data mask (DM) for write data

- Burst lengths (BL): 4, 8 and 4 with burst chop

- /CAS latency (CL): 5, 6, 7, 8, 9, 10

- /CAS write latency (CWL): 5, 6, 7, 8

- Auto precharge operation for each burst access

- · Auto refresh and self refresh modes

- Average refresh period: 7.8µs

- 1.5V I/O

- Posted CAS by programmable additive latency for better command and data bus efficiency

- On-Die-Termination for better signal quality

- Programmable Partial Array Self Refresh

- ZQ calibration for DQ drive and On-Die-Termination

- RESET-pin for Power-up sequence and resetfunction

- FBGA (μBGA) package with lead free solder (Sn-Ag-Cu)

- RoHs compliant

# **Ordering Information**

| Part number      | Mask<br>version | Organization (words × bits) | Internal<br>Banks | Speed bin<br>(CL-tRCD-tRP) | Package             |

|------------------|-----------------|-----------------------------|-------------------|----------------------------|---------------------|

| EDJ5304AASE-DG-E |                 |                             |                   | D3-1333 (8-8-8)            |                     |

| EDJ5304AASE-DJ-E |                 |                             |                   | D3-1333 (9-9-9)            |                     |

| EDJ5304AASE-AC-E | Α               | $128M \times 4$             | 8                 | D3-1066 (6-6-6)            | 78-ball FBGA (μBGA) |

| EDJ5304AASE-AE-E |                 |                             |                   | D3-1066 (7-7-7)            |                     |

| EDJ5304AASE-AG-E |                 |                             |                   | D3-1066 (8-8-8)            |                     |

| EDJ5308AASE-DG-E |                 |                             |                   | D3-1333 (8-8-8)            |                     |

| EDJ5308AASE-DJ-E |                 |                             |                   | D3-1333 (9-9-9)            |                     |

| EDJ5308AASE-AC-E |                 | $64M \times 8$              |                   | D3-1066 (6-6-6)            |                     |

| EDJ5308AASE-AE-E |                 |                             |                   | D3-1066 (7-7-7)            |                     |

| EDJ5308AASE-AG-E |                 |                             |                   | D3-1066 (8-8-8)            |                     |

| EDJ5316AASE-DG-E |                 |                             |                   | D3-1333 (8-8-8)            |                     |

| EDJ5316AASE-DJ-E |                 |                             |                   | D3-1333 (9-9-9)            |                     |

| EDJ5316AASE-AC-E |                 | $32M \times 16$             |                   | D3-1066 (6-6-6)            | 96-ball FBGA (μBGA) |

| EDJ5316AASE-AE-E |                 |                             |                   | D3-1066 (7-7-7)            |                     |

| EDJ5316AASE-AG-E |                 |                             |                   | D3-1066 (8-8-8)            |                     |

### **Part Number**

#### NOTES FOR CMOS DEVICES -

#### (1) PRECAUTION AGAINST ESD FOR MOS DEVICES

Exposing the MOS devices to a strong electric field can cause destruction of the gate oxide and ultimately degrade the MOS devices operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it, when once it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. MOS devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. MOS devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor MOS devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS DEVICES

No connection for CMOS devices input pins can be a cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. The unused pins must be handled in accordance with the related specifications.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Power-on does not necessarily define initial status of MOS devices. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the MOS devices with reset function have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. MOS devices are not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for MOS devices having reset function.

CME0107

# EDJ5304AASE, EDJ5308AASE, EDJ5316AASE

µBGA is a registered trademark of Tessera, Inc.

All other trademarks are the intellectual property of their respective owners.

The information in this document is subject to change without notice. Before using this document, confirm that this is the latest version.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Elpida Memory, Inc.

Elpida Memory, Inc. does not assume any liability for infringement of any intellectual property rights (including but not limited to patents, copyrights, and circuit layout licenses) of Elpida Memory, Inc. or third parties by or arising from the use of the products or information listed in this document. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of Elpida Memory, Inc. or others.

Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of the customer's equipment shall be done under the full responsibility of the customer. Elpida Memory, Inc. assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

#### [Product applications]

Elpida Memory, Inc. makes every attempt to ensure that its products are of high quality and reliability. However, users are instructed to contact Elpida Memory's sales office before using the product in aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment, medical equipment for life support, or other such application in which especially high quality and reliability is demanded or where its failure or malfunction may directly threaten human life or cause risk of bodily injury.

#### [Product usage]

Design your application so that the product is used within the ranges and conditions guaranteed by Elpida Memory, Inc., including the maximum ratings, operating supply voltage range, heat radiation characteristics, installation conditions and other related characteristics. Elpida Memory, Inc. bears no responsibility for failure or damage when the product is used beyond the guaranteed ranges and conditions. Even within the guaranteed ranges and conditions, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Elpida Memory, Inc. products does not cause bodily injury, fire or other consequential damage due to the operation of the Elpida Memory, Inc. product.

#### [Usage environment]

This product is not designed to be resistant to electromagnetic waves or radiation. This product must be used in a non-condensing environment.

If you export the products or technology described in this document that are controlled by the Foreign Exchange and Foreign Trade Law of Japan, you must follow the necessary procedures in accordance with the relevant laws and regulations of Japan. Also, if you export products/technology controlled by U.S. export control regulations, or another country's export control laws or regulations, you must follow the necessary procedures in accordance with such laws or regulations.

If these products/technology are sold, leased, or transferred to a third party, or a third party is granted license to use these products, that third party must be made aware that they are responsible for compliance with the relevant laws and regulations.

M01E0107