# Digital Step Attenuator 75Ω DC-2000 MHz

31 dB, 1dB Step 5 Bit, Parallel Control Interface, Dual Supply Voltage

#### **Product Features**

- Dual Supply Voltage: V<sub>DD</sub>=+3V, V<sub>SS</sub>=-3V

- Immune to latch up

- Excellent accuracy, 0.1 dB Typ

- · Parallel control interface

- · Fast switching control frequency, 1 MHz typ.

- Low Insertion Loss

- High IP3, +52 dBm

- Very low DC power consumption

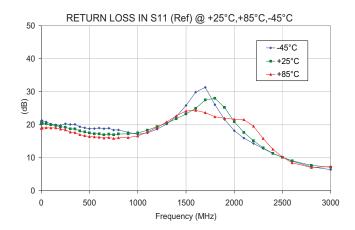

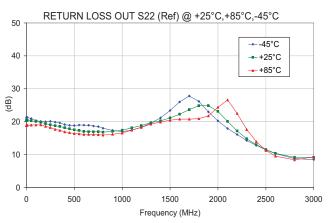

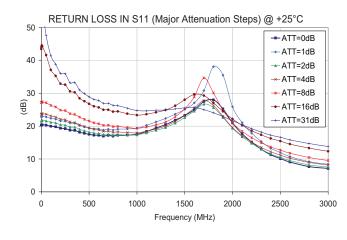

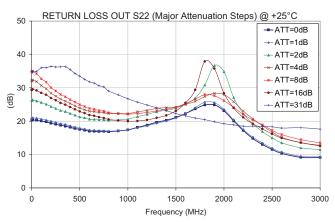

- Excellent return loss, 20 dB Typ

- Small size 4.0 x 4.0 mm

#### **Typical Applications**

- Base Station Infrastructure

- Portable Wireless

- CATV & DBS

- MMDS & Wireless LAN

- Wireless Local Loop

- UNII & Hiper LAN

- Power amplifier distortion canceling loops

**DAT-3175-PN+ DAT-3175-PN**

CASE STYLE: DG983-1 PRICE: \$3.55 ea. QTY. (10-24)

+ RoHS compliant in accordance with EU Directive (2002/95/EC)

The +Suffix identifies RoHS Compliance. See our web site for RoHS Compliance methodologies and qualifications

#### **General Description**

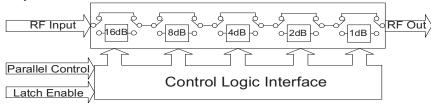

The DAT-3175-PN is a 75 $\Omega$  RF digital step attenuator that offers an attenuation range up to 31 dB in 1.0 dB steps. The control is a 5-bit parallel interface, operating on dual supply voltage:  $V_{DD}$ =+3V,  $V_{SS}$ =-3V. The DAT-3175-PN is produced using a unique CMOS process on silicon, offering the performance of GaAs, with the advantages of conventional CMOS devices.

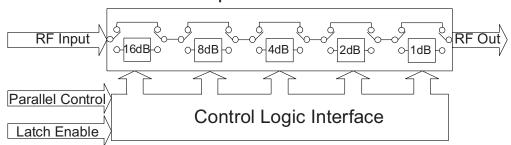

#### Simplified Schematic

For detailed performance specs & shopping online see web site

ISO 9001 ISO 14001 AS 9100 CERTIFIED

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 The Design Engineers Search Engine

Provides ACTUAL Data Instantly at minicipouits. IF/RF MICROWAVE COMPONENTS

RFV F

#### RF Electrical Specifications, DC-2000 MHz, T<sub>AMB</sub>=25°C, V<sub>DD</sub>=+3V, V<sub>SS</sub>=-3V

| Parameter                                                                          | Freq. Range<br>(GHz) | Min. | Тур. | Max. | Units |

|------------------------------------------------------------------------------------|----------------------|------|------|------|-------|

| Accuracy @ 1 dB Attenuation Setting                                                | DC-1.2               | _    | 0.03 | 0.24 | dB    |

| Accuracy & I db Attendation Setting                                                | 1.2-2.0              | _    | 0.1  | 0.25 | dB    |

| Accuracy @ 2 dB Attenuation Setting                                                | DC-1.2               | _    | 0.07 | 0.28 | dB    |

| Accuracy @ 2 db Attendation Setting                                                | 1.2-2.0              | _    | 0.15 | 0.3  | dB    |

| Accuracy @ 4 dB Attenuation Setting                                                | DC-1.2               | _    | 0.05 | 0.36 | dB    |

| Accuracy & 4 db Attendation Setting                                                | 1.2-2.0              | _    | 0.15 | 0.4  | dB    |

| Acquirect @ 9 dB Attenuation Setting                                               | DC-1.2               | _    | 0.1  | 0.52 | dB    |

| Accuracy @ 8 dB Attenuation Setting                                                | 1.2-2.0              | _    | 0.24 | 0.6  | dB    |

| Accuracy @ 16 dB Attenuation Setting                                               | DC-1.2               |      | 0.23 | 0.84 | dB    |

| Accuracy @ 16 db Attendation Setting                                               | 1.2-2.0              |      | 0.8  | 1.0  | dB    |

|                                                                                    | DC-1.2               | _    | 1.2  | 1.8  | dB    |

| Insertion Loss <sup>(note1)</sup> @ all attenuator set to 0dB                      | 1.2-2.0              | _    | 1.6  | 2.1  | dB    |

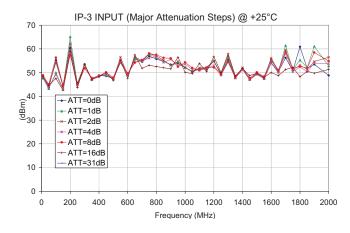

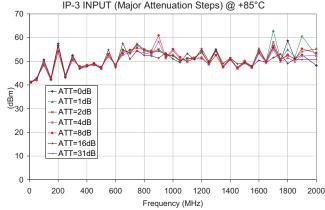

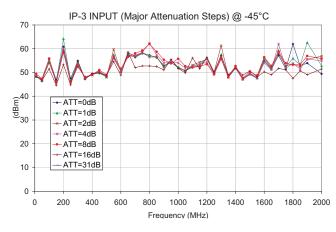

| Input IP3 <sup>(note 2)</sup> (At Min. and Max. Attenuation)                       | DC-2.0               | _    | +52  | _    | dBm   |

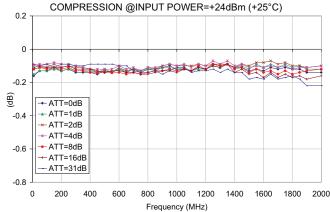

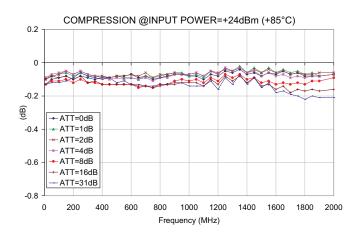

| Input Power @ 0.2dB Compression <sup>(note 2)</sup> (At Min. and Max. Attenuation) | DC-2.0               | _    | +24  | _    | dBm   |

| VSWR                                                                               | DC-1.2               | _    | 1.6  | 2.0  | _     |

| VOVVN                                                                              | 1.2-2.0              | _    | 1.7  | 2.0  | _     |

#### Notes:

#### **DC Electrical Specifications**

| Parameter                        | Min.    | Тур. | Max.                | Units |

|----------------------------------|---------|------|---------------------|-------|

| V <sub>DD</sub> , Supply Voltage | 2.7     | 3    | 3.3                 | V     |

| Vss, Supply Voltage              | -3.3    | -3   | -2.7                | V     |

| IDD (Iss), Supply Current        | _       | _    | 100                 | μΑ    |

| Control Input Low                | _       | _    | 0.3xV <sub>DD</sub> | V     |

| Control Input High               | 0.7xVDD | _    | _                   | V     |

| Control Current                  | _       | _    | 1                   | μΑ    |

#### **Switching Specifications**

| Parameter                                                  | Min. | Тур. | Max. | Units |

|------------------------------------------------------------|------|------|------|-------|

| Switching Speed, 50% Control to 0.5dB of Attenuation Value | _    | 1.0  | _    | μSec  |

| Switching Control Frequency                                | ı    | 1.0  | _    | MHz   |

#### **Absolute Maximum Ratings**

| Parameter             | Ratings                   |

|-----------------------|---------------------------|

| Operating Temperature | -40°C to 85°C             |

| Storage Temperature   | -55°C to 100°C            |

| V <sub>DD</sub>       | -0.3V Min., 4V Max.       |

| Vss                   | -4V Min., 0.3V Max.       |

| Voltage on any input  | -0.3V Min., VDD+0.3V Max. |

| ESD, HBM              | 500V                      |

| ESD, MM               | 100V                      |

| Input Power           | +24dBm                    |

Permanent damage may occur if any of these limits are exceeded.

For detailed performance specs & shopping online see web site

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 The Design Engineers Search Engine Provides ACTUAL Data Instantly at minicipcuits.com IF/RF MICROWAVE COMPONENTS

<sup>1.</sup> I. Loss values are de-embedded from test board Loss (test board's Insertion Loss: 0.10dB @100MHz, 0.40dB @1200MHz, 0.55dB @2000MHz, 0.75dB @4000MHz)

<sup>2.</sup> Input IP3 and 1dB compression degrades below 1 MHz

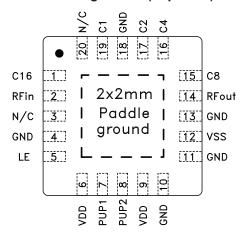

### **Pin Description**

| Function        | Pin<br>Number | Description                                |

|-----------------|---------------|--------------------------------------------|

| C16             | 1             | Control for Attenuation bit, 16dB (Note 3) |

| RF in           | 2             | RF in port (Note 1)                        |

| N/C             | 3             | Not connected (Note 4)                     |

| GND             | 4             | Ground connection                          |

| LE              | 5             | Latch Enable Input (Note 2)                |

| $V_{DD}$        | 6             | Positive Supply Voltage                    |

| PUP1            | 7             | Power-up selection                         |

| PUP2            | 8             | Power-up selection                         |

| $V_{DD}$        | 9             | Positive Supply Voltage                    |

| GND             | 10            | Ground connection                          |

| GND             | 11            | Ground connection                          |

| V <sub>SS</sub> | 12            | Negative Supply Voltage                    |

| GND             | 13            | Ground connection                          |

| RF out          | 14            | RF out port (Note 1)                       |

| C8              | 15            | Control for attenuation bit, 8 dB          |

| C4              | 16            | Control for attenuation bit, 4 dB          |

| C2              | 17            | Control for attenuation bit, 2 dB          |

| GND             | 18            | Ground Connection                          |

| C1              | 19            | Control for attenuation bit, 1 dB          |

| N/C             | 20            | Not connected (Note 4)                     |

| GND             | Paddle        | Paddle ground (Note 5)                     |

#### Notes:

- 1. Both RF ports must be held at 0VDC or DC blocked with an external series capacitor.

- 2. Latch Enable (LE) has an internal 100K $\Omega$  resistor to  $V_{DD}$ .

- 3. Place a  $10K\Omega$  resistor in series, as close to pin as possible to avoid freq. resonance.

- 4. Place a shunt  $10K\Omega$  resistor to GND.

- 5. The exposed solder pad on the bottom of the package (See Pin configuration) must be grounded for proper device operation.

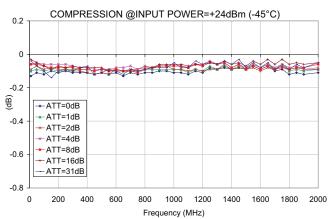

#### **Pin Configuration (Top View)**

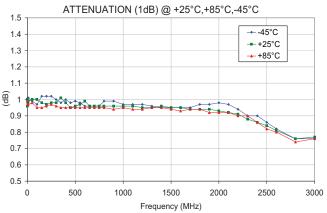

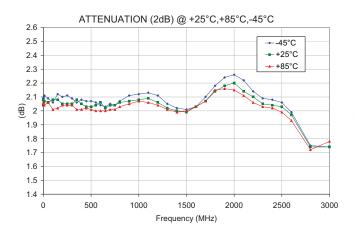

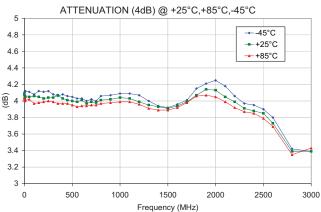

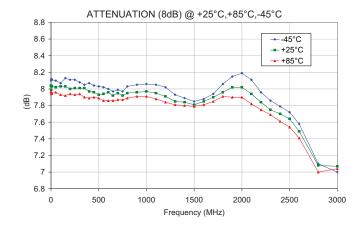

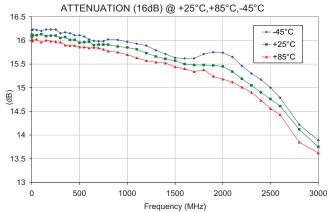

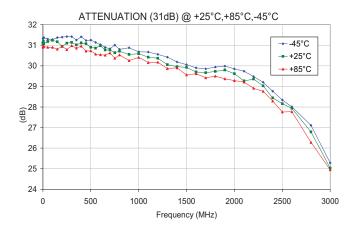

#### **Typical Performance Curves**

For detailed performance specs

ISO 9001 ISO 14001 AS 9100 CERTIFIED

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 The Design Engineers Search Engine

Provides ACTUAL Data Instantly at minicipality.com IF/RF MICROWAVE COMPONENTS

# **Typical Performance Curves**

For detailed performance specs

ISO 9001 ISO 14001 AS 9100 CERTIFIED

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 The Design Engineers Search Engine

Provides ACTUAL Data Instantly at minicipality. IF/RF MICROWAVE COMPONENTS

#### **Typical Performance Curves**

For detailed performance specs & shopping online see web site

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 The Design Engineers Search Engine Provides ACTUAL Data Instantly at minicipcuits.com IF/RF MICROWAVE COMPONENTS

## **Outline Drawing (DG983-1)**

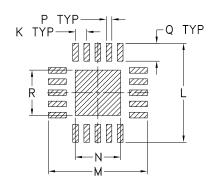

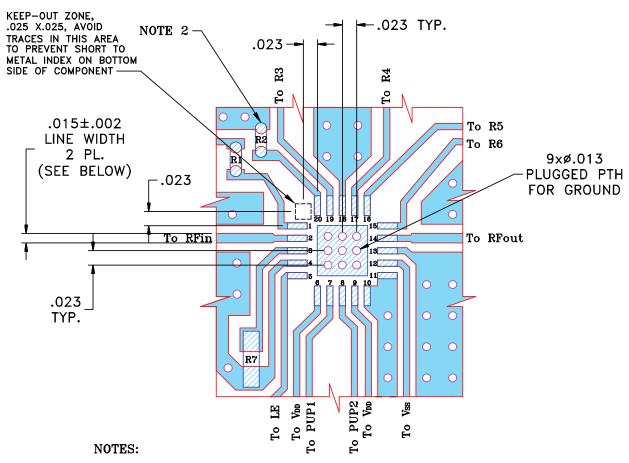

#### **PCB Land Pattern**

Suggested Layout, Tolerance to be within ±.002

## **Device Marking**

# Outline Dimensions (inch)

| А    | В    | С    | D    | E    | F    | G    | Н | J    | К    | L    | М    | N    | Р    | Q    | R    | WT.<br>GRAMS |

|------|------|------|------|------|------|------|---|------|------|------|------|------|------|------|------|--------------|

| .157 | .157 | .035 | .008 | .081 | .081 | .010 | _ | .022 | .020 | .177 | .177 | .081 | .010 | .032 | .081 | .04          |

|      |      |      |      |      |      |      |   |      |      |      |      |      |      |      |      |              |

For detailed performance specs & shopping online see web site

#### Suggested Layout for PCB Design (PL-192)

The suggested Layout shows only the footprint area of the DAT, and the components located near this area (i.e.: R1, R2, R7). For the complete Layout, see photo and schematic diagram on page 11 of 12.

- 1. TRACE WIDTH IS SHOWN FOR FR4 WITH DIELECTRIC THICKNESS. .025" $\pm .002$ ". COPPER: 1/2 OZ. EACH SIDE. FOR OTHER MATERIALS TRACE WIDTH MAY NEED TO BE MODIFIED.

- 2. 0603, 0402 SIZES CHIP FOOT PRINTS SHOWN FOR REFERENCE, VALUES OF RESISTORS WILL VARY BASED ON APPLICATION.

- 3. BOTTOM SIDE OF THE PCB IS CONTINUOUS GROUND PLANE.

For detailed performance specs

#### **Simplified Schematic**

The DAT-3175-PN parallel interface consists of 5 control bits that select the desired attenuation state, as shown in Table 1: Truth Table

| Table 1. Truth Table |                |                 |               |          |    |  |  |  |

|----------------------|----------------|-----------------|---------------|----------|----|--|--|--|

| Attenuation<br>State | C16            | C8              | C4            | C2       | C1 |  |  |  |

| Reference            | 0              | 0               | 0             | 0        | 0  |  |  |  |

| 1 (dB)               | 0              | 0               | 0             | 0        | 1  |  |  |  |

| 2 (dB)               | 0              | 0               | 0             | 1        | 0  |  |  |  |

| 4 (dB)               | 0              | 0               | 1             | 0        | 0  |  |  |  |

| 8 (dB)               | 1              | 0               | 0             | 0        | 0  |  |  |  |

| 16 (dB)              | 1              | 0               | 0             | 0        | 0  |  |  |  |

| 31 (dB)              | 1              | 1               | 1             | 1        | 1  |  |  |  |

| Note: Not all 32     | possible combi | nations of C1 - | C16 are shown | in table |    |  |  |  |

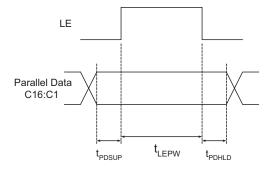

The parallel interface timing requirements are defined by **Figure 1** (Parallel Interface Timing Diagram) and **Table 2** (Parallel Interface AC Characteristics), and switching speed.

For latched parallel programming the Latch Enable (LE) should be held LOW while changing attenuation state control values, then pulse LE HIGH to LOW (per Figure 1) to latch new attenuation state into device.

For direct parallel programming, the Latch Enable (LE) line should be pulled HIGH. Changing attenuation state control values will change device state to new attenuation. Direct mode is ideal for manual control of the device (using hardwire, switches, or jumpers).

Figure 1: Parallel Interface Timing Diagram

| Table 2. Parallel Interface AC Characteristics |                                                 |    |      |       |  |  |  |  |

|------------------------------------------------|-------------------------------------------------|----|------|-------|--|--|--|--|

| Symbol                                         | Symbol Parameter                                |    | Max. | Units |  |  |  |  |

| t <sub>LEPW</sub>                              | LE minimum pulse width                          | 10 |      | ns    |  |  |  |  |

| t <sub>PDSUP</sub>                             | Data set-up time before clock rising edge of LE | 10 |      | ns    |  |  |  |  |

| t <sub>PDHLD</sub>                             | Data hold time after clock falling edge of LE   | 10 |      | ns    |  |  |  |  |

Mini-Circuits

For detailed performance specs & shopping online see web site

# **Digital Step Attenuator**

Pin 20 must always be low to prevent the attenuator from entering an unknown state.

# **Power-up Control Settings**

The DAT-3175-PN always assumes a specifiable attenuation setting on power-up, allowing a known attenuation state to be established before an initial parallel control word is provided.

When the attenuator powers up with LE=0, the control bits are automatically set to one of four possible values. These four values are selected by the two power-up control bits, PUP1 and PUP2, as shown in Table 3: (Power-Up Truth Table, Parallel Mode)

| Table 3. Power-Up Truth Table, Parallel Mode |                     |                                                                                                           |  |  |  |  |  |

|----------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PUP1 PUP2                                    |                     | LE                                                                                                        |  |  |  |  |  |

| 0                                            | 0                   | 0                                                                                                         |  |  |  |  |  |

| 0                                            | 1                   | 0                                                                                                         |  |  |  |  |  |

| 1                                            | 0                   | 0                                                                                                         |  |  |  |  |  |

| 1                                            | 1                   | 0                                                                                                         |  |  |  |  |  |

| X (Note 1)                                   | X (Note 1)          | 1                                                                                                         |  |  |  |  |  |

|                                              | PUP1<br>0<br>0<br>1 | PUP1         PUP2           0         0           0         1           1         0           1         1 |  |  |  |  |  |

Note: PUP1 and PUP2 Connection may be 0, 1, GROUND, or not connect, without effect on attenuation state.

Power-Up with LE=1 provides normal parallel operation with C1-C16, and PUP1 and PUP2 are not active.

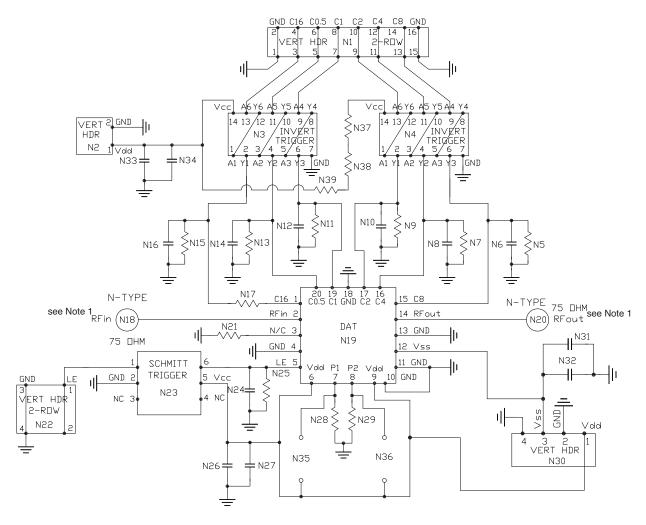

#### **TB-341 Evaluation Board Schematic Diagram**

Note 1: Both RF ports must be held at 0VDC or DC blocked with an external series capacitor.

| Bill of Materials                                  |                                        |  |  |  |  |

|----------------------------------------------------|----------------------------------------|--|--|--|--|

| N5, N7, N9, N11, N13,<br>N15, N21 & N25            | Resistor 0603 10 KOhm +/- 1%           |  |  |  |  |

| N28 & N29                                          | Resistor 0603 475 Ohm +/- 1%           |  |  |  |  |

| N37-N39                                            | Resistor 0603 0 Ohm                    |  |  |  |  |

| N17                                                | Resistor 0402 10 KOhm +/- 1%           |  |  |  |  |

| N6, N8, N10, N12, N14,<br>N16, N24, N26, N31 & N33 | NPO Capacitor 0603 100pF +/- 5%        |  |  |  |  |

| N27, N32 & N34                                     | Tantalum Capacitor 0805 100nF +/- 10%  |  |  |  |  |

| N3 & N4                                            | Hex Invert Schmitt Trigger MSL1        |  |  |  |  |

| N23                                                | Dual Schmitt Trigger Buffer SC-70 MSL1 |  |  |  |  |

**TB-341**

Mini-Circuits

For detailed performance specs & shopping online see web site

ISO 9001 ISO 14001 AS 9100 CERTIFIED

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 The Design Engineers Search Engine

Provides ACTUAL Data Instantly at minicipcuits.com IF/RF MICROWAVE COMPONENTS

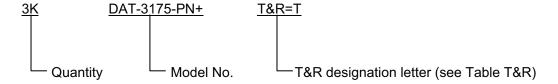

# **Tape and Reel Packaging Information**

### Table T&R

| TR<br>No. | No. of Devices                                   | Designation<br>Letter | Reel Size         | Tape<br>Width | Pitch | Unit<br>Orientation |

|-----------|--------------------------------------------------|-----------------------|-------------------|---------------|-------|---------------------|

|           | 3000                                             | Т                     | 13 inch           | 12 mm   8 mi  |       | Tape                |

| F87       | multiples of 10,<br>less than full<br>reel of 3K | PR                    | 13 inch           |               | 8 mm  | Direction of Feed - |

|           | multiples of 10,<br>on tape only                 | E                     | not<br>applicable |               |       |                     |

**Ordering Information**

| Model No.       | Description                                                    | Packaging<br>Designation Letter<br>(See Table T&R) | Quantity<br>Min.<br>No. of Units | Price<br>\$<br>Ea. |

|-----------------|----------------------------------------------------------------|----------------------------------------------------|----------------------------------|--------------------|

| DAT-3175-PN (+) | Parallel Interface,<br>Dual Voltage (Negative<br>and Positive) | E                                                  | 10                               | \$3.55             |

| TB-341          | Test Board Only                                                | Not Applicable                                     | 1                                | \$79.95            |

## **How to Order**

Example: 3000 pieces of DAT-3175-PN+

For detailed performance specs