**Programmable Array Logic Family** PAL® Series 20 AP With Programmable Output Polarity

#

#### Features/Benefits

- 25 ns maximum propagation delay

- · Programmable output polarity

- Programmable replacement for TTL logic

- Expedites prototyping and board layout

- · Programmed on standard PAL programmers

- Last fuse prevents duplication

#### **Functional Description**

The PAL series 20 AP represents an enhancement of existing PAL architectures which provides greater design flexibility and higher speed. The PAL series 20 AP comes with programmable output polarity and is pin-for-pin compatible with the standard PAL 20 series.

The programmable output polarity feature allows the user to program individual outputs either active high or active low. This feature eliminates any possible need for inversion of signals outside the device.

### **General Description**

The PAL series utilizes Monolithic Memories' advanced selfaligned washed-emitter high-speed bipolar process and the bipolar fusible-link technology to provide user-programmable logic for replacing conventional SSI/MSI gates and flip-flops at reduced chip count.

The family lets the system engineer "design his own chip" by blowing fusible links to configure AND and OR gates to perform the desired logic function. Complex interconnections which previously required time-consuming layout are thus "lifted" from the PC board and are placed on silicon where they can be easily modified during prototype check-out or production.

#### **Product Description**

| PART<br>NUMBER | PKG         | GATE ARRAY<br>DESCRIPTION |

|----------------|-------------|---------------------------|

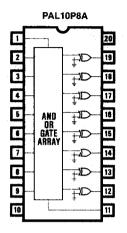

| PAL10P8A       | J, N, L, NL | Octal 10-input And-Or     |

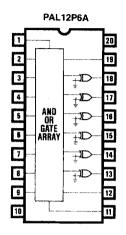

| PAL12P6A       | J, N, L, NL | Hex 12-input And-Or       |

| PAL14P4A       | J, N, L, NL | Quad 14-input And-Or      |

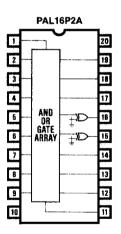

| PAL16P2A       | J, N, L, NL | Dual 16-input And-Or      |

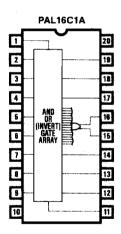

| PAL16C1A       | J. N, L, NL | 16-input And-Or           |

The PAL transfer function is the familiar sum of products. The PAL has a single array of fusible links which is a programmable AND array driving a fixed OR array.

Unused inputs are tied directly to VCC or GND. Product terms with all fuses blown assume the logical high state, and product terms connected to both true and complement of any single input assume the logical low state.

The entire PAL family is programmed on inexpensive conventional PAL programmers with appropriate personality and socket adapter modules. Once the PAL is programmed and verified two additional fuses may be blown to defeat verification. This feature gives the user a proprietary circuit which is very difficult to copy.

## **Preliminary Data**

- T<sub>PD</sub> (max) = 25 ns propagation delay

- I<sub>CC</sub> (max) = 90 mA