### **Maximum Ratings**

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it.

The MCU contains circuitry to protect the inputs against damage from high static voltages; however, do not apply voltages higher than those shown in **Table 1**. Keep  $V_{IN}$  and  $V_{OUT}$  within the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Connect unused inputs to the appropriate voltage level, either  $V_{SS}$  or  $V_{DD}$ .

**Table 1. Maximum Ratings**

| Rating                                                                    | Symbol           | Value                                   | Unit |

|---------------------------------------------------------------------------|------------------|-----------------------------------------|------|

| Supply Voltage                                                            | V <sub>DD</sub>  | -0.3 to +7.0                            | V    |

| Current Drain per Pin<br>(Excluding V <sub>DD</sub> and V <sub>SS</sub> ) | 1                | 25                                      | mA   |

| Input Voltage                                                             | V <sub>IN</sub>  | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$ | V    |

| EPROM Programming Voltage                                                 | V <sub>PP</sub>  | 16.75                                   | V    |

| Storage Temperature Range                                                 | T <sub>STG</sub> | -65 to +150                             | °C   |

#### **NOTE:**

This device is not guaranteed to operate properly at the maximum ratings. Refer to 5.0 V DC Electrical Characteristics on page 135 and 3.3 V DC Electrical Characteristics on page 136 for guaranteed operating conditions.

#### **Operating Temperature Range**

**Table 2. Operating Temperature Range**

| Package Type                                                                                                                                                                                                                                     | Symbol         | Value                                                                       | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|------|

| MC68HC705P9P <sup>(1)</sup> , DW <sup>(2)</sup> , S <sup>(3)</sup> (Standard)<br>MC68HC705P9C <sup>(4)</sup> P, CDW, CS (Extended)<br>MC68HC705P9V <sup>(5)</sup> P, VDW, VS (Automotive)<br>MC68HC705P9M <sup>(6)</sup> P, MDW, MS (Automotive) | T <sub>A</sub> | T <sub>L</sub> to T <sub>H</sub> 0 to 70 -40 to +85 -40 to +105 -40 to +125 | °C   |

- 1. P = Plastic dual in-line package (PDIP)

- 2. DW = Small outline integrated circuit (SOIC)

- 3. S = Ceramic dual in-line package (Cerdip)

- 4. C = Extended temperature range (-40 to +85 °C)

- 5. V = Automotive temperature range (-40 to +105 °C)

- 6. M = Automotive temperature range (-40 to +125 °C)

#### **Thermal Characteristics**

**Table 3. Thermal Characteristics**

| Characteristic                                                                                                                       | Symbol          | Value          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------|

| Thermal Resistance Plastic Dual In-Line Package (PDIP) Small Outline Integrated Circuit (SOIC) Ceramic Dual In-Line Package (Cerdip) | θ <sub>JA</sub> | 60<br>60<br>60 | °C/W |

#### **Power Considerations**

The average chip junction temperature, T<sub>J</sub>, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA}) \tag{1}$$

where:

T<sub>A</sub> = ambient temperature in °C

θ<sub>IA</sub> = package thermal resistance, junction to ambient in °C/W

$P_D = P_{INT} + P_{I/O}$

$P_{INT} = I_{CC} \times V_{CC} = chip internal power dissipation$

$P_{VO}$  = power dissipation on input and output pins (user-determined)

For most applications,  $P_{I/O} \ll P_{INT}$  and can be neglected.

Ignoring  $P_{I/O}$ , the relationship between  $P_D$  and  $T_J$  is approximately:

$$P_D = \frac{K}{T_\perp + 273 \,^{\circ}C} \tag{2}$$

Solving equations (1) and (2) for K gives:

$$K = P_D \times (T_A + 273 \,{}^{\circ}C) + \theta_{JA} \times (P_D)^2$$

(3)

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $P_D$  can be obtained by solving equations (1) and (2) iteratively for any value of  $P_A$ .

### 5.0 V DC Electrical Characteristics

Table 4. DC Electrical Characteristics  $(V_{DD} = 5.0 \text{ Vdc})^{(1)}$

|                                                                                                                                                      |                   |                         | - /61                       | _                                    |                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|-----------------------------|--------------------------------------|----------------------------------|

| Characteristic                                                                                                                                       | Symbol            | Min                     | Typ <sup>(2)</sup>          | Max                                  | Unit                             |

| Output Voltage $I_{LOAD} = 10.0 \mu A$ $I_{LOAD} = -10.0 \mu A$                                                                                      | V <sub>OL</sub>   | <br>V <sub>DO</sub> 0.1 | _                           | 0.1<br>                              | V                                |

| Output High Voltage (I <sub>LOAD</sub> = -0.8 mA) PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5, TCMP                                      | V <sub>OH</sub>   | V <sub>DD</sub> - 0.8   | _                           |                                      | ٧                                |

| Output Low Voltage (I <sub>LOAD</sub> = 1.6 mA) PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5, TCMP                                        | V <sub>OL</sub>   |                         | _                           | 0.4                                  | <b>v</b>                         |

| Input High Voltage PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5, PD7/TCAP, IRQ/V <sub>PP</sub> , RESET, OSC1                              | V <sub>IH</sub>   | 0.7 × V <sub>DD</sub>   |                             | V <sub>DD</sub>                      | <b>v</b>                         |

| Input Low Voltage PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5, PD7/TCAP, IRQ/V <sub>PP</sub> , RESET, OSC1                               | V <sub>IL</sub>   | V <sub>ss</sub>         |                             | 0.2 × V <sub>DD</sub>                | V                                |

| Supply Current <sup>(3)</sup> (4) (5) (6)  Run Mode  Wait Mode (ADC On)  Wait Mode (ADC Off)  Stop Mode  25 °C  0 to 70 °C (Standard)  -40 to 125 °C | I <sub>DD</sub>   | _<br>_<br>_<br>_        | 4.7<br>2.1<br>1.3<br>2<br>— | 6.5<br>2.9<br>1.9<br>30<br>50<br>100 | mA<br>mA<br>mA<br>μA<br>μA<br>μA |

| I/O Ports Hi-Z Leakage Current PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5                                                               | I <sub>IL</sub>   | _                       |                             | ±10                                  | μΑ                               |

| ADC Ports Hi-Z Leakage Current                                                                                                                       | l <sub>oz</sub> _ | <u> </u>                |                             | ±1                                   | μA                               |

| Input Current RESET, IRQ/V <sub>PP</sub> , OSC1, PD7/TCAP                                                                                            | I <sub>IN</sub>   |                         |                             | ±1                                   | μА                               |

| Capacitance Ports (As Inputs or Outputs) RESET, IRQ/V <sub>PP</sub>                                                                                  | C <sub>OUT</sub>  | <u> </u>                | _                           | 12<br>8                              | pF                               |

| Programming Voltage                                                                                                                                  | V <sub>PP</sub>   | 16.25                   | 16.5                        | 16.75                                | V V                              |

| Programming Current                                                                                                                                  | 1 <sub>PP</sub>   |                         | 5                           | 10                                   | mA                               |

| Programming Time per Byte                                                                                                                            | t <sub>EPGM</sub> | 4                       |                             |                                      | ms                               |

<sup>1.</sup>  $V_{DD}$  = 5.0 Vdc ±10%,  $V_{SS}$  = 0 Vdc,  $T_{A}$  =  $T_{L}$  to  $T_{H}$  unless otherwise noted

<sup>2.</sup> Typical values at midpoint of voltage range, 25 °C only

<sup>3.</sup> Run mode and wait mode  $I_{DD}$  measured using external square wave clock source ( $f_{OSC} = 4.2$  MHz); all inputs 0.2 V from rail; no dc loads; less than 50 pF on all outputs;  $C_L = 20$  pF on OSC2

<sup>4.</sup> Wait mode and stop mode  $I_{DD}$  measured with all ports configured as inputs;  $V_{IL}$  = 0.2 V;  $V_{IH}$  =  $V_{DD}$  – 0.2 V

<sup>5.</sup> Stop mode  $I_{DD}$  measured with OSC1 =  $V_{SS}$

<sup>6.</sup> Wait mode I<sub>DD</sub> affected linearly by OSC2 capacitance

#### 3.3 V DC Electrical Characteristics

Table 5. DC Electrical Characteristics  $(V_{DD} = 3.3 \text{ Vdc})^{(1)}$

| Characteristic                                                                                                                                | Symbol                              | Min                     | Typ <sup>(2)</sup>       | Max                                 | Unit                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------|--------------------------|-------------------------------------|----------------------------|

| Output Voltage (I <sub>LOAD</sub> ≤ 10.0 μA)                                                                                                  | V <sub>OL</sub><br>V <sub>OH</sub>  | <br>V <sub>DD</sub> 0.1 | _                        | 0.1                                 | <b>v</b>                   |

| Output High Voltage (I <sub>LOAD</sub> = -0.2 mA) PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5, TCMP                               | V <sub>OH</sub>                     | V <sub>DD</sub> - 0.3   | _                        | _                                   | ٧                          |

| Output Low Voltage (I <sub>LOAD</sub> = 0.4 mA)<br>PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5,<br>TCMP                           | V <sub>OL</sub>                     | 1                       | 1                        | 0.3                                 | <b>&gt;</b>                |

| Input High Voltage PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5, PD7/TCAP, IRQ/V <sub>PP</sub> , RESET, OSC1                       | V <sub>IH</sub>                     | 0.7 × V <sub>DD</sub>   | _                        | V <sub>DD</sub>                     | >                          |

| Input Low Voltage PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5, PD7/TCAP, IRQ/V <sub>PP</sub> , RESET, OSC1                        | V <sub>IL</sub>                     | V <sub>ss</sub>         | _                        | 0.2 × V <sub>DD</sub>               | v                          |

| Data-Retention Mode Supply Voltage                                                                                                            | V <sub>RM</sub>                     | 2.0                     | _                        |                                     | V                          |

| Supply Current <sup>(3)</sup> (4) (5) (6) Run Mode Wait Mode (ADC On) Wait Mode (ADC Off) Stop Mode 25 °C 0 to 70 °C (Standard) -40 to 125 °C | I <sub>DD</sub>                     |                         | 1.6<br>0.9<br>0.4<br>1.0 | 2.3<br>1.3<br>0.6<br>20<br>40<br>50 | mA<br>mA<br>mA<br>μA<br>μA |

| I/O Ports Hi-Z Leakage Current<br>PA7-PA0, PB7/SCK-PB5/SDO, PC7/V <sub>RH</sub> -PC0, PD5                                                     | I <sub>IL</sub>                     |                         | _                        | ±10                                 | μА                         |

| Input Current<br>RESET, IRQ/V <sub>PP</sub> , OSC1, PD7/TCAP                                                                                  | I <sub>IN</sub>                     | _                       |                          | ±1                                  | μА                         |

| Capacitance Ports (As Inputs or Outputs) RESET, IRQ/V <sub>PP</sub>                                                                           | C <sub>OUT</sub><br>C <sub>IN</sub> | _                       | _                        | 12<br>8                             | pF                         |

<sup>1.</sup>  $V_{OD}$  = 3.3 Vdc ±10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$  unless otherwise noted

<sup>2.</sup> Typical values at midpoint of voltage range, 25 °C only

<sup>3.</sup> Run mode and wait mode  $I_{DD}$  measured using external square wave clock source ( $f_{OSC} = 2.1$  MHz); all inputs 0.2 V from rail; no dc loads; less than 50 pF on all outputs;  $C_L = 20$  pF on OSC2

<sup>4.</sup> Wait mode and stop mode  $I_{DD}$  measured with all ports configured as inputs;  $V_{IL}$  = 0.2 V;  $V_{IH}$  =  $V_{DD}$  – 0.2 V

<sup>5.</sup> Stop mode  $I_{DD}$  measured with OSC1 =  $V_{SS}$

<sup>6.</sup> Wait mode I<sub>DD</sub> affected linearly by OSC2 capacitance

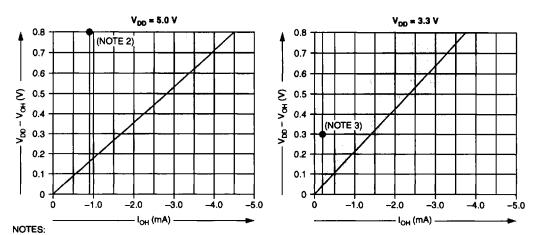

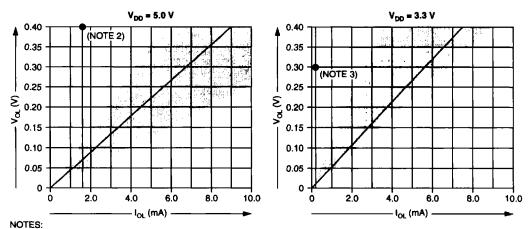

#### **Driver Characteristics**

- Shaded area indicates variation in driver characteristics due to changes in temperature and for normal processing tolerances.

Within the limited range of values shown, V vs I curves are approximately straight lines.

- 2. At  $V_{DD}$  = 5.0 V, devices are specified and tested for  $V_{OL} \le 800$  mV @  $I_{OL} \approx -0.8$  mA.

- 3. At  $V_{DO}$  = 3.3 V, devices are specified and tested for  $V_{OL} \le 300$  mV @  $I_{OL} \approx -0.2$  mA.

Figure 1. Typical High-Side Driver Characteristics

- Shaded area indicates variation in driver characteristics due to changes in temperature and for normal processing tolerances.

Within the limited range of values shown, V vs I curves are approximately straight lines.

- 2. At  $V_{DD}$  = 5.0 V, devices are specified and tested for  $V_{OL} \le 400$  mV @  $I_{OL}$  = 1.6 mA.

- 3. At  $V_{DD}$  = 3.3 V, devices are specified and tested for  $V_{OL} \le 300$  mV @  $I_{OL}$  = 0.4 mA.

Figure 2. Typical Low-Side Driver Characteristics

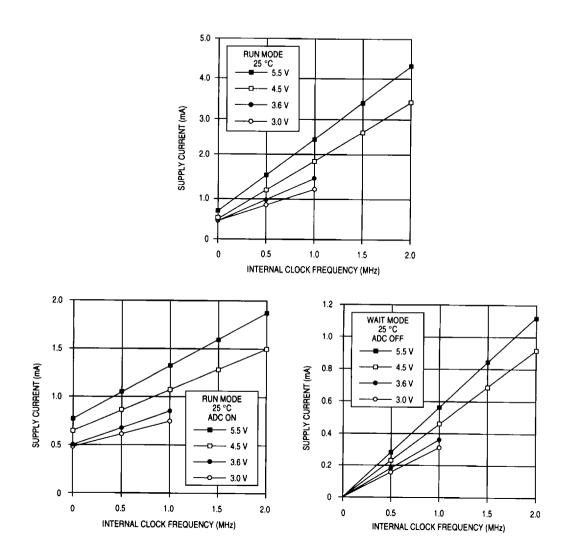

# Typical Supply Current vs. Internal Clock Frequency

Figure 3. Typical Supply Current vs. Internal Clock Frequency

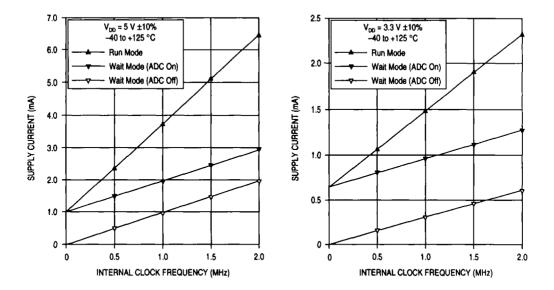

## Maximum Supply Current vs. Internal Clock Frequency

Figure 4. Maximum Supply Current vs. Internal Clock Frequency

#### 5.0 V Control Timing

Table 6. Control Timing  $(V_{DD} = 5.0 \text{ Vdc})^{(1)}$

| Characteristic                                                                       | Symbol                                                              | Min                               | Max        | Unit                                 |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------|------------|--------------------------------------|

| Oscillator Fréquency<br>Crystal<br>External Clock                                    | fosc                                                                | —<br>dc                           | 4.2<br>4.2 | MHz                                  |

| Internal Operating Frequency (f <sub>osc</sub> + 2)<br>Crystal<br>External Clock     | f <sub>OP</sub>                                                     | dc                                | 2.1<br>2.1 | MHz                                  |

| Cycle Time (1 + f <sub>OP</sub> )                                                    | t <sub>cyc</sub>                                                    | 480                               |            | ns                                   |

| Crystal Oscillator Startup Time                                                      | t <sub>oxov</sub>                                                   | _                                 | 100        | ms                                   |

| Stop Recovery Startup Time (Crystal Oscillator)                                      | t <sub>ILCH</sub>                                                   |                                   | 100        | ms                                   |

| RESET Pulse Width                                                                    | t <sub>AL</sub>                                                     | 1.5                               | _          | t <sub>cyc</sub>                     |

| Timer Resolution <sup>(2)</sup> Input Capture Pulse Width Input Capture Pulse Period | t <sub>RESL</sub> t <sub>H</sub> , t <sub>L</sub> t <sub>TLTL</sub> | 4.0<br>125<br>Note <sup>(3)</sup> | 111        | t <sub>CYC</sub> ns t <sub>CYC</sub> |

| Interrupt Pulse Width Low (Edge-Triggered)                                           | t <sub>ILIH</sub>                                                   | 125                               | _          | ns                                   |

| Interrupt Pulse Period                                                               | t <sub>ILIL</sub>                                                   | Note <sup>(4)</sup>               | 1          | tcyc                                 |

| OSC1 Pulse Width                                                                     | ton, tol                                                            | 90                                | _          | ns                                   |

| RC Oscillator Stabilization Time                                                     | t <sub>RCON</sub>                                                   | _                                 | 5          | μs                                   |

| ADC On Current Stabilization Time                                                    | <b>L</b> ADON                                                       | _                                 | 100        | μs                                   |

<sup>1.</sup>  $V_{00}$  = 5.0 Vdc ±10%,  $V_{ss}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$  unless otherwise noted

<sup>2.</sup> A 2-bit prescaler in the timer is the limiting factor as it counts 4  $t_{\rm CYC}$

<sup>3.</sup> The minimum  $t_{\rm fLTL}$  should not be less than the number of interrupt service routine cycles plus 19  $t_{\rm CYC}$

<sup>4.</sup> The minimum  $t_{\text{RLL}}$  should not be less than the number of interrupt service routine cycles plus 19  $t_{\text{CYC}}$

#### 3.3 V Control Timing

Table 7. Control Timing  $(V_{DD} = 3.3 \text{ Vdc})^{(1)}$

| Characteristic                                                                       | Symbol                                                              | Min                               | Max        | Unit                                       |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------|------------|--------------------------------------------|

| Oscillator Frequency<br>Crystal<br>External Clock                                    | f <sub>osc</sub>                                                    | —<br>dc                           | 2.0<br>2.0 | MHz                                        |

| Internal Operating Frequency (f <sub>OSC</sub> + 2)<br>Crystal<br>External Clock     | f <sub>OP</sub>                                                     | <br>dc                            | 1.0<br>1.0 | MHz                                        |

| Cycle Time (1 + f <sub>OP</sub> )                                                    | t <sub>cyc</sub>                                                    | 1                                 | _          | ms                                         |

| Crystal Oscillator Startup Time                                                      | t <sub>oxov</sub>                                                   | _                                 | 100        | ms                                         |

| Stop Recovery Startup Time (Crystal Oscillator)                                      | t <sub>ILCH</sub>                                                   |                                   | 100        | ms                                         |

| RESET Pulse Width                                                                    | t <sub>RL</sub>                                                     | 1.5                               |            | t <sub>cyc</sub>                           |

| Timer Resolution <sup>(2)</sup> Input Capture Pulse Width Input Capture Pulse Period | t <sub>RESL</sub> t <sub>H</sub> , t <sub>L</sub> t <sub>TLTL</sub> | 4.0<br>250<br>Note <sup>(3)</sup> |            | t <sub>cyc</sub><br>ns<br>t <sub>cyc</sub> |

| Interrupt Pulse Width Low (Edge-Triggered)                                           | t <sub>ILIH</sub>                                                   | 250                               | _          | ns                                         |

| Interrupt Pulse Period                                                               | t <sub>ILIL</sub>                                                   | Note <sup>(4)</sup>               | _          | t <sub>CYC</sub>                           |

| OSC1 Pulse Width                                                                     | t <sub>OH</sub> , t <sub>OL</sub>                                   | 200                               | _          | ns                                         |

<sup>1.</sup>  $V_{DD}$  = 3.3 Vdc ±10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$  unless otherwise noted

<sup>2.</sup> A 2-bit prescaler in the timer is the limiting factor as it counts 4  $t_{\mbox{\scriptsize CYC}}$

The minimum t<sub>TLTL</sub> should not be less than the number of interrupt service routine cycles plus 19 t<sub>cyc</sub>

<sup>4.</sup> The minimum  $t_{\text{tLIL}}$  should not be less than the number of interrupt service routine cycles plus 19  $t_{\text{CYC}}$

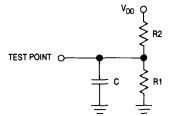

#### **Test Load**

| PINS                     | R1      | R2      | С     |

|--------------------------|---------|---------|-------|

| PA7-PA0                  |         |         |       |

| P87/SCK-P85/SDO          | 3.26 kΩ | 2.38 kΩ | 50 pF |

| PC7/V <sub>RH</sub> -PC0 |         |         |       |

Figure 5. Test Load

#### **Mechanical Specifications**

The MC68HC705P9 is available in the following packages:

- 710 Plastic dual in-line package (PDIP)

- 733 Ceramic dual in-line package (Cerdip)

- 751F Small outline integrated circuit (SOIC)

The following figures show the latest packages at the time of this publication. To make sure that you have the latest package specifications, contact one of the following:

- Local Motorola Sales Office

- Motorola Mfax

- Phone 602-244-6609

- EMAIL rmfax0@email.sps.mot.com

- Worldwide Web (wwweb) at http://design-net.com

Follow Mfax or wwweb on-line instructions to retrieve the current mechanical specifications.

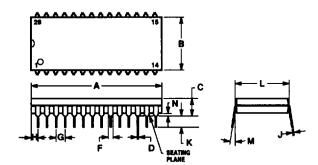

#### 28-Pin PDIP — Case #710

- NOTES:

1. POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25mm (0.010) AT MAXIMUM MATERIAL COMDITION, IN RELATION TO SEATING PLANE AND EACH OTHER OF LEADS WHEN FORMED PARALLEL

3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | MILLIMETERS |       | INC       | HES   |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| A   | 36.45       | 37.21 | 1.435     | 1.465 |

| 8   | 13.72       | 14.22 | 0.540     | 0.580 |

| С   | 3.94        | 5.08  | 0.155     | 0.200 |

| D   | 0.36        | 0.56  | 0.014     | 0.022 |

| F   | 1.02        | 1.52  | 0.040     | 0.080 |

| Ğ   | 2.54        | BSC   | 0.100 BSC |       |

| Н   | 1.65        | 2.16  | 0.065     | 0.085 |

| J   | 0.20        | 0.38  | 0.008     | 0.015 |

| K   | 2.92        | 3.43  | 0.115     | 0.135 |

| L   | 15.24 BSC   |       | 0.800     | BSC   |

| #   | O.          | 15°   | 0,        | 15°   |

| -   | 0.51        | 102   | ስ ሰንስ     | 0.040 |

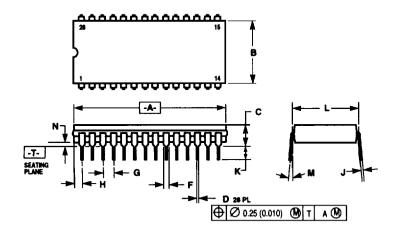

28-Pin Cerdlp --Case #733

#### NOTES:

- OTES:

1. DIMENSIONS A AND B INCLUDES MENISCUS.

2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

3. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

4. CONTROLLING DIMENSION: INCH.

| DIM | MIN       | MAX   | WIN   | MAX   |

|-----|-----------|-------|-------|-------|

| A   | 1,435     | 1.490 | 36.45 | 37.84 |

| 8   | 0.500     | 0.605 | 12.70 | 15.36 |

| С   | 0.160     | 0.230 | 4.08  | 5.84  |

|     | 0.015     | 0.022 | 0.38  | 0.55  |

| F   | 0.050     | 0.065 | 1.27  | 1.65  |

| a   | 0.100 BSC |       | 2.54  | RSC   |

| A  | 1,435 | 1.490 | 36.45    | 37.84 |

|----|-------|-------|----------|-------|

| 8  | 0.500 | 0.605 | 12.70    | 15.36 |

| U  | 0.160 | 0.230 | 4.08     | 5.84  |

| 0  | 0.015 | 0.022 | 0.38     | 0.55  |

| F  | 0.050 | 0.085 | 1.27     | 1.65  |

| G. | 0.100 | BSC   | 2.54 BSC |       |

| J  | 0.008 | 0.012 | 0.20     | 0.30  |

| K  | 0.125 | 0.180 | 3.18     | 4.06  |

| L  | 0.600 | BSC   | 15.24    | BSC   |

| M  | 0°_   | 15°_  | _0°_     | 15°   |

| N  | 0.020 | 0.050 | 0.51     | 1.27  |

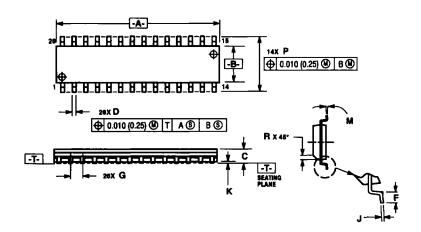

#### 28-Pin SOIC ---Case #751F

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND 8 DO NOT INCLUDE MOLD PROTRISION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.009 PER SIDE.

5. DIMENSION DOCES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.009) TOTAL IN EXCESS OF DIMENSION AT MAXIMUM MATERIAL CONDITION.

|      |       | E I ENS | INC       | ues   |

|------|-------|---------|-----------|-------|

| Diff | MIN   | MAX     |           | MAX   |

| Ā    | 17.80 | 18.05   | 0.701     | 0.711 |

| ı    | 7.40  | 7.80    | 0.292     | 0.299 |

| C    | 2.35  | 2.65    | 0.093     | 0.104 |

| 0    | 0.35  | 0.49    | 0.014     | 0.019 |

| F    | 0.41  | 0.90    | 0.016     | 0.035 |

| Ğ    | 1.27  | BSC     | 0.050 BSC |       |

| 1    | 0.23  | 0.32    | 0.009     | 0.013 |

| K    | 0.13  | 0.29    | 0.005     | 0.011 |

| . *  | ů     | 8.      | O°        | 8     |

| P    | 10.05 | 10.55   | 0.395     | 0.415 |

| R    | 0.25  | 0.75    | 0.010     | 0.029 |