# THIRD GENERATION 64-BIT SUPER-PIPELINED RISC MICROPROCESSOR

IDT79R4000, IDT79R4400 PRELIMINARY

# **FEATURES:**

- True 64-bit microprocessor

- 64-bit integer operations

- 64-bit floating-point operations

- 64-bit registers

- 64-bit virtual address space

- · High-performance microprocessor

- Super-pipelined architecture supports 150MIPS at 75MHz

- No issue restrictions for dual instruction issue

- Over 80 VUPs performance at 75MHz clock frequency

- · High level of integration

- 64-bit integer CPU

- 64-bit floating-point accelerator

- 8KB instruction cache; 8KB data cache (R4000)

- 16KB instruction; 16KB data cache (R4400)

- Flexible MMU with large TLB

- · Standard operating system support includes:

- Microsoft Windows NT

- UNISOFT UNIX System V.4

- Fully software compatible with R3000A 32-bit RISC Processor Family

- 50, 67 and 75MHz clock frequencies

- · 64GB physical address space

- · Processor family for a wide variety of applications

- Desktop workstations

- Deskside or departmental servers

- High-performance embedded applications

- Tightly coupled multi-processing systems

- Fault tolerant systems

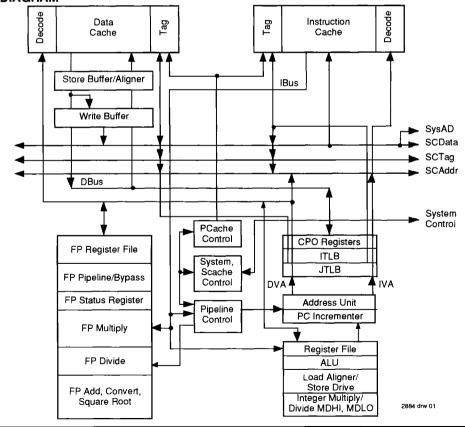

# **BLOCK DIAGRAM**

**COMMERCIAL TEMPERATURE RANGE**

OCTOBER 1992

# **DESCRIPTION:**

The IDT79R4000 family supports a wide variety of processor based applications, from 32-bit ARC compliant desktop systems through high-performance, 64-bit OLTP systems manipulating large data bases in a multi-processor based system. The IDT79R4000/R4400 family offers a broad range of price-performance options for high-performance systems, allowing the system architect unprecedented degrees of freedom in making price-performance tradeoffs.

The IDT R4000 family provides complete upward application-software compatibility with the IDT79R3000 family of microprocessors, including the IDT79R3000A and the IDT RISController™ family (the IDT79R3001 and IDT79R3051 family). Microsoft Windows NT and UNISOFT UNIX V.4 operating systems insure the availability of thousands of applications programs, geared to provide a complete solution to a large number of processing needs. An array of development tools facilitates the rapid development of R4000-based systems, enabling a wide variety of customers to take advantage of the MIPS Open Architecture philosophy.

The R4000 family achieves a unique balance between high-integer and high-floating-point performance. The key to this balance is the super-pipelined architecture of the processor, which brings performance gains to both integer and floating-point intensive programs without requiring re-compilation to take advantage of the architectural advancement. The super-pipeline architecture is well-balanced in the R4000 family; the high-performance execution engine is assured of a rapid and continual supply of instructions and data through the use of large on-chip caches, and a high-performance on-chip TLB. The result is consistently high-performance: over 80 VUPS at 75MHz over a wide variety of realistic applications programs.

The R4000 family also provides a compatible, timely, and necessary evolution path from 32-bit to true, 64-bit computing. The original design objectives of the R4000 clearly mandated this evolution path; the result is a true 64-bit processor fully compatible with 32-bit operating systems and applications.

The 64-bit computing and addressing capability of the R4000 enables a wide variety of capabilities previously limited by a smaller address space. For example, the large address space allows operating systems with extensive file mapping; direct access to large files can occur without explicit I/O calls. Applications such as large CAD databases, multi-media, and high-quality image storage and retrieval all directly benefit from the enlarged address space.

This data sheet provides an overview of the features and architecture of the IDT79R4000 CPU family. A more detailed description of the processor is available in the "R4000 User's Manual", available from IDT. Further information on develop-

ment support, applications notes, and complementary products are also available from your local IDT sales representative.

This data sheet describes both the R4000 and the R4400. The primary difference between the two devices is the amount of on-chip primary cache: the R4000 contains 8kB each of primary instruction and data cache, while the R4400 doubles this to 16kB each of cache. Throughout this data sheet, the term "R4000" will be used to describe characteristics common to both the R4000 and the R4400 devices.

# **IDT79R4000 FAMILY MEMBERS**

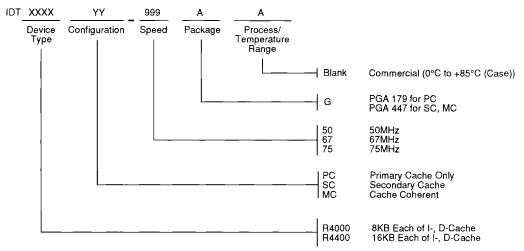

The IDT79R4000 processor is available in three different configurations: the IDT79R4000MC and IDT79R4000SC, which include a 128-bit wide secondary cache bus; and the IDT79R4000PC, with no secondary cache interface. Additionally, the R4000PC and R4000SC are available with two different on-chip cache configurations: the R4000, with 8KB each of instruction and data cache; and the R4400, which doubles on-chip cache to 16KB each of instruction and cache.

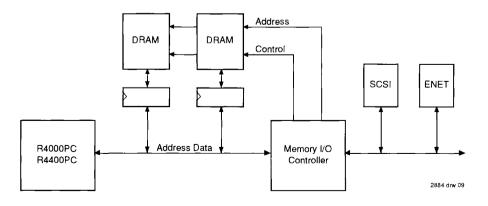

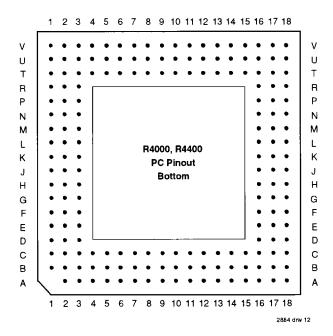

# PC CONFIGURATION

The IDT79R4000PC and 79R4400PC are available in a 179-pin Pin Grid Array (PGA). This configuration does not support secondary cache or cache coherency, and is ideal for applications such as high-performance embedded control and low-cost desktop systems, where the on-chip caches provide enough performance and where cost, power, and board space must be kept to a minimum. By eliminating a secondary cache, a system can be designed with fewer parts and lower power consumption.

# SC CONFIGURATION

The IDT79R4000SC and 79R4400SC are available in a 447-pin Pin Grid Array (PGA). This processor supports a secondary cache interface and is ideal in systems where high performance is desired. This component supports a 128kB to 4mB secondary cache made from standard SRAMs. This flexibility allows system designers to make price/performance tradeoffs in cache subsystem designs.

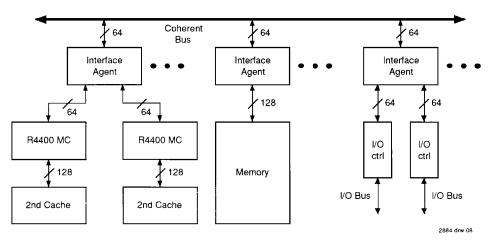

# MC CONFIGURATION

The IDT79R4400MC is also available in the 447-pin Pin Grid Array (PGA). This processor supports a secondary cache and configurable multiprocessor cache coherency protocols. Like the "SC" configuration, this processor also supports a 128kB to 4mB secondary cache made from standard SRAMs. The IDT79R4400MC is well suited for a range of designs from high performance desktop systems to fault tolerant multiprocessor servers.

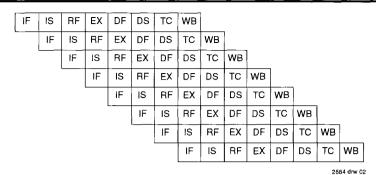

Figure 1. R4000 Family 8-Stage Super-Pipeline

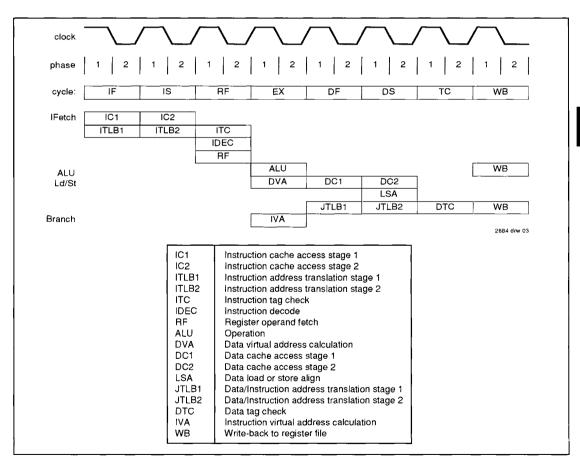

Figure 2. Pipeline Activities

5.7

# HARDWARE OVERVIEW

The IDT R4000 family brings a high-level of integration designed for high-performance computing. The key elements of the IDT R4000 are briefly described below. A more detailed description of each of these subsystems is available in other literature.

# Superpipelined Implementation

In order to achieve the high-performance desired for today's applications and user's interfaces, the R4000 exploits instruction level parallelism using a super-pipelined microarchitecture.

The R4000 uses an 8-stage superpipeline which places no issue restrictions on instruction issue. Thus, any two instructions can be issued each master clock cycle under normal circumstances, leading to 150MIPS performance at 75MHz. One key advantage of this architecture is that all existing applications can gain from the architectural advancement represented by the R4000, without requiring re-compilation to re-order the software.

In order to support dual instruction issue, the internal pipeline of the R4000 operates at twice the external clock frequency. Instruction execution stages such as cache accesses are pipelined (thus the chip itself is super-pipelined) to eliminate bottlenecks associated with long-latency functional units. Other stages, such as the ALU stage, completely process one operation per pipeline clock cycle, allowing the results of one operation to be immediately used by the instruction which follows, with no pipeline interlocks.

High clock frequency results from careful construction of the various resources of the processor: pipelining cache accesses, shortening register access times, implementing virtually indexed primary caches, and allowing the latency of functional units to span multiple pipeline stages.

After extensive simulation of many methods of exploiting instruction level parallelism, superpipelining was chosen because it improves integer performance commensurate with floating-point performance. Thus, the R4000 provides performance benefits both to technical computing applications, and also to a wide variety of commercial applications as well. In

today's technology, super-pipelining results in less complex logic, faster cycle times, quicker design cycles, and lower cost. The pipeline of the IDT79R4000 is illustrated in Figure 1.

#### THE R4000 PIPELINE

The R4000 processor has an eight-stage execution pipeline. That is, each instruction takes eight Pclock (Pipeline clocks, at twice the frequency of the input clock) cycles to execute, but a new instruction is started on each Pclock cycle. Another way of viewing the process is that at any point in time, eight separate instructions are being executed at once. Figure 1 shows the R4000 pipeline in both views: a horizontal slice shows the execution process of individual instructions, and a vertical slice shows the processing of eight instructions at once.

Each box shown in the diagram corresponds to a part of the execution process.

Figure 2 illustrates the activities occuring within each pipestage as a function of the instruction type. First, in the IF stage, an instruction address is selected by the program counter logic and the first half of the both the instruction cache fetch (IC1) and the instruction virtual to physical address translation (ITLB1) is performed. The instruction address translation is done through a two entry subset of the main or *joint* translation lookaside buffer (JTLB) called the ITLB. In the IS stage, the second half of both the instruction cache fetch (IC2) and instruction translation (ITLB2) is done.

During the RF stage, three activities occur in parallel. The instruction decoder (IDEC) decodes the instruction and checks for interlock conditions. Meanwhile, the instruction tag check (ITC) is performed between the instruction cache tag and the page frame number (PFN) from the ITLB's translation. In parallel with both of the above, the operands are fetched from the register file (RF).

In the EX stage, if the instruction is a register-to-register operation, the arithmetic or logical operation is performed (ALU). If the instruction is a load/store, a data virtual address is calculated (DVA). If the instruction is a branch, a virtual branch target address is calculated (IVA).

For load/stores, the DF stage is used to do the first half of both the data cache fetch (DC1) and the data virtual to

0

# **General Purpose Registers**

| 63 |     | 0 |

|----|-----|---|

|    | 0   |   |

|    | r1  |   |

|    | r2  |   |

|    | •   |   |

|    | •   |   |

|    | •   |   |

|    | •   |   |

|    | r29 |   |

|    | r30 |   |

|    | r31 |   |

|    |     |   |

# Multiply/Divide Registers

н

Figure 3. CPU Registers

63

physical address translation (JTLB1). Similarly, the DS stage does the second half of both the data fetch (DC2) and the data translation (JTLB2) as well as the load align or store align (LSA), as appropriate. If the instruction is a branch, the JTLB is used during DF and DS to translate the branch address and refill the ITLB if necessary.

The TC stage is used to perform the tag check for load/ stores. During the WB stage the instruction result is written to the register file.

Smooth pipeline flow is interrupted when cache accesses miss, data dependencies are detected, or when exceptions occur. Interruptions that are handled by hardware, such as cache misses, are referred to as *interlocks*, while those that are handled using software are *exceptions*. Collectively, the cases of all interlock and exception conditions are referred to as *faults*.

Interlocks come in two varieties. Those interlocks which are resolved by simply stopping the pipeline are referred to as *stalls*, while those which require part of the pipeline to advance while holding up another part are *slips*.

At each cycle, exception and interlock conditions are checked for all active instructions. The conditions can be referred back to particular instructions, as each exception or interlock condition corresponds to a particular pipeline stage.

When an exception condition occurs, the relevant instruction and all that follow it in the pipeline are cancelled. Accordingly, any stall conditions and any later exception conditions that are referenced to the same instruction are inhibited; there is no value in servicing stalls for a cancelled instruction. A new instruction stream is begun, starting execution at a predefined exception vector. System control coprocessor registers are loaded with information that will identify the type of exception and any necessary auxiliary information, such as the virtual address at which translation exceptions occur.

When a stall condition is detected, all eight instructions, each in a different stage of the pipeline, are frozen at once. Often, the stall condition is only detected after parts of the pipeline have advanced using incorrect data; this occurrence is referred to as *pipeline overrun*. When in the stalled state, parts of the pipeline that are immune to overrun are frozen and the remainder is permitted to continue clocking. Just before resuming execution, the pipeline overrun is reversed by inserting corrected information into the pipeline.

When a slip condition is detected, the pipeline stages which must advance in order to resolve the dependency continue to be retired while the dependent stages are held until the necessary data is available.

Another class of interlocks exists which, since they originate external to the processor, are not referenced to a particular pipeline stage. These interlocks are referred to as *external* stalls and are unaffected by the occurrence of exceptions.

# Integer Execution Engine

The R4000 implements the extended MIPS Instruction Set architecture, and thus is fully upwards compatible with appli-

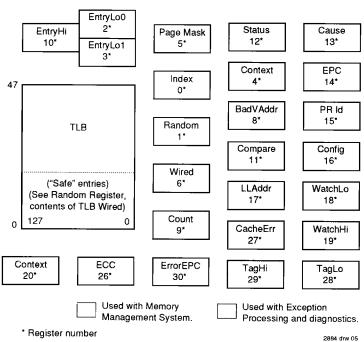

#### CP0 & the TLB

Figure 4. The R4000 CP0 Registers

5.7

5

cations running on the earlier generation parts. The R4000 includes additions to the instruction set, targeted at improving performance and capability while maintaining binary compatibility with earlier processors. The extensions result in better code density, greater multi-processing support, improved performance for commonly used code sequences in operating system kernels, and faster execution of floating-point intensive applications. All resource dependencies are made transparent to the programmer, insuring transportability amongst implementations of the MIPS instruction set architecture.

In addition to the instruction extensions detailed above, new instructions have been defined to take advantage of the 64-bit architecture of the processor. When operating as a 32-bit processor, the R4000 will take an exception on these new instructions.

The MIPS integer unit implements a load/store architecture with single cycle ALU operations (logical, shift, add, sub) and autonomous multiply/divide unit. The programmer model for the R4000 includes the register set illustrated in Figure 3. The register resources include: 32 general purpose orthogonal integer registers, the HI/LO result registers for the intger multiply/divide unit, and the program counter. In addition, the on-chip floating-point co-processor adds 32 floating-point registers, and a floating-point control/status register.

# System Control Co-processor (CP0)

The system control co-processor in the MIPS architecture is responsible for the virtual memory sub-system, the exception control system, and the diagnostics capability of the processor. In the MIPS architecture, the system control co-processor (and thus the kernel software) is implementation dependent. The R4000 CP0 is a superset extension of the MMU found in the R3000A.

The Memory management unit controls the virtual memory system page mapping. It consists of an instruction translation buffer (the ITLB), a Joint TLB (the JTLB), and co-processor registers used for the virtual memory mapping sub-system.

### System Control Co-Processor Registers

The R4000 incorporates all system control co-processor (CP0) registers on-chip. These registers provide the path through which the virtual memory system's page mapping is examined and changed, the operating modes (kernel vs. user mode, interrupts enabled or disabled, cache features) controlled, and these registers control exception handling. In addition, the R4000 includes registers to implement a real-time cycle counting facility, to address reference traps for debugging, to aid in cache diagnostic testing, and to assist in data error detection and correction.

Figure 4 illustrates the System Control Co-Processor.

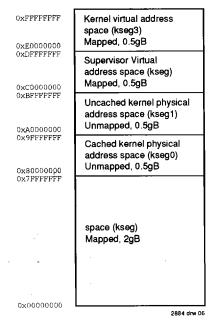

# Virtual to Physical Address Mapping

The R4000 provides three modes of virtual addressing:

- user mode

- kernel mode

- supervisor mode

This mechanism is available to system software to provide a secure environment for user processes. Bits in a status register determine which virtual addressing mode is used. In the user mode, the R4000 provides a single, uniform virtual address space of 2GB:

When operating in the kernel mode, four distinct virtual address spaces, totalling 4GB, are simultaneously available and are differentiated by the high-order bits of the virtual address.

The R4000 processors also support a supervisor mode in which the virtual address space is 2.5GB, divided into two regions based on the high-order bits of the virtual address. The three different modes of virtual addressing are shown in Figure 5. When the R4000 is configured as a 64-bit microprocessor, the virtual address space layout is a compatible extension of the 32-bit virtual address space layout.

#### Joint TLB

For fast virtual-to-physical address decoding, the R4000 uses a large, fully associative TLB which maps 96 Virtual pages to their corresponding physical addresses. The TLB is organized as 48 pairs of even-odd entries, and maps a virtual address and address space identifier into the large, 64gB physical address space.

Two mechanisms are provided to assist in controlling the amount of mapped space, and the replacement characteristics of various memory regions. First, the page size can be configured, on a per-entry basis, to map a page size of 4KB to 16MB (in multiples of 4). A CPO register is loaded with the page size of a mapping, and that size is entered into the TLB when

Figure 5. Kernel Mode Virtual Addressing (32-bit mode)

a new entry is written. Thus, operating systems can treat various regions of memory distinctly from applications programs and data files: for example, a typical frame buffer can be memory mapped using only one TLB entry.

The second mechanism controls the replacement algorithm when a TLB miss occurs. The R4000 uses a Random Replacement algorithm to select a TLB entry to be written with a new mapping; however, the processor provides a mechanism whereby a system specific number of mappings can be locked into the TLB, and thus avoid being randomly replaced. This facilitates the design of real-time systems, by allowing deterministic access to critical software.

The joint TLB also contains information to control the cache coherency protocol for each page. Specifically, each page has attribute bits to determine whether the coherency algorithm is:

uncached, noncoherent, sharable, exclusive, or update. The use of these attributes, coupled with state information in the processor caches, enables a wide variety of multi-processing strategies to be easily implemented.

Figure 6 shows the format of the TLB entry and registers used to control the TLB.

#### Instruction TLB

The R4000 also incorporates a 2-entry instruction TLB. Each entry maps a 4KB page. The instruction TLB improves performance by allowing instruction address translation to occur in parallel with data address translation. When a miss occurs on an instruction address translation, the ITLB is filled from the JTLB. The operation of the ITLB is invisible to the user.

Figure 6. Fields of an R4000 TLB Entry

#### Register File

The R4000 has thirty-two general purpose registers. These registers are used for scalar integer operations and address calculation. The register file consists of two read ports and one write port, and uses bypassing to enable the reading and writing of the same register twice per cycle as well as to minimize the operation latency in the pipeline.

#### ALU

The R4000 ALU consists of the integer adder and logic unit. The adder performs address calculations in addition to arithmetic operations, and the logic unit performs all shift operations. Each of these units is highly optimized and can perform an operation in a single superpipeline cycle.

# Integer Multiplier/Divider

The R4000 integer multiplier and divider units perform signed and unsigned multiply and divide operations and execute instructions in parallel with the ALU. The results of the operation are placed in the MDHI and MDLO registers. The values can then be transferred to the general purpose register file using the MFHI/MFLO instructions. The following table shows the number of processor internal cycles required between a 32-bit integer multiply or divide and a subsequent MFHI or MFLO operation, in order that no interlock or stall occurs.

| Operation | Single Word | Double Word |

|-----------|-------------|-------------|

| MULT      | 10          | 20          |

| DIV       | 69          | 133         |

2884 tbl 01

# FLOATING-POINT UNIT

The R4000 incorporates an entire floating-point unit on chip, including a floating-point register file and execution unit. The floating-point unit forms a "seamless" interface with the integer unit, decoding and executing instructions in parallel with the integer unit.

# Floating-point Co-Processor

The R4000 floating-point execution unit supports single and double precision arithmetic, as specified in the IEEE Standard 754. The execution unit is broken into separate multiply, divide, and add/convert/square root units, which allow for overlapped operations. The multiplier is pipelined, allowing a new multiply to begin every 4 cycles.

As in the IDT79R2010 and IDT79R3010, the R4000 maintains fully precise floating-point exceptions while allowing both overlapped and pipelined operations. Precise exceptions are extremely important in mission-critical environments, such as ADA, and highly desirable for debugging in any environment.

The floating-point unit's operation set includes floating-point add, subtract, multiply, divide, square root, conversion between fixed-point and floating-point format, conversion among floating-point formats, and floating-point compare. Thes operations comply with the IEEE Standard 754.

The following table gives the latencies of some of the floating-point instructions in internal processor cycles.

| Operation | Single<br>Precision | Double<br>Precision |

|-----------|---------------------|---------------------|

| ADD       | 4                   | 4                   |

| SUB       | 4                   | 4                   |

| MUL       | 7                   | 8                   |

| DIV       | 23                  | 36                  |

| SQRT      | 54                  | 112                 |

| CMP       | 3                   | 3                   |

| FIX       | 4                   | 4                   |

| ROUND     | 4                   | 4                   |

| TRUNC     | 4                   | 4                   |

| FLOAT     | 5                   | 5                   |

| ABS       | 2                   | 2                   |

| MOV       | 1                   | 1                   |

| NEG       | 2                   | 2                   |

| LWC1,LDC1 | 3                   | 3                   |

| SWC1,SDC1 | 1                   | 1                   |

# Floating-Point General Register File

2884 tbl 02

The floating-point register file is made up of sixteen 64-bit registers which can also be viewed as thirty-two 32-bit floating-point registers. The MIPS architecture supports a coprocessor load and store double so, when configured as 64-bit registers, the floating-point unit can take advantage of the 64-bit wide data cache and issue a co-processor load or store a doubleword instruction in every cycle.

# Floating-Point Control Register File

The floating-point control registers contain a register for determining configuration and revision information for the coprocessor and control and status information. These are primarily involved with diagnostic software, exception handling, state saving and restoring, and control of rounding modes.

#### CACHE MEMORY

In order to keep the R4000's high-performance superpipeline full and operating efficiently, the R4000 incorporates on-chip instruction and data caches. Each cache has its own 64-bit data path that can be accessed twice a cycle, so the instruction and data caches can be accessed in parallel with full pipelining. Combining this feature with a pipelined, single master clock cycle access of each cache, the cache subsystem provides the integer and floating-point units with an aggregate bandwidth of 2GB per second at a system clock frequency of 75MHz.

#### Instruction Cache

The IDT79R4000 incorporates a direct-mapped on-chip instruction cache. This virtually indexed, physically tagged

5.7

cache is 8KB in size and is protected with byte parity. The R4400 doubles the on-chip instruction cache to 16KB.

Because the cache is virtually indexed, the virtual-tophysical address translation occurs in parallel with the cache access, thus further increasing performance by allowing these two operations to occur simultaneously. The tag holds a 24bit physical address and valid bit, and is parity protected.

The instruction cache is 64-bits wide, and can be refilled or accessed twice per master clock cycle, although the current IDT79R4000 CPU fetches on 32-bit unit/master cycle for a peak instruction bandwidth of 400MB/sec. The line size can be configured as four or eight words to allow different applications to have a line size that delivers optimum performance.

#### **Data Cache**

For fast, single cycle data access, the IDT79R4000 includes an 8KB on-chip data cache. The R4400 doubles the on-chip instruction cache to 16KB.

The data cache is protected with byte parity and its tag is protected with a single parity bit. It is virtually indexed and physically tagged to allow simultaneous address translation and data cache access.

The Data Cache is direct mapped, and its line size can be configured as four or eight words. The write policy is writeback, which means that a Store to a cache line does not immediately cause memory to be updated. This increases system performance by reducing bus traffic and eliminating the bottleneck of waiting for each Store operation to finish before issuing a subsequent memory operation.

Associated with the Data Cache is the store buffer. When the R4000 executes a Store instruction, this 2-entry buffer gets written with the store data while the tag comparison is performed. If the tag matches, then the data gets written into the Data Cache in the next cycle that the Data Cache is not accessed. The store buffer allows the R4000 to execute two stores per master cycle and to perform back-to-back stores without penalty. Likewise, the R4000 can perform two loads or a load and store per master cycle without penalty, yielding 1.2GB/sec bandwidth without restrictions on instruction combinations.

When the Data Cache line does need to be written back to slower memory (either secondary cache or main memory), the processor writes the data to an internal write buffer which can hold a line (4 or 8 words) of data. By writing the data to the fast write buffer, the processor can continue executing instructions without having to wait until the write completes to the slower memory.

The IDT79R4000 caches are designed for easy and flexible integration in many types of multiprocessor systems. The Data Cache contains all the necessary state bits to allow the R4000 to maintain cache coherency across all R4000 processors in a system.

# SECONDARY CACHE INTERFACE

The R4000/R4400SC and R4400MC support a secondary cache that can range in size from 128KBs to 4MBs. The cache can be configured as a unified cache or split into an instruction cache and a data cache, and it can be designed using industry standard SRAMs. The IDT R4000 provides all of the secondary cache control circuitry on chip, including ECC.

The secondary cache interface consists of a 128-bit data bus, a 25-bit tag bus, and 18-bit address bus, and SRAM control signals. The wide data bus improves performance by providing a high bandwidth data path to fill the primary caches. ECC check bits are added to both the data and tag buses to improve data integrity. All double-bit errors can be detected and all single bit-errors can be detected and all single bit-errors can be corrected on both buses.

The secondary cache access time is configurable, providing system designers with the flexibility to tailor the cache design to specific applications. The line size of the secondary cache is also configurable and can be 4, 8, 16, or 32 words. The line size of the primary cache must always be less than or equal to the line size of the secondary cache.

The secondary cache is physically tagged and physically indexed. The physical cache prevents problems that could arise due to virtual address aliasing. Also, a physical cache makes multiprocessing cache coherency protocols easier to implement. The R4400MC provides a set of cache states and a mechanism for manipulating the contents and state of the

Figure 7. Typical Desktop System Block Diagram

cache, which are sufficient to implement a variety of cache coherency protocols, using either bus snooping or directory based schemes.

#### SYSTEM INTERFACE

The R4000 supports a 64-bit system interface that can be used to construct systems as simple as a uniprocessor with a direct DRAM interface and no secondary cache or as sopisticated as a fully cache coherent multiprocessor. The interface consists of a 64-bit Address/Data bus with 8 check bits and a 9-bit command bus protected with parity. In addition, there are 8 handshake signals. The interface has a simple timing specification and is capable of transferring data between the processor and memory at a peak rate of 600MB/sec at 75MHz.

Figure 7 shows a typical desktop system using the R4000PC. Similarly, a high-performance desktop workstation/server system can be built using the IDT79R4000SC and adding a secondary cache.

The system interface allows the processor to access external resources in order to satisfy cache misses and uncached operations. The IDT79R4000MC, in addition to handling simple memory and I/O transactions, supports a number of cache coherency transactions of sufficient generality to support variety of cache coherent multiprocessing models. In particular, the interface is designed to support both bus snooping and directory based multiprocessor models and supports both write-update and write-invalidate coherency protocols.

Figure 8 shows a typical multiprocessor system using the IDT79R4000MC, an interface agent, and a secondary cache.

#### System Address/Data Bus

The 64-bit System Address Data (SysAD) bus is used to transfer addresses and data between the R4000 and the rest of the system. It is protected with an 8-bit check bus, SysADC. The check bits can be configured as either parity or ECC, for flexibility in interfacing to either parity or ECC memory systems.

The system interface is configurable to allow easier interfacing to memory and I/O systems of varying frequencies. The data rate and the bus frequency at which the R4000 transmits data to the system interface are programmable via boot time mode control bits. Also, the rate at which the processor receives data is fully controlled by the external device. Therefore, either a low cost interface requiring no write buffering or a fast, high performance interface can be designed to communicate with the R4000. Again, the system designer has the flexibility to make these price/perfomance tradeoffs.

# **System Command Bus**

The R4000 interface has a 9-bit System Command (SysCmd) bus. The command bus indicates whether the SysAD bus carries an address or data. If the SysAD carries an address, then the SysCmd bus also indicates what type of transaction is to take place (for example, a read or write). If the SysAD carries data, then the SysCmd bus also gives information about the data (for example, this is the last data word transmitted, or the cache state of this line of data is clean exclusive). The SysCmd bus is bidirectional to support both processor requests and external requests to the R4000. Processor requests are initiated by the R4000 and responded to by an external device. External requests are issued by an external device and require the R4000 to respond.

The R4000 supports byte, halfword, tribyte, word, doubleword, and block transfers on the SysAD bus. In the case of a sub-doubleword transfer, the low-order 3 address bits gives the byte address of the transfer, and the SysCmd bus indicates the number of bytes being transferred.

#### Handshake Signals

There are eight handshake signals on the system interface. Two of these,  $\overline{\text{RdRdy}}$  and  $\overline{\text{WrRdy}}$  are used by an external device to indicate to the IDT79R4000 whether it can accept a new read or write transaction. The IDT79R4000 samples these signals before deasserting the address on read and write requests.

Figure 8. Multiprocessor System Using the R4400 MC

10

ExtRqst and Release are used to transfer control of the SysAD and SysCmd buses between the processor and an external device. When an external device needs to control the interface, it asserts ExtRqst. The IDT79R4000 responds by asserting Release to release the system interface to slave state.

$\label{eq:ValidOut} \begin{tabular}{ll} \hline ValidOut and $\overline{ValidIn}$ are used by the IDT79R4000 and the external device respectively to indicate that there is a valid command or data on the SysAD and SysCmd buses. The R4000 asserts $\overline{ValidOut}$ when it is driving these buses with a valid command or data, and the external device drives $\overline{ValidIn}$ when it has control of the buses and is driving a valid command or data. \\ \end{tabular}$

Finally, there are two signals that are available on the MC version only and are used in multiprocessing systems. They are <a href="IvdAck">IvdAck</a> and <a href="IvdAck">IvdErr</a>, and they are driven by an external device to indicate the completion status of the current processor invalidate or update request.

# **R4000 Requests**

The R4000 is capable of issuing requests to a memory and I/O subsystem. The system interface supports two modes of operation:

- · Secondary Cache mode

- · No Secondary Cache mode

# No Secondary Cache Mode

The R4000 without a secondary cache requires a nonoverlapping system interface. This means that only one processor request may be outstanding at a time and that the request must be serviced by an external device before the R4000 issues another request. The R4000PC can issue read and write requests to an external device, and an external device can issue read and write requests to the R4000.

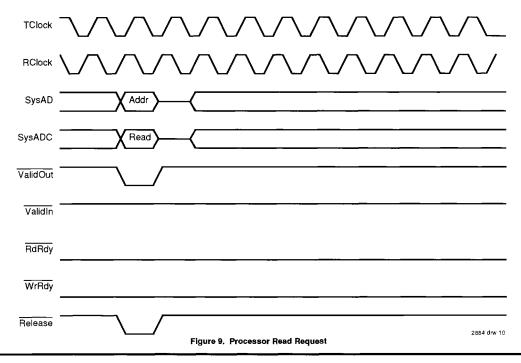

Figure 9 shows a processor read request. The R4000 asserts ValidOut and simultaneously drives the address and read command on th SysAD and SysCmd buses. If the system interface has RdRdy asserted, then the processor tristates its drivers and releases the system interface to slave state by asserting Release. The external device can then begin sending the data to the IDT79R4000.

# Secondary Cache Mode

The R4000 with a secondary cache operates in an overlapping bus transfer mode in which multiple system interface transactions may be issued in parallel. The processor may issue a combination of read request, an update or invalidate request, and a write request. For instance, when a dirty cache line needs to be replaced, the processor issues a read request immediately followed by a write request, without waiting for the read data to return. This has the advantage of "hiding" the write transaction between the read request and read response, thus increasing overall system performance. This mode of operation is not necessary or useful in R4000 systems without secondary cache since the processor contains a write buffer capable of accepting an entire primary cache line of data. Overlapping is a superset of non-overlapping systemoperation.

5.7

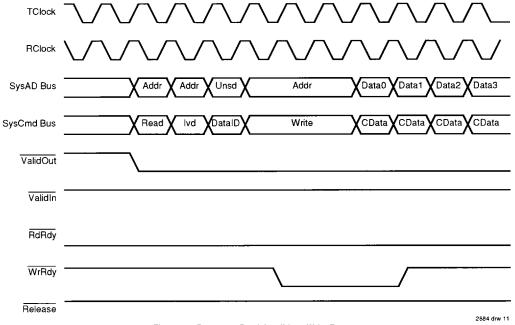

Figure 10 illustrates a processor request in overlap mode. This request is made up of a read, invalidate, and write request. Note that the protocol for the read, the invalidate, and the write are all similar to each other, with the exception that the processor also sends out valid data during the write request. In Figure 10 the processor write transaction not only occurs before the read response from the external device, but it also illustrates how an external device can hold off a write request through the deassertion of WrRdy.

# **External Requests**

The R4000 responds to requests issued by an external device. The requests can take several forms. An external device may need to supply data in response to an R4000 read request or it may need to gain control over the system interface bus to access other resources which may be on that bus. It also may issue cache coherency requests to the processor, such as a request for the R4000 to update, invalidate, or snoop upon its caches, or to supply a cache line of data. Additionally, an external device may need to write to the R4000 interrupt register.

The following is a list of the supported external requests:

- Read

- Write

- · Invalidate

- Update

- Snoop

- InterventionNull

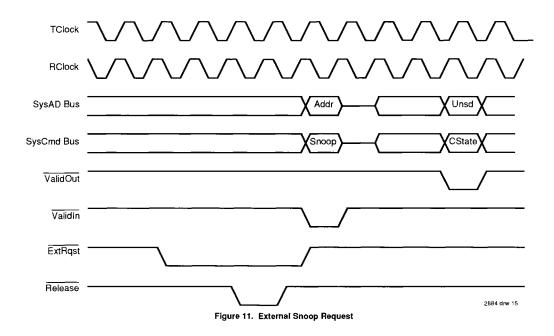

Figure 11 shows an example of an external snoop request. The process by which the external device issues the request is very similar to the way the R4000 issues a request. The external device first gains ownership of the system interface by asserting ExtRqst and waiting for the R4000 to assert Release. The external device then sends in a valid command by asserting ValidIn and driving the SysCmd and SysAD buses with the snoop command and address. The R4000 responds to the request by asserting ValidOut and driving the SysCmd bus with the cache state of the snooped upon line.

#### CACHE COHERENCY CAPABILITY

With the IDT79R4400MC, cache coherence is maintained in hardware. The system control coprocessor permits the specification of different caching protocols on a per-page basis. A page may be:

- · uncached

- · cached but non-coherent

- cached and coherent exclusive (only one processor cache contains the data on loads and stores).

- cached and coherent exclusive on writes (write invalidate scheme-only one processor cache contains the data when that datum is written to).

- cached and coherent with updates on writes (writeupdate scheme).

Depending upon the amount and type of data sharing in an application, the operating system can choose the most appropriate caching strategy.

Figure 10. Processor Read, Invalidate, Write Request

5.7

12

Support for processor synchronization is provided by the Load Linked and Store Conditional instructions. The Load Linked and Store Conditional instructions:

- Provide a simple mechanism for generating all of the common synchronization primitives including test-andset, bit-level locks, semaphores, counters, sequencers, etc. with no additional hardware overhead.

- Operate in such a fashion that bus traffic is only generated when the state of the cache line changes.

- Need not lock a system bus—a very important feature for larger systems.

#### ADVANCED FEATURES

The R4000 supports a number of other capabilities in addition to the standard processor model described above. Many of these capabilities are selected by the system designer during the processor reset sequence, via the boot time mode control interface. Features are included to support fault tolerance, system test, or other system environments.

### **Boot Time Options**

Fundamental operational modes for the processor are initialized by the boot-time mode control interface. The boot-time mode control interface is a serial interface operating at a very low frequency (Master clock divided by 256). The low frequency operation allows the initialization information to be kept in a low cost EPROM.

Immediately after the VCCOk Signal is asserted, the processor reads a serial bit stream of 256 bits to initialize all fundamental operational modes. After initialization is com-

plete, the processor continues to drive the serial clock output, but no further initialization bits are read.

#### JITAG INTERFACE

The JTAG boundary scan mechanism provides a capability for testing the interconnect between the IDT79R4000 processor, the printed circuit board to which it is attached, and the other components on the board. In addition the JTAG boundary scan mechanism provides a rudimentary capability for low-speed logical testing of the secondary cache RAMs. The JTAG boundary scan mechanism does not provide any capability for testing the R4000 processor itself.

In accordance with the JTAG specification the R4000 processor contains a TAP controller, JTAG instruction register, JTAG boundary scan register, JTAG identification register, and JTAG bypass register. However, the R4000 JTAG implementation provides only the *external test* functionality of the boundary scan register.

# **FAULT TOLERANT SUPPORT**

The R4000 has been designed to support varying models of fault tolerance. These modes include: master/checker operation and triple-modular redundancy. In addition to explicit fault-tolerant modes of operation, the design of internal processor operation is such to support processor synchronization; for example, both the TLB random replacement algorithm, and the on-chip timer, can be forced to known states via software. Thus, the IDT R4000 family can be used to build "non-stop" machines across a number of different system models.

5.7

# **BOOT-TIME MODES**

| Serial Bit | Value                                             | Mode Setting                                                                                                                             |

|------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0          |                                                   | BlkOrder: Block read response ordering.                                                                                                  |

|            | 0                                                 | Sequential ordering.                                                                                                                     |

|            | 1                                                 | Sub-block ordering.                                                                                                                      |

| 1          |                                                   | EIBParMode: System interface check bus checking.                                                                                         |

|            | 0                                                 | SECDED error checking and correcting mode.                                                                                               |

|            | 1                                                 | Byte parity.                                                                                                                             |

| 2          |                                                   | EndBlt: Byte ordering.                                                                                                                   |

|            | 0                                                 | Little Endian.                                                                                                                           |

|            | 1                                                 | Big Endian.                                                                                                                              |

| 3          |                                                   | <b>DShMdDis:</b> Dirty shared mode, enables transition to dirty shared state on processor update                                         |

|            |                                                   | successful.                                                                                                                              |

|            | 0                                                 | Dirty Shared Enabled                                                                                                                     |

|            | 1                                                 | Dirty Shared Disabled.                                                                                                                   |

| 4          | 1                                                 | NoSCMode: Specifies presence of secondary cache.                                                                                         |

|            | 0 1                                               | Present. Not Present.                                                                                                                    |

|            | <del>  '                                   </del> |                                                                                                                                          |

| 5:6        |                                                   | SysPort: System Interface port width (Bit 6 Most Significant).                                                                           |

|            | 0 1-3                                             | 64 bits. Reserved <sup>(1)</sup>                                                                                                         |

|            | 1-0                                               | <u> </u>                                                                                                                                 |

| 7          |                                                   | SC64BitMd: Secondary cache interface port width.                                                                                         |

|            | 0                                                 | 128 bits. Reserved <sup>(1)</sup>                                                                                                        |

|            | + '                                               |                                                                                                                                          |

| 8          | 0                                                 | EISpltMd: Secondary cache organization Unified                                                                                           |

|            | 1                                                 | Reserved <sup>(1)</sup>                                                                                                                  |

| 0:40       | <del>  '</del>                                    |                                                                                                                                          |

| 9:10       | 0                                                 | SCBIkSz: Secondary cache line size (Bit 10 Most Significant). 4 words.                                                                   |

|            | 1 1                                               | 8 words.                                                                                                                                 |

|            | 2                                                 | 16 words.                                                                                                                                |

|            | 3                                                 | 32 words.                                                                                                                                |

| 11:14      |                                                   | XmitDatPat: System Interface Data Rate (Bit 14 Most Significant).                                                                        |

|            | l 0                                               | D                                                                                                                                        |

|            | 1                                                 | DDx                                                                                                                                      |

|            | 2                                                 | DDxx                                                                                                                                     |

|            | 3                                                 | DxDx                                                                                                                                     |

|            | 4                                                 | DDxxx                                                                                                                                    |

|            | 5                                                 | DDxxxx                                                                                                                                   |

|            | 6                                                 | DxxDxx                                                                                                                                   |

|            | 7 8                                               | DDxxxxxx                                                                                                                                 |

|            | 9-15                                              | DxxxDxxx Reserved <sup>(†)</sup>                                                                                                         |

| 15:17      | 3-13                                              |                                                                                                                                          |

| 15:17      | 1                                                 | SysCkRatio: PClock to SClock divisor: frequency relationship between SClock, RClock, and TClock and PClock (Bit 17 MostSignificant).     |

|            | 0                                                 | Divide by 2                                                                                                                              |

|            | l ĭ                                               | Divide by 3                                                                                                                              |

|            | 2                                                 | Divide by 4                                                                                                                              |

|            | 3-7                                               | Reserved <sup>(1)</sup>                                                                                                                  |

| 18         | 0                                                 | Reserved (Required value)                                                                                                                |

| 19         | <u> </u>                                          | TimIntDis: Timer Interrupt enable allows timer interrupts, otherwise the interrupt used by the                                           |

|            | 1                                                 | timer becomes a general-purpose interrupt.                                                                                               |

|            | 0                                                 | Enabled                                                                                                                                  |

|            | 1                                                 | Disabled                                                                                                                                 |

|            |                                                   |                                                                                                                                          |

| 20         |                                                   | PotUpdDis: Potential invalidate enable (allows potential invalidates to be issued. Otherwise                                             |

| 20         |                                                   | <b>PotUpdDis:</b> Potential invalidate enable (allows potential invalidates to be issued. Otherwise only normal invalidates are issued). |

| 20         | 0                                                 |                                                                                                                                          |

| Serial Bit | Value                                            | Mode Setting                                                                                                                            |

|------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 21:24      |                                                  | TWrSUp: Secondary cache write deassertion delay, Twrsup in PCycles (Bit 24 Most Significant).                                           |

|            | 0-2                                              | Undefined                                                                                                                               |

|            | 3-15                                             | Mumber of PCLK cycles (Min 3; Max 15)                                                                                                   |

| 25:26      | Į                                                | TWr2Dly: Secondary cache write assertion delay 2, TwrDly in PCycles (Bit 26 Most Signifi                                                |

|            | 0                                                | cant). Undefined                                                                                                                        |

|            | 1-3                                              | Number of PCLK cycles (Min 1; Max 3)                                                                                                    |

| 27:28      | <u> </u>                                         | TWr1Dly: Secondary cache write assertion delay 1, TwrDiy in PCycles (Bit 28 Most Signifi                                                |

|            |                                                  | cant).                                                                                                                                  |

|            | 1-3                                              | Undefined Number of PCLK cycles (Min 1; Max 3)                                                                                          |

| 29         | 1-3                                              | TWrRc: Secondary cache write recovery time, TWrRc in PCycles either 0 or 1 cycles.                                                      |

| 29         | 0                                                | 0 cycle                                                                                                                                 |

|            | 1                                                | 1 cycle                                                                                                                                 |

| 30:32      |                                                  | TDis: Secondary cache disable time, TDis in PCycles (Bit 32 Most Significant).                                                          |

|            | 0                                                | Undefined Number of PCLK cycles (Min 2; Max 7)                                                                                          |

| 33:36      | <u> </u>                                         | TRd2Cyc: Secondary cache read cycle time 2, TRdCyc2 in PCycles (Bit 36 Most Significant).                                               |

| 55.55      | 0-2                                              | Undefined                                                                                                                               |

|            | 3-15                                             | Number of PCLK cycles (Min 3; Max 15)                                                                                                   |

| 37:40      |                                                  | TRd2Cyc: Secondary cache read cycle time 1, TRdCyc1 in PCycles, (Bit 40 Most Significant).                                              |

|            | 0-3<br>4-15                                      | Undefined Number of PCLK cycles (Min 4; Max 15)                                                                                         |

| 41:45(2)   | 0                                                | Reserved.                                                                                                                               |

| 46         | <del>+                                    </del> | Pkq179: R4000 type.                                                                                                                     |

| 40         | 0                                                | Large (447 pin). SC/MC                                                                                                                  |

|            | 1                                                | Small (179). PC                                                                                                                         |

| 47:49      | 1                                                | CycDivisor: This mode determines the clock divisior for the reduced power mode. When the                                                |

|            |                                                  | RP bit in the Status Register is set to one, the pipeline clock is divided by one of the following values (Bit 49 is Most Significant). |

|            | 0                                                | Divide by 2                                                                                                                             |

|            | 1 2                                              | Divide by 4 Divide by 8                                                                                                                 |

|            | 3                                                | Divide by 8 Divide by 16                                                                                                                |

|            | 4-7                                              | Reserved <sup>(1)</sup>                                                                                                                 |

| 50:52      |                                                  | Drv0_50, Drv0_75, Drv1_00: Drive the outputs in N x MasterClock period (Bit 52 Most                                                     |

|            | 0-1                                              | Significant) .  Drive at 0.5 x MasterClockperiod.                                                                                       |

|            | 2-3                                              | Drive at 0.75 x MasterClock period.                                                                                                     |

|            | 4-7                                              | Drive at 1.0 x MasterClock period.                                                                                                      |

| 53:56      |                                                  | InitP: Initial values for the state bits that determine the pull-down di/dt and switching speed                                         |

|            |                                                  | of the output buffers (Bit 53 Most Significant).  Fastest pull-down rate.                                                               |

|            | 1-14                                             | Intermediate pull-down rate.                                                                                                            |

|            | 15                                               | Slowest pull-down rate.                                                                                                                 |

| 57:60      |                                                  | InitN: Initial values for the state bits that determine the pull-up di/dt and switching speed                                           |

|            | 0                                                | of the output buffers (Bit 57 Most Significant).  Slowest pull-up rate.                                                                 |

|            | 1-14                                             | Intermediate pull-up rates.                                                                                                             |

|            | 15                                               | Fastest pull-up rate                                                                                                                    |

| 61         |                                                  | EnbIDPLLR: Enables the negative feedback loop that determines the di/dt and switching                                                   |

|            | 0                                                | speed of the output buffers only during ColdReset.  Disable di/dt control mechanism.                                                    |

|            | 1                                                | Enable di/dt control mechanism.                                                                                                         |

|            |                                                  |                                                                                                                                         |

| Serial Bit | Value | Mode Setting                                                                                                                                                   |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62         |       | EnbiDPLL: Enables the negative feedback loop that determines the di/dt and switching speed of the output buffers during ColdReset and during normal operation. |

|            | 0     | Disable di/dt control mechanism.                                                                                                                               |

|            | 1     | Enable di/dt control mechanism.                                                                                                                                |

| 63         |       | DsbIDPLL: Enables PLLs that match Masterin and produce RClock, TClock, SClock and the                                                                          |

|            |       | internal clocks.                                                                                                                                               |

|            | 0     | Enable PLLs.                                                                                                                                                   |

|            | 1     | Disable PLLs.                                                                                                                                                  |

| 64         |       | SRTristate: Controls when output-only pins are trestated                                                                                                       |

|            | 0     | Only whe Cold Reset is asserted.                                                                                                                               |

|            | 1     | When Reset or Cold Reset are asserted                                                                                                                          |

| 65-255     | 0(2)  | Reserved (must be scanned in as zeros).                                                                                                                        |

# NOTES:

2884 tbl 05

- Selecting a Reserved value results in undefined processor behavior.

O's must be presented for these reserved values.

5.7 16

# **PIN DESCRIPTION**

The following is a list of interface, interrupt, and maintenance pins available on the different package configurations.

| Pin Name           | Туре                | Description                                                                                                                                                                                                                             |

|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secondary cach     | e interface pins av | vailable only on the SC and MC configuration:                                                                                                                                                                                           |

| SCAddr(17:1)       | Output              | Secondary cache address bus A 17-bit address bus for the secondary cache.                                                                                                                                                               |

| SCAddr0(W:Z)       | Output              | Secondary cache address lsb<br>To minimize loading effect, there are 4 identical copies of this signal.                                                                                                                                 |

| SCAPar(2:0)        | Output              | Secondary cache address parity bus A 3-bit bus that carries the parity of the SCAddr bus and the cache control lines SCOE, SCWR, SCDCS and SCTCS.                                                                                       |

| SCData(127:0)      | Input/Output        | Secondary cache data bus<br>A 128-bit bus used to read or write cache data from/to the secondary cache.                                                                                                                                 |

| SCDChk(15:0)       | Input/Output        | Secondary cache data ECC bus A 16-bit bus that carries two 8-bit ECC fields that covers the 128 bits of the SCData from/to the secondary cache. SCDChk(15:8) corresponds to SCData(127:64) and SCDChk(7:0) corresponds to SCData(63:0). |

| SCDCS              | Output              | Secondary cache data chip select Chip select enable signal for the secondary cache Ram associated with SCData and SCDChk.                                                                                                               |

| SCOE               | Output              | Secondary cache output enable Output enable for the secondary cache RAM.                                                                                                                                                                |

| SCTag(24:0)        | Input/Output        | Secondary cache tag bus A 25-bit bus used to read or write cache tags from/to the secondary cache.                                                                                                                                      |

| SCTChk(6:0)        | Input/Output        | Secondary cache tag ECC bus A 7-bit bus that carries an ECC field covering the SCTag from/to the secondary cache.                                                                                                                       |

| SCTCS              | Output              | Secondary cache tag chip select<br>Chip select enable signal for the secondary cache tag RAM associated with SCTag and<br>SCTChk.                                                                                                       |

| SCWr(W:Z)          | Output              | Secondary Cache write enable Write enable for the secondary cache RAM.                                                                                                                                                                  |

| System interface p | oins available on a | all parts:                                                                                                                                                                                                                              |

| ExtRqst            | Input               | External request Signals that the system interface needs to submit an external request.                                                                                                                                                 |

| Release            | Output              | Release interface Signals that the processor is releasing the system interface to slave state                                                                                                                                           |

| RdRdy              | Input               | Read Ready Signals that an external agent can now accept a processor read, invalidate, or update request in both secondary cache and no secondary cache mode or can accept a read followed by a write request in secondary cache mode.  |

| SysAD(63:0)        | Input/Output        | System address/data bus A 64-bit address and data bus for communication between the processor and an external agent.                                                                                                                    |

| SysADC(7:0)        | Input/Output        | System address/data check bus An 8-bit bus containing check bits for the SysAD bus.                                                                                                                                                     |

| SysCmd(8:0)        | Input/Output        | System command/data identifier bus A 9-bit bus for command and data identifier transmission between the processor and an external agent.                                                                                                |

| SysCmdP            | Input/Output        | System command/data identifier bus parity A single, even-parity bit for the SysCmd bus.                                                                                                                                                 |

| ValidIn            | Input               | Valid Input Signals that an external agent is now driving a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.                                                                            |

| Pin Name            | Туре                  | Description                                                                                                                                                                                         |

|---------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Valid Out           | Output                | Valid output Signals that the processor is now driving a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.                                           |

| WrRdy               | Input                 | Write Ready Signals that an external agent can now accept a processor write request in both non-overlap and overlap mode.                                                                           |

| System interface    | pins available only   | on the MC configuration.                                                                                                                                                                            |

| ĪvdAck              | Input                 | Invalidate acknowledge<br>Signals successful completion of a processor invalidate or update request.                                                                                                |

| lvdErr              | Input                 | Invalidate error<br>Signals unsuccessful completion of a processor invalidate or update request.                                                                                                    |

| Interrupt pins ava  | ilable only on the F  | PC configuration:                                                                                                                                                                                   |

| Int(5:1)            | Input                 | Interrupt Five of six general processor interrupts, bit-wise ORed with bits 5:1 of the interrupt register.                                                                                          |

| Interrupt pin avail | able on all devices   |                                                                                                                                                                                                     |

| Înt(0)              | Input                 | Interrupt One of six general processor interrupts, bit-wise ORed with bit 0 of the interrupt register.                                                                                              |

| Non-maskable int    | terrupt pin available | e on all devices:                                                                                                                                                                                   |

| ЙMI                 | Input                 | Non-maskable interrupt<br>Non-maskable interrupt, ORed with bit 6 of the interrupt register.                                                                                                        |

| Boot-time mode of   | control interface pir | ns available on all devices:                                                                                                                                                                        |

| ModeClock           | Output                | Boot mode clock Serial boot-mode data clock output at the system clock frequency divided by two hundred and fifty six.                                                                              |

| Modeln              | Input                 | Boot mode data in<br>Serial boot-mode data input.                                                                                                                                                   |

| JTAG interface pi   | ns available on all   | devices:                                                                                                                                                                                            |

| JTDI                | Input                 | JTAG data in<br>JTAG serial data in.                                                                                                                                                                |

| JTCK                | Input                 | JTAG clock input JTAG serial clock input.                                                                                                                                                           |

| JTDO                | Output                | JTAG data out<br>JTAG serial data out.                                                                                                                                                              |