# Intel<sup>®</sup> LXT914 Flexible Quad Ethernet Repeater

# **Datasheet**

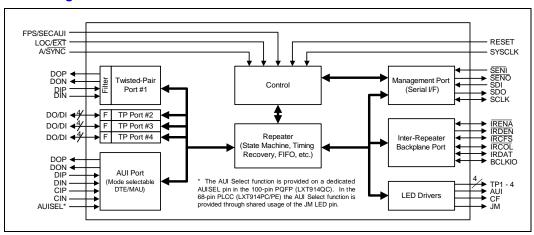

The Intel<sup>®</sup> LXT914 Flexible Quad Ethernet Repeater (called hereafter the LXT914 Repeater) is an integrated multi-port repeater designed for mixed-media networks. It provides all the active circuitry required for the repeater function in a single CMOS device. It includes one Attachment Unit Interface (AUI) port and four 10BASE-T transceivers. The AUI port is mode selectable: DTE mode allows connection of an external transceiver (10BASE2, 10BASE5, 10BASE-T or FOIRL) or a drop cable. MAU mode creates a MAU output allowing direct connection to another DTE interface. The 10BASE-T transceivers are entirely self-contained with internal filters which simplify the design work required for FCC-compliant EMI performance.

An inter-repeater backplane interface allows 128 or more 10BASE-T ports to be cascaded together. In addition, a serial port provides information for network management.

The LXT914 Repeater requires only a single 5-volt power supply due to an advanced CMOS fabrication process.

# **Product Features**

- Four integrated 10BASE-T transceivers and one AUI transceiver on a single chip

- Programmable DTE/MAU interface on AUI port

- Seven integrated LED drivers with four unique operational modes

- On-chip transmit and receive filtering

- Automatic partitioning of faulty ports, enabled on an individual port basis

- Automatic polarity detection and correction

- Programmable squelch level allows extended range in low-noise environments

- Synchronous or asynchronous interrepeater backplane supports "hot swapping"

- Inter-repeater backplane allows cascaded repeaters, linking 128 or more 10BASE-T ports

- Serial port for selecting programmable options

- 68-pin PLCC (Commercial or Extended temp range)

- 100-pin PQFP (Commercial temp range)

# **Applications**

- LAN Repeaters

- Integrated Repeaters

Switched Repeater Clusters

Order Number: 248989, Revision: 003 31-Oct-2005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES REALATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

The Intel® LXT914 Flexible Quad Ethernet Repeater may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at <a href="http://www.intel.com">http://www.intel.com</a>.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation. All Rights Reserved.

| 1.0 | LXT        | 914 Pin Assignments and Signal Descriptions   | 7  |

|-----|------------|-----------------------------------------------|----|

| 2.0 | Fund       | ctional Description                           | 14 |

|     | 2.1        | Introduction                                  | 14 |

|     | 2.2        | External Interfaces                           | 14 |

|     |            | 2.2.1 10BASE-T Ports                          | 14 |

|     |            | 2.2.2 AUI Port                                | 14 |

|     |            | 2.2.3 Serial Port                             | 14 |

|     |            | 2.2.4 Inter-Repeater Backplane                |    |

|     |            | 2.2.4.1 Synchronous IRB Operation             |    |

|     |            | 2.2.4.2 Asynchronous IRB Operation            | 15 |

|     | 2.3        | Internal Repeater Circuitry                   | 15 |

|     | 2.4        | Initialization                                |    |

|     |            | 2.4.1 Local Management Mode Initialization    |    |

|     |            | 2.4.2 External Management Mode Initialization |    |

|     | 2.5        | 10BASE-T Port Operation                       |    |

|     |            | 2.5.1 10BASE-T Reception                      |    |

|     |            | 2.5.1.1 Programmable Internal Squelch Level   |    |

|     |            | 2.5.1.2 Polarity Detection and Correction     |    |

|     |            | 2.5.2 10BASE-T Transmission                   |    |

|     |            | 2.5.3 10BASE-T Link Integrity Testing         |    |

|     | 2.6        | AUI Port Operation                            |    |

|     |            | 2.6.1 AUI Reception                           |    |

|     |            | 2.6.2 AUI Transmission                        |    |

|     | 0.7        | 2.6.3 AUI Mode Selection (DTE/MAU)            |    |

|     | 2.7        | Collision Handling                            |    |

|     | 2.8<br>2.9 | Security Mode                                 |    |

|     | 2.9        | LED Display                                   | 23 |

| 3.0 | Appl       | lication Information                          | 27 |

|     | 3.1        | Layout Requirements                           | 27 |

|     |            | 3.1.1 The Twisted Pair Interface              | 27 |

|     |            | 3.1.2 The RBIAS Pin                           | 27 |

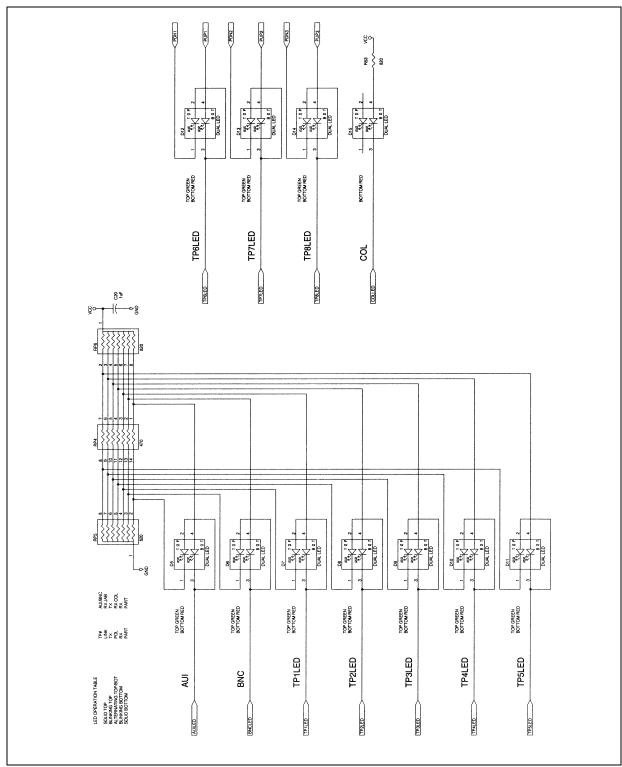

|     | 3.2        | 12-Port Hub Repeater                          | 27 |

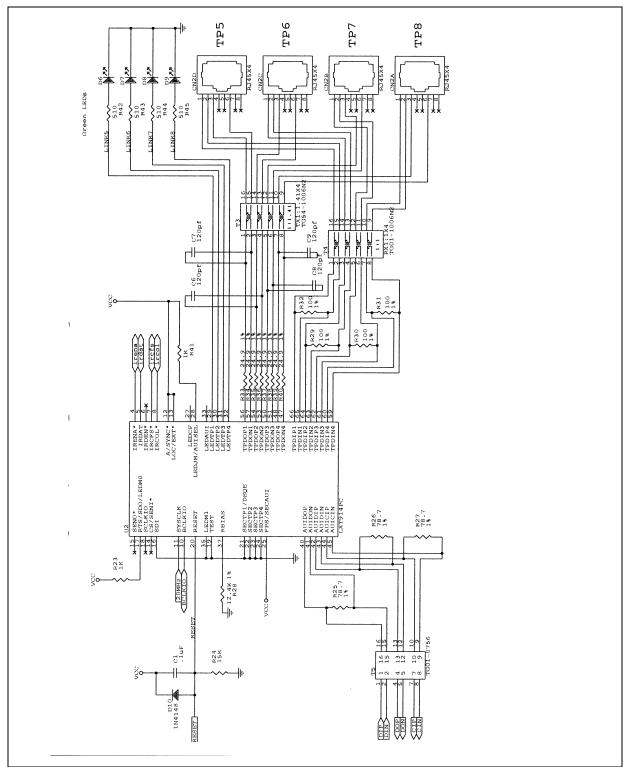

|     | 3.3        | 8-Port Print or File Server                   | 28 |

| 1.0 | Test       | Specifications                                | 35 |

| 5.0 | Pack       | kage Specifications                           | 40 |

|     | 5.1        | Top-Label Marking                             | 42 |

| 6.0 | Prod       | duct Ordering Information                     | 44 |

# **Figures**

| 1      | Block Diagram                                                             | 7  |

|--------|---------------------------------------------------------------------------|----|

| 2      | Pin Assignments                                                           |    |

| 3      | Global State Machine                                                      |    |

| 4      | Partitioning State Machine                                                |    |

| 5      | Integrated LED Driver Indications                                         |    |

| 6      | 12-Port Application Schematic, 68-Pin PLCC Package (Sheet 1 of 4)         |    |

| 7      | 12-Port Application Schematic, 68-Pin PLCC Package (Sheet 2 of 4)         |    |

| 8      | 12-Port Application Schematic, 68-Pin PLCC Package (Sheet 3 of 4)         |    |

| 9      | 12-Port Application Schematic, 68-Pin PLCC Package (Sheet 4 of 4)         |    |

| 10     | 8-Port Application Schematic, LED Mode 1 with AUISEL = MAU (Sheet 1 of 2) |    |

| 11     | 8-Port Application Schematic, LED Mode 1 with AUISEL = MAU (Sheet 2 of 2) |    |

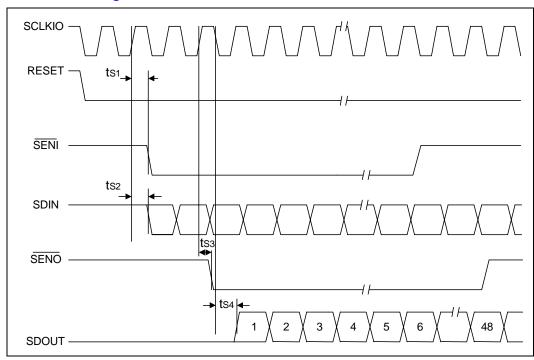

| 12     | Serial Port Timing                                                        | 38 |

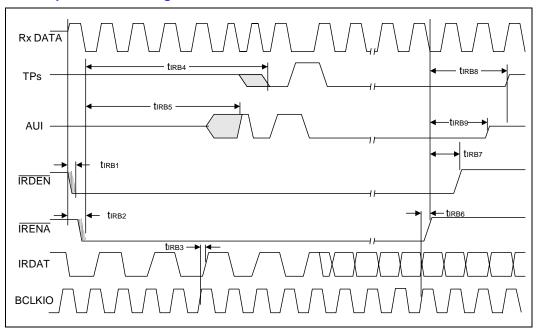

| 13     | Inter-Repeater Bus Timing                                                 | 39 |

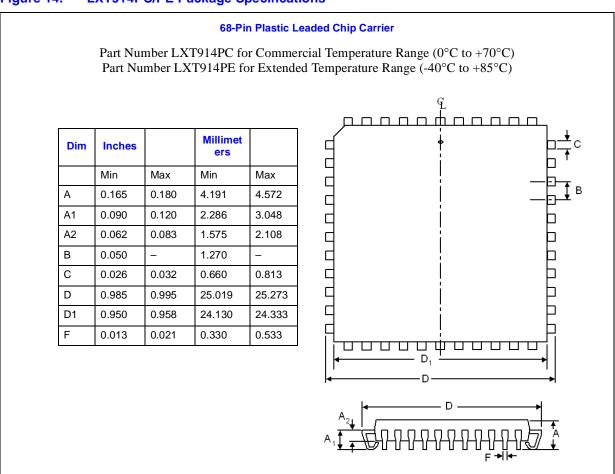

| 14     | LXT914PC/PE Package Specifications                                        | 40 |

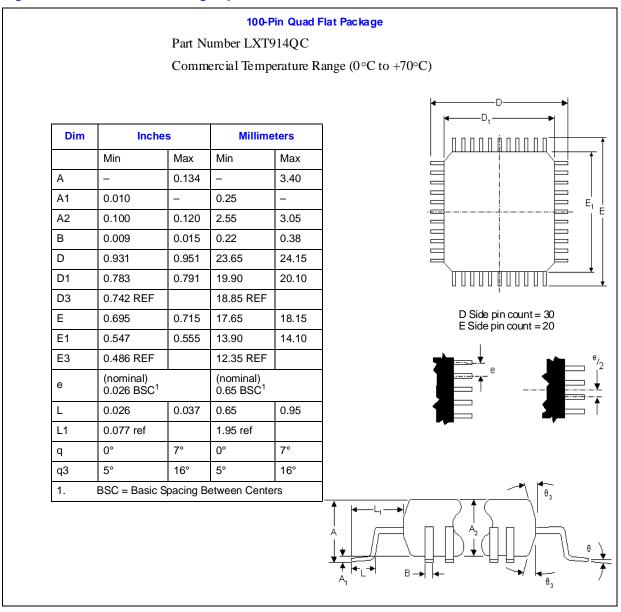

| 15     | LXT914QC Package Specifications                                           |    |

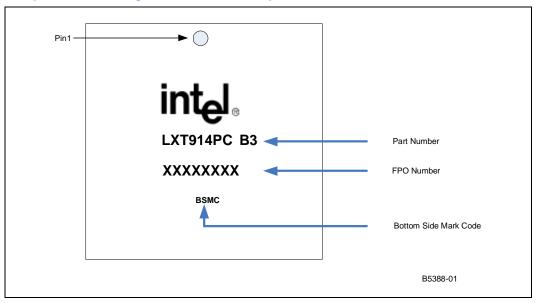

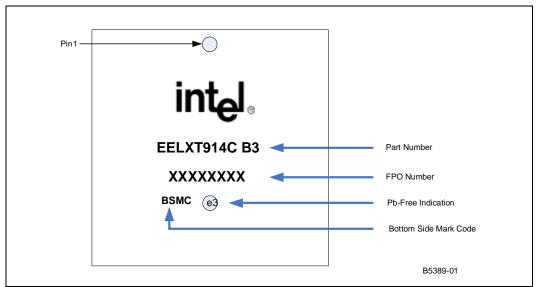

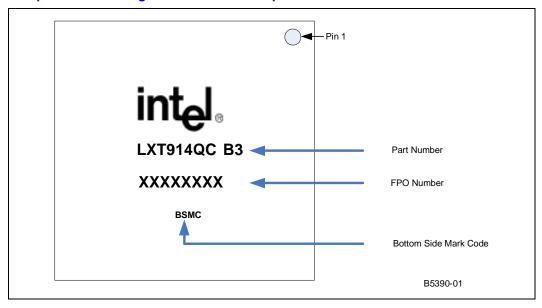

| 16     | Sample PLCC Package - Intel® LXT914 Repeater                              |    |

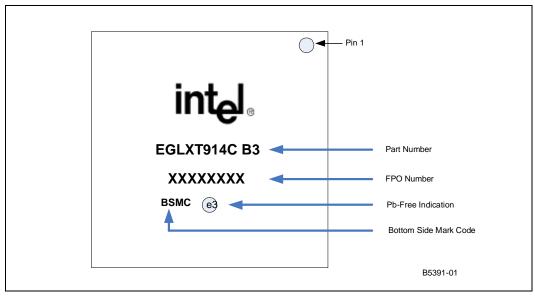

| 17     | Sample Pb-Free (RoHS-Compliant) PLCC Package - Intel® LXT914 Repeater     | 42 |

| 18     | Sample PQFP Package - Intel® LXT914 Repeater                              | 43 |

| 19     | Sample Pb-Free (RoHS-Compliant) PQFP Package - Intel® LXT914 Repeater     | 43 |

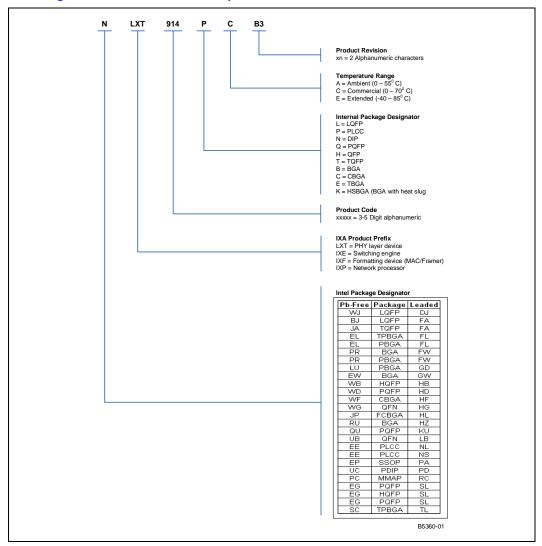

| 20     | Ordering Information Matrix – Sample                                      | 45 |

|        |                                                                           |    |

| Tab    | les                                                                       |    |

|        |                                                                           |    |

| 1      | Power, Ground, and Clock Signal Descriptions                              |    |

| 2<br>3 | Inter-Repeater Backplane Signal Descriptions                              |    |

| 4      | Serial Port Signal Descriptions (External Management Mode)                |    |

| 5      | Serial Port Signal Descriptions (External Management Mode)                |    |

| 6      | Miscellaneous Control Signal Descriptions                                 |    |

| 7      | LED Driver Signal Descriptions                                            |    |

| 8      | Repeater Port Signal Descriptions                                         |    |

| 9      | Setup Register Bit Assignments                                            |    |

| 10     | Setup Register Bit Definitions                                            |    |

| 11     | Packet Status Register Bit Assignments                                    |    |

| 12     | Packet Status Register Bit Definitions                                    |    |

| 13     | AUI Mode Selection (DTE/MAU)                                              |    |

| 14     | LED Mode Selection                                                        |    |

| 15     | Mode 0 (Default) LED Truth Table                                          |    |

| 16     | Mode 1 LED Truth Table                                                    |    |

| 17     | Mode 2 LED Truth Table                                                    |    |

| 18     | Mode 3 LED Truth Table                                                    | 25 |

| 19     | Manufacturers Magnetics List                                              |    |

| 20     | Absolute Maximum Ratings                                                  |    |

| 21     | Recommended Operating Conditions                                          | 35 |

| 22     | I/O Electrical Characteristics <sup>1</sup>                               | 35 |

| 23     | AUI Electrical Characteristics                                            | 36 |

| 24     | Twisted-Pair Electrical Characteristics                                   |    |

| 25     | IRB Electrical Characteristics                                            | 37 |

|        |                                                                           |    |

# Intel® LXT914 Flexible Quad Ethernet Repeater

| 26 | Switching Characteristics        | .37 |

|----|----------------------------------|-----|

|    | Serial Port Timing—External Mode |     |

| 28 | Inter-Repeater Bus Timing        | .38 |

|    | Product Ordering Information     |     |

# Revision History

| Date        | Revision | Description                                                                                                                                                                                                                                                                             |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Oct-2005 | 003      | <ul> <li>Added Section 5.1 and Figure 16 through Figure 19 (RoHS top labels).</li> <li>Added Section 6.0, "Product Ordering Information" on page 44 with Table 29 "Product Ordering Information" on page 44 and Figure 20 "Ordering Information Matrix – Sample" on page 45.</li> </ul> |

| Feb 2001    | 002      | <ul> <li>Added Layout Requirements section under Application Information.</li> <li>Modified I/O Electrical Characteristics table: Change Max value under Supply Current from 180 to 240; Add text under Test Conditions: "100 test load, no LEDs"; add table note 3.</li> </ul>         |

7

# 1.0 LXT914 Pin Assignments and Signal Descriptions

# Figure 1. Block Diagram

Intel® LXT914 Flexible Quad Ethernet Repeater Order Number: 248989, Revision: 003

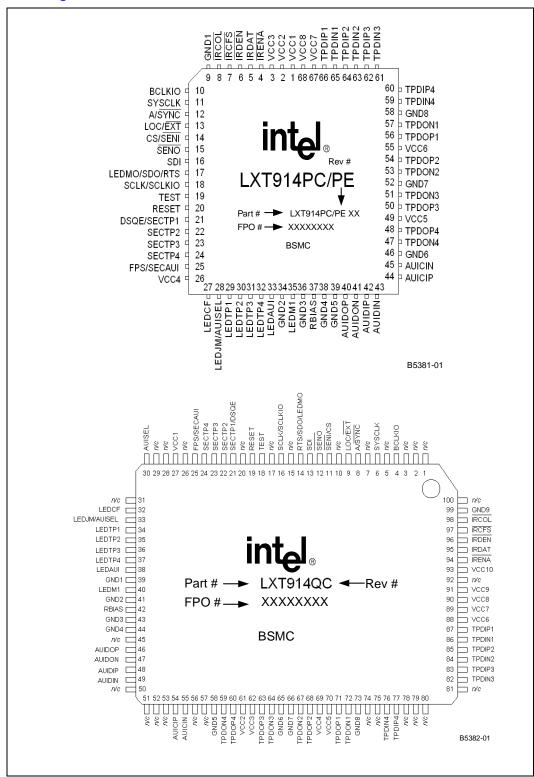

Figure 2. Pin Assignments

# Table 1. Power, Ground, and Clock Signal Descriptions

| Piı  | n #  | # Symbol |        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

|------|------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| PLCC | PQFP | Symbol   | Cymbol | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description |

| 1    | 27   | VCC1     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 2    | 61   | VCC2     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 3    | 62   | VCC3     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 26   | 69   | VCC4     | _      | Power Supply Inputs. These pins each require a +5 VDC power supply.                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 49   | 70   | VCC5     | _      | The various pins may be supplied from a single power source, but special                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| 55   | 88   | VCC6     | _      | de-coupling requirements may apply. Each VCC input must be within ±0.3                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| 67   | 89   | VCC7     | _      | V of every other VCC input.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

| 68   | 90   | VCC8     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| _    | 91   | VCC9     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| _    | 93   | VCC10    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 9    | 39   | GND1     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 34   | 41   | GND2     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 36   | 43   | GND3     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 38   | 44   | GND4     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 39   | 58   | GND5     | _      | <b>Ground.</b> These pins provide ground return paths for the various power supply pins.                                                                                                                                                                                                                                                                                                                                                                                      |             |

| 46   | 65   | GND6     | _      | очерну рино.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| 52   | 66   | GND7     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 58   | 73   | GND8     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| -    | 99   | GND9     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 37   | 42   | RBIAS    | _      | <b>Bias.</b> This pin provides bias current for the internal circuitry. The 100 μA bias current is provided through an external 12.4 k $\Omega$ resistor to ground.                                                                                                                                                                                                                                                                                                           |             |

| 10   | 4    | BCLKIO   | I/O    | Backplane Clock. This 10 MHz clock synchronizes multiple repeaters on a common backplane. In the synchronous mode, BCLKIO must be supplied to all repeaters from a common external source. In the asynchronous mode, BCLKIO is supplied only when a repeater is outputting data to the bus. Each repeater outputs its internally recovered clock when it takes control of the bus. Other repeaters on the backplane then sync to BCLKIO for the duration of the transmission. |             |

| 11   | 6    | SYSCLK   | I      | <b>System Clock.</b> The required 20 MHz system clock is input at this pin. Clock must have a 40-60 duty cycle with < 10 ns rise time.                                                                                                                                                                                                                                                                                                                                        |             |

#### Table 2. Inter-Repeater Backplane Signal Descriptions

| PLCC | PQFP     | Symbol         | 1/0        | Description                                                                                                                                                                                                                                                                                                                                |

|------|----------|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | 94       | ĪRĒNĀ          | I/O        | Inter-Repeater Backplane Enable. This pin allows individual LXT914 repeaters to take control of the Inter-Repeater Backplane (IRB) data bus (IRDAT). The IRENA bus must be pulled up locally by a 330 Ω resistor. 1                                                                                                                        |

| 5    | 95       | IRDAT          | I/O        | IRB Data. This pin is used to pass data between multiple repeaters on the IRB. The IRDAT bus must be pulled up locally by a 330 $\Omega$ resistor. <sup>1</sup>                                                                                                                                                                            |

| 6    | 96       | ĪRDEN          | 0          | IRB Driver Enable. The $\overline{\text{IRDEN}}$ pin is used to enable external bus drivers which may be required in synchronous systems with large backplanes. This is an active Low signal, maintained for the duration of the data transmission. IRDEN must be pulled up locally by a 330 $\Omega$ resistor.                            |

| 7 8  | 97<br>98 | IRCFS<br>IRCOL | I/O<br>I/O | IRB Collision Flag Sense (IRCFS) and IRB Collision (IRCOL). These two pins are used for collision signalling between multiple LXT914 devices on the Inter-Repeater Backplane (IRB). Both the IRCFS bus and the IRCOL bus must be pulled up globally with 330 $\Omega$ resistors. (IRCFS requires a precision resistor [±1%].) <sup>2</sup> |

#### NOTES:

- 1.  $\overline{\text{IRENA}}$  and IRDAT can be buffered between boards in multi-board configurations. Where buffering is used, a 330  $\Omega$  pull-up resistor can be used on each signal, on each board. Where no buffering is used, the total impedance should be no less than 330  $\Omega$ .

- 2. IRCFS and IRCOL cannot be buffered. In multi-board configurations, the total impedance on IRCOL should be no smaller than 330  $\Omega$ . IRCFS should be pulled up only once, by a single 330  $\Omega$ , 1% resistor.

# Table 3. Mode Select and Control Signal Descriptions

| PLCC     | PQFP     | Symbol           | I/O        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|----------|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12       | 8        | A/SYNC           | ı          | Backplane Sync Mode Select. This pin selects the backplane sync mode. When this pin is left floating an internal pull-up defaults to the Asynchronous mode (A/SYNC High). In the asynchronous mode 12 or more LXT914s can be connected on the backplane, and an external 10 MHz backplane clock source is not required. When the synchronous mode is selected (A/SYNC tied Low), 32 or more LXT914s can be connected to the backplane and an external 10 MHz backplane clock source is required. |

| 13       | 9        | LOC/EXT          | ı          | Management Mode Select. This pin selects the management mode. When this pin is left floating, an internal pull-up defaults to the Local management mode (LOC/EXT High). In the Local mode, setup parameters are downloaded from an EEPROM during initialization. Once initialized with the setup parameters, the repeater functions independently.                                                                                                                                               |

| 28       | 33       | LEDJM/<br>AUISEL | I/O        | LED Driver or DTE/MAU Select. At reset, this pin selects the mode of the AUI port. If left floating, an internal pull-down device forces the AUI port to DTE mode. If pulled High with an external resistor, the port changes to a MAU, in which case the functions of the LEDJM pin are disabled and the default LED mode (Refer to Table 7) is not available.                                                                                                                                  |

| _        | 30       | AUISEL           | I          | <b>DTE/MAU Select.</b> This pin changes the mode of the AUI port independent of the condition at reset. This function is available only in the 100-pin PQFP package.                                                                                                                                                                                                                                                                                                                             |

| 17<br>35 | 14<br>40 | LEDM0<br>LEDM1   | I/O<br>I/O | <b>LED Mode 0 &amp; 1 Select.</b> These two pins select one of four possible LED modes of operation. The Functional Description section describes the four modes.                                                                                                                                                                                                                                                                                                                                |

# Table 4. Serial Port Signal Descriptions (External Management Mode)

| PLCC | PQFP | Symbol | I/O | Description                                                                                                                                                                                                                                                                                                                                           |

|------|------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | 11   | SENI   | ı   | Serial Enable Input. This active Low input is used to access the LXT914 serial interface. To write to the serial input (SDI), an External Management Device (EMD) must drive this pin from High to Low. The input must be asserted Low concurrent with the appearance of data on SDI and remain Low for the duration of the serial input transaction. |

| 15   | 12   | SENO   | 0   | <b>Serial Enable Output.</b> This active Low output is used to access the serial interface of an EMD. When the LXT914 sends a data stream to the EMD through the serial port (SDO), this output transitions from High to Low and remains Low for the duration of the serial transmission.                                                             |

| 16   | 13   | SDI    | 1   | <b>Serial Data Input.</b> This pin is the input for the EMD serial interface. Setup and operating parameters are supplied to the LXT914 in a serial data stream through this port when operating in the External Management Mode.                                                                                                                     |

| 17   | 14   | SDO    | I/O | <b>Serial Data Output.</b> After each packet transmission or interrupt event, the LXT914 reports status information to the EMD in a serial data stream through this port.                                                                                                                                                                             |

| 18   | 16   | SCLK   | I   | <b>Serial Clock.</b> This 10 MHz clock synchronizes the serial interface between the LXT914 and the EMD. Both devices must be supplied from the same clock source. In synchronous mode, SCLK and BCLK may be tied together.                                                                                                                           |

# Table 5. Serial Port Signal Descriptions (Local Management Mode)

| PLCC | PQFP | Symbol | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | 11   | CS     | 0   | Chip Select. The LXT914 is designed for use with an EEPROM or similar device which may be used to store setup parameters and serially download them to the LXT914 during initialization. In a single-device application or in the first device of a daisy chain application, this pin is an active High Chip Select output used to enable the EEPROM.                                                                                         |

|      |      | SENI   | I   | Serial Enable Input. In subsequent devices of a daisy-chain configuration, a High-to-Low transition on this pin enables the serial input port (SDI). The input must be asserted concurrent with the appearance of data on SDI and remain Low for the duration of the serial input transaction.                                                                                                                                                |

| 15   | 12   | SENO   | 0   | Serial Enable Output. During initialization, the LXT914 accepts 48 bits of setup data through the SDI port. After the 48th bit, the LXT914 asserts this pin Low. When multiple LXT914 devices are connected in a daisy-chain, this output is tied to the SENI input of the next device in the chain. Thus each device in the chain is serially enabled by the previous device until all the devices have read in their 48 bits of setup data. |

| 16   | 13   | SDI    | I   | <b>Setup Data Input.</b> This pin is the serial input port for the setup parameters (48 bits). This pin should be tied Low if no EEPROM is present.                                                                                                                                                                                                                                                                                           |

| 17   | 14   | RTS    | I/O | Request To Send. In a single-device application or in the first device of a daisy chain application, this pin outputs a 9-bit, active High sequence. This pin must be tied to the EEPROM DI input to trigger the EEPROM to download its stored data. In subsequent devices this pin is not used.                                                                                                                                              |

| 18   | 16   | SCLKIO | I/O | <b>Serial Clock.</b> A 1 MHz clock provided by the first LXT914 in the chain to all subsequent repeaters and the EEPROM. In the Local mode all repeaters have their SCLKIO pins tied together.                                                                                                                                                                                                                                                |

# Table 6. Miscellaneous Control Signal Descriptions

| PLCC           | PQFP           | Symbol                                   | I/O | Description                                                                                                                                                                                                                                                                                                                                 |

|----------------|----------------|------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19             | 18             | TEST                                     | I   | Test Mode Select. This pin must be tied Low for normal operation.                                                                                                                                                                                                                                                                           |

| 20             | 19             | RESET                                    | I   | <b>RESET.</b> This pin resets the LXT914 circuitry when pulled High for ≥ 1 ms.                                                                                                                                                                                                                                                             |

|                |                | DSQE<br>(Local)                          | I   | <b>DSQE.</b> In Local Mode, this pin controls the SQE function. When High, the SQE function of the AUI port is disabled. When Low, SQE is enabled.                                                                                                                                                                                          |

| 21             | 21             | SECTP1<br>(External)                     | ı   | Security Mode Select (TP Port 1). In External Mode, this pin enables the security mode for twisted-pair port 1. When pulled High, the LXT914 Jams the port. This pin must be tied Low if external security control is not required.                                                                                                         |

| 22<br>23<br>24 | 22<br>23<br>24 | SECTP2<br>SECTP3<br>SECTP4<br>(External) |     | Security Mode Select (TP Ports 2–4). In External Mode, these pins enable the security mode for the respective twisted-pair ports (TP1 through TP4). When pulled High, the LXT914 jams the affected port. The SEC pins must be tied Low if external security control is not required.                                                        |

| 25             | 25             | FPS<br>(Local)                           | ı   | First Position Select. In the Local mode this pin identifies the first device in a daisy chain configuration. When tied High (First position), the LXT914 controls the local EEPROM by providing clock and handshaking. When tied Low (Not First), the LXT914 will accept CLK and data in its turn from previous LXT914s in the data chain. |

|                |                | SECAUI<br>(External)                     | I   | Security Mode Select (AUI Port). In the External mode this pin enables the security mode for the AUI port. When pulled High, the LXT914 jams the AUI port. The security feature is available only in External management mode.                                                                                                              |

# Table 7. LED Driver Signal Descriptions

| PLCC | PQFP | Symbol | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27   | 32   | LEDCF  | 0   | Collision & FIFO Error LED Driver. This tri-state LED driver pin reports collisions and FIFO errors. It pulses Low to report collisions, and pulses High to report FIFO errors. When this pin is connected to the anode of one LED and to the cathode of a second LED, the LXT914 will simultaneously monitor and report both conditions independently.                                                          |

| 28   | 33   | LEDJM  | 0   | Jabber/MJLP & Manchester Code Violation LED Driver. This tri-state LED driver pin reports jabber and code violations. It pulses Low to report MAU Jabber Lockup Protection (MJLP), and pulses High to report Manchester code violations. When this pin is connected to the anode of one LED and to the cathode of a second LED, the LXT914 will simultaneously monitor and report both conditions independently. |

| 29   | 34   | LEDTP1 | 0   | Twisted-Pair Port LED Drivers. These tri-state LED drivers use an                                                                                                                                                                                                                                                                                                                                                |

| 30   | 35   | LEDTP2 | 0   | alternating pulsed output to report TP port status. Each pin should be tied to                                                                                                                                                                                                                                                                                                                                   |

| 31   | 36   | LEDTP3 | 0   | a pair of LEDs (to the anode of one LED and the cathode of a second LED).  When connected this way, each pin reports five separate conditions                                                                                                                                                                                                                                                                    |

| 32   | 37   | LEDTP4 | 0   | (receive, transmit, link integrity, reverse polarity and auto partition).                                                                                                                                                                                                                                                                                                                                        |

| 33   | 38   | LEDAUI | 0   | <b>AUI Port LED Driver.</b> This tri-state LED driver uses an alternating pulsed output to report AUI port status. This pin should be tied to a pair of LEDs (to the anode of one LED and the cathode of a second LED). When connected this way, this pin reports five separate conditions (receive, transmit, receive jabber, receive collision and auto partition.                                             |

# Table 8. Repeater Port Signal Descriptions

|          |          |                  |        | ,                                                                                                                                            |

|----------|----------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC     | PQFP     | Symbol           | 1/0    | Description                                                                                                                                  |

| 40       | 46       | AUIDOP           | 0      | AUI Data Outputs (Positive and Negative). These pins are the positive and negative data outputs for the AUI Port. In MAU Mode these pins are |

| 41       | 47       | AUIDON           | 0      | connected to the DI pins of the DTE.                                                                                                         |

| 42       | 48       | AUIDIP           | ı      | AUI Data Input (Positive and Negative). These pins are the positive and negative data inputs for the AUI Port. In MAU Mode, these pins are   |

| 43       | 49       | AUIDIN           | I      | connected to the DO pins of the DTE.                                                                                                         |

| 44       | 54       | AUICIP           | I/O    | AUI Collision (Positive and Negative). These pins are the positive and negative Collision inputs for the AUI Port in DTE Mode. In MAU Mode,  |

| 45       | 55       | AUICIN           | I/O    | these pins output a collision indication to the DTE.                                                                                         |

| 56       | 71       | TPDOP1           | 0      |                                                                                                                                              |

| 57       | 72       | TPDON1           | 0      |                                                                                                                                              |

| 54<br>53 | 68<br>67 | TPDOP2<br>TPDON2 | 0      | Twisted-Pair Data Outputs (Positive and Negative). These pins are the                                                                        |

| 50       | 63       | TPDOP3           | 0      | positive (TPDOP1-4) and negative (TPDON1-4) outputs to the network                                                                           |

| 51       | 64       | TPDON3           | Ö      | from the respective twisted-pair ports.                                                                                                      |

| 48       | 60       | TPDOP4           | 0      |                                                                                                                                              |

| 47       | 59       | TPDON4           | 0      |                                                                                                                                              |

| 66<br>65 | 87<br>86 | TPDIP1<br>TPDIN1 | I<br>I |                                                                                                                                              |

| 64       | 85       | TPDIP2           |        |                                                                                                                                              |

| 63       | 84       | TPDIP2<br>TPDIN2 |        | Twisted-Pair Data Inputs (Positive and Negative). These pins are the                                                                         |

| 62       | 83       | TPDIP3           | ı      | positive (TPDIP1-4) and negative (TPDIN1-4) inputs from the network to the respective twisted-pair ports.                                    |

| 61       | 82       | TPDIN3           | - 1    | and respective timetod pair portor                                                                                                           |

| 60       | 77       | TPDIP4           | -1     |                                                                                                                                              |

| 59       | 76       | TPDIN4           | I      |                                                                                                                                              |

# 2.0 Functional Description

### 2.1 Introduction

The LXT914 Repeater is an integrated hub repeater for 10BASE-T networks. The hub repeater is the central point for information transfer across the network. The LXT914 Repeater offers multiple operating modes to suit a broad range of applications ranging from simple 4-port stand-alone hubs or attachments for print and file servers, up to intelligent 128-port enterprise systems with microprocessor/gate arLXT914 Repeater ray management.

The main functions of the LXT914 Repeater hub repeater are data recovery and re-transmission and collision propagation. Data packets received at the AUI or 10BASE-T ports are detected and recovered by the port receivers before being passed to the repeater core circuitry for re-timing and re-transmission. Data packets received through the IRB port are essentially passed directly to the core for retransmission. After recovery of a valid data packet, the repeater broadcasts it to all enabled stations, except the originator station.

# 2.2 External Interfaces

The LXT914 Repeater includes four 10BASE-T ports with internal filters. The LXT914 Repeater also includes an Attachment Unit Interface (AUI) port, a serial port and an Inter-Repeater Backplane (IRB) port. The serial port allows an external device such as an EEPROM to download setup parameters to the repeater. In more complex designs the serial port can also be used to monitor repeater status. The IRB port enables multiple LXT914 Repeater devices to be cascaded, creating a large, multi-port repeater.

### 2.2.1 10BASE-T Ports

The four 10BASE-T transceiver ports are completely self-contained. Since the transmitters and receivers include the required filtering, only simple, inexpensive transformers are required to complete the 10BASE-T interface. Each individual Twisted-Pair (TP) port is implemented in accordance with the IEEE 802.3 10BASE-T standard.

#### 2.2.2 AUI Port

The AUI port mode is selectable (DTE mode or MAU mode). With DTE mode selected, the AUI port allows connection of an external transceiver (10BASE2, 10BASE5, 10BASE-T or FOIRL) or a drop cable. With MAU mode selected, the AUI port establishes a MAU output allowing direct connection to another DTE interface.

### 2.2.3 Serial Port

The serial port provides the management interface to the LXT914 Repeater. Refer to Test Specifications for serial port timing. The serial port can be either unidirectional or bidirectional, depending on the management mode selected. In the Local management mode the serial port is

Order Number: 248989, Revision: 003

unidirectional (input only), and is used only to download setup parameters during initialization. The Local mode is intended for use with a simple EEPROM, but the serial port may be tied Low if an EEPROM is not required.

In the External management mode, the serial port is bi-directional (input for setup parameters, output for status reports). The External mode is intended for use with an External Management Device (EMD) and a Media Access Controller (MAC). The EMD (typically a gate array) communicates with a microprocessor (e.g., Intel 8051) and can control up to three LXT914 Repeaters. This simplifies design of a relatively standard 12-port repeater on a single printed circuit board.

# 2.2.4 Inter-Repeater Backplane

The Inter-Repeater Backplane (IRB) allows several LXT914 Repeaters to function as a single repeater. Refer to Test Specifications for IRB timing. The IRB also allows several multi-repeater boards to be integrated in a standard rack and to function as a single unit. The IRB supports "hot swapping" for easy maintenance and troubleshooting. Each individual repeater distributes recovered and re-timed data to other repeaters on the IRB for broadcast on all ports simultaneously. This simultaneous rebroadcast allows the multi-repeater system to act as a single large repeater unit. The maximum number of repeaters on the IRB is limited by bus loading factors such as parasitic capacitance. The IRB can be operated synchronously or asynchronously.

# 2.2.4.1 Synchronous IRB Operation

In the synchronous mode, a common external source provides the 10 MHz backplane clock (BCLKIO) and the 20 MHz system clock (SYSCLK) to all repeaters. BCLKIO must be synchronous to SYSCLK and may be derived from SYSCLK using a divide-by-two circuit. In the synchronous mode 32 or more LXT914 Repeaters may be connected on the IRB, providing 128 10BASE-T ports and 32 AUI ports.

### 2.2.4.2 Asynchronous IRB Operation

In the asynchronous mode an external BCLKIO source is not required. The repeaters run independently until one takes control of the IRB. The transmitting repeater then outputs its own 10 MHz clock onto the BCLKIO line. All other repeaters sync to that clock for the duration of the transmission. In the asynchronous mode 12 or more LXT914 Repeater may be connected to the IRB, providing 48 10BASE-T ports and 12 AUI ports.

The maximum number of repeaters which may be linked on the backplane is limited by board design factors. The numbers listed above are engineering estimates only. Stronger drivers and reduced capacitive loading in PCB layout may allow an increased device count.

# 2.3 Internal Repeater Circuitry

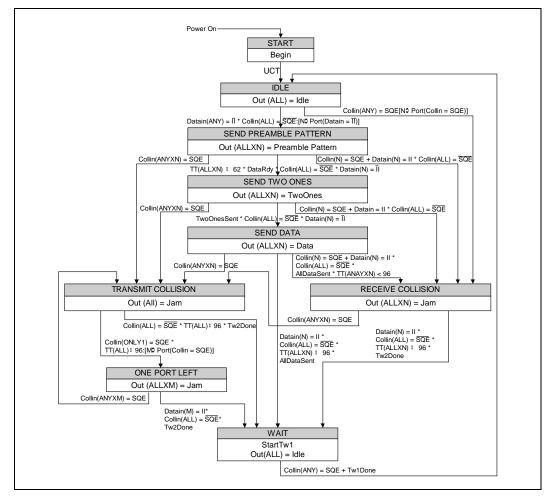

The basic repeater circuitry is shared among all the ports within the LXT914 Repeater. It consists of a global repeater state machine, several timers and counters and the timing recovery circuit. The timing recovery circuit includes a FIFO for re-timing and recovery of the clock which is used to clock the receive data out onto the IRB.

The shared functional blocks of the LXT914 Repeater are controlled by the global state machine (Figure 3). This diagram and all associated notations used are in strict accordance with section 9.6 of the IEEE 802.3 standard.

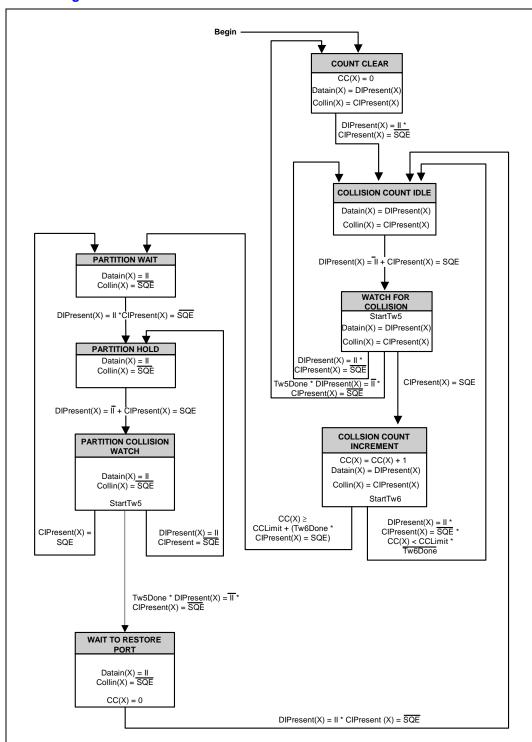

The LXT914 Repeater also implements the Partition State Diagram as defined by the IEEE 802.3 standard and shown in Figure 4. The value of CCLimit as implemented in the LXT914 Repeater is 64.

The CCLimit value sets the number of consecutive collisions that must occur before the port is subjected to automatic partitioning. Auto-partition/re-connection is also supported by the LXT914 Repeater with Tw5 conforming to the standard requirement of 450 to 560 bit times.

### 2.4 Initialization

The following description applies to the initial power-on reset and to any subsequent hardware reset. When a reset occurs (RESET pin pulled High for > 1 ms), the device senses the levels at the various control pins (see Figure 3) to determine the correct operating modes for Management, LEDs, and the AUI port functions.

# 2.4.1 Local Management Mode Initialization

An internal pull-up causes the LXT914 Repeater to default to the Local management mode unless the LOC/EXT pin is tied Low. In the Local mode the serial port is a unidirectional interface used only to download setup parameters from an external device.

In a Locally managed multiple-repeater (daisy chain) configuration, the first repeater in the chain performs special functions. The First Position Select (FPS) pin is used to establish position (FPS High = First, FPS Low = Not First). After establishing the Hardware mode, each LXT914 Repeater monitors the FPS pin to determine its position.

If FPS is High (First Position), the repeater performs the following functions:

Outputs a 1 MHz Serial Clock (SCLK). SCLK is derived from the 20 MHz SYSCLK input in ASYNC mode and from BCLKIO in SYNC mode; it is supplied to the SCLK inputs of all other repeaters on the bus and to the EEPROM.

Asserts Chip Select (CS) High to enable the EEPROM.

Outputs a serial 9-bit request-to-send (RTS) strobe. The programmable device responds to the RTS strobe with a serial data stream containing the setup parameters for all repeaters in the chain.

Clocks the first 48 serial data input (SDI) bits from the EEPROM into its setup register. Refer to Table 9 and Table 10 for Setup Register bit assignments.

Asserts Serial Enable Output (SENO) Low to enable the next repeater in line.

The second repeater has FPS tied Low and Serial Enable Input (SENI) connected to the Serial Enable Output (SENO) of the first repeater. When enabled by a Low on SENI, each repeater downloads its portion of the stream, then stops accepting data and asserts SENO Low. The SENO pin is linked to the SENI input of the next repeater. This enables the next repeater to clock in its 48-bit word and so on.

If FPS is Low (Not First Position), the repeater performs the following functions:

Order Number: 248989, Revision: 003

- 1. Syncs to the 1 MHz Serial Clock (SCLK) input. SCLK is supplied by the First Position repeater.

- 2. Responds to SENI Low by enabling the SDI port.

- 3. Clocks 48 bits from the EEPROM into its setup register through the SDI port.

- 4. Asserts SENO Low to enable the next repeater in line.

Figure 3. Global State Machine

Figure 4. Partitioning State Machine

| Table 9. | Setup | Register | <b>Bit Assid</b> | anments |

|----------|-------|----------|------------------|---------|

|          |       |          |                  |         |

| Register | D7     | D6     | D5     | D4     | D3     | D2     | D1     | D0     |

|----------|--------|--------|--------|--------|--------|--------|--------|--------|

| SR(0)    | DISLI3 | DISLI2 | DISLI1 | DISAP4 | DISAP3 | DISAP2 | DISAP1 | DISAPA |

| SR(1)    | DISTX2 | DISTX1 | DISTXA | DPRC4  | DPRC3  | DPRC2  | DPRC1  | DISLI4 |

| SR(2)    | ERSQ1  | DISRX4 | DISRX3 | DISRX2 | DISRX1 | DISRXA | DISTX4 | DISTX3 |

| SR(3)    | DFIFOE | DPFRM  | DSQE   | DMCV   | ERXJAB | ERSQ4  | ERSQ3  | ERSQ2  |

| SR(4)    | RES    |

| SR(5)    | RES    |

**Table 10. Setup Register Bit Definitions**

| Bit           | Definition                                                                                       |

|---------------|--------------------------------------------------------------------------------------------------|

| DISAPx        | 1 = Disable Auto-Partitioning on Port <i>x</i>                                                   |

| DISLIx        | 1 = Disable Link Integrity on Port x (Twisted-pair ports only)                                   |

| DPRCx         | 1 = Disable Polarity Reverse detection and Correction on Port <i>x</i> (Twisted-pair ports only) |

| DISTXx        | 1 = Disable Transmit on Port x                                                                   |

| DISRXx        | 1 = Disable Receive on Port <i>x</i>                                                             |

| ERSQ <i>x</i> | 1 = Enable Reduced Squelch on Port x (Twisted-pair ports only)                                   |

| ERXJAB        | 1 = Enable Receive JAB (Long Packet) (Global)                                                    |

| DMCV          | 1 = Disable entering Tx Collision state on reception of Manchester Code Violation                |

| DSQE          | 1 = Disable Signal Quality Error to provide heartbeat (AUI port only)                            |

| DPFRM         | 1 = Disable End-of-Frame checking for polarity correction (Global)                               |

| DFIFOE        | 1 = Disable entering Tx Collision state on FIFO over/underflow condition (Global)                |

| DMJLP         | 1 = Disable MJLP counter (Global)                                                                |

| RES           | Reserved. Must be set to 0.                                                                      |

# 2.4.2 External Management Mode Initialization

The LXT914 Repeater operates in the External management mode when the LOC/EXT pin is tied Low. In the External mode, the serial port is a bidirectional interface between the LXT914 Repeater and an external management device (EMD). The serial port is used to download initial setup parameters to the repeater and to monitor status reports from the repeater. The LXT914 Repeater setup parameters can be changed at any time by the EMD. The initialization process for each repeater in a managed mode configuration is the same, regardless of its position; each repeater is connected directly to the EMD. Each LXT914 Repeater initializes as follows:

- 1. Syncs to the 10 MHz Serial Clock (SCLK) input. SCLK must be supplied from an external source.

- 2. Responds to  $\overline{SENI}$  Low by enabling the SDI port.

- 3. Clocks 48 bits from the EMD into its setup register through the SDI port.

- 4. Once initialized, the LXT914 Repeater reports its status in a 48-bit serial stream after every packet transmission or interrupt event. Refer to Table 11 and Table 12 for packet status register bit assignments and definitions.

**Table 11. Packet Status Register Bit Assignments**

| Register | D7     | D6    | D5    | D4     | D3     | D2     | D1     | D0     |

|----------|--------|-------|-------|--------|--------|--------|--------|--------|

| PSR(0)   | COL2   | COL1  | COLA  | RX4    | RX3    | RX2    | RX1    | RXA    |

| PSR(1)   | PR2    | PR1   | LLS4  | LLS3   | LLS2   | LLS1   | COL4   | COL3   |

| PSR(2)   | SPA    | AP4   | AP3   | AP2    | AP1    | APA    | PR4    | PR3    |

| PSR(3)   | LP3    | LP2   | LP1   | LPA    | SP4    | SP3    | SP2    | SP1    |

| PSR(4)   | RXJABA | MJLP  | LCOL4 | LCOL3  | LCOL2  | LCOL1  | LCOLA  | LP4    |

| PSR(5)   | RES    | RXCOL | MANCV | FIFOER | RXJAB4 | RXJAB3 | RXJAB2 | RXJAB1 |

**Table 12. Packet Status Register Bit Definitions**

| $\mathbf{Bit}^1$ | Definition                                                               |

|------------------|--------------------------------------------------------------------------|

| RXx              | Received Packet on Twisted-Pair Port 1-4 or on AUI Port                  |

| COLx             | Transmit Collision of Twisted -Pair Port 1-4 or on AUI Port              |

| LLSCx            | Link Loss State on Twisted-Pair Port 1-4 or on AUI Port                  |

| PRx              | Polarity reversed on Twisted-Pair Port 1-4 or on AUI Port                |

| AP <i>x</i>      | Auto-Partition circuit isolated Twisted-Pair Port 1-4 or the AUI Port    |

| SPx              | Short Packet (less than 74 bits) on Twisted-Pair Port 1-4 or on AUI Port |

| LPx              | Long Packet (more than 1.3 ms) on Twisted-Pair Port 1-4 or on AUI Port   |

| LCOLx            | Late Collision on Twisted-Pair Port 1-4 or on AUI Port                   |

| MJLP             | MAU Jabber Lockup Protection                                             |

| RXJAB <i>x</i>   | Receive Jabber Lockup Protection                                         |

| FIFOER           | FIFO overflow/underflow                                                  |

| MANCV            | Manchester Code Violation                                                |

| RXCOL            | Receive Collision on the AUI Port                                        |

| RES              | Reserved. Not used                                                       |

| Noto             |                                                                          |

#### Note:

# 2.5 10BASE-T Port Operation

# 2.5.1 10BASE-T Reception

Each LXT914 Repeater 10BASE-T port receiver acquires data packets from its twisted-pair input (TPDIP/TPDIN). An internal RC filter and an intelligent squelch function discriminate noise from link test pulses and valid data streams. The receive function is activated only by valid data streams (above the squelch level and with proper timing). If the differential signal at the DI circuit inputs falls below 75% of the threshold level (unsquelched) for eight bit times (typical), the port receiver enters the idle state.

The notation ABCDx means bit ABCD associated with port x, which can be any of the four Twisted-Pair Ports or the AUI Port.

#### 2.5.1.1 Programmable Internal Squelch Level

The 10BASE-T port receivers have two squelch levels: a normal level or default setting and a reduced level squelch (-4.5 dB) selected when the ERSQx is set in the Setup register. When used with Low noise media such as shielded twisted-pair cabling, the reduced squelch level allows longer loop lengths in the network.

### 2.5.1.2 Polarity Detection and Correction

The LXT914 Repeater 10BASE-T ports detect and correct for reversed polarity by monitoring link pulses and end-of-frame sequences. A reversed polarity condition is declared when the port receives sixteen or more incorrect link pulses consecutively, or four frames with reversed start-of-idle sequence. In these cases the receiver reverses the polarity of the signal and thereby corrects for this failure condition. If the port enters the link fail state and no valid data or link pulses are received within 96 to 128 ms, the polarity is reset to the default non-flipped condition. (If Link Integrity Testing is disabled, polarity detection is based only on received data.)

### 2.5.2 10BASE-T Transmission

Each LXT914 Repeater 10BASE-T port receives NRZ data from the repeater core and passes it through a Manchester encoder. The encoded data is then transmitted to the twisted-pair network (the DO circuit). The advanced integrated pulse shaping and filtering network produces the predistorted and pre-filtered output signal to meet the 10BASE-T jitter template. An internal continuous resistor-capacitor filter is used to remove any high-frequency clocking noise from the pulse shaping circuitry. Integrated filters simplify the design work required for FCC compliant EMI performance. During idle periods, the LXT914 Repeater 10BASE-T ports transmit link integrity test pulses in accordance with the 802.3 10BASE-T standard.

Data packets transmitted by the LXT914 Repeater contain a minimum of 56 preamble bits before the start of frame delimiter (SFD). In the Asynchronous mode, preamble regeneration takes place on the transmit side. In the Synchronous mode, the preamble is regenerated on the receive side and distributed via the IRB. If the total packet is less than 96 bits including the preamble, the LXT914 Repeater extends the packet length to 96 bits by appending a Jam signal (1010...) at the end.

# 2.5.3 10BASE-T Link Integrity Testing

The LXT914 Repeater fully supports the 10BASE-T Link Integrity test function. The link integrity test determines the status of the receive side twisted-pair cable. Link integrity testing is enabled unless disabled via the DISLIx bit in the Setup register. When enabled, the receiver recognizes link integrity pulses transmitted in the absence of data traffic. With no data packets or link integrity pulses within  $100 \, (\pm 50)$  ms, the port enters a link fail state and disables its transmitter. The port remains in the link fail state until it detects three or more data packets or link integrity pulses.

# 2.6 AUI Port Operation

# 2.6.1 AUI Reception

The LXT914 Repeater AUI port receiver acquires data packets from the network (AUIDIP/AUIDIN). Only valid data streams above the squelch level activate the receive function. If the differential signal at the DI circuit inputs falls below 75% of the threshold level (unsquelched) for 8 bit times (typical), the AUI receiver enters the idle state.

#### 2.6.2 AUI Transmission

The LXT914 Repeater AUI port receives NRZ data from the repeater core, and passes it through a Manchester encoder. The encoded data then goes out on the network (AUIDOP/AUIDON).

# 2.6.3 AUI Mode Selection (DTE/MAU)

The LXT914 Repeater allows the user to change the mode of the AUI from a DTE to a MAU interface. This option is available on both 68- and 100-pin versions except as follows:

- When using the LEDJM/AUISEL pin to select the AUI interface mode the following is true:

After reset the state of the LEDJM/AUISEL pin is sensed for the correct mode. The LEDJM/

AUISEL pin when floated or pulled Low will select the DTE interface and the LEDJM/

AUISEL output is still available. When the LEDJM/AUISEL pin is pulled High the MAU

interface is selected and the LEDJM/AUISEL function is unavailable.

- The 100-pin PQFP has an additional pin, AUISEL (pin 30). When using this pin to select the AUI interface mode the LEDJM/AUISEL pin is still a functional LED driver. The AUISEL pin is not latched after reset and is actively polled to determine which AUI interface mode is to be used. Refer to Table 13.

Table 13. AUI Mode Selection (DTE/MAU)

| App #                                                          | AUISEL<br>(PQFP only) | LEDJM/<br>AUISEL<br>(both pkgs) | AUI Mode | Available<br>LED<br>Modes |

|----------------------------------------------------------------|-----------------------|---------------------------------|----------|---------------------------|

| 1                                                              | Low                   | Low                             | DTE      | default, 0-3              |

| 2                                                              | Low                   | High                            | MAU      | 1-3                       |

| 3                                                              | High                  | Low                             | MAU      | default, 0-3              |

| 4 High                                                         |                       | High                            | MAU      | 1-3                       |

| Note: Application 3 is valid only when using the 100-pin PQFP. |                       |                                 |          |                           |

23

# 2.7 Collision Handling

A collision occurs when two or more repeater ports receive simultaneously, or when the AUI CIP/CIN signal is active. The LXT914 Repeater fully complies with the IEEE 802.3 collision specifications, both in individual and multi-repeater applications. In multiple-repeater configurations, collision signaling on the IRB allows all repeaters to share collision parameters, acting as a single large repeater.

$\overline{\text{IRCOL}}$  is a digital open-drain pin.  $\overline{\text{IRCFS}}$  is an analog/digital port. The  $\overline{\text{IRCOL}}$  and  $\overline{\text{IRCFS}}$  lines are pulled up globally (i.e., each signal requires one pull-up resistor for all boards). If there are eight 3-repeater boards in the system, all eight boards share a single pull-up resistor for  $\overline{\text{IRCOL}}$  and a single pull-up resistor for  $\overline{\text{IRCFS}}$ . The global pull-up may be located on one of the boards, or on the backplane. The  $\overline{\text{IRCFS}}$  line requires a precision ( $\pm$  1%) resistor.

The IRENA, IRDAT and IRDEN lines are each pulled up locally (one pull-up resistor per board) if external bus drivers are used. If no bus drivers are used then only one global pull-up per signal is used.

# 2.8 Security Mode

The LXT914 Repeater security mode is fully transparent to the user. In the External management mode, the security feature is available for all four TP ports and the AUI port. In the Local mode, security is available for the TP ports only (the SECAUI input is reassigned as FPS). The security inputs are normally held Low to disable the security feature. Any input can independently be pulled High to scramble the respective port for any given length of time. For applications which do not require security control, the SEC pins must be tied Low.

The security mode pins are real time response inputs. This allows the board designer to screen the destination address with an application specific device and (on match of the destination address) to assert the security input to jam the respective port for the given frame. This real time detection and jam assertion method provides the flexibility to implement customer specific solutions. The destination address decoding and security signal assertion functions can be integrated into the external management device.

# 2.9 LED Display

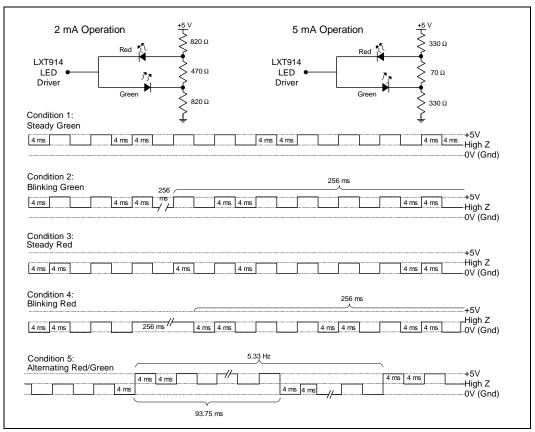

The LED display interface consists of seven integrated LED drivers, one for each of the five network ports and two for common functions. Each pin provides a three-state pulsed output (+5 V, high Z, and 0 V) which allows multiple conditions to be monitored and reported independently. Table 14 shows the LED Mode selected with each LEDM1 and LEDM0 combination. Figure 5 shows the LED Driver output conditions, and Table 15 through Table 18 list the repeater states associated with each of the five conditions.

**Note:** If LED mode 0 is selected and the LEDJM/AUISEL pin is High (which selects MAU Mode), the device defaults to LED Mode 1. LED Mode 0 is not available when LEDJM/AUISEL is pulled High.

#### Table 14. LED Mode Selection

|          | LEDM1 | LEDM0 |                      |

|----------|-------|-------|----------------------|

| PLCC pin | 35    | 17    | LED Mode<br>Selected |

| PQFP pin | 40    | 14    |                      |

|          | Low   | Low   | 0<br>Note 1          |

|          | Low   | High  | 1                    |

|          | High  | Low   | 2                    |

|          | High  | High  | 3                    |

#### Note:

LED Mode 0 (Default) This mode is selected when LEDM1 and LEDM0 are floating or pulled

Low. Refer to Table 15. This mode is not available when using the LEDJM/AUISEL pin to select a MAU interface in the AUI port. In this case,

the LED Mode defaults to Mode 1.

LED Mode 1 This mode is selected when LEDM1 is floating or pulled Low and LEDM0

is pulled High by a pull-up resistor. Refer to Table 16.

LED Mode 2 This mode is selected when LEDM1 is pulled High by a pull-up resistor

and LEDM0 is floating or pulled Low. Refer to Table 17.

**LED Mode 3.** This mode is selected when LEDM1 is pulled High by a pull-up resistor

and LEDM0 is also pulled High by a pull-up resistor. Refer to Table 18.

### Table 15. Mode 0 (Default) LED Truth Table

| Condition | LEDTP 1-4         | LEDAUI          | LEDCF      | LEDJM                               |

|-----------|-------------------|-----------------|------------|-------------------------------------|

| 1         | Rx Link Pulse     | N/A             | FIFO Error | Manchester Code Violation           |