# UNIDIRECTIONAL P-GATE THYRISTOR OVERVOLTAGE AND OVERCURRENT PROTECTOR

# TISP8250D Overvoltage and Overcurrent Protector

Telecommunication System 30 A 10/1000 Protector

## Ion-Implanted Breakdown Region

- Precise and Stable Voltage

| Device Name | V <sub>DRM</sub><br>V | V <sub>(BO)</sub><br>V |

|-------------|-----------------------|------------------------|

| TISP8250D   | 250                   | 340                    |

#### **Rated for International Surge Wave Shapes**

| Wave Shape | Standard      | I <sub>PPSM</sub><br>A |

|------------|---------------|------------------------|

| 2/10       | GR-1089-CORE  | 75                     |

| 0.5/700    | CNET I 31-24  | 40                     |

| 10/700     | ITU-T K.20/21 | 40                     |

| 10/1000    | GR-1089-CORE  | 30                     |

#### **Functional Replacement for TPP25011**

UL Recognized Component

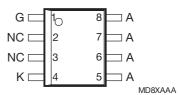

#### 8-SOIC Package (Top View)

NC - No internal connection

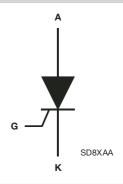

#### **Device Symbol**

# Description

The TISP8250D is a P-gate reverse-blocking thyristor (SCR) designed for the protection of telecommunications equipment against overvoltages and overcurrents on the telephone line caused by lightning, a.c. power contact and induction. The fixed voltage and current triggered modes make the TISP8250D particularly suitable for the protection of ungrounded customer premise equipment. Connected across the d.c. side of a telephone set polarity bridge, in fixed voltage mode these devices can protect the ringer in the on-hook condition. In an off-hook condition, either the fixed voltage or current triggered modes can protect the following telephone electronics.

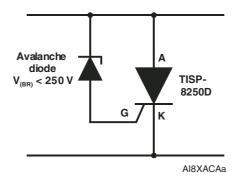

Without external gate activation, the TISP8250D is a fixed voltage protector. The maximum working voltage without clipping is 250 V and the protection voltage is 340 V. Lower values of protection voltage may be set by connecting an avalanche breakdown diode of less than 250 V between the TISP8250D gate and anode (see Figure 2.)

By connecting a small value resistor in series with the line conductor and connecting the TISP8250D gate cathode terminals in parallel with the resistor, conductor overcurrents can gate trigger the TISP8250D into conduction.

Overvoltages are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to crowbar into a low-voltage on state. Overcurrents develop sufficient voltage across the external gate-cathode resistor to trigger the device into a low-voltage on state. This low-voltage on state causes the current resulting from the overstress to be safely diverted through the device. The high crowbar holding current prevents d.c. latchup as the diverted current subsides.

### **How To Order**

| Device     | Package | Carrier              | For Standard<br>Termination Finish<br>Order As | For Lead Free<br>Termination Finish<br>Order As | Marking<br>Code | Standard<br>Quantity |

|------------|---------|----------------------|------------------------------------------------|-------------------------------------------------|-----------------|----------------------|

| TISP8250D  | 8-SOIC  | Embossed Tape Reeled | TISP8250DR                                     | TISP8250DR-S                                    | 9050            | 2500                 |

| 1101 02300 | 0 0010  | Tube                 | TISP8250D                                      | TISP8250D-S                                     | 8250            | 1500                 |

# TISP8250D Overvoltage and Overcurrent Protector **BOURNS**®

# Absolute Maximum Ratings, $T_A = 25$ °C (Unless Otherwise Noted)

| Rating                                                             | Symbol            | Value       | Unit |

|--------------------------------------------------------------------|-------------------|-------------|------|

| Repetitive peak off-state voltage (see Note 1)                     | $V_{DRM}$         | 250         | V    |

| Non-repetitive peak impulse current (see Notes 2, 3 and 4)         |                   |             |      |

| 2/10 μs (Telcordia GR-1089-CORE, 2/10 μs waveshape)                |                   | 75          | ł l  |

| 0.2/310 (CNET I 31-24, 0.5/700 μs waveshape)                       |                   | 40          | i    |

| 5/310 μs (ITU-T K.20/21, 10/700 μs voltage waveshape)              | I <sub>PPSM</sub> | 40          | Α    |

| 5/310 µs (FTZ R12, 10/700 µs voltage waveshape)                    |                   | 40          | i l  |

| 10/1000 μs (Telcordia GR-1089-CORE, 10/1000 μs voltage waveshape)  |                   | 30          |      |

| Non-repetitive peak on-state current, 50 Hz (see Notes 2, 3 and 4) |                   |             |      |

| 10 ms half sine wave                                               |                   | 5           | i l  |

| 1s rectified sine wave                                             | I <sub>TSM</sub>  | 3.5         | Α    |

| 1000 s rectified sine wave                                         |                   | 0.7         |      |

| Junction temperature                                               | T <sub>J</sub>    | -40 to +150 | °C   |

| Storage temperature range                                          | T <sub>stg</sub>  | -65 to +150 | °C   |

- NOTES: 1. For voltage values at lower temperatures, derate at 0.13 %/°C.

- 2. Initially the device must be in thermal equilibrium, with  $T_{J}$  = 25  $^{\circ}\text{C}.$

- 3. The surge may be repeated after the device returns to its initial condtions.

- 4. EIA/JESD51-2 environment and EIA/JESD51-3 PCB with standard footprint dimensions connected with 5 A printed wiring track widths. Derate current values at -0.61 %/°C for ambient temperatures above 25 °C.

# Electrical Characteristics, $T_A = 25$ °C (Unless Otherwise Noted)

| Parameter         |                                   | Test Conditions                                               |     | Тур | Max     | Unit |

|-------------------|-----------------------------------|---------------------------------------------------------------|-----|-----|---------|------|

| I <sub>DRM</sub>  | Repetitive peak off-state current | $V_D = V_{DRM}$ $T_A = 25  ^{\circ}C$ $T_A = 85  ^{\circ}C$   |     |     | 5<br>10 | μА   |

| V <sub>(BO)</sub> | Breakover voltage                 | $dv/dt = 250 \text{ V/ms}, R_{SOURCE} = 300 \Omega$           |     |     | 340     | V    |

| I <sub>(BO)</sub> | Breakover current                 | $dv/dt = 250 \text{ V/ms}, R_{SOURCE} = 300 \Omega$           | 15  |     | 200     | mA   |

| I <sub>H</sub>    | Holding current                   | $I_T = 5 \text{ A}, \text{ di/dt} = -30 \text{ mA/ms}$        | 180 |     |         | mA   |

| V <sub>GK</sub>   | Gate-cathode voltage              | I <sub>G</sub> = 30 mA                                        | 0.6 |     | 1.2     | V    |

| I <sub>GT</sub>   | Gate trigger current              | V <sub>AK</sub> = 100 V                                       |     |     | 40      | mA   |

| I <sub>D</sub>    | Off-state current                 | $V_{D} = 60 \text{ V}$                                        |     |     | 5       | μΑ   |

| C <sub>O</sub>    | Off-state capacitance             | $f = 1 \text{ MHz}, V_d = 1 \text{ V rms}, V_D = 5 \text{ V}$ |     |     | 100     | pF   |

# Thermal Characteristics, $T_A$ = 25 °C (Unless Otherwise Noted)

|                 | Parameter                              | Test Conditions                                      | Min | Тур | Max | Unit |

|-----------------|----------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| $R_{\theta JA}$ | Junction to ambient thermal resistance | EIA/JESD51-3 PCB, $I_T = I_{TSM(1000)}$ (see Note 5) |     |     | 170 | °C/W |

NOTE 5. EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5A rated printed wiring track widths.

# TISP8250D Overvoltage and Overcurrent Protector **BOURNS**®

#

Figure 1. Voltage-Current Characteristic for A and K Terminals All Measurements are Referenced to the K Terminal

PM8XAAA

Figure 2. Overvoltage Protection Circuit

Anode Negative Reverse Characteristic

## **Bourns Sales Offices**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

## **Technical Assistance**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

## www.bourns.com

Bourns® products are available through an extensive network of manufacturer's representatives, agents and distributors. To obtain technical applications assistance, a quotation, or to place an order, contact a Bourns representative in your area.

Reliable Electronic Solutions