# Short Haul Loop Dual PCM Codec-Filter/SLIC Chipset with GCI Interface

:

### **CONTENTS**

Section 1

| Ove        | rview                                             |            |

|------------|---------------------------------------------------|------------|

| 1.1<br>1.2 | Introduction: MC1420232 CODSP and MC1430132 SHLIC | 1-1<br>1-1 |

|            | tion 2<br>dications                               |            |

| 2.1        | Recommended External Components                   | 2-3        |

| 2.2        | Overvoltage Protection                            | 2-3        |

|            | tion 3<br>Descriptions                            |            |

| 3.1        | Device Pinouts                                    | 3-1        |

| 3.2        | MC1420232 Pin Descriptions                        | 3-2        |

| 3.3        | MC1430132 Pin Descriptions                        | 3-4        |

| 3.4        | Unused Pins                                       | 3-5        |

|            | 3.4.1 CODSP                                       | 3-5        |

|            | 3.4.2 SHLIC                                       | 3-5        |

| 3.5        | Note on Decoupling                                | 3-6        |

|            | 3.5.1 CODSP Decoupling                            | 3-6        |

| Section 4                         |                       |

|-----------------------------------|-----------------------|

| <b>Functional Characteristics</b> | of the SH-POTS System |

| 4.1 | On-Ho  | ok Conditions                | 4-1 |

|-----|--------|------------------------------|-----|

| 4.2 | Ringin | g Injection                  | 4-3 |

|     | 4.2.1  | Balanced Ringing             | 4-3 |

|     | 4.2.2  | Semi-Unbalanced Ringing      | 4-4 |

| 4.3 | DC Fee | ed Characteristics           | 4-4 |

|     | 4.3.1  | Battery Voltage and Reversal | 4-5 |

#### Contents

| 4.4  | AC Transmission Characteristics (MS140131KT System) | 4-6          |

|------|-----------------------------------------------------|--------------|

|      | 4.4.1 Transmit and Receive Filter Characteristics   | 4-6          |

|      | 4.4.2 Transmit and Receive Gain                     | 4-7          |

|      | 4.4.3 Source Impedance (Z <sub>CO</sub> )           | 4-7          |

|      | 4.4.4 Balance Impedance (Echo Canceller)            | 4-8          |

| 4.5  |                                                     | 4-8          |

|      | 4.5.1 Metering Injection                            | 4-8          |

|      | 4.5.2 Metering Characteristics                      | <b>1-1</b> 0 |

| 4.6  | Tone Generation                                     | <b>1-1</b> 0 |

| 4.7  | CODSP Clock Recovery PLL                            |              |

|      | 4.7.1 User-Defined I/O Pins                         | 1-14         |

|      | 4.7.2 Test Functions                                | l-14         |

|      | tion 5<br>etrical Characteristics                   |              |

| 5.1  | Absolute Maximum Ratings                            | 5-1          |

| 5.2  |                                                     | 5-1          |

| 5.3  |                                                     | 5-2          |

|      |                                                     | 5-2          |

| 5.4  |                                                     | 5-2          |

|      |                                                     | 5-3          |

|      |                                                     | 5-4          |

|      | 223 0                                               | 5-6          |

|      | , 1                                                 | 5-6          |

|      |                                                     | 5-7          |

|      | 1                                                   | 5-7          |

|      | 5.4.7 Characteristics for the Digital I/O Pins      | 5-8          |

|      |                                                     | 5-9          |

|      |                                                     | 5-9          |

| 5.5  | AC Characteristics (SHLIC)                          |              |

|      | 5.5.1 Receive Path                                  |              |

|      | 5.5.2 Transmit Path                                 |              |

|      | 5.5.3 Overpower and Short Circuit Protection        |              |

| 5.6  | Off-Hook Characteristics (MS140131KT System)        |              |

| Sec  | tion 6                                              |              |

| Deta | ailed Programming Description                       |              |

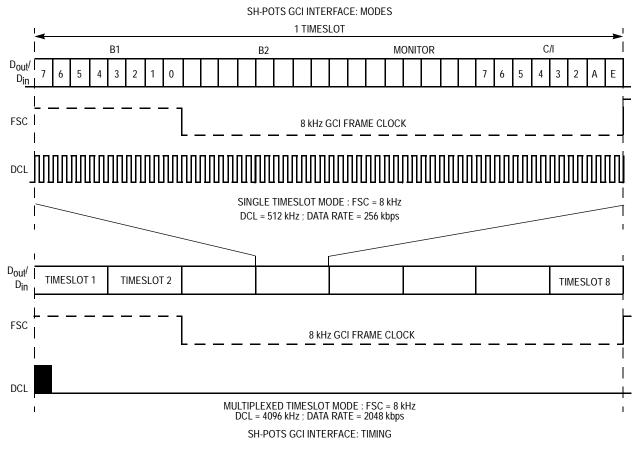

| 6.1  | GCI Interface                                       | 6-1          |

| 6.2  | Timeslot Address                                    | 6-2          |

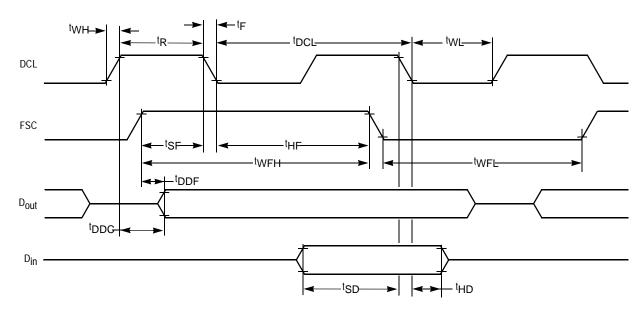

| 6.3  | SH-POTS GCI Interface: Timing                       | 6-3          |

| 6.4  | C/I Bits                                            | 6-4          |

| 6.5  | Monitor Channel                                     | 6-4          |

| 6.6  | ID Request6                                       | 5-4 |

|------|---------------------------------------------------|-----|

| 6.7  | Read Command                                      | 6-5 |

| 6.8  | Write Command6                                    | 6-5 |

| 6.9  | Memory Map of the CODSP6                          | 6-5 |

| 6.10 | Data RAM — MemID = 2                              | 6-6 |

| 6.11 | LBO Register                                      | 6-7 |

| 6.12 | Alarm Bits                                        | 5-8 |

| 6.13 | Meaning and Default Values of the Parameters      | 5-8 |

| 6.14 | Coprocessor Coefficient RAM — MemID = 4 6-        | -11 |

| 6.15 | Meaning and Default Values of the Parameters      | -12 |

| 6.16 | Shared Memory — MemID = 5                         | -14 |

| 6.17 | Meaning and Default Values of the Parameters      | ·14 |

|      | tion 7<br>hanical Specifications                  |     |

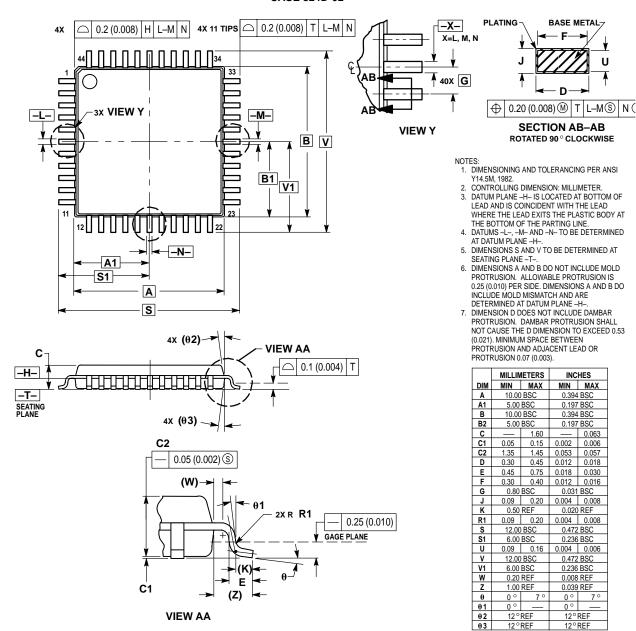

| 7.1  | MC1420232 Package Dimensions                      | 7-1 |

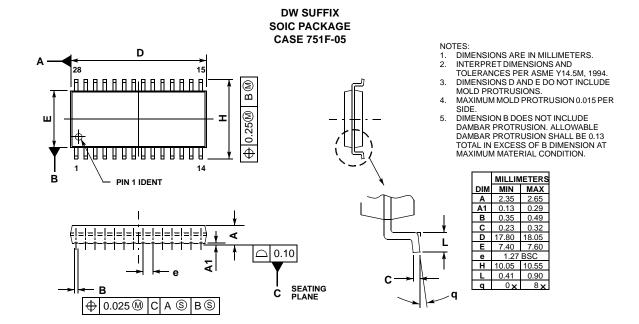

| 7.2  | MC1430132 Package Dimensions                      | 7-2 |

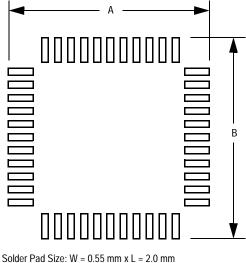

| 7.3  | Recommended Pad Layout for 44-Lead TQFP MC1420232 | 7-3 |

#### Contents

## **FIGURES**

| 1-1. | Block Diagram                                                                           | 1-2  |

|------|-----------------------------------------------------------------------------------------|------|

| 2-1. | Typical SH-POTS Application                                                             | 2-1  |

| 2-2. | Application Schematic for Two Analog Lines                                              | 2-2  |

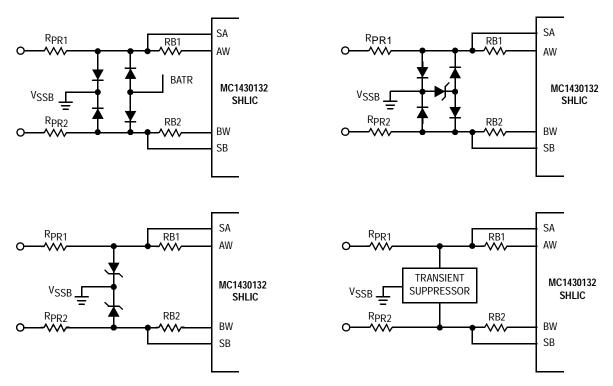

| 2-3. | Recommended Overvoltage Protection Options                                              | 2-4  |

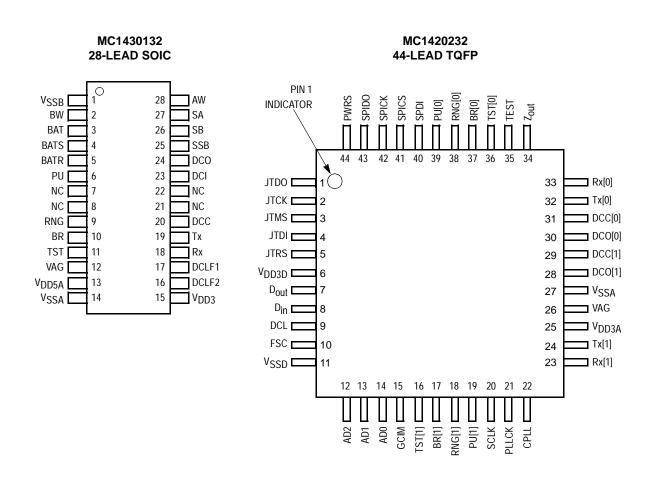

| 3-1. | Pin Assignments                                                                         | 3-1  |

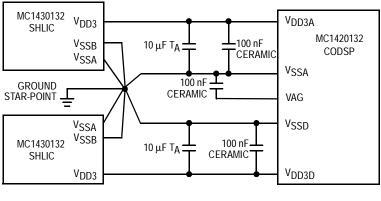

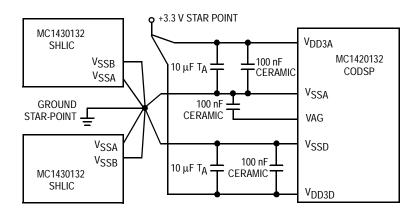

| 3-2. | MC1420232 CODSP Recommended Power-Supply Decoupling Arrangements                        | 3-7  |

| 4-1. | SH-POTS Line Voltages — Example                                                         | 4-1  |

| 4-2. | Nominal Hookswitch Detection Thresholds (Default Values)                                | 4-2  |

| 4-3. | Application Suggestion for Semi-Unbalanced Ringing Injection                            | 4-4  |

| 4-4. | DC Feed Characteristics                                                                 | 4-5  |

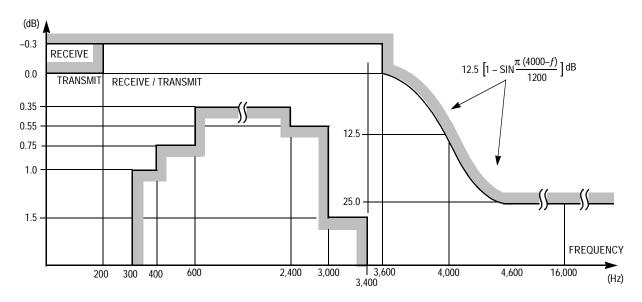

| 4-5. | Transmit and Receive Frequency Response (Default)                                       | 4-6  |

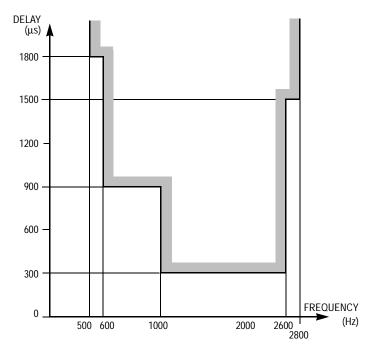

| 4-6. | Relative Group Delay, Transmit and Receive Paths (Digital-to-Digital) Referred to 1 kHz | 4-7  |

| 4-7. | Three-Element Z <sub>CO</sub> Model                                                     | 4-8  |

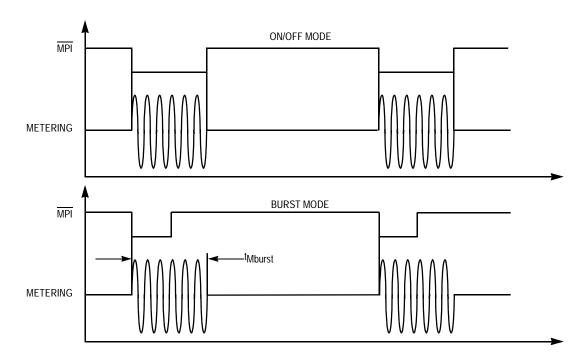

| 4-8. | Metering Pulse Timing Diagrams                                                          | 4-9  |

| 5-1. | Block Diagram Showing Gains in Various Signal Paths in SHLIC                            | 5-10 |

| 5-2. | Short Circuit Protection                                                                | 5-12 |

| 6-1. | GCI Data Exchange                                                                       | 6-1  |

| 6-2. | GCI Timing Diagram                                                                      | 6-3  |

| 7-1. | Recommended Pad Layout for 44-Lead TQFP MC1420232                                       | 7-3  |

### **TABLES**

| 2-1.  | Recommended External Components                                                                                            | 2-3  |

|-------|----------------------------------------------------------------------------------------------------------------------------|------|

| 3-1.  | Pin Descriptions for MC1420232 CODSP                                                                                       | 3-2  |

| 3-2.  | Pin Descriptions for MC1430132 SHLIC                                                                                       | 3-4  |

| 3-3.  | MC1420232 CODSP Unused Pin Connections                                                                                     | 3-5  |

| 3-4.  | MC1430132 SHLIC Unused Pin Connections                                                                                     | 3-6  |

| 4-1.  | On-Hook Characteristics                                                                                                    | 4-2  |

| 4-2.  | Ringing Characteristics                                                                                                    | 4-3  |

| 4-3.  | DC Feed Characteristics [ $R_{feed} = 60 \Omega \text{ Total } (50 \Omega + 10 \Omega \text{ Protection}) \times 2] \dots$ | 4-5  |

| 4-4.  | Examples of Z <sub>CO</sub> Coefficients                                                                                   | 4-8  |

| 4-5.  | Metering Characteristics (Determined by MC1420232 CODSP)                                                                   | 4-10 |

| 4-6.  | Tone Signal Levels (Common Values)                                                                                         | 4-11 |

| 4-7.  | Tone Generator Division Values for Common Frequencies from ETS-300-001 and DTMF Tones                                      | 4-12 |

| 4-8.  | Required Frequency Setting Values (N) for a Melody Generator (Western Equal-Tempered Scale)                                | 4-13 |

| 5-1.  | Absolute Maximum Ratings                                                                                                   |      |

| 5-2.  | Operating Conditions                                                                                                       | 5-2  |

| 5-3.  | Power Supply Currents                                                                                                      | 5-3  |

| 5-4.  | SHLIC Dissipation                                                                                                          | 5-3  |

| 5-5.  | Power-On Reset Characteristics                                                                                             | 5-4  |

| 5-6.  | V <sub>DD3</sub> Regulator Characteristics                                                                                 | 5-4  |

| 5-7.  | Voltage Characteristics A Wire (AW), B Wire (BW)                                                                           | 5-5  |

| 5-8.  | Impedance Characteristics A Wire (AW), B Wire (BW)                                                                         | 5-5  |

| 5-9.  | Rx, Tx Characteristics                                                                                                     | 5-6  |

| 5-10. | DCO Characteristics                                                                                                        | 5-6  |

| 5-11. | VAG Characteristics                                                                                                        | 5-6  |

| 5-12. | DC Loop Filter Characteristics                                                                                             | 5-7  |

| 5-13. | DCC Input Characteristics                                                                                                  | 5-7  |

| 5-14. | Digital I/O Characteristics                                                                                                | 5-8  |

| 5-15. | Sense Bridge Inputs Characteristics                                                                                        | 5-8  |

| 5-16. | Test Switch Characteristics                                                                                                | 5-9  |

|       | Ringing Battery Switch Characteristics                                                                                     |      |

| 5-18. | Typical Gains                                                                                                              |      |

| 5-19. |                                                                                                                            |      |

| 5-20. | Off-Hook Characteristics (MS140131KT System)                                                                               |      |

| 6-1.  | GCI Mode and Timeslot Address Programming                                                                                  | 6-2  |

| 6-2.  | GCI Interface: Timing Characteristics.                                                                                     |      |

| 6-3.  | C/I Bit Allocation                                                                                                         |      |

| 6-4.  | Memory Map for CODSP                                                                                                       |      |

| 6-5.  | Data RAM: Memory Map                                                                                                       | 6-6  |

#### **Tables**

| 6-6.  | LBO Register Description                                         |

|-------|------------------------------------------------------------------|

| 6-7.  | Data RAM: Description and Default Values                         |

| 6-8.  | Coprocessor Coefficient RAM: Memory Map                          |

| 6-9.  | Coprocessor Coefficient RAM: Description and Default Values 6-12 |

| 6-10. | Shared Memory: Memory Map                                        |

| 6-11. | Shared Memory: Description and Default Values                    |

**Tables**

## SECTION 1 OVERVIEW

## 1.1 INTRODUCTION: MC1420232 CODSP AND MC1430132 SHLIC

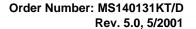

The MS140131KT chipset provides all the functions necessary to connect analog telephone sets or other analog terminals (telefax, answering machines, modems, etc.) into digital communication systems. It provides an economical solution for the traditional "BORS(C)HT" [Battery, Overvoltage, Ringing, Supervision, (Codec), Hybrid, Test] functions found in central-office exchanges, but is optimized for short-range communication [e.g., up to 500 m with 5 RENs (Ringer Equivalence Number) attached]. Virtually all system-dependent parameters can be set under software control, giving an unprecedented flexibility to the system integrator, as well as optimizing the system cost. The digital interface to the SH-POTS (Short Haul, Plain Old Telephone System) chipset uses the industry-standard GCI interface<sup>1</sup>. The system architecture has been designed to offer the most cost-effective solution for short haul systems, yet offers the full flexibility required to meet worldwide analog telephony standards. The MS140131KT chipset is also suitable for Q.552 applications.

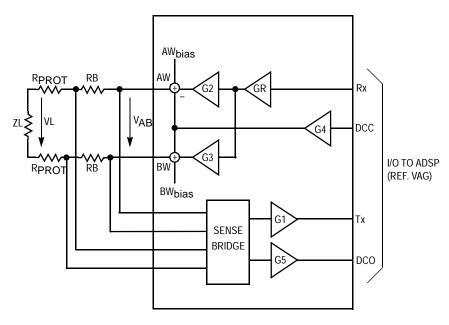

The MS140131KT chipset comprises three devices (see Figure 1-1): a pair of high-voltage devices, the Short Haul Line Interface Circuit (SHLIC) which provides the signal and power interface to the analog lines (one per line), and a low-voltage CMOS, DSP-based dual codec/control device (CODSP) which provides all signal processing and control functions for up to two lines.

#### 1.2 KEY FEATURES

- Digitally Programmable Transmission and Signalling Characteristics Meet Worldwide Specification Requirements

- Integrated Ringing: Sine or Trapezoid with Auto Cadence

- Metering Injection (12 or 16 kHz)

- Support On-Hook Transmission: ADSI, CLIP

- Battery Reversal

- Codec and AC Parameters ( $Z_{CO}$  and Hybrid) are Fully Programmable (A-Law or  $\mu$ -Law)

- Tone Generators for Signalling and Testing

- Loop Current Control and Monitoring are Programmable

<sup>1.</sup> The General Circuit Interface (GCI) is an interface specification developed jointly by Alcatel, Italtel, GPT, and Siemens, March 1989, Issue 1.0.

#### : Key Features

- Minimal External Components

- Codec and SLIC Functions for Two Lines

- Low-Cost POTS Interface for Short Range

- Standard GCI Interface with Timeslot Assigner

- Test Support (Test Load Switch, Loopback, Tone Generators)

- Supports up to -72 V on  $V_{BAT}$  Ring and -35 V on  $V_{BAT}$  Speech

- CODSP (Dual Codec) is 3.3 V with 5 V Tolerant Input for Low Power Consumption

Figure 1-1. Block Diagram

## SECTION 2 APPLICATIONS

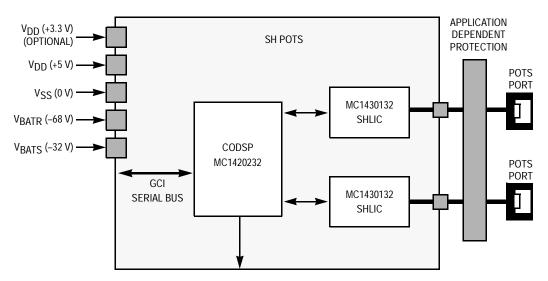

Figure 2-1 shows a typical SH-POTS application using Motorola semiconductor chip solutions. The short haul dual PCM chipset provides all necessary functions to connect analog telephone sets or fax terminals to digital communications systems.

- Advanced ISDN NT (NTplus), Smart NT1 Personal Router

- Analog/Digital PABX

- Cable Telephone Systems (Set-Top Box)

- Remote Telephone Access Systems

- Fiber to the Curb

- Radio in the Loop

- Internet Telephones

Figure 2-1. Typical SH-POTS Application

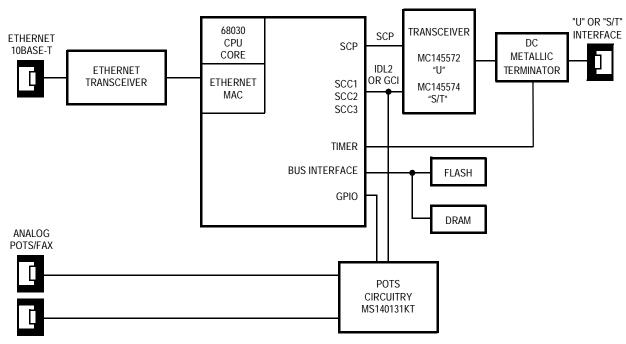

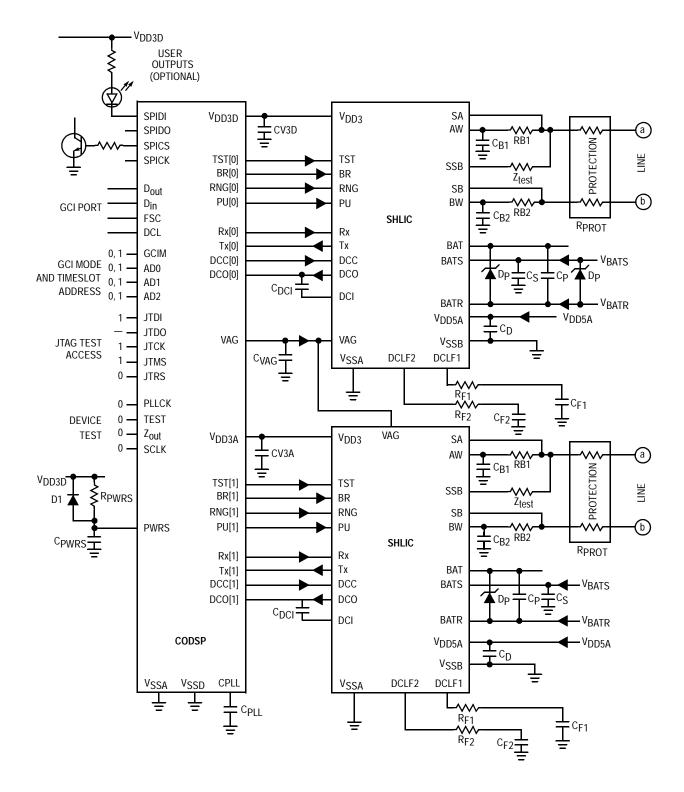

Figure 2-2. Application Schematic for Two Analog Lines

## 2.1 RECOMMENDED EXTERNAL COMPONENTS

**Table 2-1.** Recommended External Components

| Component                         | Function                          | x              | Comment                                        |

|-----------------------------------|-----------------------------------|----------------|------------------------------------------------|

| R <sub>B1</sub> , R <sub>B2</sub> | Feed resistor                     | 50 Ω           | 1/4 W ±1% (see Note 1)                         |

| R <sub>PROT</sub>                 | Protection resistance             | 2 x 10 Ω       |                                                |

| Z <sub>test</sub>                 | Test resistor                     | 510 Ω          | 1/4 W, optional                                |

| R <sub>F1</sub> , R <sub>F2</sub> | DC bias filter                    | 10 kΩ          |                                                |

| C <sub>B1</sub> , C <sub>B2</sub> | No-load stabilization             | 1 nF           | 100 V (see Note 2)                             |

| C <sub>DCI</sub>                  | DC feed separation                | 330 nF         | 5%                                             |

| C <sub>F1</sub> , C <sub>F2</sub> | DC bias filter                    | 470 nF         | 100 V, 10%                                     |

| C <sub>VAG</sub>                  | Analog ground decoupling          | 100 nF         |                                                |

| CV3A                              | Analog 3.3 V regulator decoupling | 10 μF + 100 nF |                                                |

| CV3D                              | Digital 3.3 V decoupling          | 10 μF + 100 nF |                                                |

| CS                                | Battery supply decoupling         | 100 nF         | 100 V                                          |

| C <sub>PLL</sub>                  | PLL loop filter                   | 4.7 nF         |                                                |

| C <sub>PWRS</sub>                 | Power-on reset delay              | 100 nF         |                                                |

| R <sub>PWS</sub>                  | Power-on reset delay              | 100 kΩ         |                                                |

| D <sub>1</sub>                    | Power loss reset                  | _              | Any small signal diode                         |

| D <sub>P</sub>                    | Battery input protection          | _              | BAT46 required depending on the power supplies |

| C <sub>D</sub>                    | 5 V power supply decoupling       | 100 nF         |                                                |

**NOTES: 1.** A ±1% results in a maximum longitudinal balance of 40 dB. For higher values, more precise matching is required (e.g., ±0.1% for 46 dB).

#### 2.2 OVERVOLTAGE PROTECTION

There are several recommended overvoltage protection options. The application will determine the most appropriate one to chose (e.g., in-house only systems with minimal protection requirements, or systems with loops outside a protected environment requiring more extended protection).

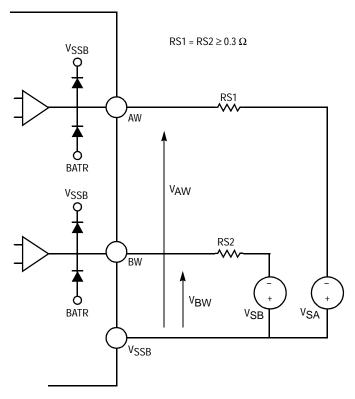

The first external protection network to protect the line circuit against foreign voltages consist of resistors  $R_{PR1}$  and  $R_{PR2}$  and an overvoltage protection component (see Figure 2-3). Series resistors  $R_{PR1}$  and  $R_{PR2}$  can be PTC, poly-switch, or fusible components.

For further protection, the simplest and cheapest solution is a diode bridge between SA, SB and V<sub>SSB</sub>, BATR, respectively. The diodes must be able to allow current peaks more than 20 A.

In case the battery BATR can not accept these high current peaks, add a voltage clamping component to  $V_{SS}$ , or a transient suppressor between each line and  $V_{SS}$ . The clamp voltage or protection voltage minimum must always be larger than the maximum used ringing battery BATR.

MS140131KT

<sup>2.</sup> Capacitors are generally not required. They are foreseen to stabilize the line driver outputs when active but driving no load (test condition only).

The protection components must be dimensioned in such a way that the transient energy on the chip pins AW, BW does not exceed 1 mJoule (or, the energy on-chip because of one lightning pulse).

Figure 2-3. Recommended Overvoltage Protection Options

## SECTION 3 PIN DESCRIPTIONS

#### 3.1 DEVICE PINOUTS

Figure 3-1. Pin Assignments

## 3.2 MC1420232 PIN DESCRIPTIONS

Table 3-1. Pin Descriptions for MC1420232 CODSP

| Pin Name          | Pin No. | Pin Description                                           | Type<br>(See Note) |

|-------------------|---------|-----------------------------------------------------------|--------------------|

| JTDO              | 1       | JTAG test port data out                                   | DO                 |

| JTCK              | 2       | JTAG test port clock                                      | Dlu                |

| JTMS              | 3       | JTAG test port mode select                                | Dlu                |

| JTDI              | 4       | JTAG test port data in                                    | Dlu                |

| JTRS              | 5       | JTAG test port reset                                      | Dlu                |

| V <sub>DD3D</sub> | 6       | Digital section supply voltage                            | Р                  |

| D <sub>out</sub>  | 7       | GCI port upstream data                                    | DO5                |

| D <sub>in</sub>   | 8       | GCI port downstream data                                  | DI5                |

| DCL               | 9       | GCI port data clock                                       | DI5                |

| FSC               | 10      | GCI port frame clock                                      | DI5                |

| V <sub>SSD</sub>  | 11      | Digital ground (0 V)                                      | Р                  |

| AD2               | 12      | GCI port timeslot select, MSB                             | DI                 |

| AD1               | 13      | GCI port timeslot select                                  | DI                 |

| AD0               | 14      | GCI port timeslot select, LSB                             | DI                 |

| GCIM              | 15      | GCI port operating mode (0 = 1 timeslot, 1 = 8 timeslots) | DIs                |

| TST[1]            | 16      | SHLIC 1 test select                                       | DO                 |

| BR[1]             | 17      | SHLIC 1 bat reverse control                               | DO                 |

| RNG[1] 18 SH      |         | SHLIC 1 ring control                                      | DO                 |

| PU[1]             | 19      | SHLIC 1 power-up control                                  | DB                 |

| SCLK              | 20      | System clock (test only)                                  | DI                 |

| PLLCK             | 21      | PLL clock (test only)                                     | Dls                |

| CPLL              | 22      | PLL loop filter capacitor                                 | AO                 |

| Rx[1]             | 23      | SHLIC 1 Rx analog signal                                  | AO                 |

| Tx[1]             | 24      | SHLIC 1 Tx analog signal                                  | Al                 |

| V <sub>DD3A</sub> | 25      | Analog supply voltage                                     | Р                  |

| VAG               | 26      | Analog ground reference voltage output                    | AO                 |

| V <sub>SSA</sub>  | 27      | Analog ground (0 V)                                       | Р                  |

| DCO[1]            | 28      | SHLIC 1 DC loop output                                    | Al                 |

| DCC[1]            | 29      | SHLIC 1 DC loop control                                   | AO                 |

| DCO[0]            | 30      | SHLIC 0 DC loop output                                    | Al                 |

| DCC[0]            | 31      | SHLIC 0 DC loop control                                   | AO                 |

| Tx[0]             | 32      | SHLIC 0 Tx analog signal                                  | Al                 |

Table 3-1. Pin Descriptions for MC1420232 CODSP (continued)

| Pin Name         | Pin No. | Pin Description                       | Type<br>(See Note) |

|------------------|---------|---------------------------------------|--------------------|

| Rx[0]            | 33      | SHLIC 0 Rx analog signal              | AO                 |

| Z <sub>out</sub> | 34      | Digital I/O drive control (test only) | DB                 |

| TEST             | 35      | Test mode select (test only)          | Dld                |

| TST[0]           | 36      | SHLIC 0 test select                   | DO                 |

| BR[0]            | 37      | SHLIC 0 bat reverse control           | DO                 |

| RNG[0]           | 38      | SHLIC 0 ring control                  | DO                 |

| PU[0]            | 39      | SHLIC 0 power-up control              | DB                 |

| SPIDI            | 40      | SPI port data in (user I/O)           | DB                 |

| SPICS            | 41      | SPI port chip-select (user I/O)       | DB                 |

| SPICK            | 42      | SPI port clock (user I/O)             | DB                 |

| SPIDO            | 43      | SPI port data out (user I/O)          | DB                 |

| PWRS             | 44      | Reset input                           | DIs                |

**NOTE:** The first letter differentiates between:

D: Digital

A: Analog

P: Power

The second letter differentiates between:

I: Input

O: Output

B: Bidirectional

The third letter differentiates between:

d: Pin with internal pull-down

u: Pin with internal pull-up

s: Pin with Schmitt-trigger input

5: 5 V compatible input

NC: No connect

### 3.3 MC1430132 PIN DESCRIPTIONS

Table 3-2. Pin Descriptions for MC1430132 SHLIC

| Pin Name           | Pin No. | Pin Description                          | Туре |

|--------------------|---------|------------------------------------------|------|

| V <sub>SSB</sub>   | 1       | Battery ground (0 V)                     | Р    |

| BW                 | 2       | B wire output                            | AB   |

| BAT                | 3       | Battery voltage (output, do not connect) | Р    |

| BATS               | 4       | Battery voltage input, SPEECH mode       | Р    |

| BATR               | 5       | Battery voltage input, RING mode         | Р    |

| PU                 | 6       | Power-up control                         | DI   |

| NC                 | 7       | Do not connect; thermal conduction pin   | NC   |

| NC                 | 8       | Do not connect; thermal conduction pin   | NC   |

| RNG                | 9       | Ring mode control                        | DI   |

| BR                 | 10      | Battery reverse control                  | DI   |

| TST                | 11      | Test mode control                        | DI   |

| VAG                | 12      | Analog ground reference input            | Р    |

| V <sub>DD5</sub> A | 13      | Analog supply voltage                    | Р    |

| VSSA               | 14      | Analog ground, 0 V                       | Р    |

| V <sub>DD3</sub>   | 15      | 3 V regulator output                     | Р    |

| DCLF2              | 16      | DC bias filter capacitor 2               | AO   |

| DCLF1              | 17      | DC bias filter capacitor 1               | AO   |

| Rx                 | 18      | Analog receive signal                    | AO   |

| Tx                 | 19      | Analog transmit signal                   | AI   |

| DCC                | 20      | DC loop control input                    | DI   |

| NC                 | 21      | Do not connect; thermal conduction pin   | NC   |

| NC                 | 22      | Do not connect; thermal conduction pin   | NC   |

| DCI                | 23      | DC loop control separation filter input  | Al   |

| DCO                | 24      | DC loop control output                   | AO   |

| SSB                | 25      | Loop test resistor switch                | Al   |

| SB                 | 26      | B wire sense input                       | Al   |

| SA                 | 27      | A wire sense input                       | Al   |

| AW                 | 28      | A wire output                            | AB   |

**NOTES: 1.** A ±1% results in a maximum longitudinal balance of 40 dB. For higher values, more precise matching is required (e.g., ±0.1% for 46 dB).

3-4 MS140131KT (A) MOTOROLA

**<sup>2.</sup>** Capacitors are generally not required. They are foreseen to stabilize the line driver outputs when active but driving no load (test condition only).

#### 3.4 UNUSED PINS

#### 3.4.1 **CODSP**

Table 3-3 lists the pins on the CODSP that are not connected. Pins that are not used in the application should be connected as described here. Failure to do so could result in excessive sensitivity to RFI or other erratic behavior. A 0 or 1 indicates that the pin should be connected to ground or to the device's digital supply. A "—" indicates that the pin is an output and must be left unconnected.

**Table 3-3.** MC1420232 CODSP Unused Pin Connections

| Pin Name         | Pin No. | Connect To                 |

|------------------|---------|----------------------------|

| SPDO             | 43      | _                          |

| GCIM             | 15      | 0, 1 (GCI mode select)     |

| AD0              | 14      | 0, 1 (GCI timeslot select) |

| AD1              | 13      | 0, 1 (GCI timeslot select) |

| AD2              | 12      | 0, 1 (GCI timeslot select) |

| JTDI             | 4       | 1 (V <sub>DD3D</sub> )     |

| JTDO             | 1       | _                          |

| JTCK             | 2       | 1 (V <sub>DD3D</sub> )     |

| JTMS             | 3       | 1 (V <sub>DD3D</sub> )     |

| JTRS             | 5       | 0 (V <sub>SS</sub> )       |

| SCLK             | 20      | V <sub>SS</sub>            |

| PLLCK            | 21      | V <sub>SS</sub>            |

| Z <sub>out</sub> | 34      | V <sub>SS</sub>            |

| TEST             | 35      | V <sub>SS</sub>            |

#### 3.4.2 SHLIC

Table 3-4 lists the pins on the SHLIC that are not connected. The NC pins (7, 8, 21, and 22) are connected to the device substrate, which is at a voltage equal to the  $V_{BATR}$  supply pin, and may optionally be electrically connected to this pin.

The BAT pin is the internal supply to the line drivers, and adopts the voltage of  $V_{BATR}$  or  $V_{BATS}$ , plus the voltage drop across the internal switch, depending on the operating mode. In low-voltage only systems (very short connections), the BAT pins,  $V_{BATR}$  and  $V_{BATS}$ , may all be connected together and a single supply (e.g., -27~V) may be used for both ringing and speech modes. (In this mode, the voltage drop of the internal switches is avoided.)

**Table 3-4.** MC1430132 SHLIC Unused Pin Connections

| Pin Name | Pin No. | Connect To                   |

|----------|---------|------------------------------|

| BAT      | 3       | No connect or see text above |

| NC       | 7       | No connect or see text above |

| NC       | 8       | No connect or see text above |

| NC       | 21      | No connect or see text above |

| NC       | 22      | No connect or see text above |

#### 3.5 NOTE ON DECOUPLING

As in any system, the PCB layout and supply decoupling can influence the system performance, particularly with respect to noise.

#### 3.5.1 CODSP Decoupling

- It is recommended to connect V<sub>DD3D</sub> and V<sub>DD3A</sub> (digital and analog supply pins) in a star configuration from the supply (either from the SHLIC or from an external supply), and each pin be independently decoupled using 10 μF in parallel with 100 nF.

- In two-line systems, using the SHLIC regulator to supply only the CODSP (i.e., no other use is made of the regulator), one SHLIC may be used to provide  $V_{DD3D}$  power and the other  $V_{DD3A}$ , thus giving improved decoupling between analog and digital supplies. See Figure 3-2.

- The VAG line (analog signal reference) must always be properly decoupled using 100 nF, placed as close as possible to the CODSP device.

#### 3.5.2 SHLIC Decoupling

The SHLIC should use separate 100 nF decoupling capacitors between V<sub>DD5A</sub> and V<sub>SSB</sub>, and V<sub>DD5A</sub> and V<sub>SSA</sub>. When the on-board regulator of the SHLIC is not used, no capacitor is required at the V<sub>DD3</sub> pin.

(M) MOTOROLA

(a) Arrangement A

(b) Arrangement B

**Figure 3-2.** MC1420232 CODSP Recommended Power-Supply Decoupling Arrangements

MS140131KT

3-7

# SECTION 4 FUNCTIONAL CHARACTERISTICS OF THE SH-POTS SYSTEM

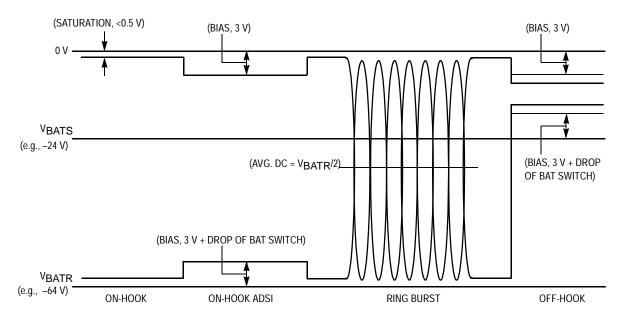

For reference, Figure 4-1 shows the typical voltages on tip and ring during various stages of operation. For detailed electrical parameters, refer to Section 5.

Figure 4-1. SH-POTS Line Voltages — Example

#### 4.1 ON-HOOK CONDITIONS

When a line is not in use (on-hook), the designer may select either the speech battery or the ringing battery as the supply to the line drivers. In the on-hook mode, most of the internal circuits are put into a low-power operating mode to minimize supply currents. The A and B wire outputs are effectively connected to the supply voltage, thus applying this voltage (minus a small saturation voltage) to the line. The output is current-limited in this mode, thus protecting against short circuits and limiting any inrush current when a set goes off-hook. If the SHLIC detects a current in excess of a (programmable) limit, the off-hook

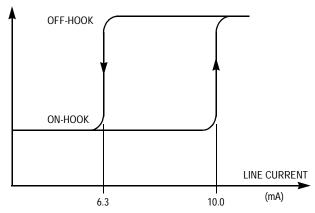

condition will be detected (an on-chip debouncer with selectable delay avoids accidental hookswitch detection), and the circuit will be put into active speech mode. The nominal off-hook detection currents and hysteresis are shown in Figure 4-2. When a line is in the on-hook condition, the system designer may select, under program control via the GCI bus, an "on-hook active mode," whereby, on-hook signalling (ADSI, CLIP, etc.) can be performed in either direction (though battery reversal is not available in this mode).

The hookswitch detector has a programmable debounce timer. Times of 8, 16, 24, or 64 ms can be selected. (The timer is common for both channels.)

**Figure 4-2.** Nominal Hookswitch Detection Thresholds (Default Values)

Table 4-1. On-Hook Characteristics

| Parameter                                  | Condition                                                            | Min                 | Max                 | Unit | Note |

|--------------------------------------------|----------------------------------------------------------------------|---------------------|---------------------|------|------|

| V <sub>feed</sub> O                        | Open-line feed voltage                                               | V <sub>BATS-1</sub> | V <sub>BATR-1</sub> | V    | 1    |

| I <sub>on</sub>                            | Line current guaranteeing on-hook state                              | 4.67                | 7.93                | mA   | 2    |

| l <sub>off</sub>                           | Line current guaranteeing off-hook state                             | 7.86                | 12.14               | mA   | 2    |

| IOHYST                                     | Hookswitch detect hysteresis                                         | 2                   | _                   | mA   | 2    |

| loc                                        | Peak over-current limit, on-hook mode                                | _                   | 145                 | mA   | 3    |

| V <sub>bias</sub> H<br>V <sub>bias</sub> L | Bias voltage during ADSI mode on A (H) and B (L) wires, ref. BAT pin | 2                   | 4                   | V    |      |

- NOTES: 1. I<sub>line</sub> = 0 mA, independent of battery reversal mode. This voltage is selected by the user. The output impedance when in the on-hook condition is set by the sense resistors R<sub>feed</sub>. The hook-switch detector has a programmable debounce timer. Times of 8, 16, 24, or 64 ms can be selected (common for both channels).

- 2. These are the default values after reset. The on-hook and off-hook thresholds can be individually programmed in the range 0 to 63 mA nominal.

- 3. This is the intrinsic current limit of the output driver. This current can only be seen during on-hook to off-hook transients, or during ringing into a short-circuit load during the ring-trip delay period. The actual value measured will depend on the load resistance used.

MOTOROLA

#### 4.2 RINGING INJECTION

#### 4.2.1 Balanced Ringing

The SH-POTS chipset is capable of directly injecting a ringing signal of up to 50 Vrms (sine wave) without the need for additional external components. The technique of "balanced ringing" is used, which allows this large voltage swing to remain within the technology limits of the SHLIC device. (Balanced ringing requires a specific algorithm for ring-trip detection, which is also implemented by the chipset.) The SH-POTS chipset allows the user to program a dc offset during ringing as well as a reduced amplitude ringing signal, should the application require this. Ringing waveform, frequency, amplitude, and cadence, as well as ring-trip thresholds, are controlled by the CODSP device, and are all programmable. Ringing cadence can be automatic, with independently programmable ring and pause times, or ringing can be controlled directly via the GCI bus. In the automatic cadence mode, ringing bursts on both channels can be optionally interleaved, if simultaneously active, to avoid peaks in current from the ringing battery supply.

**Parameter** Condition Min Max Unit Note  $F_R$ Ringing frequency Hz 16.66, 20, 25 Hz -1 1 50 Hz -2 2 Single-frequency noise, 10 Hz to 4 kHz -63dBm SFNR Ringing voltage (max), VBATR = -72 V 1  $V_{R}$ Vrms 50 Ringing distortion, sine mode 30 Hz to 132 kHz 5 %  $D_{R}$ Ring-trip delay, load =  $500 \Omega + 4 \mu F$ 150 ms **tRTD** Ring-trip debounce time 0 30 ms 2 <sup>t</sup>RTDEB Ring-cadence times (active and silent) 1 255 n/n 4 tC Ring-trip current, high threshold 6.0 12.0 mΑ 3 **IRTH** 3.5 3 **IRTL** Ring-trip current, low threshold 9.5 mΑ HRT Ring-trip hysteresis 2 mΑ

Table 4-2. Ringing Characteristics

**NOTES: 1.** Ringing voltage is user-programmable from 0 to 70 Vp(diff) between the A and B wires (NB, the ringing battery voltage must be large enough to encompass this voltage) in 256 steps. The default is the maximum value. Condition: Load = 0 mA.

- 2. User-selectable 0 or 30 ms. Default is 30 ms.

- 3. These are the default values after reset. The max and min ring-trip thresholds can be individually programmed in the range 0 to 63 mA nominal. The ring-trip detect mask time is used to bridge the zero-crossings of the ringing signal, and is programmable between 0 and 32 ms in 125  $\mu$ s steps.

- **4.** Units are periods of the selected ringing frequency. The default values are 1 s on, 3 s off, with a ringing frequency of 50 Hz.

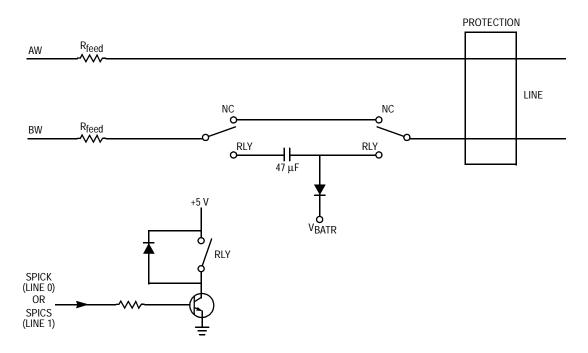

### 4.2.2 Semi-Unbalanced Ringing

In order to support "semi-unbalanced ringing" (dc bias equal to  $V_{BATR}$  superimposed on the differential ringing signal), two of these outputs will be active high during the active ringing period on each channel (SPICK for channel 0 and SPICS for channel 1). This can be used to drive a relay via an external NPN transistor, as shown in Figure 4-3.

4-3

Figure 4-3. Application Suggestion for Semi-Unbalanced Ringing Injection

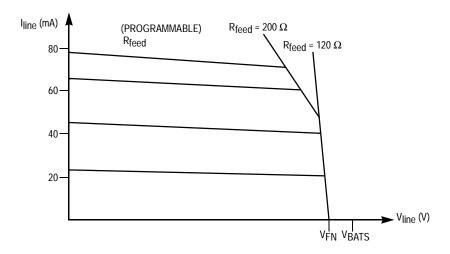

#### 4.3 DC FEED CHARACTERISTICS

As shown in Figure 4-4, the SH-POTS chipset implements a constant-current feed. The limit current and the residual resistance (slope of the characteristic) are both programmable by the user. The dc characteristic falls into three regions. When the combination of line and subset result in a current less than the programmed limit current, the system behaves like a battery with a fixed feed resistance of 120  $\Omega$ , and a voltage equivalent to the speech supply voltage (V<sub>BATS</sub>) minus the bias voltage on both lines (6 V nominal in total). Should line conditions permit a current that exceeds the programmed limit current, the system enters the constant-current feed mode described above. In order to protect the output stage in the transition region at higher line currents (in excess of 50 mA), a third region is defined, where the system synthesizes a fixed feed resistance of 200  $\Omega$ . The slope of the voltage/current characteristic in the constant-current mode can be user-programmed to select the effective feed-resistance.

#### **NOTE**

The SHLIC device includes over-temperature protection, that activates at 165°C in case of overheating of the device.

(M) MOTOROLA

Figure 4-4. DC Feed Characteristics

**Table 4-3.** DC Feed Characteristics [R<sub>feed</sub> =  $60 \Omega$  Total ( $50 \Omega + 10 \Omega$  Protection) x 2]

| Parameter             | Condition                                                    | Min        | Max | Unit |

|-----------------------|--------------------------------------------------------------|------------|-----|------|

| V <sub>bias</sub> H   | Bias voltage, A wire (I <sub>line</sub> = 0)                 | 2.5        | 3.5 | V    |

| V <sub>biasL</sub>    | Bias voltage, B wire (I <sub>line</sub> = 0)                 | 2.5        | 3.5 | V    |

| TOL <sub>ICL</sub>    | Current limit tolerance                                      | <b>–15</b> | 15  | %    |

| T <sub>Rfeed</sub> CL | TRfeedCL Tolerance on programmed Rfeed when in current-limit |            | 15  | %    |

| ICL                   | Current-limit, useful programmed range                       | 20         | 70  | mA   |

#### 4.3.1 Battery Voltage and Reversal

The open-line voltage (i.e., the voltage seen on the line when on-hook) is user-selectable for each channel via an internal register. It can be either the ringing battery supply (most common use) or the speech battery supply. The speech battery supply is automatically selected when an off-hook condition is detected, independently of these control bits. The selected supply voltage is maintained when the on-hook signalling function (ADSI) is enabled.

The polarity of the line feed can be dynamically controlled by the user. In the "normal" condition, the A wire is the most positive. Thus, reversal makes the B wire the most positive. Battery reversal is fast (audible), is controlled by programming an internal register, and is independent for both channels. The selected polarity is used in all states (on-hook, off-hook, ringing, etc.) except for on-hook signalling, which is in normal battery mode.

## 4.4 AC TRANSMISSION CHARACTERISTICS (MS140131KT SYSTEM)

#### 4.4.1 Transmit and Receive Filter Characteristics

The SH-POTS chipset implements transmit and receive filters according to ITU-T (G.712). These filters can be reprogrammed by the user for specific requirements. Please contact a Motorola sales office for more information. The implemented default filter characteristics are shown in Figures 4-5 and 4-6.

Figure 4-5. Transmit and Receive Frequency Response (Default)

(M) MOTOROLA

**Figure 4-6.** Relative Group Delay, Transmit and Receive Paths (Digital-to-Digital) Referred to 1 kHz

#### 4.4.2 Transmit and Receive Gain

Transmit (from analog subset towards the switching system) and receive gains are user-programmable, independently for both lines. The default values are 0 dBr in the transmit direction, and -7 dBr in the receive direction.

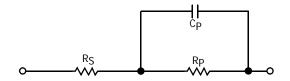

### 4.4.3 Source Impedance (Z<sub>CO</sub>)

The central-office impedance,  $Z_{CO}$ , is synthesized using digital signal processing techniques. This renders it very stable, and moreover, programmable by the user by means of coefficients which are loaded via the GCI. Real or complex  $Z_{CO}$  impedances can be synthesized using the common three-element model (Rs, Rp, Cp; see Figure 4-7). The  $Z_{CO}$  setting is common for both lines. Both real and complex  $Z_{CO}$  impedances can be programmed to address the local requirements of specifications worldwide, and cover the following range.

Using the default coefficient values, the return loss when measured against 600  $\Omega$  (using 0 dBm input signal level) is better than 20 dB in the 300 to 3400 Hz band, and better than 10 dB at 10 kHz.

Real impedances:  $600 \Omega$  to  $900 \Omega$ .

Complex impedances: Rs from 160  $\Omega$  to 500  $\Omega$

Rp from 300  $\Omega$  to 1000  $\Omega$

Rp//Cp pole from 725 Hz to 5 kHz.

MS140131KT 4-7

Figure 4-7. Three-Element Z<sub>CO</sub> Model

#### 4.4.4 Balance Impedance (Echo Canceller)

The balance impedance (model of the line plus set impedance used to separate the receive and transmit signals in the "hybrid") is independently programmable (though is the same for both channels). Default values offer echo return loss of better than 20 dB, though optimization to specific line and set characteristics may yield further improvement.

|                     | Rs  | Rp  | Ср     | Z <sub>CO</sub> Sh<br>Alfa3 | Z <sub>CO</sub> A2 | RZCO | Z <sub>CO</sub> -<br>Gamma | Z <sub>CO</sub> -<br>Alfa3 | Ftx | Ар  | Nan  | ACG |

|---------------------|-----|-----|--------|-----------------------------|--------------------|------|----------------------------|----------------------------|-----|-----|------|-----|

| Belgium             | 600 | 0   | 0      | 0                           | 0                  | 3    | 0                          | 0                          | 237 | 0   | 0    | 103 |

| Germany             | 220 | 820 | 115 nF | 0                           | 40                 | 9    | 9                          | 5                          | 52  | 346 | 512  | 125 |

| Europe              | 270 | 750 | 150 nF | 0                           | 19                 | 7    | 15                         | 4                          | 122 | 388 | -179 | 125 |

| Z <sub>CO</sub> 850 | 850 | 0   | 0      | 0                           | 0                  | 0    | 0                          | 0                          | 282 | 0   | 0    | 123 |

| Z <sub>CO</sub> 900 | 900 | 0   | 0      | 0                           | 0                  | 0    | 0                          | 0                          | 290 | 0   | 0    | 126 |

**Table 4-4.** Examples of Z<sub>CO</sub> Coefficients

|                     | h0  | h1  | h2  | h3  | a0 | с5 | b0 | Dzd0 | Dzd1 |

|---------------------|-----|-----|-----|-----|----|----|----|------|------|

| Belgium             | 4   | -22 | 105 | 95  | 0  | 0  | 0  | 1    | 1    |

| Germany             | -31 | 48  | 1   | 156 | 0  | 0  | 0  | 0    | 0    |

| Europe              | 3   | -23 | 118 | 88  | 0  | 0  | 0  | 0    | 0    |

| Z <sub>CO</sub> 850 | 4   | -22 | 105 | 95  | 0  | 0  | 0  | 1    | 1    |

| Z <sub>CO</sub> 900 | 4   | -22 | 105 | 95  | 0  | 0  | 0  | 1    | 1    |

### 4.5 METERING

#### 4.5.1 Metering Injection

Metering pulses of selectable frequency (12 kHz or 16 kHz) and programmable amplitude can be injected into either analog channel independently. The width of the injected pulse is determined by the user (on/off mode), or by an internal timer (burst mode) which can be set by the user from 2 ms to 510 ms in steps of 2 ms. The metering signal is always a multiple of half metering periods. See Figure 4-8.

Metering is initiated on a channel by an active low state on the corresponding MPI bit in the GCI C/I byte.

MOTOROLA

Figure 4-8. Metering Pulse Timing Diagrams

The metering level on the line is set by:  $V_{LM} = (V_{GEN} Z_M)/(Z_M + Z_{COM})$  where:

$V_{LM}$  = metering pulse level on the line

$V_{GEN}$  = set level of the metering generator

$Z_{M}$  = impedance of the metering load

$Z_{COM}$  = CO impedance at the metering frequency.

The metering level  $V_{GEN}$  is selectable from 0 to a maximum level of 230 mVrms (500 m line with  $Z_{CO}$  = 900  $\Omega$ ) in 15 linear steps. The internal tolerance on the metering signal level is  $\pm 10\%$ .

**MS140131KT** 4-9

#### 4.5.2 Metering Characteristics

**Table 4-5.** Metering Characteristics (Determined by MC1420232 CODSP) (Conditions: Refer to Section 5.2)

| Parameter         | Condition                                                                                          | Min         | Max               | Unit  | Note |

|-------------------|----------------------------------------------------------------------------------------------------|-------------|-------------------|-------|------|

| FML               | Metering frequency, 12 kHz                                                                         | 11,940      | 12,060            | Hz    | 1    |

| FMH               | Metering frequency, 16 kHz                                                                         | 25,920      | 16,080            | Hz    | 1    |

| SFN1              | Single-frequency noise, subharmonics<br>for 12 kHz, 30 Hz to 12 kHz<br>for 16 kHz, 30 Hz to 12 kHz |             | -69<br>-69        | dBm0  |      |

| SFN2              | Single-frequency noise, mixed products 12 kHz, 12 kHz to 20 kHz 12 kHz, 20 kHz to 132 kHz 16 kHz   | _<br>_<br>_ | –51<br>–69<br>–69 | dBm0  |      |

| N <sub>MC</sub>   | In-band noise due to metering signal                                                               | _           | -60               | dBmp  | 2    |

| NMT               | Transient noise due to metering pulse                                                              | _           | -35               | dBm0  | 2    |

| THD <sub>M</sub>  | Metering total harmonic distortion, 30 Hz to 132 kHz, out of CODSP                                 | _           | 0.5               | %     |      |

| D <sub>M</sub>    | Metering signal distortion at load                                                                 | _           | 5                 | %     | 3    |

| V <sub>LM</sub>   | Metering pulse amplitude, maximum level with $Z_{CO}$ = 900 $\Omega$ , $R_{line}$ = 130 $\Omega$   | 207         | 253               | mVrms | 4    |

| SYMM              | Metering symmetry, A and B wires                                                                   | 24          |                   | dB    | 5    |

| SFN <sub>TX</sub> | Single frequency noise, mixed products, 10 Hz to 4 kHz, Tx path                                    | _           | -63               | dBm   |      |

**NOTES: 1.** Tolerance =  $\pm 0.5\%$ .

- 2. Measured in accordance to ITU-T Specification 071 (Blue Book).

- **3.** On 200  $\Omega$ .

- 4. Tolerance =  $\pm 10\%$ .

- 5. Tolerance = max 6%.

#### 4.6 TONE GENERATION

The SH-POTS system allows the injection of user programmable tones, independently per channel, for signalling or user test purposes. Per channel, a tone comprising two programmable (sine wave) frequencies and programmable amplitudes can be generated (in this way, the most common call-progress and information tones, melody notes, or DTMF tones can be synthesized). The tone signal is added to the speech signal (the user must be aware of possible clipping which may occur if high signal levels are programmed), or the speech signal can also be muted during a tone burst. The tone burst duration is under user control only (the control bits for mute and tone insertion occupy the same register, which simplifies the generation of tone bursts).

The amplitude of each frequency within the tone can be independently set from 0 to the maximum level in 256 linear amplitude steps (8-bit value), with n=63 corresponding to 0 dBm on the line. From this, the line signal level,  $V_{TL}$ , for a given gain factor n is given by:

$V_{TL} = 20 \log(n/63)$  in dBm

MOTOROLA

or

$$n = int(63 \times 10^{\circ}(Vtl/20) + 0.5)$$

Table 4-6 lists values for n, for a range of tone signal levels.

The tone frequency is given by:

Fout =

$$250 \times N / 256 Hz$$

,

where N is a 16-bit value (thus, N = 1024 yields a tone of 1 kHz) or

$$N = int(Fout \times 256/250 + 0.5)$$

The tone generated has continuous phase if the programmed frequency is changed during the course of a tone (this is not so if the generator is stopped and restarted). Tables 4-7 and 4-8 list the values of N required to generate commonly occurring frequencies, and the resulting error.

**Table 4-6.** Tone Signal Levels (Common Values) (See Note)

| dBm  | n  | Actual | Error (dB) |

|------|----|--------|------------|

| 3    | 89 | 3.00   | 0.00       |

| 1.5  | 75 | 1.51   | 0.01       |

| 0    | 63 | 0.00   | 0.00       |

| -1.5 | 53 | -1.50  | 0.00       |

| -3   | 45 | -2.92  | 0.08       |

| -6   | 32 | -5.88  | 0.12       |

| -8   | 25 | -8.03  | -0.03      |

| -10  | 20 | -9.97  | 0.03       |

| -15  | 11 | -15.16 | -0.16      |

| -20  | 6  | -20.42 | -0.42      |

| -30  | 2  | -29.97 | 0.03       |

| -36  | 1  | -35.99 | 0.01       |

**NOTE:** It is possible to generate tones of very high amplitude. The user must ensure that the amplitude parameter is programmed before the tone is enabled.

**Table 4-7.** Tone Generator Division Values for Common Frequencies from ETS-300-001 and DTMF Tones

| Common Signalling Frequencies |      |                  |           |  |  |  |  |

|-------------------------------|------|------------------|-----------|--|--|--|--|

| Frequency (Hz)                | N    | Actual Frequency | Error (%) |  |  |  |  |

| 300.00                        | 307  | 299.805          | -0.07     |  |  |  |  |

| 320.00                        | 328  | 320.313          | 0.10      |  |  |  |  |

| 325.00                        | 333  | 325.195          | 0.06      |  |  |  |  |

| 340.00                        | 348  | 339.844          | -0.05     |  |  |  |  |

| 350.00                        | 358  | 349.609          | -0.11     |  |  |  |  |

| 375.00                        | 384  | 375.000          | 0.00      |  |  |  |  |

| 380.00                        | 389  | 379.883          | -0.03     |  |  |  |  |

| 382.50                        | 392  | 382.813          | 0.08      |  |  |  |  |

| 400.00                        | 410  | 400.391          | 0.10      |  |  |  |  |

| 410.00                        | 420  | 410.156          | 0.04      |  |  |  |  |

| 420.00                        | 430  | 419.922          | -0.02     |  |  |  |  |

| 440.00                        | 451  | 440.430          | 0.10      |  |  |  |  |

| 450.00                        | 461  | 450.195          | 0.04      |  |  |  |  |

| 455.00                        | 466  | 455.078          | 0.02      |  |  |  |  |

| 475.00                        | 486  | 474.609          | -0.08     |  |  |  |  |

| 490.00                        | 502  | 490.234          | 0.05      |  |  |  |  |

| 500.00                        | 512  | 500.000          | 0.00      |  |  |  |  |

| 525.00                        | 538  | 525.391          | 0.07      |  |  |  |  |

| 550.00                        | 563  | 549.805          | -0.04     |  |  |  |  |

|                               | DTMF | Tones            |           |  |  |  |  |

| Frequency (Hz)                | N    | Actual Frequency | Error (%) |  |  |  |  |

| 697.00                        | 714  | 697.266          | 0.04      |  |  |  |  |

| 770.00                        | 788  | 769.531          | -0.06     |  |  |  |  |

| 852.00                        | 872  | 851.563          | -0.05     |  |  |  |  |

| 941.00                        | 964  | 941.406          | 0.04      |  |  |  |  |

| 1209.00                       | 1238 | 1208.984         | 0.00      |  |  |  |  |

| 1336.00                       | 1368 | 1335.938         | 0.00      |  |  |  |  |

| 1477.00                       | 1512 | 1476.563         | -0.03     |  |  |  |  |

| 1633.00                       | 1672 | 1632.813         | -0.01     |  |  |  |  |

(M) MOTOROLA

**Table 4-8.** Required Frequency Setting Values (N) for a Melody Generator (Western Equal-Tempered Scale)

| Octave | Note | Frequency<br>(Hz) | N    | Actual   | Error<br>(%) |            |

|--------|------|-------------------|------|----------|--------------|------------|

| 2      | С    | 261.626           | 268  | 261.719  | 0.04         | (Middle-C) |

| 2      | C#   | 277.183           | 284  | 277.344  | 0.06         | (          |

| 2      | D    | 293.665           | 301  | 293.945  | 0.10         |            |

| 2      | Eb   | 311.127           | 319  | 311.523  | 0.13         |            |

| 2      | Е    | 329.628           | 338  | 330.078  | 0.14         |            |

| 2      | F    | 349.228           | 358  | 349.609  | 0.11         |            |

| 2      | F#   | 369.994           | 379  | 370.117  | 0.03         |            |

| 2      | G    | 391.995           | 401  | 391.602  | -0.10        |            |

| 2      | Ab   | 415.305           | 425  | 415.039  | -0.06        |            |

| 2      | Α    | 440.000           | 451  | 440.430  | 0.10         |            |

| 2      | Bb   | 466.164           | 477  | 465.820  | -0.07        |            |

| 2      | В    | 493.883           | 506  | 494.141  | 0.05         |            |

| 3      | С    | 523.251           | 536  | 523.438  | 0.04         |            |

| 3      | C#   | 554.365           | 568  | 554.688  | 0.06         |            |

| 3      | D    | 587.330           | 601  | 586.914  | -0.07        |            |

| 3      | Eb   | 622.254           | 637  | 622.070  | -0.03        |            |

| 3      | Е    | 659.255           | 675  | 659.180  | -0.01        |            |

| 3      | F    | 698.456           | 715  | 698.242  | -0.03        |            |

| 3      | F#   | 739.989           | 758  | 740.234  | 0.03         |            |

| 3      | G    | 783.991           | 803  | 784.180  | 0.02         |            |

| 3      | Ab   | 830.609           | 851  | 831.055  | 0.05         |            |

| 3      | Α    | 880.000           | 901  | 879.883  | -0.01        |            |

| 3      | Bb   | 932.328           | 955  | 932.617  | 0.03         |            |

| 3      | В    | 987.767           | 1011 | 987.305  | -0.05        |            |

| 4      | С    | 1046.502          | 1072 | 1046.875 | 0.04         |            |

| 4      | C#   | 1108.731          | 1135 | 1108.398 | -0.03        |            |

| 4      | D    | 1174.659          | 1203 | 1174.805 | 0.01         |            |

| 4      | Eb   | 1244.508          | 1274 | 1244.141 | -0.03        |            |

| 4      | Е    | 1318.510          | 1350 | 1318.359 | -0.01        |            |

| 4      | F    | 1396.913          | 1430 | 1396.484 | -0.03        |            |

| 4      | F#   | 1479.978          | 1515 | 1479.492 | -0.03        |            |

| 4      | G    | 1567.982          | 1606 | 1568.359 | 0.02         |            |

| 4      | Ab   | 1661.219          | 1701 | 1661.133 | -0.01        |            |

| 4      | Α    | 1760.000          | 1802 | 1759.766 | -0.01        |            |

| 4      | Bb   | 1864.655          | 1909 | 1864.258 | -0.02        |            |

| 4      | В    | 1975.533          | 2023 | 1975.586 | 0.00         |            |

| 5      | С    | 2093.005          | 2143 | 2092.773 | -0.01        |            |

| 5      | C#   | 2217.461          | 2271 | 2217.773 | 0.01         |            |

| 5      | D    | 2349.318          | 2406 | 2349.609 | 0.01         |            |

| 5      | Eb   | 2489.016          | 2549 | 2489.258 | 0.01         |            |

**Table 4-8.** Required Frequency Setting Values (N) for a Melody Generator (Western Equal-Tempered Scale) (continued)

| Octave | Note | Frequency<br>(Hz) | N    | Actual   | Error<br>(%) |  |

|--------|------|-------------------|------|----------|--------------|--|

| 5      | Е    | 2637.020          | 2700 | 2636.719 | -0.01        |  |

| 5      | F    | 2793.826          | 2861 | 2793.945 | 0.00         |  |

| 5      | F#   | 2959.955          | 3031 | 2959.961 | 0.00         |  |

| 5      | G    | 3135.963          | 3211 | 3135.742 | -0.01        |  |

| 5      | Ab   | 3322.438          | 3402 | 3322.266 | -0.01        |  |

| 5      | А    | 3520.000          | 3604 | 3519.531 | -0.01        |  |

| 5      | Bb   | 3729.310          | 3819 | 3729.492 | 0.00         |  |

| 5      | В    | 3951.066          | 4046 | 3951.172 | 0.00         |  |

#### 4.7 CODSP CLOCK RECOVERY PLL

The CODSP device derives its internal clocks from the GCI DCL input by means of a PLL. The PLL automatically detects the clock mode in use, and sets the multiplication factor accordingly. The PLL loop filter requires an external capacitor as shown in the application schematic.

#### 4.7.1 User-Defined I/O Pins

The SPIDI, SPICS, and SPICK pins are part of an SPI port which is used by the manufacturer during product evaluation and testing. They are available to the user, via the GCI, as output bits (e.g., for driving small indicator LEDs). The SPIDO pin is used as part of the power-up and testing routines, and the behavior during power-up can not be guaranteed. It is, therefore, advised not to make use of this pin for any other purpose. The outputs can source or sink a maximum of 4 mA each.

#### 4.7.2 Test Functions

Please contact a Motorola sales office.

# SECTION 5 ELECTRICAL CHARACTERISTICS

#### 5.1 ABSOLUTE MAXIMUM RATINGS

Operation of the device at or near these conditions is not guaranteed. Sustained exposure to these limits will adversely affect device reliability.

**Table 5-1.** Absolute Maximum Ratings

| Parameter                                                          | Symbol            | Min                   | Max                    | Unit |

|--------------------------------------------------------------------|-------------------|-----------------------|------------------------|------|

| Battery voltage BATR (ref. to V <sub>SSB</sub> ) of SHLIC          | BATR              | -75                   | 0.5                    | V    |

| Battery voltage BATS (ref. to V <sub>SSB</sub> ) of SHLIC          | BATS              | -35                   | 0.5                    | V    |

| Difference between the batteries BATR and BATS, BATR-BATS of SHLIC | DBAT              | -40                   | 0.5                    | V    |

| V <sub>DD5A</sub> (ref. to V <sub>SSA</sub> ) of SHLIC             | V <sub>DD5A</sub> | -0.5                  | 7                      | V    |

| V <sub>SSB</sub> (ref. to V <sub>SSA</sub> ) of SHLIC              | VSSB              | -0.5                  | 0.5                    | V    |

| Ambient temperature under bias of SHLIC                            | TA                | -40                   | 85                     | °C   |

| Maximum absolute power dissipation, T <sub>A</sub> = 85°C          |                   | _                     | 1.3                    | W    |

| V <sub>DD3A</sub> ,V <sub>DD3D</sub> to CODSP                      | V <sub>DD3</sub>  | V <sub>SS</sub> - 0.3 | 4                      | V    |

| Voltage on any device pin (see Note) of CODSP                      | V <sub>in</sub>   | V <sub>SS</sub> - 0.3 | V <sub>DD3</sub> + 0.3 | V    |

| Function temperature under bias of CODSP                           |                   | -55                   | 150                    | °C   |

| Storage temperature                                                | T <sub>stg</sub>  | -65                   | 150                    | °C   |

| Lead temperature (soldering 10 s)                                  |                   | _                     | 300                    | °C   |

**NOTE:** Except special 5 V tolerant I/Os of CODSP.

#### 5.2 OPERATING CONDITIONS

Operating ranges define the limits for functional operation and parametric characteristics of the device as described in this document, and for the reliability specifications. Correct functioning outside of these limits is not implied. Total cumulative exposure outside the normal power supply voltage range or ambient temperature under bias, must be less than 0.1% of the normal useful life as defined in the Reliability section.

Table 5-2. Operating Conditions

(All Voltages Referenced to V<sub>SSA</sub> = V<sub>SSB</sub> or V<sub>SS</sub> = V<sub>SSA</sub>, as Appropriate)

|                                        |                                                           |                 | Limits          |       |              |

|----------------------------------------|-----------------------------------------------------------|-----------------|-----------------|-------|--------------|

| Symbol                                 | Parameter                                                 | Min             | Тур             | Max   | Unit         |

| BATR                                   | Ringing battery voltage                                   | <del>-</del> 72 | <del>-</del> 65 | -18   | V            |

| BATS                                   | Speech battery voltage                                    | -35             | -32             | -18   | V            |

| D <sub>BAT</sub>                       | Difference between the batteries BATR and BATS, BATR-BATS | -40             | -35             | 0     | V            |

| V <sub>DD5A</sub>                      | Supply voltage SHLIC (ref. to V <sub>SSA</sub> )          | 4.75            | 5               | 5.5   | V            |

| T <sub>range</sub>                     | Operating temperature range                               | -40             | _               | 85    | °C<br>(Note) |

| V <sub>DD3D</sub><br>V <sub>DD3A</sub> | V <sub>DD</sub> of CODSP (3.3 V ±8%)                      | 3.036           | 3.3             | 3.564 | V            |

**NOTE:** See Section 5.4; maximum power dissipation is dependent on maximum ambient temperature.

#### 5.3 THERMAL SHUTDOWN SHLIC

Thermal limiting circuitry on chip of the SHLIC will shut down the circuit at a junction temperature of about 165°C. The device should never be run at this temperature. Operation above 145°C junction temperature might degrade device reliability.

Thermal resistance =  $55^{\circ}$ C/w typ.

5-2

#### 5.3.1 Transient Energy Capability

During testing, each device termination withstands being shorted to the supply voltages or ground as specified below. The shorting must be limited to 1 s.

Shorted to  $V_{SSA}$ ,  $V_{DD5A}$  or  $V_{SSB}$ : VAG, PU, RNG, BR, TST,  $T_A$ , DCC, DCO, DCI, Tx to Rx

Shorted to V<sub>SSA</sub>, V<sub>SSB</sub> or BATS: AW, BW, SA to SB

# 5.4 DC CHARACTERISTICS (MC1430132 SHLIC, UNLESS OTHERWISE NOTED)

Unless otherwise stated, these characteristics apply for the operating conditions specified in Section 5.2. All parameters are explicitly or implicitly tested during production at the operating conditions unless they are marked with an asterisk (\*), where they are guaranteed by design. Parameters marked with a double asterisk (\*\*) are meant as user information only. Tests are performed using an equivalent of the application schematic.

MS140131KT (A) MOTOROLA

Table 5-3. Power Supply Currents

|                  |                                                     |                         |     | Limits                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |

|------------------|-----------------------------------------------------|-------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| Symbol           | Parameter                                           | Test Condition          | Min | Тур                                                                                                                                                                                                                                                                                                                                                                                                           | Max | Unit |

| IBATR            | BATR current (IL = 0)                               | Power RNG = 0           | _   | 0.35                                                                                                                                                                                                                                                                                                                                                                                                          | 0.5 | mA   |

|                  |                                                     | Up RNG = 1              | _   | 3.5                                                                                                                                                                                                                                                                                                                                                                                                           | 5.0 | mA   |

|                  |                                                     | Power RNG = 0           | _   | 0.35                                                                                                                                                                                                                                                                                                                                                                                                          | 0.5 | mA   |

|                  |                                                     | Down RNG = 1            | _   | Typ         Max         Un           0.35         0.5         m/s           3.5         5.0         m/s           0.35         0.5         m/s           2.5         3.5         m/s           3.5         5         m/s           1.5         2.5         m/s           -         0.5         m/s           2.5         4         m/s           -         30         m/s           -         140         m/s | mA  |      |

| IBATS            | BATS current (IL = 0)                               | Power RNG = 0           | _   | 3.5                                                                                                                                                                                                                                                                                                                                                                                                           | 5   | mA   |

|                  |                                                     | Up RNG = 1              | _   | 3.5                                                                                                                                                                                                                                                                                                                                                                                                           | 5   | mA   |

|                  |                                                     | Power RNG = 0           | _   | 1.5                                                                                                                                                                                                                                                                                                                                                                                                           | 2.5 | mA   |

|                  |                                                     | Down RNG = 1            | _   | _                                                                                                                                                                                                                                                                                                                                                                                                             | 0.5 | mA   |

| I <sub>VDD</sub> | V <sub>DD</sub> current (I <sub>V3</sub> = 0)       | Power-up                | _   | 3                                                                                                                                                                                                                                                                                                                                                                                                             | 5.5 | mA   |

|                  |                                                     | Power-down              | _   | 2.5                                                                                                                                                                                                                                                                                                                                                                                                           | 4   | mA   |

| Pcc              | Power dissipation of CODSP                          | Power-down              | _   | _                                                                                                                                                                                                                                                                                                                                                                                                             | 30  | mW   |