# M/XI/M **Dual 1.25Gbps Transceiver**

## **General Description**

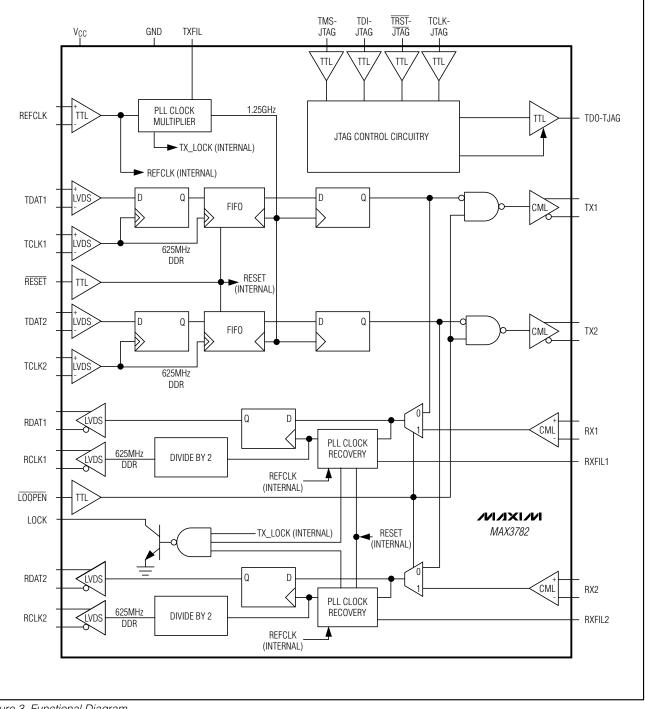

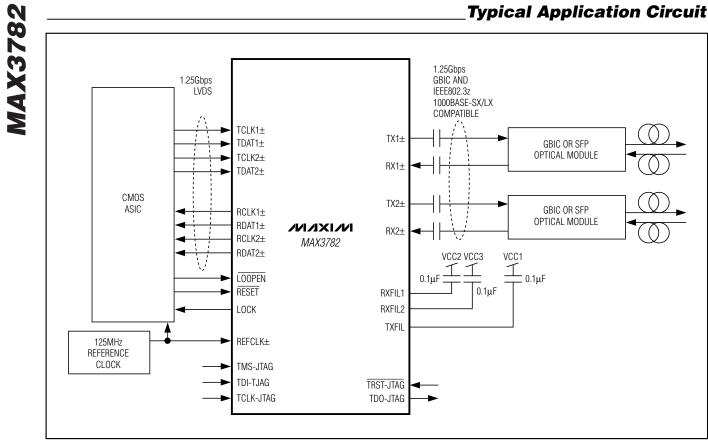

The MAX3782 is a dual 1.25Gbps data retiming and clock recovery transceiver. It interfaces 1.25Gbps LVDS data and clock to a 1.25Gbps serial interface compatible with 1000Base-SX/LX (IEEE 802.3z-2000) standards, GBIC, and small form-factor pluggable (SFP) module interface recommendations. The serial differential transmitter and receiver are PECL compatible using an ACcoupled CML interface with on-chip termination/bias resistors for superior forward and back terminations. The transmit path converts the LVDS signaling to CML and retimes the serial data to a low-jitter reference clock. The transmitter section contains LVDS buffers, FIFO, clock multiplier, and CML output buffers. The transmitter accepts a single 1.25Gbps serial-data channel and a 625MHz double-data-rate (DDR) clock that are compatible with IEEE Std 1596-1996 DC specifications. Serial LVDS data is clocked into the FIFO on both edges of the 625MHz source-synchronous TCLK. Data is clocked out of the FIFO using an internal 1.25GHz clock derived from a low-jitter 125MHz reference. Serial data is then clocked out as differential CML.

The receive path converts the CML signaling to LVDS and locks on to the data stream to recover the sourcesynchronous clock (RCLK). The receive section contains a CML input buffer, clock recovery circuit, and LVDS output buffers. The receiver accepts a CML serial data stream. The clock recovery phase-locked loop (PLL) locks on to the incoming serial data stream and generates a 625MHz LVDS DDR clock. RCLK edges are at the center of the "eye" of RDAT data.

> 1000Base-SX/LX Optical Links **GBIC Modules** SFP Fiber Transceiver Modules

Typical Application Circuit appears at end of data sheet.

### Features

- 1000Base-SX/LX, GBIC, or SFP Serial Data Conversion to/from 1.25Gbps LVDS Serial Data and DDR Clock

- CML Interface Exceeds all PECL AC Specifications for 1000Base-SX/LX, GBIC, or SFP Serial Data

- Tx Data Retiming with <0.1UI Total Output Jitter</p> as per IEEE802.3z

- Rx Data and Clock Recovery with 0.75UI Jitter Tolerance as per IEEE802.3z

- On-Chip Forward and Back Termination Using CML I/O and Integrated Termination/Bias Resistors

- PLL Lock Status Indicator

- System Loopback

- JTAG I/O Scan for Board-Level Testing

## **Ordering Information**

| PART       | TEMP RANGE    | PIN-<br>PACKAGE | PKG CODE |

|------------|---------------|-----------------|----------|

| MAX3782UGK | -5°C to +85°C | 68 QFN-EP*      | G6800-4  |

\*EP = exposed pad.

## **MIXIM**

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

**Applications**

## **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage (VCC1, VCC2, VCC3,

| VCC4, VCC5, VCC6, VCCTEMP)    | 0.5V to +4.0V                    |

|-------------------------------|----------------------------------|

| LVDS Input and Output Voltage | 0.5V to (V <sub>CC</sub> + 0.5V) |

| LVTTL Input or Output Voltage | 0.5V to (V <sub>CC</sub> + 0.5V) |

| CML Input Voltage             | 0.5V to (V <sub>CC</sub> + 0.5V) |

| Continuous CML Output Current | 10mA to +25mA                    |

| Momentary CML Output Voltage  |                                  |

| (duration <1min, +25°C)       | 0 to (V <sub>CC</sub> + 0.5V)    |

TEMPSENS, RXFIL1, RXFIL2,

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 3.0V to 3.6V, LVDS differential load =  $100\Omega \pm 1\%$ , CML differential load =  $100\Omega \pm 1\%$ , T<sub>A</sub> = -5°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25°C.)

| PARAMETER                        | SYMBOL     | CONDITIONS                                         | MIN  | ТҮР                   | MAX  | UNITS             |

|----------------------------------|------------|----------------------------------------------------|------|-----------------------|------|-------------------|

| Supply Current                   |            |                                                    |      | 440                   | 620  | mA                |

| Power Dissipation                |            |                                                    |      | 1.45                  | 2.23 | W                 |

| Supply Noise Tolerance           |            | DC-500kHz, single-ended REFCLK (Note 1)            |      | 50                    |      | mV <sub>P-P</sub> |

| LVTTL INPUTS AND OUTPUTS (       | except REF | CLK±)                                              |      |                       |      |                   |

| Input High Voltage               |            |                                                    | 2.0  |                       |      | V                 |

| Input Low Voltage                |            |                                                    |      |                       | 0.8  | V                 |

| Input High Current               |            |                                                    |      |                       | -250 | μΑ                |

| Input Low Current                |            |                                                    |      |                       | -500 | μA                |

| Output High Voltage              |            | (Note 2)                                           | 2.4  |                       |      | V                 |

| Output Low Voltage               |            | (Note 2)                                           |      |                       | 0.4  | V                 |

| Output Three State Current       |            | Three-state enabled, $0.4V \le V_{OUT} \le V_{CC}$ | -100 |                       | +100 |                   |

| Output Three-State Current       |            | Three-state enabled, $GND \le V_{OUT} < 0.4V$      |      |                       | 400  | μA                |

| REFCLK INPUTS                    |            |                                                    |      |                       |      |                   |

| Differential Input Amplitude     |            | REFCLK± AC-coupled                                 | 200  |                       | 2000 | mV <sub>P-P</sub> |

| Single-Ended Input High Voltage  |            | REFCLK- connected through 0.01µF to GND            | 2.0  |                       |      | V                 |

| Single-Ended Input Low Voltage   |            | REFCLK- connected through 0.01µF to GND            |      |                       | 0.8  | V                 |

| REFCLK Input High Current        |            | $2.0V \le V_{IN} \le V_{CC}$                       |      |                       | 440  | μA                |

| REFCLK Input Low Current         |            | $GND \le V_{IN} \le 0.8V$                          |      |                       | -227 | μA                |

| CML INPUTS (Note 3)              |            |                                                    |      |                       |      |                   |

| Differential Input Voltage Range |            | 802.3z and GBIC compatible                         | 370  |                       | 2000 | mV <sub>P-P</sub> |

| Common-Mode Voltage              |            | Inputs open or AC-coupled                          |      | V <sub>CC</sub> - 0.3 |      | V                 |

| Input Impedance                  |            | (Note 4)                                           | 85   | 100                   | 115  | Ω                 |

| CML OUTPUTS (Note 3)             |            |                                                    |      |                       | _    |                   |

| Differential Output Voltage      |            |                                                    | 1100 |                       | 2000 | mV <sub>P-P</sub> |

| Output Common-Mode Voltage       |            |                                                    |      | V <sub>CC</sub> - 0.4 |      | V                 |

| Differential Output Impedance    |            | (Note 4)                                           | 85   | 100                   | 115  | Ω                 |

|                                  |            |                                                    |      |                       |      |                   |

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 3.0V \text{ to } 3.6V, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{CML differential load} = 100\Omega \pm 1\%, T_A = -5^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted}$ . Typical values are at V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25^{\circ}C.)

| PARAMETER                                                                         | SYMBOL              | CONDITIONS                             | MIN   | ТҮР | MAX   | UNITS |

|-----------------------------------------------------------------------------------|---------------------|----------------------------------------|-------|-----|-------|-------|

| LVDS INPUTS                                                                       | •                   |                                        | •     |     |       |       |

| Input Voltage Range                                                               | VI                  | IV <sub>GPD</sub> I < 925mV            | 0     |     | 2000  | mV    |

| Differential Input Voltage                                                        | IVIDI               | IV <sub>GPD</sub> I < 925mV            | 150   |     | 500   | mV    |

| Differential Input Impedance                                                      | RIN                 |                                        | 85    | 100 | 115   | Ω     |

| Input Common-Mode Current                                                         |                     | $V_{OS} = 1.2V$ , inputs tied together |       | 270 | 400   | μA    |

| LVDS OUTPUTS                                                                      |                     |                                        |       |     |       |       |

| Differential Output Voltage                                                       | IV <sub>OD</sub> I  |                                        | 250   |     | 400   | mV    |

| Output High Voltage                                                               | VOH                 |                                        |       |     | 1.475 | V     |

| Output Low Voltage                                                                | Vol                 |                                        | 0.925 |     |       | V     |

| Change in Magnitude of<br>Differential Output Voltage for<br>Complementary States | ΔIV <sub>OD</sub> I |                                        |       |     | 25    | mV    |

| Output Offset Voltage                                                             | VOS                 |                                        | 1.125 |     | 1.275 | V     |

| Change in Magnitude of Output<br>Offset Voltage for<br>Complementary States       | ΔIV <sub>OS</sub> I |                                        |       |     | 25    | mV    |

| Differential Output Impedance                                                     | Rod                 |                                        | 80    | 100 | 120   | Ω     |

| Short-Circuit Current                                                             |                     | Short to supply or ground              |       |     | 40    | mA    |

Note 1: Supply noise tolerance is the amount of noise allowable on the power supply. The intent of this is to specify the conditions whereby the CML I/O jitter performance remains compliant with IEEE802.3z jitter specifications.

**Note 2:** The LOCK output is open collector and requires a  $10k\Omega$  pullup to V<sub>CC</sub>. TDO output load  $\geq 11k\Omega$  to V<sub>CC</sub> or to GND.

Note 3: CML differential signal amplitudes are specified as the total signal across the load (V+ - V-). CML inputs and outputs are designed to be AC-coupled.

**Note 4:**  $100\Omega$  is standard for SFP, nonstandard for IEEE802.3z and GBIC.

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3.0V \text{ to } 3.6V, LVDS \text{ differential load} = 100\Omega \pm 1\%$ , CML differential load = 100 $\Omega \pm 1\%$ , REFCLK = 125MHz, T<sub>A</sub> = -5°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25°C.) (Note 5)

| PARAMETER                                | SYMBOL | CONDITIONS                                        | MIN | ТҮР | MAX | UNITS |

|------------------------------------------|--------|---------------------------------------------------|-----|-----|-----|-------|

| JTAG PARAMETERS                          |        |                                                   |     |     |     |       |

| Clock Frequency                          |        |                                                   |     |     | 15  | MHz   |

| Setup Time                               |        | Data input to clock positive edge                 | 15  | 7   |     | ns    |

| Hold Time                                |        | Clock positive edge to data input                 | 13  | 5   |     | ns    |

| Propagation Delay                        |        | Clock negative edge to data output $(C \le 20pF)$ | 2   |     | 30  | ns    |

| TDO Output Rise Time                     |        | $C \le 20pF$ , measured 20% to 80%                | 2   |     | 20  | ns    |

| TDO Output Fall Time                     |        | $C \le 20pF$ , measured 20% to 80%                | 1   |     | 20  | ns    |

| TDO Output Three-State to<br>Active Time |        | $C \le 20pF$ , measured as rise or fall time      | 1   |     | 30  | ns    |

## AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 3.0V \text{ to } 3.6V, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{ CML differential load} = 100\Omega \pm 1\%, \text{ REFCLK} = 125\text{MHz}, \text{ T}_{\text{A}} = -5^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at V_{CC} = 3.3V \text{ and } \text{T}_{\text{A}} = +25^{\circ}\text{C}.)$  (Note 5)

| PARAMETER                                    | SYMBOL   | CONDITIONS                                                                                                    | MIN   | ТҮР   | MAX | UNITS |

|----------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------|-------|-------|-----|-------|

| LOCK DETECT PARAMETERS                       | •        |                                                                                                               |       |       |     |       |

| Assert Time                                  |          | To assert, the Tx and Rx PLL internal lock indicators must be high (lock achieved) for this period.           |       | 394   |     | μs    |

| Deassert Time                                |          | To deassert, the Tx or Rx PLL internal lock indicators must be low for this period                            |       | 1053  |     | μs    |

| TRANSMITTER PARAMETERS                       |          |                                                                                                               |       |       |     |       |

| TCLK Frequency                               |          |                                                                                                               |       | 625   |     | MHz   |

| REFCLK Input Rise/Fall Time                  |          | Single ended, 20% to 80%                                                                                      |       |       | 2   | ns    |

| Transmitter Latency                          |          | From TDAT to Tx                                                                                               |       | 5     |     | ns    |

| LVDS INPUTS                                  |          |                                                                                                               |       |       |     |       |

| Accumulated Phase Error at<br>TCLK1 or TCLK2 |          | Relative to REFCLK                                                                                            |       | ±1    |     | ns    |

| Setup Time                                   | tsu      | Figure 1                                                                                                      | 100   | 42    |     | ps    |

| Hold Time                                    | tH       | Figure 1                                                                                                      | 100   | 42    |     | ps    |

| CML OUTPUTS                                  |          |                                                                                                               |       |       |     |       |

| Differential Skew                            |          |                                                                                                               |       |       | 25  | ps    |

| Tx Output Jitter, Total                      |          | (Notes 6, 8)                                                                                                  |       | 32    | 73  | psp-p |

| Tx Output Jitter, Deterministic              |          | (Notes 6, 8)                                                                                                  |       | 9     | 20  | psp-p |

| Tx Output Jitter, Random                     |          | (Notes 6, 8)                                                                                                  |       | 23    | 53  | psp-p |

| <b>RECEIVER PARAMETERS</b> (Not              | es 7, 8) |                                                                                                               |       |       |     |       |

| Input Data Rate                              |          |                                                                                                               |       | 1.25  |     | Gbps  |

| PLL Lock Time                                |          | K28.5 pattern applied to Rx inputs, REFCLK must be applied and stable                                         |       | 1     |     | ms    |

|                                              |          | Pattern = $2^7 - 1$ , differential skew = 0,<br>0.45UI <sub>P-P</sub> of data-dependent jitter                |       | 0.938 |     |       |

| Input Jitter Tolerance<br>(Note 9)           |          | Pattern = CRPAT, differential skew = 0ps,<br>0.45UIP-P of data-dependent jitter                               |       | 0.885 |     | ]     |

|                                              |          | Pattern = CRPAT, differential skew = 218ps,<br>$0.45UI_{P-P}$ of data-dependent jitter                        | 0.776 | 0.838 |     | UIP-P |

|                                              |          | Pattern = CJTPAT, differential skew = $218$ ps,<br>0.248UI <sub>P-P</sub> of pulse-width distortion (Note 10) | 0.595 | 0.694 |     | 1     |

| Differential Skew Tolerance                  |          | 802.3z and GBIC compliant                                                                                     | 205   |       |     | ps    |

| Jitter Generation                            |          |                                                                                                               |       | 20    | 100 | psp-p |

| Receiver Latency                             |          | From Rx to RDAT                                                                                               |       | 5     |     | ns    |

### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 3.0V \text{ to } 3.6V, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{ CML differential load} = 100\Omega \pm 1\%, \text{ REFCLK} = 125\text{MHz}, \text{ T}_{\text{A}} = -5^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25°C.) (Note 5)

| PARAMETER                   | SYMBOL                          | CONDITIONS                                                                                      | MIN  | TYP | MAX  | UNITS             |

|-----------------------------|---------------------------------|-------------------------------------------------------------------------------------------------|------|-----|------|-------------------|

| LVDS OUTPUTS                |                                 |                                                                                                 |      |     |      |                   |

| Clock Duty-Cycle Distortion |                                 | Variation of 50% crossing from ideal time                                                       | -32  |     | +32  | ps                |

| Deterministic Jitter        |                                 | Measured with K28.5 pattern at RDAT_<br>outputs                                                 |      | 8   | 50   | psp-p             |

| Edge Speed                  | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%                                                                                      |      | 200 | 250  | ps                |

| Clock-to-Data Delay         | τclk-Q                          | Figure 2                                                                                        | 268  | 400 | 532  | ps                |

| REFERENCE CLOCK REQUIRE     | MENTS                           |                                                                                                 |      |     |      |                   |

| REFCLK Frequency            |                                 |                                                                                                 |      | 125 |      | MHz               |

| REFCLK Frequency Tolerance  |                                 |                                                                                                 | -100 |     | +100 | ppm               |

| REFCLK Duty Cycle           |                                 |                                                                                                 | 40   |     | 60   | %                 |

|                             |                                 | f - Ekula iitter ensumed Coursion                                                               |      |     | 210  | psp-p             |

|                             |                                 | f < 5kHz, jitter assumed Gaussian                                                               |      |     | 15   | ps <sub>RMS</sub> |

| REFCLK Jitter               |                                 | f > 5kHz, jitter is assumed deterministic,<br>caused by power-supply noise and buffer<br>jitter |      |     | 20   | psp-p             |

Note 5: AC characteristics are guaranteed by design and characterization.

- **Note 6:** Tx output jitter, total, is the sum of both deterministic (20psp-p max) and random (53psp-p max at BER = 10<sup>-12</sup>), as per IEEE802.3z. Measured with K28.5 pattern and one-pole 637kHz highpass filter weighting.

- Note 7: JITTER TEST METHODS: These are described in the draft technical report by ANSI T11.2/Project 1230, document FC-MJS, "Fibre Channel - Methodologies for Jitter Specification." The maximum BER used to specify both Fibre Channel links, as well as IEEE802.3z links is 10<sup>-12</sup>.

- **Note 8:** JITTER TEST CONDITIONS: The difference between the MAX3782 jitter specifications and the IEEE802.3z standards (see Table 1) represents the margin that must absorb all impairments such as jitter transfer from REFCLK, power-supply noise, and oscillator pulling (due to different Tx and Rx frequencies).

- Note 9: Input jitter tolerance is the total amount of high-frequency jitter at the inputs. Total jitter = deterministic jitter (DJ) + random jitter (RJ) + 5MHz sinusoidal jitter (SJ). Random jitter = 2ps<sub>RMS</sub> (35mUI<sub>RMS</sub>).

- **Note 10:** CJTPAT is a unique pattern, which toggles between high transition-density sections to low transition-density sections at a rate within the loop bandwidth of a CDR. Passing this signal through a band-limited channel results in data-dependent jitter (DDJ) that has instantaneous phase jumps occurring at the rate of transition-density change. The phase vs. time looks like a low-frequency square wave. A 0.5UIP-P low-frequency square wave of jitter is the maximum that can be tolerated by an ideal CDR. In other words, 0.5UIP-P low-frequency square-wave jitter produces an equivalent stress as 1.0UIP-P high-frequency square-wave jitter.

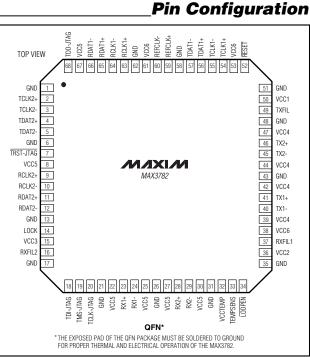

Figure 1. LVDS Receiver Input Eye Mask

(V<sub>CC</sub> = 3.3V, T<sub>A</sub> =  $+25^{\circ}C$ , unless otherwise noted.)

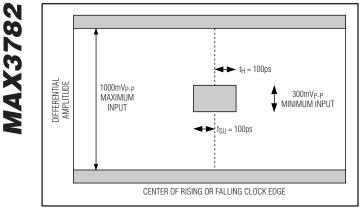

Figure 2. Definition of Clock-to-Data Delay

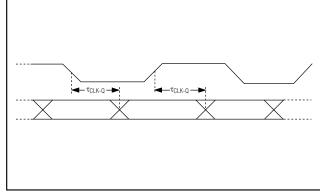

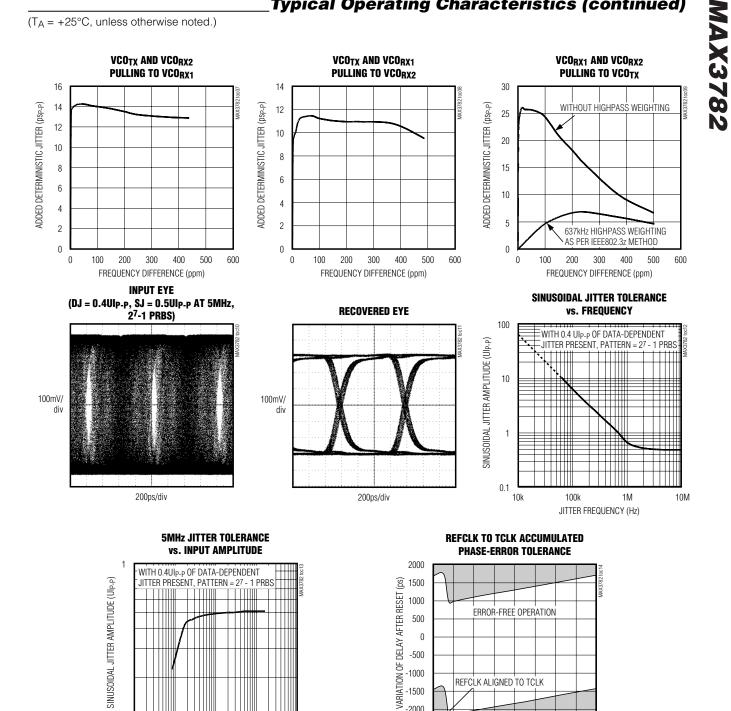

## **Typical Operating Characteristics**

## **Typical Operating Characteristics (continued)**

REFCLK ALIGNED TO TCLK

100 200 300 400 500 600 700 800

PHASE AT RESET (ps)

-2000

-2500

0

/N/XI/N

0.1

1

10

100

INPUT AMPLITUDE (mVP-P)

1000

10,000

**MAX3782**

| PIN                                                          | NAME                                                                                                                     | FUNCTION                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 13,<br>17, 21, 26,<br>31, 35, 43,<br>48, 51, 58,<br>62 | GND                                                                                                                      | Supply Ground                                                                                                                                                                                                                                              |

| 2                                                            | TCLK2+                                                                                                                   | Transmitter Positive Clock Input 2, LVDS. Input data is clocked on both the rising and falling edges of the 625MHz clock.                                                                                                                                  |

| 3                                                            | TCLK2-                                                                                                                   | Transmitter Negative Clock Input 2, LVDS. Input data is clocked on both the rising and falling edges of the 625MHz clock.                                                                                                                                  |

| 4                                                            | TDAT2+                                                                                                                   | Transmitter Positive Data Input 2, LVDS                                                                                                                                                                                                                    |

| 5                                                            | TDAT2-                                                                                                                   | Transmitter Negative Data Input 2, LVDS                                                                                                                                                                                                                    |

| 7                                                            | TRST-JTAG                                                                                                                | JTAG Test Reset Input, LVTTL. Momentarily connect $\overline{\text{TRST}}$ to GND to reset JTAG test circuitry. Internally pulled high through 15k $\Omega$ resistor.                                                                                      |

| 8, 22, 25,<br>27, 30, 67                                     | VCC5                                                                                                                     | 3.3V Supply for Receiver Digital Functions and JTAG Circuitry                                                                                                                                                                                              |

| 9                                                            | RCLK2+                                                                                                                   | Receiver Positive Clock Output 2, LVDS. Output data is clocked on both the rising and falling edges of the 625MHz clock.                                                                                                                                   |

| 10                                                           | RCLK2- Receiver Negative Clock Output 2, LVDS. Output data is clocked on both the rising and fallin of the 625MHz clock. |                                                                                                                                                                                                                                                            |

| 11                                                           | RDAT2+                                                                                                                   | Receiver Positive Data Output 2, LVDS                                                                                                                                                                                                                      |

| 12                                                           | RDAT2-                                                                                                                   | Receiver Negative Data Output 2, LVDS                                                                                                                                                                                                                      |

| 14                                                           | LOCK                                                                                                                     | Lock Status Indicator Output, LVTTL. This output goes high when the transmit PLL and receiver PLLs are in lock. Because this output is open-collector TTL, the LOCK pins from multiple MAX3782s can be connected in parallel to form a single LOCK signal. |

| 15                                                           | VCC3                                                                                                                     | 3.3V Supply for RX2 Receiver VCO, Analog Receiver Functions, and External Loop-Filter Connection                                                                                                                                                           |

| 16                                                           | RXFIL2                                                                                                                   | RX2 Receiver Loop-Filter Connection. Connect a 0.1µF capacitor between RXFIL2 and VCC3.                                                                                                                                                                    |

| 18                                                           | TDI-JTAG                                                                                                                 | JTAG Test Data Input, LVTTL. Internally pulled high through 15k $\Omega$ resistor.                                                                                                                                                                         |

| 19                                                           | TMS-JTAG                                                                                                                 | JTAG Test Mode Select Input, LVTTL. Internally pulled high through 15k $\Omega$ resistor.                                                                                                                                                                  |

| 20                                                           | TCLK-JTAG                                                                                                                | JTAG Test Clock Input, LVTTL. Internally pulled high through 15k $\Omega$ resistor.                                                                                                                                                                        |

| 23                                                           | RX1+                                                                                                                     | Receiver Positive Input 1, CML                                                                                                                                                                                                                             |

| 24                                                           | RX1-                                                                                                                     | Receiver Negative Input 1, CML                                                                                                                                                                                                                             |

| 28                                                           | RX2+                                                                                                                     | Receiver Positive Input 2, CML                                                                                                                                                                                                                             |

| 29                                                           | RX2-                                                                                                                     | Receiver Negative Input 2, CML                                                                                                                                                                                                                             |

| 32                                                           | VCCTEMP                                                                                                                  | 3.3V Supply for TEMPSENS. Connect to ground to disable the temperature-sensing function.                                                                                                                                                                   |

| 33                                                           | TEMPSENS                                                                                                                 | Junction Temperature Sensor Output, Analog. TEMPSENS corresponds to the junction temperature of the die. Leave open for normal use.                                                                                                                        |

| 34                                                           | LOOPEN                                                                                                                   | Loopback Enable Input, LVTTL. Force low to enable system loopback. Internally pulled high through $15 k\Omega$ .                                                                                                                                           |

| 36                                                           | VCC2                                                                                                                     | 3.3V Supply for RX1 Receiver VCO, Analog Receiver Functions, and External Loop-Filter Connection                                                                                                                                                           |

| 37                                                           | RXFIL1                                                                                                                   | RX1 Receiver Loop-Filter Connection. Connect a 0.1µF capacitor between RXFIL1 and VCC2.                                                                                                                                                                    |

| 38, 53, 61                                                   | VCC6                                                                                                                     | 3.3V Supply for Transmitter Digital Functions                                                                                                                                                                                                              |

| 39, 42, 44,<br>47                                            | VCC4                                                                                                                     | 3.3V Supply for CML Outputs                                                                                                                                                                                                                                |

**Pin Description**

## \_Pin Description (continued)

| PIN | NAME           | FUNCTION                                                                                                                                                                                                                                   |

|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40  | TX1-           | Transmitter Negative Output 1, CML                                                                                                                                                                                                         |

| 40  | TX1-           | Transmitter Positive Output 1, CML                                                                                                                                                                                                         |

| 41  | TX1+<br>TX2-   | Transmitter Negative Output 2, CML                                                                                                                                                                                                         |

| 43  | TX2+           | Transmitter Positive Output 2, CML                                                                                                                                                                                                         |

| 40  | TXEIL          |                                                                                                                                                                                                                                            |

| -   |                | Transmitter Loop-Filter Connection. Connect a $0.1\mu$ F capacitor between TXFIL and VCC1.                                                                                                                                                 |

| 50  | VCC1           | 3.3V Supply for Transmitter VCO, Analog Transmitter Functions, and External Loop-Filter Connection                                                                                                                                         |

| 52  | RESET          | Reset Input, LVTTL. Connect low for >80ns to reset FIFO and receiver components. Internally pulled high through $15k\Omega$ .                                                                                                              |

| 54  | TCLK1+         | Transmitter Positive Clock Input 1, LVDS. Input data is clocked on both the rising and falling edges of the 625MHz clock.                                                                                                                  |

| 55  | TCLK1-         | Transmitter Negative Clock Input 1, LVDS. Input data is clocked on both the rising and falling edges of the 625MHz clock.                                                                                                                  |

| 56  | TDAT1+         | Transmitter Positive Data Input 1, LVDS                                                                                                                                                                                                    |

| 57  | TDAT1-         | Transmitter Negative Data Input 1, LVDS                                                                                                                                                                                                    |

| 59  | REFCLK+        | Reference Clock Positive Input. See specification table for differential or single-ended use.                                                                                                                                              |

| 60  | REFCLK-        | Reference Clock Negative Input. See specification table for differential or single-ended use.                                                                                                                                              |

| 63  | RCLK1+         | Receiver Positive Clock Output 1, LVDS. Output data is clocked on both the rising and falling edges of the 625MHz clock.                                                                                                                   |

| 64  | RCLK1-         | Receiver Negative Clock Output 1, LVDS. Output data is clocked on both the rising and falling edges of the 625MHz clock.                                                                                                                   |

| 65  | RDAT1+         | Receiver Positive Data Input 1, LVDS                                                                                                                                                                                                       |

| 66  | RDAT1-         | Receiver Negative Data Input 1, LVDS                                                                                                                                                                                                       |

| 68  | TDO-JTAG       | JTAG Test Data Output, Three-State LVTTL                                                                                                                                                                                                   |

| EP  | Exposed<br>Pad | Supply Ground. The exposed pad must be soldered to the circuit board ground for proper thermal and electrical performance. See <i>Exposed-Pad Package</i> . The MAX3782 uses exposed pad variation G6800-4 in the package outline drawing. |

**MAX3782**

Figure 3. Functional Diagram

### **Detailed Description**

The MAX3782 dual 1.25Gbps transceiver is a data retimer and clock recovery device for 1000Base-SX/LX, GBIC, and SFP applications. In the transmitter, an integrated clock synthesizer generates a clean 1.25GHz clock. This clock is used with a FIFO to retime the data before transmission. CML output buffers provide excellent performance with minimal external components.

The receiver has two separate PLL clock recovery circuits, allowing independent recovery of each received data signal. The receiver has CML inputs, easing system design and decreasing component count.

JTAG functionality is included to help with board-level testing. A LOCK pin indicates the status of the internal PLLs. System loopback may be asserted with the LOOPEN input.

#### **LVDS Inputs and Outputs**

The MAX3782 LVDS interface includes two differential data inputs at 1.25Gbps, two half-rate differential clock inputs at 625MHz, two differential data outputs at 1.25Gbps, and two half-rate differential clock outputs at 625MHz. The MAX3782 LVDS-compatible interface is designed to work with the user's ASICs, minimize power dissipation, speed transition time, and improve noise immunity. The LVDS outputs also have short-circuit protection in case of shorts to VCC or GND. The LVDS inputs must be DC-coupled for proper biasing. AC-coupling these inputs results in unreliable opera-

tion. The LVDS outputs are designed to drive 100  $\!\Omega$  differential loads and are not designed to drive 50  $\!\Omega$  to ground.

#### **PLL Clock Multiplier**

The PLL clock multiplier uses the 125MHz reference clock to synthesize the 1.25GHz clock that synchronizes the transmitter functions. The reference clock also aids frequency acquisition in the receiver. To achieve proper jitter performance and BER benchmarks, using a high-quality, low-jitter reference clock is critical. REFCLK inputs can be driven differentially or single ended. Differential operation is recommended for its superior jitter performance and noise immunity.

#### **PLL Clock Recovery**

Both receive channels (RX1 and RX2) use PLLs to recover synchronous clocks from the incoming serial data. The recovered clocks are then used to retime the serial data. The typical loop bandwidth of the PLL clock recovery circuits is 1.5MHz.

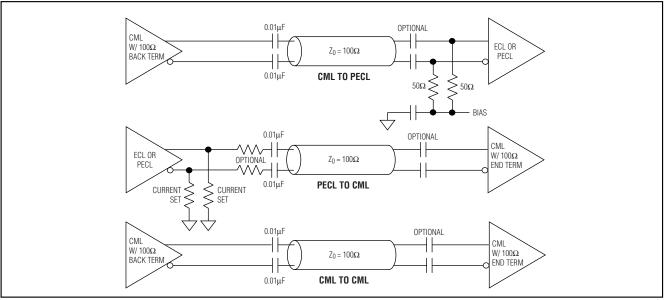

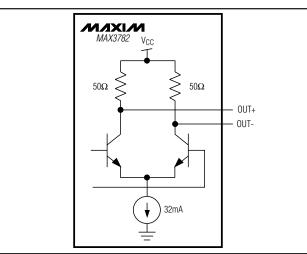

#### **CML Inputs and Outputs**

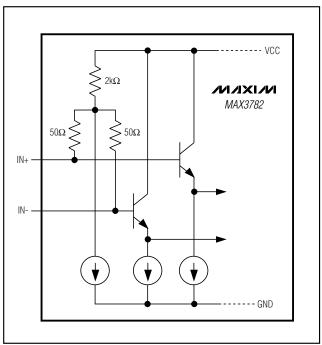

The CML inputs and outputs of the MAX3782 offer low power dissipation, excellent performance, and integrated termination resistors. AC-coupling capacitors should be used for PECL and IEEE802.3z compatibility. Figure 4 shows interface examples. The CML output structure is shown in Figure 5, and the CML input structure is shown in Figure 6. For more information, refer to

Figure 4. CML I/O Interconnect Examples

Figure 5. CML Output Structure

the applications note HFAN-01.0, *Introduction to LVDS, PECL, and CML*.

#### **Lock Detection**

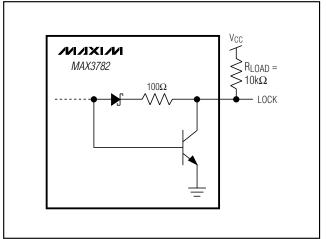

The LOCK output indicates the state of the transmitter and receiver PLLs. For lock detect to be asserted high, the transmitter and receiver internal lock indicators must be high for 394µs. The internal lock signals go high once frequency lock has been achieved. For lock detect to be asserted low, either the transmitter or receiver internal lock indicators must be low for a minimum of 1053µs. Lock detect also is asserted low when the external reset pin is forced low. LOCK stays low for a minimum of 394µs. For the lock detector to function properly, there must be data transitions at the RX1 and RX2 inputs and a valid reference clock input. Note: The LOCK output is not an accurate indicator of signal presence at the receiver inputs. With no data input, the LOCK output can be high, low, or toggling. The output structure of the LOCK pin is shown in Figure 7.

#### **RESET** Input

RESET must be held low for a minimum of four reference clock cycles for it to be properly asserted. Approximately 10ms or longer after power up, the RESET input should be asserted low. RESET resets the LOCK state and FIFO clock logic.

#### **Temperature Sensor**

To help evaluate thermal performance, a temperature sensor is incorporated into the MAX3782. The temperature sensor may be powered on or off regardless of the state of the rest of the chip. The VCCTEMP pin provides supply voltage for the temperature sensor circuit. The TEMPSENS output is designed to output a voltage pro-

Figure 6. CML Input Structure

portional to the die junction temperature (1mV per Kelvin). The temperature of the die can be calculated as:

$$\Gamma(^{\circ}C) \approx V_{\text{TEMPSENS}}(\text{mV}) \times \frac{1^{\circ}C}{\text{mV}} - 273^{\circ}C$$

Figure 7. LOCK Output Structure

## **Applications Information**

#### **Jitter Budget Example** for **Optical Link**

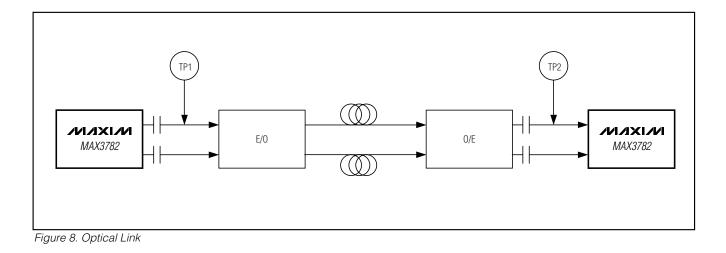

The MAX3782 outperforms IEEE802.3z jitter specifications. See Figure 8 and Table 1.

#### **JTAG**

JTAG functionality is compliant with IEEE1149.1 specifications. The BSDL file is available on request. Table 2 provides JTAG pin assignments.

#### **Layout Techniques**

For best performance, use good high-frequency layout techniques. Filter voltage supplies, keep ground connections short, and use multiple vias where possible. Use controlled-impedance  $50\Omega$  transmission lines to interface with the MAX3782 high-speed inputs and outputs.

Place power-supply decoupling capacitors as close to V<sub>CC</sub> as possible. To reduce feedthrough, isolate the input signals from the output signals.

### Table 1. Comparison of IEEE802.3z and MAX3782 Jitter Budget

|                  | TOTAL JIT                   | TOTAL JITTER (psp-p) DETERMINISTIC JITTER |                             |                          |

|------------------|-----------------------------|-------------------------------------------|-----------------------------|--------------------------|

| COMPLIANCE POINT | IEEE802.3z<br>SPECIFICATION | MAX3782<br>SPECIFICATION                  | IEEE802.3z<br>SPECIFICATION | MAX3782<br>SPECIFICATION |

| TP1              | 192                         | 73 (max)                                  | 100                         | 20 (max)                 |

|                  | 192                         | 32 (typ)                                  | 100                         | 9 (typ)                  |

|                  | TOTAL JITTER TO             | TOTAL JITTER TOLERANCE (psp-p)            |                             |                          |

| COMPLIANCE POINT | IEEE802.3z<br>SPECIFICATION | MAX3782<br>SPECIFICATION                  | -                           | _                        |

| TP2              | 600                         | 620 (min, CRPAT)                          | ]                           |                          |

| 172              | 600                         | 670 (typ, CRPAT)                          |                             |                          |

**MAX3782**

| MAX3782         | BOUNDARY SCAN | Ι/Ο ΤΥΡΕ              |                     | ROUTING |     |  |

|-----------------|---------------|-----------------------|---------------------|---------|-----|--|

| PIN NAME        | PORT NAME     |                       | CELL TYPE           | IN      | OUT |  |

| LOCK            | lock          | Open Collector Output | Observe and Control |         | 1   |  |

| RX2+            | rx2p          | CML Input             | Observe             | 2       |     |  |

| RX2-            | rx2n          | CML Input             | Observe             | 2       |     |  |

| RX1+            | rx1p          | CML Input             | Observe             | 3       |     |  |

| RX1-            | rx1n          | CML Input             | Observe             | 3       |     |  |

| LOOPEN          | loopen_bar    | LVTTL Input           | Observe             | 4       |     |  |

| TDAT2+          | tdat2p        | LVDS Input            | Observe             | 5       |     |  |

| TDAT2-          | tdat2n        | LVDS Input            | Observe             | 5       |     |  |

| TCLK2+          | tck2p         | LVDS Input            | Observe             | 6       |     |  |

| TCLK2-          | tck2n         | LVDS Input            | Observe             | 6       |     |  |

| TDAT1+          | tdat1p        | LVDS Input            | Observe             | 7       |     |  |

| TDAT1-          | tdat1n        | LVDS Input            | Observe             | 7       |     |  |

| TCLK1+          | tck1p         | LVDS Input            | Observe             | 8       |     |  |

| TCLK1-          | tck1n         | LVDS Input            | Observe             | 8       |     |  |

| TX1+            | tx1p          | CML Output            | Observe and Control |         | 9   |  |

| TX1-            | tx1n          | CML Output            | Observe and Control |         | 9   |  |

| TX2+            | tx2p          | CML Output            | Observe and Control |         | 10  |  |

| TX2-            | tx2n          | CML Output            | Observe and Control |         | 10  |  |

| RESET           | reset_bar     | LVTTL Input           | Observe             | 11      |     |  |

| REFCLK+         | refckp        | LVTTL Input           | Observe             | 12      |     |  |

| REFCLK-         | refckn        | LVTTL Input           | Observe             | 12      |     |  |

| RCLK1+          | rck1p         | LVDS Output           | Observe and Control |         | 13  |  |

| RCLK1-          | rck1n         | LVDS Output           | Observe and Control |         | 13  |  |

| RDAT1+          | rdat1p        | LVDS Output           | Observe and Control |         | 14  |  |

| RDAT1-          | rdat1n        | LVDS Output           | Observe and Control |         | 14  |  |

| RCLK2+          | rck2p         | LVDS Output           | Observe and Control |         | 15  |  |

| RCLK2-          | rck2n         | LVDS Output           | Observe and Control | 15      |     |  |

| RDAT2+          | rdat2p        | LVDS Output           | Observe and Control |         | 16  |  |

| RDAT2-          | rdat2n        | LVDS Output           | Observe and Control |         | 16  |  |

| JTAG CONTROL PI | NS            |                       |                     |         |     |  |

| TCLK-JTAG       | tck           | LVTTL Input           |                     |         |     |  |

| TDI-JTAG        | tdi           | LVTTL Input           |                     |         |     |  |

| TDO-JTAG        | tdo           | LVTTL Output          |                     |         |     |  |

| TMS-JTAG        | tms           | LVTTL Input           |                     |         |     |  |

| TRST-JTAG       | trst_bar      | LVTTL Input           |                     |         |     |  |

## Table 2. JTAG Pin Assignments

**MAX3782**

### **Table 3. JTAG Instructions**

| INSTRUCTION    | JTAG<br>OPCODE | ACTION                                           |

|----------------|----------------|--------------------------------------------------|

| EXTEST         | 000 b          | External boundary test mode                      |

| SAMPLE/PRELOAD | 001 b          | Initialization for boundary test mode            |

| BYPASS         | 111 b          | Connects bypass register between TDI and TDO     |

| IDCODE         | 010 b          | 32-bit device ID register selected (see Table 4) |

### **Table 4. Device Identification Code**

| CODE   | VERSION | ON PART NO. MANUFACTURER = MAXIM                      |                                          | LSB |  |

|--------|---------|-------------------------------------------------------|------------------------------------------|-----|--|

| Binary | 0001 b  | 0000 1110 1100 0110 b<br>[ = 3782 <sub>base10</sub> ] | 00011001011 b<br>[ ref: JEDEC JEP106-I ] | 1 b |  |

#### **Exposed-Pad Package**

The exposed-pad, 68-pin QFN-EP incorporates features that provide a very low thermal-resistance path for heat removal from the IC. The EP and EP ring are electrical ground on the MAX3782 and must be soldered to the circuit board for proper thermal and electrical performance. Refer to HFAN 08.10, *Thermal Considerations of QFN and Other Exposed-Pad Packages*, for more information.

## Chip Information

**MAX3782**

TRANSISTOR COUNT: 14329 PROCESS: Silicon bipolar

**Typical Application Circuit**

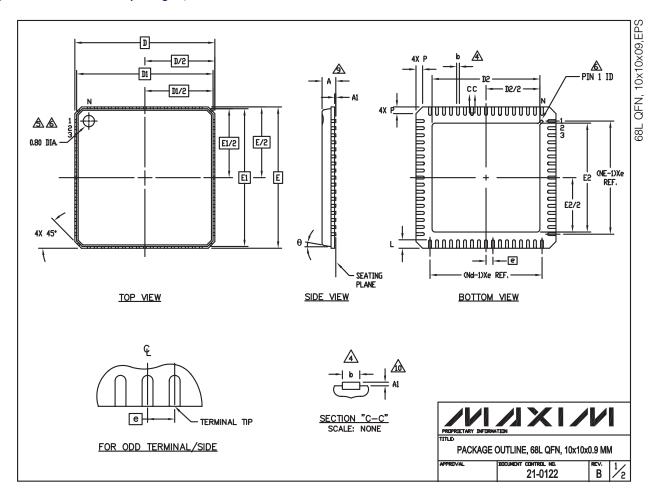

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

| S<br>Y∎®ol | COMMON DIMENSIONS |      |      | N <sub>O</sub> T <sub>E</sub> |

|------------|-------------------|------|------|-------------------------------|

| ٩          | MIN.              | NOM. | MAX. | ŤΕ                            |

| A          | -                 | 0.90 | 1.00 |                               |

| A1         | 0.00              | 0.01 | 0.05 | 11                            |

| b          | 0.18              | 0.23 | 0.30 | 4                             |

| D          | 10.00 BSC         |      |      |                               |

| D1         | 9.75 BSC          |      |      |                               |

| e          | 0.50 BSC          |      |      |                               |

| E          | 10.00 BSC         |      |      |                               |

| E1         | 9.75 BSC          |      |      |                               |

| L          | 0.50              | 0.60 | 0.75 |                               |

| N          | 68                |      |      | 3                             |

| Nd         | 17 3              |      |      | 3                             |

| Ne         | 17                |      |      | 3                             |

| θ          | 0                 | 12°  |      |                               |

| Ρ          | 0 0.42 0.60       |      |      |                               |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |

|------------------------|------|------|------|------|------|------|

|                        | D2   |      |      | E2   |      |      |

| PKG CODE               | MIN  | NDM  | MAX  | MIN  | NDM  | MAX  |

| G6800-2                | 7.55 | 7.70 | 7.85 | 7.55 | 7.70 | 7.85 |

| G6800-4                | 5.65 | 5.80 | 5.95 | 5.65 | 5.80 | 5.95 |

1. DIE THICKNESS ALLOWABLE IS .012 INCHES MAXIMUM.

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION &

- Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- ∠S THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY.

- 6 EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- PACKAGE WARPAGE MAX 0.10mm.

- APPLIES TO EXPOSED SURFACE OF PADS AND TERMINALS

- APPLIES ONLY TO TERMINALS.

|       | X | / | <b>/</b> // |

|-------|---|---|-------------|

| TITLE |   |   |             |

PACKAGE OUTLINE, 68L QFN, 10x10x0.9 MM

⅔

В

21-0122

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

|   | 0 |

|---|---|

| т |   |

|   |   |

|   |   |

\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.