# SHARC<sup>®</sup> Processor Data Sheet Addendum

### **Preliminary Technical Data**

## ADSP-21367/ADSP-21368/ADSP-21369

#### SUMMARY

- High performance 32-bit/40-bit floating point processor optimized for high performance audio processing

- Single-instruction, multiple-data (SIMD) computational architecture

- On-chip memory—2M bit of on-chip SRAM and 6M bit of onchip mask programmable ROM

- 400 MHz maximum core clock frequency

- 1.3 V core V<sub>DD</sub>/3.3 V I/O

- Code compatible with all other members of the SHARC family

- The ADSP-21367/ADSP-21368/ADSP-21369 are available with a 400 MHz core instruction rate with unique audiocentric peripherals such as the digital audio interface, S/PDIF transceiver, serial ports, 8-channel asynchronous

- sample rate converter, precision clock generators, and more. For complete ordering information, see Ordering Guide on Page 11.

- At 400 MHz (2.5 ns) core instruction rate, the processors perform 2.4 GFLOPS/800 MMACS

- Transfers between memory and core at a sustained 6.4G bytes/s bandwidth at 400 MHz core instruction rate

### **GENERAL DESCRIPTION**

This data sheet addendum introduces the 400 MHz ADSP-21367/ADSP-21368/ADSP-21369 SHARC processors. This addendum provides the frequency benchmark, as well as ac and dc specifications that differ from the 333 MHz ADSP-21367/ADSP-21368/ADSP-21369 SHARC processors. All other specifications and timing data as well as package information for these devices can be found in the ADSP-21367/ADSP-21368/ADSP-21369 SHARC Processor Data Sheet, Rev A. The products listed in the addendum are engineering grade and have not been fully characterized. For complete ordering information, see the Ordering Guide on Page 11.

SHARC and the SHARC logo are registered trademarks of Analog Devices, Inc.

#### Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

#### **TABLE OF CONTENTS**

| Summary                    | 1  |

|----------------------------|----|

| General Description        |    |

| Specifications             |    |

| Operating Conditions       | 3  |

| Electrical Characteristics |    |

| Timing Specifications      | 4  |

| Output Drive Currents      |    |

| Capacitive Loading         | 10 |

| Ordering Guide             |    |

|                            |    |

#### **PERFORMANCE BENCHMARKS**

The processors use two computational units to deliver a significant performance increase over the previous SHARC processors on a range of DSP algorithms. Fabricated in a state-of-the-art, high speed, CMOS process, the ADSP-21367/ADSP-

21368/ADSP-21369 processors achieve an instruction cycle time of up to 2.5 ns at 400 MHz. With its SIMD computational hardware, the processors can perform 2.4 GFLOPS running at 400 MHz. Table 1 shows performance benchmarks for these devices.

#### Table 1. Processor Benchmarks (at 400 MHz)

| Benchmark Algorithm                                            | Speed (at 400 MHz) |

|----------------------------------------------------------------|--------------------|

| 1024 Point Complex FFT (Radix 4, with reversal)                | 23.2 μs            |

| FIR Filter (per tap) <sup>1</sup>                              | 1.25 ns            |

| IIR Filter (per biquad) <sup>1</sup>                           | 5.0 ns             |

| Matrix Multiply (pipelined) $[3 \times 3] \times [3 \times 1]$ | 11.25 ns           |

| $[4 \times 4] \times [4 \times 1]$                             | 20.0 ns            |

| Divide (y/×)                                                   | 8.75 ns            |

| Inverse Square Root                                            | 13.5 ns            |

<sup>1</sup>Assumes two files in multichannel SIMD mode.

#### **POWER SUPPLIES**

The processors have separate power supply connections for the internal ( $V_{DDINT}$ ), external ( $V_{DDEXT}$ ), and analog ( $A_{VDD}/A_{VSS}$ ) power supplies. The internal and analog supplies must meet the 1.3 V requirement for the 400 MHz device. The external supply must meet the 3.3 V requirement. All external supply pins must be connected to the same power supply.

### SPECIFICATIONS

#### **OPERATING CONDITIONS**

| Parameter <sup>1</sup>             | Description                                                                         | Min  | Max               | Unit |

|------------------------------------|-------------------------------------------------------------------------------------|------|-------------------|------|

| V <sub>DDINT</sub>                 | Internal (Core) Supply Voltage                                                      | 1.25 | 1.35              | V    |

| A <sub>VDD</sub>                   | Analog (PLL) Supply Voltage                                                         | 1.25 | 1.35              | V    |

| V <sub>DDEXT</sub>                 | External (I/O) Supply Voltage                                                       | 3.13 | 3.47              | V    |

| V <sub>IH</sub> <sup>2</sup>       | High Level Input Voltage @ V <sub>DDEXT</sub> = max                                 | 2.0  | $V_{DDEXT} + 0.5$ | V    |

| V <sub>IL</sub> <sup>2</sup>       | Low Level Input Voltage @ V <sub>DDEXT</sub> = min                                  | -0.5 | +0.8              | V    |

| V <sub>IH_CLKIN</sub> <sup>3</sup> | High Level Input Voltage @ V <sub>DDEXT</sub> = max                                 | 1.74 | $V_{DDEXT} + 0.5$ | V    |

| V <sub>IL_CLKIN</sub> <sup>3</sup> | Low Level Input Voltage @ V <sub>DDEXT</sub> = min                                  | -0.5 | +1.1              | V    |

| τ                                  | Junction Temperature, 256-Ball SBGA @ $T_{\mbox{\scriptsize AMBIENT}}$ 0°C to +70°C | 0    | +105              | °C   |

<sup>1</sup>Specifications subject to change without notice.

<sup>2</sup>Applies to input and bidirectional pins: DATAx, ACK, RPBA, BRx, IDx, FLAGx, DAI\_Px, DPI\_Px, BOOT\_CFGx, CLK\_CFGx, RESET, TCK, TMS, TDI, TRST. <sup>3</sup>Applies to input pin CLKIN.

#### **ELECTRICAL CHARACTERISTICS**

| Parameter <sup>1</sup>             | Description                         | Test Conditions                                                                 | Min | Тур | Max | Unit |

|------------------------------------|-------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| $V_{OH}^{2}$                       | High Level Output Voltage           | @ $V_{DDEXT} = min, I_{OH} = -1.0 mA^3$                                         | 2.4 |     |     | V    |

| V <sub>OL</sub> <sup>2</sup>       | Low Level Output Voltage            | @ $V_{DDEXT} = min$ , $I_{OL} = 1.0 mA^3$                                       |     |     | 0.4 | V    |

| I <sub>IH</sub> <sup>4, 5</sup>    | High Level Input Current            | $@V_{DDEXT} = max, V_{IN} = V_{DDEXT} max$                                      |     |     | 10  | μA   |

| I <sub>IL</sub> <sup>4, 6, 7</sup> | Low Level Input Current             | @ $V_{DDEXT} = max, V_{IN} = 0 V$                                               |     |     | 10  | μΑ   |

| I <sub>IHPD</sub> <sup>6</sup>     | High Level Input Current Pull-down  | @ $V_{DDEXT} = max, V_{IN} = 0 V$                                               |     |     | 250 | μΑ   |

| I <sub>ILPU</sub> 5                | Low Level Input Current Pull-up     | $@V_{DDEXT} = max, V_{IN} = 0 V$                                                |     |     | 200 | μΑ   |

| I <sub>OZH</sub> <sup>8,9</sup>    | Three-State Leakage Current         | $@V_{DDEXT} = max, V_{IN} = V_{DDEXT} max$                                      |     |     | 10  | μA   |

| I <sub>OZL</sub> <sup>8, 10</sup>  | Three-State Leakage Current         | @ $V_{DDEXT} = max, V_{IN} = 0 V$                                               |     |     | 10  | μΑ   |

| I <sub>OZLPU</sub> 9               | Three-State Leakage Current Pull-up | @ $V_{DDEXT} = max, V_{IN} = 0 V$                                               |     |     | 200 | μA   |

| IDD-INTYP <sup>11</sup>            | Supply Current (Internal)           | $t_{CCLK} = 2.5 \text{ ns}, V_{DDINT} = 1.3 \text{ V}, 25^{\circ}\text{C}$      |     | 1.4 |     | А    |

| $AI_{DD}^{12}$                     | Supply Current (Analog)             | A <sub>VDD</sub> = max                                                          |     |     | 10  | mA   |

| C <sub>IN</sub> <sup>13, 14</sup>  | Input Capacitance                   | $f_{IN} = 1 \text{ MHz}, T_{CASE} = 25^{\circ}\text{C}, V_{IN} = 1.3 \text{ V}$ |     |     | 4.7 | pF   |

<sup>1</sup> Specifications subject to change without notice.

<sup>2</sup>Applies to output and bidirectional pins: ADDRx, DATAx, RD, WR, MSx, BRx, FLAGx, DAI\_Px, DPI\_Px, SDRAS, SDCAS, SDWE, SDCKE, SDA10, SDCLKx, EMU, TDO, CLKOUT.

<sup>4</sup>Applies to input pins without internal pull-ups: BOOT\_CFGx, CLK\_CFGx, CLKIN, RESET, TCK.

<sup>5</sup> Applies to input pins with internal pull-ups: ACK, RPBA, TMS, TDI, TRST.

<sup>6</sup>Applies to input pins with internal pull-downs: IDx.

<sup>8</sup>Applies to three-statable pins without internal pull-ups: FLAGx, SDCLKx, TDO.

<sup>9</sup>Applies to three-statable pins with internal pull-ups: ADDRx, DATAx, RD, WR, MSx, BRx, DAI\_Px, DPI\_Px, SDRAS, SDCAS, SDWE, SDCKE, SDA10, EMU.

<sup>10</sup>Applies to three-statable pins with internal pull-ups disabled: ADDRx, DATAX, RD, WR, MSx, BRx, DAI\_Px, DPI\_Px, SDRAS, SDCAS, SDCKE, SDA10 <sup>11</sup>See Engineer-to-Engineer Note 299 for further information.

<sup>12</sup>Characterized, but not tested.

<sup>13</sup>Applies to all signal pins.

<sup>14</sup>Guaranteed, but not tested.

<sup>&</sup>lt;sup>3</sup>See Output Drive Currents on Page 10 for typical drive current capabilities.

<sup>&</sup>lt;sup>7</sup> Applies to input pins with internal pull-ups disabled: ACK, RPBA.

#### TIMING SPECIFICATIONS

The processor's internal clock (a multiple of CLKIN) provides the clock signal for timing internal memory, processor core, and serial ports. During reset, program the ratio between the processor's internal clock frequency and external (CLKIN) clock frequency with the CLK\_CFG1–0 pins. To determine switching frequencies for the serial ports, divide down the internal clock, using the programmable divider control of each port (DIVx for the serial ports).

The processor's internal clock switches at higher frequencies than the system input clock (CLKIN). To generate the internal clock, the processor uses an internal phase-locked loop (PLL). This PLL-based clocking minimizes the skew between the system clock (CLKIN) signal and the processor's internal clock.

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While addition or subtraction would yield meaningful results for an individual device, the values given in this data sheet reflect statistical variations and worst cases. Consequently, it is not meaningful to add parameters to derive longer times. *Switching Characteristics* specify how the processor changes its signals. Circuitry external to the processor must be designed for compatibility with these signal characteristics. Switching characteristics describe what the processor will do in a given circumstance. Use switching characteristics to ensure that any timing requirement of a device connected to the processor (such as memory) is satisfied.

*Timing Requirements* apply to signals that are controlled by circuitry external to the processor, such as the data input for a read operation. Timing requirements guarantee that the processor operates correctly with other devices.

#### **Power-Up Sequencing**

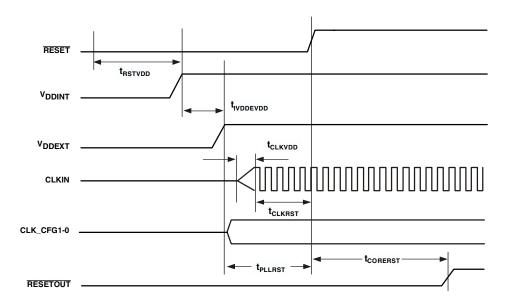

The timing requirements for processor startup are given in Table 2.

#### Table 2. Power-Up Sequencing Timing Requirements (Processor Startup)

| Parameter                        |                                                                | Min                              | Max  | Unit |

|----------------------------------|----------------------------------------------------------------|----------------------------------|------|------|

| Timing Requirer                  | ments                                                          |                                  |      |      |

| t <sub>RSTVDD</sub>              | RESET Low Before V <sub>DDINT</sub> /V <sub>DDEXT</sub> On     | 0                                |      | ns   |

| t <sub>IVDDEVDD</sub>            | V <sub>DDINT</sub> On Before V <sub>DDEXT</sub>                | -50                              | +200 | ms   |

| t <sub>CLKVDD</sub> <sup>1</sup> | CLKIN Valid After V <sub>DDINT</sub> /V <sub>DDEXT</sub> Valid | 0                                | +200 | ms   |

| t <sub>CLKRST</sub>              | CLKIN Valid Before RESET Deasserted                            | 10 <sup>2</sup>                  |      | μs   |

| t <sub>PLLRST</sub>              | PLL Control Setup Before RESET Deasserted                      | 20                               |      | μs   |

| Switching Chard                  | acteristic                                                     |                                  |      |      |

| t <sub>CORERST</sub>             | Core Reset Deasserted After RESET Deasserted                   | $4096t_{CK} + 2 t_{CCLK}^{3, 4}$ |      |      |

<sup>1</sup>Valid V<sub>DDINT</sub>/V<sub>DDEXT</sub> assumes that the supplies are fully ramped to their 1.3 volt rails and 3.3 volt rails. Voltage ramp rates can vary from microseconds to hundreds of milliseconds depending on the design of the power supply subsystem.

<sup>2</sup> Assumes a stable CLKIN signal, after meeting worst-case startup timing of crystal oscillators. Refer to your crystal oscillator manufacturer's data sheet for start-up time. Assume a 25 ms maximum oscillator start-up time if using the XTAL pin and internal oscillator circuit in conjunction with an external crystal.

<sup>3</sup> Applies after the power-up sequence is complete. Subsequent resets require RESET to be held low a minimum of four CLKIN cycles in order to properly initialize and propagate default states at all I/O pins.

<sup>4</sup> The 4096 cycle count depends on t<sub>srst</sub> specification. If setup time is not met, 1 additional CLKIN cycle may be added to the core reset time, resulting in 4097 cycles maximum.

Figure 1. Power-Up Sequencing

#### **Clock Input**

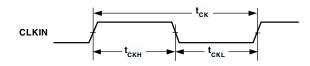

#### Table 3. Clock Input

|                                  |                                     | 400 MH           | lz               |      |

|----------------------------------|-------------------------------------|------------------|------------------|------|

| Parameter                        |                                     | Min              | Max              | Unit |

| Timing                           | Requirements                        |                  |                  |      |

| t <sub>CK</sub>                  | CLKIN Period                        | 18 <sup>1</sup>  | 100 <sup>2</sup> | ns   |

| t <sub>CKL</sub>                 | CLKIN Width Low                     | 8 <sup>1</sup>   | 45 <sup>2</sup>  | ns   |

| t <sub>CKH</sub>                 | CLKIN Width High                    | 8 <sup>1</sup>   | 45 <sup>2</sup>  | ns   |

| t <sub>CKRF</sub>                | CLKIN Rise/Fall (0.4 V to<br>2.0 V) |                  | 3                | ns   |

| t <sub>CCLK</sub> <sup>3</sup>   | CCLK Period                         | 2.5 <sup>1</sup> | 10               | ns   |

| t <sub>CKJ</sub> <sup>4, 5</sup> | CLKIN Jitter Tolerance              | -250             | +250             | ps   |

$^1$  Applies only for CLK\_CFG1–0 = 00 and default values for PLL control bits in PMCTL.

<sup>2</sup>Applies only for CLK\_CFG1-0 = 10 and default values for PLL control bits in PMCTL.

<sup>3</sup> Any changes to PLL control bits in the PMCTL register must meet core clock timing specification t<sub>CCLK</sub>.

$^4$  Actual input jitter should be combined with ac specifications for accurate timing analysis.

<sup>5</sup> Jitter specification is maximum peak-to-peak time interval error (TIE) jitter.

Figure 2. Clock Input

#### **Clock Signals**

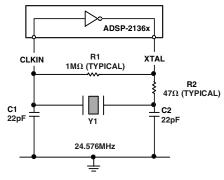

The processors can use an external clock or a crystal. See the CLKIN pin description. Programs can configure the processor to use its internal clock generator by connecting the necessary components to CLKIN and XTAL. Figure 3 shows the component connections used for a crystal operating in fundamental mode. Note that the clock rate is achieved using a 25 MHz crystal and a PLL multiplier ratio 16:1 (CCLK:CLKIN achieves a clock speed of 400 MHz). To achieve the full core clock rate, programs need to configure the multiplier bits in the PMCTL register.

R2 SHOULD BE CHOSEN TO LIMIT CRYSTAL DRIVE POWER. REFER TO CRYSTAL MANUFACTURER'S SPECIFICATIONS

Figure 3. 400 MHz Operation (Fundamental Mode Crystal)

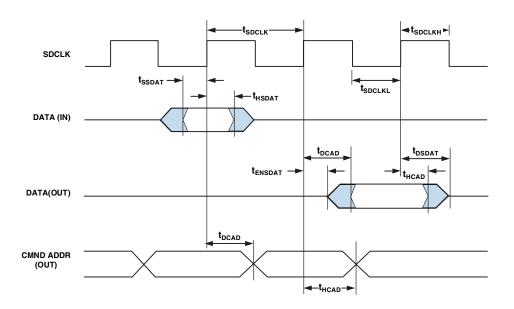

#### SDRAM Interface Timing (133 MHz SDCLK)

The 133 MHz access speed is for a single processor. When multiple ADSP-21368 processors are connected in a shared memory system, the access speed is 100 MHz.

#### Table 4. SDRAM Interface Timing<sup>1</sup>

| Paramete            | r                                                  | Min  | Max | Unit |

|---------------------|----------------------------------------------------|------|-----|------|

| Timing Red          | quirements                                         |      |     |      |

| t <sub>SSDAT</sub>  | DATA Setup Before SDCLK                            | 0.78 |     | ns   |

| t <sub>HSDAT</sub>  | DATA Hold After SDCLK                              | 1.23 |     | ns   |

| Switching           | Characteristics                                    |      |     |      |

| t <sub>SDCLK</sub>  | SDCLK Period                                       | 7.5  |     | ns   |

| t <sub>SDCLKH</sub> | SDCLK Width High                                   | 3.65 |     | ns   |

| t <sub>SDCLKL</sub> | SDCLK Width Low                                    | 3.65 |     | ns   |

| t <sub>DCAD</sub>   | Command, ADDR, Data Delay After SDCLK <sup>2</sup> |      | 4.8 | ns   |

| t <sub>HCAD</sub>   | Command, ADDR, Data Hold After SDCLK <sup>2</sup>  | 1.2  |     | ns   |

| t <sub>DSDAT</sub>  | Data Disable After SDCLK                           |      | 5.3 | ns   |

| t <sub>ensdat</sub> | Data Enable After SDCLK                            | 1.2  |     | ns   |

$^1\,\text{For}\ \text{F}_{\text{CCLK}}$  = 400 MHz (SDCLK ratio = 1:2.5).

<sup>2</sup>Command pins include: SDCAS, SDRAS, SDWE, MSx, SDA10, SDCKE.

Figure 4. SDRAM Interface Timing

### ADSP-21367/ADSP-21368/ADSP-21369 Data Sheet Adddendum

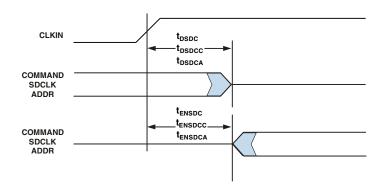

#### SDRAM Interface Enable/Disable Timing (133 MHz SDCLK)

#### Table 5. SDRAM Interface Enable/Disable Timing<sup>1</sup>

| Paramete                  | r                                | Min                     | Max                     | Unit |

|---------------------------|----------------------------------|-------------------------|-------------------------|------|

| Switching Characteristics |                                  |                         |                         |      |

| t <sub>DSDC</sub>         | Command Disable After CLKIN Rise |                         | $2 \times t_{PCLK} + 1$ | ns   |

| t <sub>ENSDC</sub>        | Command Enable After CLKIN Rise  | 4.0                     |                         | ns   |

| t <sub>DSDCC</sub>        | SDCLK Disable After CLKIN Rise   |                         | 8.5                     | ns   |

| t <sub>ENSDCC</sub>       | SDCLK Enable After CLKIN Rise    | 3.8                     |                         | ns   |

| t <sub>DSDCA</sub>        | Address Disable After CLKIN Rise |                         | 9.2                     | ns   |

| t <sub>ENSDCA</sub>       | Address Enable After CLKIN Rise  | $2 \times t_{PCLK} - 4$ | $4 \times t_{PCLK}$     | ns   |

$^{1}$  For  $F_{CCLK} = 400 \text{ MHz}$  (SDCLK ratio = 1:2.5).

Figure 5. SDRAM Interface Enable/Disable Timing

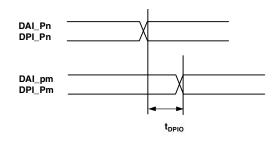

#### Pin to Pin Direct Routing (DAI and DPI)

For direct pin connections only (for example, DAI\_PB01\_I to DAI\_PB02\_O).

#### Table 6. DAI Pin to Pin Routing

| Parameter                                                       |  | Min | Max | Unit |

|-----------------------------------------------------------------|--|-----|-----|------|

| Timing Requirement                                              |  |     |     |      |

| t <sub>DPIO</sub> Delay DAI Pin Input Valid to DAI Output Valid |  | 1.5 | 12  | ns   |

Figure 6. DAI Pin to Pin Direct Routing

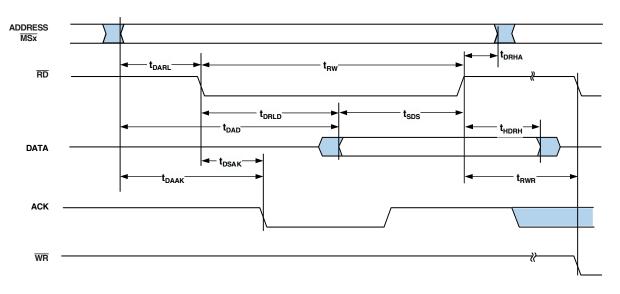

#### Memory Read - Bus Master to Memory Read

Use these specifications for asynchronous interfacing to memories. These specifications apply when the processors are the bus master accessing external memory space in asynchronous access mode. Note that timing for ACK, DATA, RD, WR, and strobe timing parameters only apply to asynchronous access mode.

#### Table 7. Memory Read—Bus Master

| Parameter         |                                                            | Min                          | Мах                   | Unit |

|-------------------|------------------------------------------------------------|------------------------------|-----------------------|------|

| Timing Req        | uirements                                                  |                              |                       |      |

| t <sub>DAD</sub>  | Address, Selects Delay to Data Valid <sup>1, 2</sup>       |                              | $W+t_{SDCLK}-5.12$    | ns   |

| t <sub>DRLD</sub> | RD Low to Data Valid <sup>1</sup>                          |                              | W– 2.9                | ns   |

| t <sub>sds</sub>  | Data Setup to RD High                                      | 2.2                          |                       | ns   |

| HDRH              | Data Hold from $\overline{\text{RD}}$ High <sup>3, 4</sup> | 0                            |                       | ns   |

| t <sub>DAAK</sub> | ACK Delay from Address, Selects <sup>2, 5</sup>            |                              | $t_{SDCLK} - 9.5 + W$ | ns   |

| DSAK              | ACK Delay from RD Low <sup>4</sup>                         |                              | W – 7.0               | ns   |

| Switching (       | haracteristics                                             |                              |                       |      |

| DRHA              | Address Selects Hold After RD High                         | RH + 0.18                    |                       | ns   |

| DARL              | Address Selects to RD Low <sup>2</sup>                     | t <sub>SDCLK</sub> – 3.3     |                       | ns   |

| RW                | RD Pulse Width                                             | W – 1.2                      |                       | ns   |

| t <sub>RWR</sub>  | RD High to WR, RD Low                                      | HI +t <sub>SDCLK</sub> – 0.8 |                       | ns   |

W = (number of wait states specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

HI =RHC + IC (RHC = number of read hold cycles specified in AMICTLx register) × t<sub>SDCLK</sub>

IC = (number of idle cycles specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

H = (number of hold cycles specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

$^1\text{Data}$  delay/setup: system must meet  $t_{\text{DAD}}$  ,  $t_{\text{DRLD}}$  , or  $t_{\text{SDS}.}$

<sup>2</sup> The falling edge of  $\overline{\text{MS}}x$  is referenced.

<sup>3</sup>Note that timing for ACK, DATA, RD, WR, and strobe timing parameters only apply to asynchronous access mode.

$^4$  Data hold: User must meet  $t_{\rm HDA}$  or  $t_{\rm HDRH}$  in asynchronous access mode.

<sup>5</sup>ACK Delay/Setup: User must meet t<sub>DAAK</sub>, or t<sub>DSAK</sub>, for deassertion of ACK (low). For asynchronous assertion of ACK (high) user must meet t<sub>DAAK</sub> or t<sub>DSAK</sub>.

#### **OUTPUT DRIVE CURRENTS**

**Figure 8** shows typical I-V characteristics for the output drivers of the ADSP-21367/ADSP-21368/ADSP-21369. The curves represent the current drive capability of the output drivers as a function of output voltage.

Figure 8. Typical Drive at Junction temperature

#### **CAPACITIVE LOADING**

Output delays and holds are based on standard capacitive loads: 30 pF on all pins. Figure 11 shows graphically how output delays and holds vary with load capacitance. The graphs of Figure 9, Figure 10, and Figure 11 may not be linear outside the ranges shown for Typical Output Delay vs. Load Capacitance and Typical Output Rise Time (20% to 80%, V = Min) vs. Load Capacitance.

Figure 10. Typical Output Rise/Fall Time (20% to 80%,  $V_{DDEXT} = Min$ )

Figure 11. Typical Output Delay or Hold vs. Load Capacitance (at Junction Temperature)

### ADSP-21367/ADSP-21368/ADSP-21369 Data Sheet Addendum

#### **ORDERING GUIDE**

| Part Number                    | Temperature<br>Range              | Instruction<br>Rate | On-Chip<br>SRAM | ROM    | Operating<br>Voltage<br>Internal/External | Package<br>Description | Package<br>Option |

|--------------------------------|-----------------------------------|---------------------|-----------------|--------|-------------------------------------------|------------------------|-------------------|

| ADSP-21367KBP-3A <sup>1</sup>  | $0^{\circ}$ C to +70°C            | 400 MHz             | 2M bit          | 6M bit | 1.3 V/3.3 V                               | 256-Ball SBGA          | BP-256            |

| ADSP-21367KBPZ-3A <sup>2</sup> | $0^{\circ}$ C to +70 $^{\circ}$ C | 400 MHz             | 2M bit          | 6M bit | 1.3 V/3.3 V                               | 256-Ball SBGA          | BP-256            |

| ADSP-21368KBP-3A               | $0^{\circ}$ C to +70 $^{\circ}$ C | 400 MHz             | 2M bit          | 6M bit | 1.3 V/3.3 V                               | 256-Ball SBGA          | BP-256            |

| ADSP-21368KBPZ-3A <sup>2</sup> | $0^{\circ}$ C to +70 $^{\circ}$ C | 400 MHz             | 2M bit          | 6M bit | 1.3 V/3.3 V                               | 256-Ball SBGA          | BP-256            |

| ADSP-21369KBP-3A               | $0^{\circ}$ C to +70 $^{\circ}$ C | 400 MHz             | 2M bit          | 6M bit | 1.3 V/3.3 V                               | 256-Ball SBGA          | BP-256            |

| ADSP-21369KBPZ-3A <sup>2</sup> | $0^{\circ}$ C to +70 $^{\circ}$ C | 400 MHz             | 2M bit          | 6M bit | 1.3 V/3.3 V                               | 256-Ball SBGA          | BP-256            |

<sup>1</sup> Available with a wide variety of audio algorithm combinations sold as part of a chipset and bundled with necessary software. For a complete list, visit our website at www.analog.com/SHARC.

<sup>2</sup>Z = RoHS Compliant Part.

$\hfill {\fill {\mathbb S}}$  2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. PR06770-0-4/07(PrA)

www.analog.com