# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

ζενεςν

### DATA SHEET

#

# /µPD70F3003A,70F3025A,70F3003A(A)

## V853 32-BIT SINGLE-CHIP MICROCONTROLLERS

#### DESCRIPTION

The  $\mu$ PD70F3003A,  $\mu$ PD70F3025A, and  $\mu$ PD70F3003A(A) have a flash memory instead of the internal mask ROM of the  $\mu$ PD703003A/703004A,  $\mu$ PD703025A, and  $\mu$ PD703003A(A), respectively. This model is useful for small-scale production of a variety of application sets or early start of production since the program can be written and erased by the user even with the  $\mu$ PD70F3003 mounted on the board.

Detailed function descriptions are provided in the following user's manuals. Be sure to read them before designing.

V853 Hardware User's Manual: U10913E V850 Series Architecture User's Manual: U10243E

#### FEATURES

- Compatible with  $\mu$ PD703003A, 703004A, 703025A, and 703003A(A)

- Can be replaced with mask ROM model for mass production of application set μPD70F3003A → μPD703003A, 703004A μPD70F3025A → μPD703025A μPD70F3003A(A) → μPD703003A(A)

- Internal memory Flash memory: 128KB (µPD70F3003A, 70F3003A(A))

256KB (µPD70F3025A)

Remark For differences among the products, refer to 1. DIFFERENCES BETWEEN PRODUCT.

#### **\*** ORDERING INFORMATION

| Part Number             | Package                                              | Quality Grade |

|-------------------------|------------------------------------------------------|---------------|

| μPD70F3003AGC-33-8EU    | 100-pin plastic LQFP (fine pitch) (14 $\times$ 14)   | Standard      |

| µPD70F3003AGC-33-8EU-A  | 100-pin plastic LQFP (fine pitch) (14 $\times$ 14)   | Standard      |

| μPD70F3025AGC-33-8EU    | 100-pin plastic LQFP (fine pitch) (14 $\times$ 14)   | Standard      |

| μPD70F3025AGC-33-8EU-A  | 100-pin plastic LQFP (fine pitch) ( $14 \times 14$ ) | Standard      |

| µPD70F3003AGC(A)-33-8EU | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14)    | Special       |

**Remarks 1.** The  $\mu$ PD70F3003A and  $\mu$ PD70F3003A(A) differ in the quality grade only.

2. Products with -A at the end of the part number are lead-free products.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Electronics Corporation to know the specification of the quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

#### APPLICATIONS

| µPD70F3003A, 70F3025A: | Camcorders, VCRs, PPCs, LBPs, printers, motor controllers, NC machine |

|------------------------|-----------------------------------------------------------------------|

|                        | tools, mobile telephones, etc.                                        |

| μPD70F3003A(A):        | Medical equipment, automotive appliances, etc.                        |

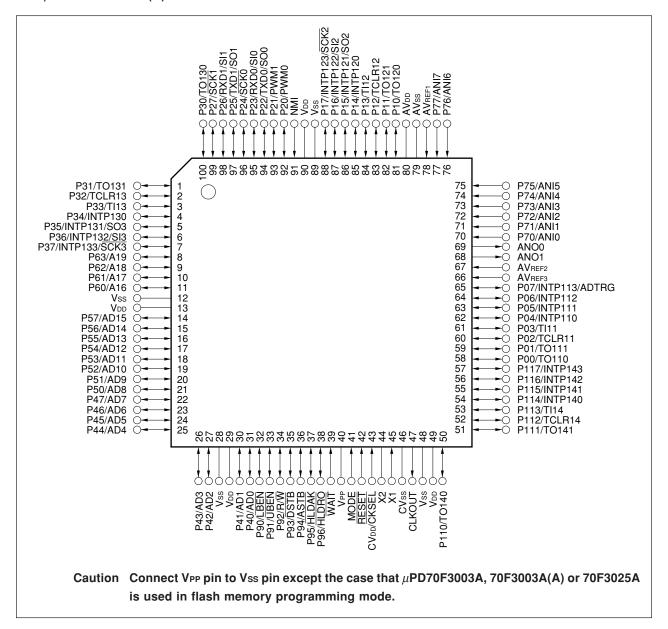

#### ★ PIN CONFIGURATION (Top View)

100-Pin Plastic LQFP (fine pitch) (14 × 14)

μPD70F3003AGC-33-8EU

μPD70F3003AGC-33-8EU-A

μPD70F3003AGC(A)-33-8EU

μPD70F3003AGC(A)-33-8EU

#### PIN NAMES

| A16 to A19:         | Address bus                        | P40 to P47:        | Port 4                   |

|---------------------|------------------------------------|--------------------|--------------------------|

| AD0 to AD15:        | Address/data bus                   | P50 to P57:        | Port 5                   |

| ADTRG:              | A/D Trigger input                  | P60 to P63:        | Port 6                   |

| ANI0 to ANI7:       | Analog input                       | P70 to P77:        | Port 7                   |

| ANO0, ANO1:         | Analog output                      | P90 to P96:        | Port 9                   |

| ASTB:               | Address strobe                     | P110 to P117:      | Port 11                  |

| AVDD:               | Analog VDD                         | PWM0, PWM1:        | Pulse width modulation   |

| AVREF1 to AVREF3:   | Analog reference voltage           | RESET:             | Reset                    |

| AVss:               | Analog Vss                         | $R/\overline{W}$ : | Read/write status        |

| CVDD:               | Power supply for clock generator   | RXD0, PXD1:        | Receive data             |

| CVss:               | Ground for clock generator         | SCK0 to SCK3:      | Serial clock             |

| CKSEL:              | Clock select                       | SI0 to SI3:        | Serial input             |

| CLKOUT :            | Clock output                       | SO0 to SO3:        | Serial output            |

| DSTB:               | Data strobe                        | TO110, TO111,      |                          |

| HLDAK:              | Hold acknowledge                   | TO120, TO121,      |                          |

| HLDRQ:              | Hold request                       | TO130, TO131,      |                          |

| INTP110 to INTP113, |                                    | TO140, TO141:      | Timer output             |

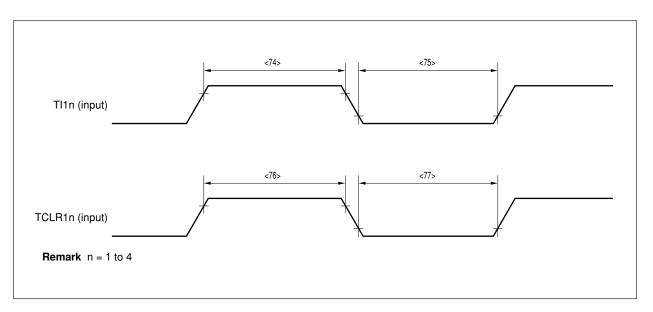

| INTP120 to INTP123, |                                    | TCLR11 to TCLR14:  | Timer clear              |

| INTP130 to INTP133, |                                    | TI11 to TI14:      | Timer input              |

| INTP140 to INTP143: | Interrupt request from peripherals | TXD0, TXD1:        | Transmit data            |

| LBEN:               | Lower byte enable                  | UBEN:              | Upper byte enable        |

| MODE:               | Mode                               | WAIT:              | Wait                     |

| NMI:                | Non-maskable interrupt request     | X1, X2:            | Crystal                  |

| P00 to P07:         | Port 0                             | Vdd:               | Power supply             |

| P10 to P17:         | Port 1                             | Vpp:               | Programming power supply |

| P20 to P27:         | Port 2                             | Vss:               | Ground                   |

| P30 to P37:         | Port 3                             |                    |                          |

|                     |                                    |                    |                          |

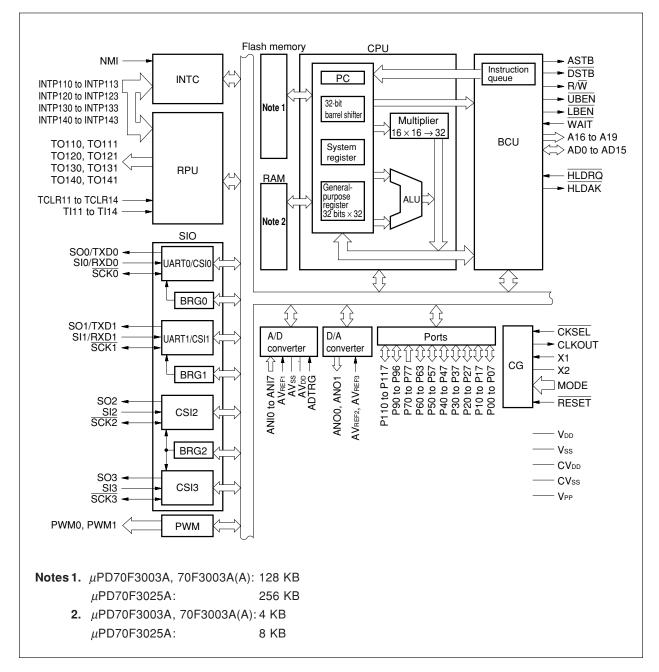

#### INTERNAL BLOCK DIAGRAM

$\star$

### CONTENTS

| 1. DIFFERENCES BETWEEN PRODUCTS                                | 6  |

|----------------------------------------------------------------|----|

| 2. PIN FUNCTIONS                                               |    |

| 2.1 Port Pins                                                  | 7  |

| 2.2 Non-Port Pins                                              | 9  |

| 2.3 Pin I/O Circuits and Recommended Connection of Unused Pins | 11 |

| 3. ELECTRICAL SPECIFICATIONS                                   | 14 |

| 3.1 Normal Operation Mode                                      | 14 |

| 3.2 Flash Memory Programming Mode                              | 37 |

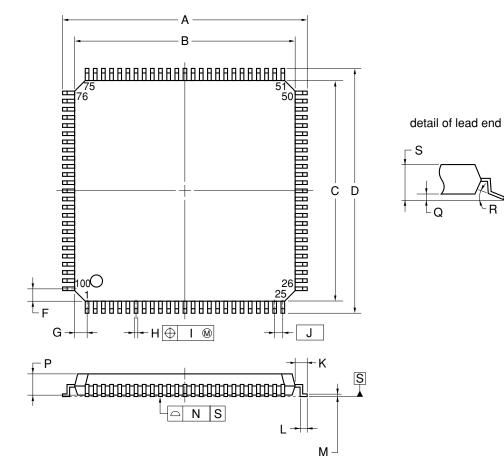

| 4. PACKAGE DRAWING                                             | 40 |

| 5. RECOMMENDED SOLDERING CONDITIONS                            | 41 |

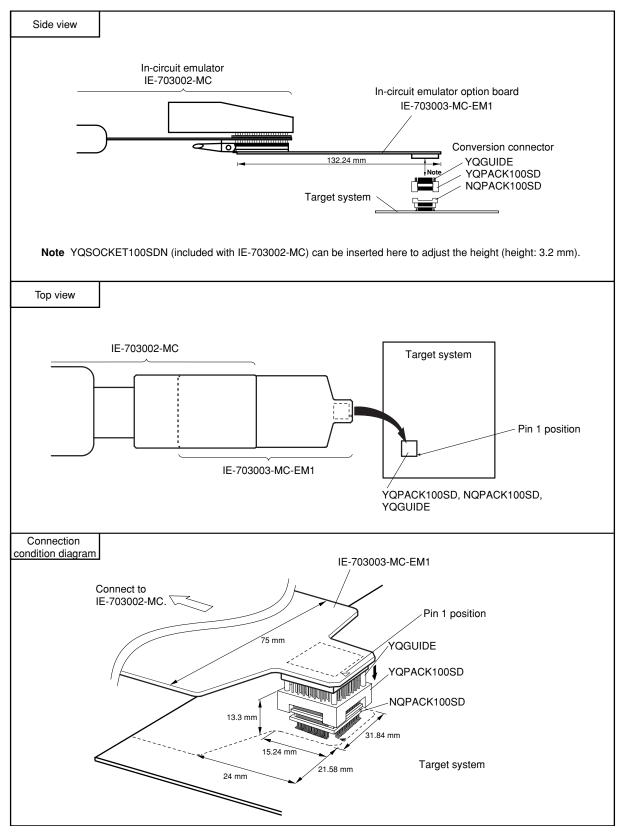

| APPENDIX NOTES ON TARGET SYSTEM DESIGN                         | 43 |

#### **1. DIFFERENCES BETWEEN PRODUCTS**

| Item                             | µPD703003A | µPD703004A                                                                             | μPD703025A | µPD703003A(A) | µPD703025A(A) | µPD70F3003A | µPD70F3025A  | µPD70F3003A(A) |  |

|----------------------------------|------------|----------------------------------------------------------------------------------------|------------|---------------|---------------|-------------|--------------|----------------|--|

| Internal ROM                     | Mask ROM   | Mask ROM                                                                               |            |               |               |             | Flash memory |                |  |

|                                  | 128 KB     | 96 KB                                                                                  | 256 KB     | 128 KB        | 256 KB        | 128 KB      | 256 KB       | 128 KB         |  |

| Internal RAM                     | 4 KB 8 KB  |                                                                                        |            | 4 KB          | 8 KB          | 4 KB        | 8 KB         | 4 KB           |  |

| Flash memory<br>programming mode | None       | None Provided                                                                          |            |               |               |             |              |                |  |

| VPP pin                          | None       | None Provided                                                                          |            |               |               |             |              |                |  |

| Quality grade                    | Standard   | Standard Special                                                                       |            |               |               |             |              | Special        |  |

| Electrical specifications        | Current co | Current consumption, etc. differs. (Refer to each product data sheets).                |            |               |               |             |              |                |  |

| Others                           | Noise imm  | oise immunity and noise radiation differ because circuit scale and mask layout differ. |            |               |               |             |              |                |  |

Caution There are differences in noise immunity and noise radiation between the flash memory version and mask ROM version. When pre-producing an application set with the flash memory version and then mass-producing it with the mask ROM version, be sure to conduct sufficient evaluation for commercial samples (not engineering samples) of the mask ROM version.

#### 2. PIN FUNCTIONS

#### 2.1 Port Pins

| Pin Name   | I/O | Function                                      | Alternate Function |

|------------|-----|-----------------------------------------------|--------------------|

| P00        | I/O | Port 0                                        | TO110              |

| P01        |     | 8-bit I/O port.                               | TO111              |

| P02        |     | Input/output can be specified in 1-bit units. | TCLR11             |

| P03        |     |                                               | TI11               |

| P04        |     |                                               | INTP110            |

| P05        |     |                                               | INTP111            |

| P06        |     |                                               | INTP112            |

| P07        |     |                                               | INTP113/ADTRG      |

| P10        | I/O | Port 1                                        | TO120              |

| P11        |     | 8-bit I/O port.                               | TO121              |

| P12        |     | Input/output can be specified in 1-bit units. | TCLR12             |

| P13        |     |                                               | TI12               |

| P14        |     |                                               | INTP120            |

| P15        |     |                                               | INTP121/SO2        |

| P16        |     |                                               | INTP122/SI2        |

| P17        |     |                                               | INTP123/SCK2       |

| P20        | I/O | Port 2                                        | PWM0               |

| P21        |     | 8-bit I/O port.                               | PWM1               |

| P22        |     | Input/output can be specified in 1-bit units. | TXD0/SO0           |

| P23        |     |                                               | RXD0/SI0           |

| P24        |     |                                               | SCK0               |

| P25        |     |                                               | TXD1/SO1           |

| P26        |     |                                               | RXD1/SI1           |

| P27        |     |                                               | SCK1               |

| P30        | I/O | Port 3                                        | TO130              |

| P31        |     | 8-bit I/O port.                               | TO131              |

| P32        |     | Input/output can be specified in 1-bit units. | TCLR13             |

| P33        |     |                                               | TI13               |

| P34        |     |                                               | INTP130            |

| P35        |     |                                               | INTP131/SO3        |

| P36        |     |                                               | INTP132/SI3        |

| P37        |     |                                               | INTP133/SCK3       |

| P40 to P47 | I/O | Port 4                                        | AD0 to AD7         |

|            |     | 8-bit I/O port.                               |                    |

|            |     | Input/output can be specified in 1-bit units. |                    |

| P50 to P57 | I/O | Port 5                                        | AD8 to AD15        |

|            |     | 8-bit I/O port.                               |                    |

|            |     | Input/output can be specified in 1-bit units. |                    |

|            |       |                                               | (2/2)              |

|------------|-------|-----------------------------------------------|--------------------|

| Pin Name   | I/O   | Function                                      | Alternate Function |

| P60 to P63 | I/O   | Port 6                                        | A16 to A19         |

|            |       | 4-bit I/O port.                               |                    |

|            |       | Input/output can be specified in 1-bit units. |                    |

| P70 to P77 | Input | Port 7                                        | ANI0 to ANI7       |

|            |       | 8-bit input port.                             |                    |

| P90        | I/O   | Port 9                                        | LBEN               |

| P91        |       | 7-bit I/O port.                               | UBEN               |

| P92        |       | Input/output can be specified in 1-bit units. | R/W                |

| P93        |       |                                               | DSTB               |

| P94        | _     |                                               | ASTB               |

| P95        |       |                                               | HLDAK              |

| P96        |       |                                               | HLDRQ              |

| P110       | I/O   | Port 11                                       | TO140              |

| P111       | _     | 8-bit I/O port.                               | TO141              |

| P112       |       | Input/output can be specified in 1-bit units. | TCLR14             |

| P113       |       |                                               | TI14               |

| P114       |       |                                               | INTP140            |

| P115       |       |                                               | INTP141            |

| P116       |       |                                               | INTP142            |

| P117       | -     |                                               | INTP143            |

#### 2.2 Non-Port Pins

| Pin Name | I/O         | Function                                                       | Alternate Function |

|----------|-------------|----------------------------------------------------------------|--------------------|

| TO110    | Output      | Pulse signal output from timers 11 to 14                       | P00                |

| TO111    |             |                                                                | P01                |

| TO120    |             |                                                                | P10                |

| TO121    |             |                                                                | P11                |

| TO130    |             |                                                                | P30                |

| TO131    |             |                                                                | P31                |

| TO140    |             |                                                                | P110               |

| TO141    |             |                                                                | P111               |

| TCLR11   | Input       | External clear signal input for timers 11 to 14                | P02                |

| TCLR12   |             |                                                                | P12                |

| TCLR13   |             |                                                                | P32                |

| TCLR14   |             |                                                                | P112               |

| TI11     | Input       | External count clock input for timers 11 to 14                 | P03                |

| TI12     |             |                                                                | P13                |

| TI13     |             |                                                                | P33                |

| TI14     |             |                                                                | P113               |

| INTP110  | Input       | External maskable interrupt request input and external capture | P04                |

| INTP111  | trigger inp | trigger input for timer 11                                     | P05                |

| INTP112  |             |                                                                | P06                |

| INTP113  |             |                                                                | P07/ADTRG          |

| INTP120  | Input       | External maskable interrupt request input and external capture | P14                |

| INTP121  |             | trigger input for timer 12                                     | P15/SO2            |

| INTP122  |             |                                                                | P16/S12            |

| INTP123  |             |                                                                | P17/SCK2           |

| INTP130  | Input       | External maskable interrupt request input and external capture | P34                |

| INTP131  |             | trigger input for timer 13                                     | P35/SO3            |

| INTP132  |             |                                                                | P36/SI3            |

| INTP133  |             |                                                                | P37/SCK3           |

| INTP140  | Input       | External maskable interrupt request input and external capture | P114               |

| INTP141  |             | trigger input for timer 14                                     | P115               |

| INTP142  |             |                                                                | P116               |

| INTP143  |             |                                                                | P117               |

| SO0      | Output      | Serial transmit data output for CSI0 to CSI3 (3-wire)          | P22/TXD0           |

| SO1      |             |                                                                | P25/TXD1           |

| SO2      |             |                                                                | P15/INTP121        |

| SO3      |             |                                                                | P35/INTP131        |

| SI0      | Input       | Serial receive data output for CSI0 to CSI3 (3-wire)           | P23/RXD0           |

| SI1      | 7           |                                                                | P26/RXD1           |

| SI2      | 1           |                                                                | P16/INTP122        |

| SI3      | 1           |                                                                | P36/INTP132        |

| Pin Name           | I/O    | Function                                                              | Alternate Function |

|--------------------|--------|-----------------------------------------------------------------------|--------------------|

| SCK0               | I/O    | Serial clock I/O for CSI0 to CSI3 (3-wire)                            | P24                |

| SCK1               |        |                                                                       | P27                |

| SCK2               |        |                                                                       | P17/INTP123        |

| SCK3               |        |                                                                       | P37/INTP133        |

| TXD0               | Output | Serial transmit data output of UART0 to UART1                         | P22/SO0            |

| TXD1               |        |                                                                       | P25/SO1            |

| RXD0               | Input  | Serial receive data input of UART0 to UART1                           | P23/SI0            |

| RXD1               | 1      |                                                                       | P26/SI1            |

| PWM0               | Output | Pulse signal output of PWM                                            | P20                |

| PWM1               | _      |                                                                       | P21                |

| AD0 to AD7         | I/O    | 16-bit multiplexed address/data bus when external memory is connected | P40 to P47         |

| AD8 to AD15        |        |                                                                       | P50 to P57         |

| A16 to A19         | Output | Higher address bus when external memory is connected                  | P60 to P63         |

| LBEN               | Output | Lower byte enable signal output of external data bus                  | P90                |

| UBEN               |        | Higher byte enable signal output of external data bus                 | P91                |

| R/W                | Output | External read/write status output                                     | P92                |

| DSTB               |        | External data strobe signal output                                    | P93                |

| ASTB               | 1      | External address strobe signal output                                 | P94                |

| HLDAK              | Output | Bus hold acknowledge output                                           | P95                |

| HLDRQ              | Input  | Bus hold request input                                                | P96                |

| ANI0 to ANI7       | Input  | Analog input to A/D converter                                         | P70 to P77         |

| ANO0, ANO1         | Output | Analog output of D/A converter                                        |                    |

| NMI                | Input  | Non-maskable interrupt request input                                  | _                  |

| CLKOUT             | Output | System clock output                                                   |                    |

| CKSEL              | Input  | Input specifying operation mode of clock generator                    | CVDD               |

| WAIT               | Input  | Control signal input inserting wait state in bus cycle                |                    |

| MODE               | Input  | Operation mode specification                                          | _                  |

| RESET              | Input  | System reset input                                                    |                    |

| X1                 | Input  | System clock resonator connection. Input external clock to X1 to      | _                  |

| X2                 | _      | supply external clock.                                                |                    |

| ADTRG              | Input  | A/D converter external trigger input                                  | P07/INTP113        |

| AV <sub>REF1</sub> | Input  | Reference voltage input for A/D converter                             | _                  |

| AV <sub>REF2</sub> | Input  | Reference voltage input for D/A converter                             | _                  |

| AV <sub>REF3</sub> | 1      |                                                                       |                    |

| AVDD               | _      | Positive power supply for A/D converter                               | _                  |

| AVss               |        | Ground potential for A/D converter                                    | _                  |

| CVDD               | _      | Positive power supply for internal clock generator                    | CKSEL              |

| CVss               |        | Ground potential for internal clock generator                         | _                  |

| Vdd                |        | Positive power supply                                                 | _                  |

| Vss                |        | Ground potential                                                      | _                  |

| VPP                |        | High voltage application pin when program is written/verified         |                    |

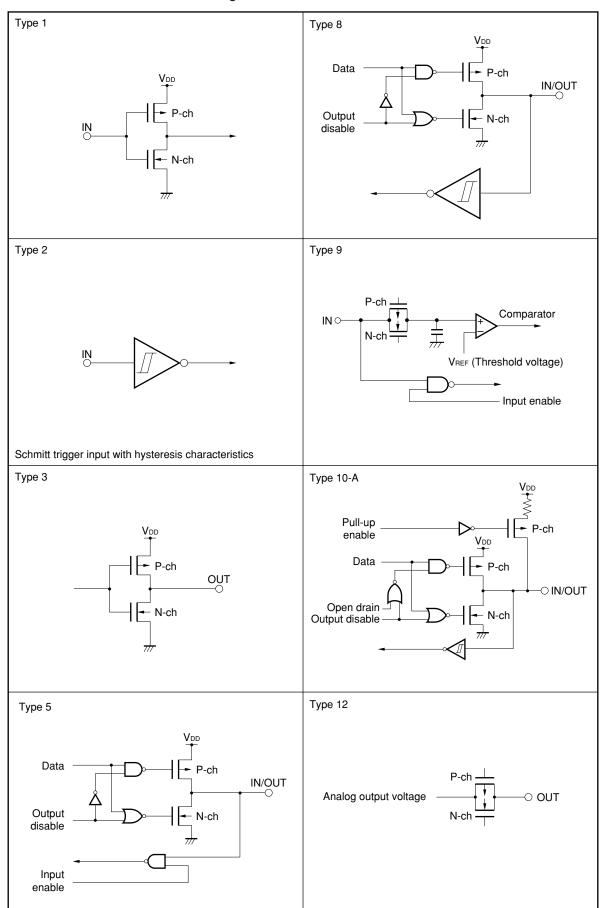

#### 2.3 Pin I/O Circuits and Recommended Connection of Unused Pins

Table 2-1 shows the I/O circuit type of each pin, and the recommended connections of the unused pins. Figure 2-1 shows a partially simplified diagram of each circuit.

It is recommended that 1 to 10 k $\Omega$  resistors be used when connecting to V\_DD or Vss via a resistor.

#### Table 2-1. Types of Pin I/O Circuits and Recommended Connections of Unused Pins (1/2)

| Pin Name                         | I/O Circuit Type | Recommended Connection of Unused Pins                      |

|----------------------------------|------------------|------------------------------------------------------------|

| P00/TO110, P01/TO111             | 5                | Input: Independently connect to VDD or VSS via a resistor. |

| P02/TCLR11, P03/TI11,            | 8                | Output: Leave open.                                        |

| P04/INTP110 to P07/INTP113/ADTRG |                  |                                                            |

| P10 to TO120, P11/TO121          | 5                |                                                            |

| P12/TCLR12, P13/TI12             | 8                |                                                            |

| P14/INTP120                      |                  |                                                            |

| P15/INTP121/SO2                  |                  |                                                            |

| P16/INTP122/SI2                  |                  |                                                            |

| P17/INTP123/SCK2                 |                  |                                                            |

| P20/PWM0, P21/PWM1               | 5                |                                                            |

| P22/TXD0/SO0                     |                  |                                                            |

| P23/RXD0/SI0, P24/SCK0           | 8                |                                                            |

| P25/TXD1/SO1                     | 5                |                                                            |

| P26/RXD1/SI1, P27/SCK1           | 8                |                                                            |

| P30/TO130, P31/TO131             | 5                |                                                            |

| P32/TCLR13, P33/TI13             | 8                |                                                            |

| P34/INTP130                      |                  |                                                            |

| P35/INTP131/SO3                  | 10-A             |                                                            |

| P36/INTP132/SI3                  |                  |                                                            |

| P37/INTP133/SCK3                 |                  |                                                            |

| P40/AD0 to P47/AD7               | 5                |                                                            |

| P50/AD8 to P57/AD15              | -                |                                                            |

| P60/A16 to P63/A19               |                  |                                                            |

| P70/ANI0 to P77/ANI7             | 9                | Directly connect to Vss.                                   |

| P90/LBEN                         | 5                | Input: Independently connect to VDD or VSS via a resistor. |

| P91/UBEN                         |                  | Output: Leave open.                                        |

| P92/R/W                          |                  |                                                            |

| P93/DSTB                         |                  |                                                            |

| P94/ASTB                         |                  |                                                            |

| P95/HLDAK                        |                  |                                                            |

| P96/HLDRQ                        |                  |                                                            |

| P110/TO140, P111/TO141           |                  |                                                            |

| P112/TCLR14, P113/TI14           | 8                |                                                            |

| P114/INTP140 to P117/INTP143     |                  |                                                            |

#### Table 2-1. Types of Pin I/O Circuits and Recommended Connection of Unused Pins (2/2)

| Pin Name               | I/O Circuit Type | Recommended Connection of Unused Pins |

|------------------------|------------------|---------------------------------------|

| ANO0, ANO1             | 12               | Leave open.                           |

| NMI                    | 2                | Directly connect to Vss.              |

| CLKOUT                 | 3                | Leave open.                           |

| WAIT                   | 1                | Directly connect to VDD.              |

| MODE                   | 2                |                                       |

| RESET                  |                  | —                                     |

|                        | -                | _                                     |

| AVREF1 to AVREF3, AVSS | _                | Directly connect to Vss.              |

| AVDD                   | _                | Directly connect to VDD.              |

| Vpp                    | _                | Connect to Vss.                       |

Figure 2-1. Pins I/O Circuits

#### 3. ELECTRICAL SPECIFICATIONS

#### 3.1 Normal Operation Mode

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Parameter                      | Symbol          | Conditio                         | ins                                | Ratings                                         | Unit |

|--------------------------------|-----------------|----------------------------------|------------------------------------|-------------------------------------------------|------|

| Supply voltage                 | Vdd             | Vdd pin                          | -0.5 to +7.0                       | V                                               |      |

|                                | CVDD            | CV <sub>DD</sub> pin             | CV <sub>DD</sub> pin               |                                                 | V    |

|                                | CVss            | CVss pin                         |                                    | -0.5 to +0.5                                    | V    |

|                                | AVDD            | AV <sub>DD</sub> pin             |                                    | -0.5 to V_DD + 0.3 <sup>Note 1</sup>            | V    |

|                                | AVss            | AVss pin                         |                                    | -0.5 to +0.5                                    | V    |

| Input voltage                  | VI1             | <b>Note 2</b> , VDD = 5.0 V ±10% | /<br>0                             | -0.5 to V <sub>DD</sub> + 0.3 <sup>Note 1</sup> | V    |

|                                | V <sub>12</sub> | VPP pin in flash memory p        | rogramming mode,                   | -0.5 to +11.0                                   | V    |

|                                |                 | $V_{DD} = 5.0 V \pm 10\%$        |                                    |                                                 |      |

| Clock input voltage            | Vк              | X1 pin, VDD = 5.0 V ±10%         | )                                  | -0.5 to VDD + 1.0 <sup>Note 1</sup>             | V    |

| Output current, low            | lc∟             | 1 pin                            |                                    | 4.0                                             | mA   |

|                                |                 | Total of all pins                |                                    | 100                                             | mA   |

| Output current, high           | Існ             | 1 pin                            |                                    | -4.0                                            | mA   |

|                                |                 | Total of all pins                |                                    | -100                                            | mA   |

| Output voltage                 | Vo              | $V_{DD} = 5.0 V \pm 10\%$        |                                    | -0.5 to VDD + 0.3Note 1                         | V    |

| Analog input voltage           | VIAN            | P70/ANI0 to P77/ANI7             | AVDD > VDD                         | -0.5 to VDD + 0.3Note 1                         | V    |

|                                |                 |                                  | $V_{DD} \ge AV_{DD}$               |                                                 | V    |

| Analog reference input voltage | AVREF           | AVREF1 tO AVREF3 AVDD > VDD      |                                    | -0.5 to VDD + 0.3Note 1                         | V    |

|                                |                 |                                  | $V_{\text{DD}} \ge AV_{\text{DD}}$ | -0.5 to AVDD + 0.3Note 1                        | V    |

| Operating ambient temperature  | TA              |                                  |                                    | -40 to +85                                      | °C   |

| Storage temperature            | Tstg            |                                  |                                    | -65 to +125                                     | °C   |

Notes 1. Be sure not to exceed the absolute maximum ratings (MAX. value) of each supply voltage.

2. X1, P70 to P77, AVREF1 to AVREF3, and their alternate-function pins are excluded.

- Cautions 1. Avoid direct connections among the IC device output (or I/O) pins and between VDD or Vcc and GND. However, direct connections among open-drain and open-collector pins are possible, as are direct connections to external circuits that have timing designed to prevent output conflict with pins that become high-impedance.

- Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded. The normal operating ranges of ratings and conditions in which the quality of the product is guaranteed are specified in the following DC Characteristics and AC Characteristics.

#### Capacitance (T<sub>A</sub> = $25^{\circ}$ C, V<sub>DD</sub> = V<sub>SS</sub> = 0 V)

| Parameter          | Symbol | Conditions                      | MIN. | TYP. | MAX. | Unit |

|--------------------|--------|---------------------------------|------|------|------|------|

| Input capacitance  | С      | fc = 1 MHz                      |      |      | 15   | рF   |

| I/O capacitance    | Сю     | Pins other than tested pin: 0 V |      |      | 15   | pF   |

| Output capacitance | Co     |                                 |      |      | 15   | pF   |

#### **Operating Conditions**

| Operation Mode | Internal System Clock Frequency ( $\phi$ ) | Operating Temperature (TA) | Supply Voltage (VDD) |

|----------------|--------------------------------------------|----------------------------|----------------------|

| Direct mode,   | 2 to 33 MHz <sup>Note 1</sup>              | −40 to +85°C               | 5.0 V ±10%           |

| PLL mode       | 5 to 33 MHz <sup>Note 2</sup>              | −40 to +85°C               | 5.0 V ±10%           |

Notes 1. When A/D converter not used.

2. When A/D converter used.

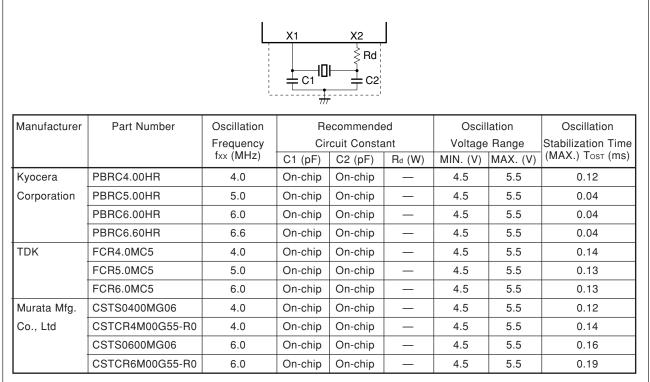

#### **Recommended Oscillator**

Caution For the resonator selection and oscillator constant of the  $\mu$ PD70F3003A(A), customers are requested to apply to the resonator manufacturer for evaluation.

#### (1) Ceramic resonator connection (T<sub>A</sub> = -40 to $+85^{\circ}$ C)

#### (a) *µ*PD70F3003A

| X1 X2 $Rd$ $C1$ $C2$ |                 |                                         |         |             |        |          |          |                    |  |  |

|----------------------|-----------------|-----------------------------------------|---------|-------------|--------|----------|----------|--------------------|--|--|

| Manufacturer         | Part Number     | ber Oscillation Recommended Oscillation |         |             |        |          |          | Oscillation        |  |  |

|                      |                 | Frequency                               | Cir     | cuit Consta | ant    | Voltage  | Range    | Stabilization Time |  |  |

|                      |                 | fxx (MHz)                               | C1 (pF) | C2 (pF)     | Rd (W) | MIN. (V) | MAX. (V) | (MAX.) Tost (ms)   |  |  |

| Kyocera              | PBRC4.00HR      | 4.0                                     | On-chip | On-chip     | _      | 4.5      | 5.5      | 0.10               |  |  |

| Corporation          | PBRC5.00HR      | 5.0                                     | On-chip | On-chip     | —      | 4.5      | 5.5      | 0.08               |  |  |

|                      | PBRC6.00HR      | 6.0                                     | On-chip | On-chip     | —      | 4.5      | 5.5      | 0.08               |  |  |

|                      | PBRC6.60HR      | 6.6                                     | On-chip | On-chip     | —      | 4.5      | 5.5      | 0.08               |  |  |

| TDK                  | FCR4.0MC5       | 4.0                                     | On-chip | On-chip     | —      | 4.5      | 5.5      | 0.14               |  |  |

|                      | FCR5.0MC5       | 5.0                                     | On-chip | On-chip     | —      | 4.5      | 5.5      | 0.14               |  |  |

|                      | FCR6.0MC5       | 6.0                                     | On-chip | On-chip     | —      | 4.5      | 5.5      | 0.11               |  |  |

| Murata Mfg.          | CSTS0400MG06    | 4.0                                     | On-chip | On-chip     | _      | 4.5      | 5.5      | 0.12               |  |  |

| Co., Ltd             | CSTCR4M00G05    | 4.0                                     | On-chip | On-chip     | _      | 4.5      | 5.5      | 0.14               |  |  |

|                      | CSTS0600MG06    | 6.0                                     | On-chip | On-chip     | _      | 4.5      | 5.5      | 0.14               |  |  |

|                      | CSTCR6M00G55-R0 | 6.0                                     | On-chip | On-chip     | —      | 4.5      | 5.5      | 0.18               |  |  |

Cautions 1. Connect the oscillator as closely to the X1 and X2 pins as possible.

2. Do not wire any other signal lines in the area indicated by the broken lines.

3. Thoroughly evaluate the matching between the  $\mu$ PD70F3003A and the resonator.

#### (b) µPD70F3025A

Cautions 1. Connect the oscillator as closely to the X1 and X2 pins as possible.

- 2. Do not wire any other signal lines in the area indicated by the broken lines.

- 3. Thoroughly evaluate the matching between the  $\mu$ PD70F3025A and the resonator.

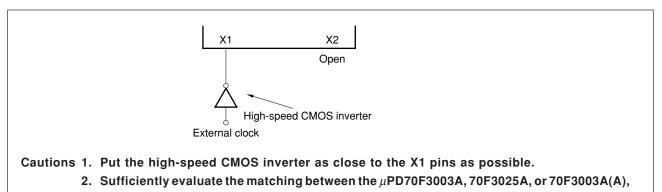

#### (2) External clock input

and the high-speed CMOS inverter.

|                                         |                 |                                                          |           |      |           | (1/  |

|-----------------------------------------|-----------------|----------------------------------------------------------|-----------|------|-----------|------|

| Parameter                               | Symbol          | Conditions                                               | MIN.      | TYP. | MAX.      | Unit |

| Input voltage, high                     | Vін             | Except X1 and Note                                       | 2.2       |      | VDD + 0.3 | V    |

|                                         |                 | Note                                                     | 0.8Vdd    |      | VDD + 0.3 | V    |

| Input voltage, low                      | VIL             | Except X1 and Note                                       | -0.5      |      | +0.8      | V    |

|                                         |                 | Note                                                     | -0.5      |      | 0.2Vdd    | V    |

| Clock input voltage, high               | Vхн             | X1                                                       | 0.8Vdd    |      | VDD + 0.5 | V    |

| Clock input voltage, low                | V <sub>XL</sub> | X1                                                       | -0.5      |      | 0.6       | V    |

| Schmitt trigger input threshold voltage | VT <sup>+</sup> | Note, rising                                             |           | 3.0  |           | V    |

|                                         | VT              | Note, falling                                            |           | 2.0  |           | V    |

| Schmitt trigger input hysteresis width  | $V_T^+ - V_T^-$ | Note                                                     | 0.5       |      |           | V    |

| Output voltage, high                    | Vон             | Іон = -2.5 mA                                            | 0.7Vdd    |      |           | V    |

|                                         |                 | Іон = -100 µА                                            | Vdd - 0.4 |      |           | V    |

| Output voltage, low                     | Vol             | loc = 2.5 mA                                             |           |      | 0.45      | V    |

| Input leakage current, high             | Іцн             | VI = VDD                                                 |           |      | 10        | μA   |

| Input leakage current, low              | ILIL            | $V_I = 0 V$                                              |           |      | -10       | μA   |

| Output leakage current, high            | Ігон            | Vo = Vdd                                                 |           |      | 10        | μA   |

| Output leakage current, low             | Ilol            | Vo = 0 V                                                 |           |      | -10       | μA   |

| Software pull-up resistor               | R               | P35/INTP131/SO3,<br>P36/INTP132/SI3,<br>P37/INTP133/SCK3 | 15        | 40   | 90        | kΩ   |

#### DC Characteristics (TA = -40 to +85°C, V\_DD = 5.0 V $\pm$ 10%, Vss = 0 V)

Note P02 to P07, P12 to P17, P23, P24, P26, P27, P32 to P37, P112 to P117, RESET, NMI, MODE, and their alternate-function pins.

**Remark** TYP. values are reference values for when  $T_A = 25^{\circ}C$  and  $V_{DD} = 5.0$  V.

|         |              |              |        |                          |      |                         |                         | (2/2) |

|---------|--------------|--------------|--------|--------------------------|------|-------------------------|-------------------------|-------|

|         | Parameter    | r            | Symbol | Conditions               | MIN. | TYP.                    | MAX.                    | Unit  |

| Supply  | µPD70F3003A, | Operating    |        | Direct mode              |      | $2.2 \times \phi + 7.5$ | $2.5 	imes \phi + 22$   | mA    |

| current | 70F3003A(A)  |              |        | PLL mode                 |      | $2.3 	imes \phi + 9.5$  | $2.6 \times \phi + 25$  | mA    |

|         |              | In HALT mode | DD2    | Direct mode              |      | $1.2 \times \phi + 7.5$ | $1.3 \times \phi + 15$  | mA    |

|         |              |              |        | PLL mode                 |      | $1.3 	imes \phi$ + 9.5  | $1.4 \times \phi + 17$  | mA    |

|         |              | In IDLE mode | IDD3   | Direct mode              |      | $8 	imes \phi$ + 300    | $10 \times \phi$ + 500  | μA    |

|         |              |              |        | PLL mode                 |      | $0.1 \times \phi + 2$   | $0.2 \times \phi + 3$   | mA    |

|         |              | In STOP mode | DD4    | CESEL = 0, Note 1        |      | 2                       | 50                      | μΑ    |

|         |              |              |        | CESEL = 0, Note 2        |      | 2                       | 200                     | μA    |

|         |              |              |        | CESEL = 1, Note 1        |      | 30                      | 200                     | μA    |

|         |              |              |        | CESEL = 1, Note 2        |      | 30                      | 500                     | μA    |

|         | µPD70F3025A  | Operating    | DD1    | Direct mode              |      | $2.5 	imes \phi + 8$    | $2.8 	imes \phi$ + 22.5 | mA    |

|         |              |              |        | PLL mode                 |      | $2.6 	imes \phi + 10$   | $2.9 	imes \phi$ + 25.5 | mA    |

|         |              | In HALT mode | IDD2   | Direct mode              |      | $1.3 	imes \phi$ + 7.5  | $1.4 	imes \phi$ + 15   | mA    |

|         |              |              |        | PLL mode                 |      | $1.3 	imes \phi$ + 12.5 | $1.4 	imes \phi$ + 20   | mA    |

|         |              | In IDLE mode | IDD3   | Direct mode              |      | $8 	imes \phi$ + 300    | $10 	imes \phi$ + 500   | μA    |

|         |              |              |        | PLL mode                 |      | $0.1 \times \phi + 2$   | $0.2 \times \phi + 3$   | mA    |

|         |              | In STOP mode | IDD4   | CESEL = 0, Note 1        |      | 2                       | 50                      | μA    |

|         |              |              |        | CESEL = 0, Note 2        |      | 2                       | 200                     | μΑ    |

|         |              |              |        | CESEL = 1, <b>Note 1</b> |      | 60                      | 300                     | μA    |

|         |              |              |        | CESEL = 1, Note 2        |      | 60                      | 500                     | μA    |

Notes 1.  $-40^{\circ}C \le T_A \le +50^{\circ}C$

**2.**  $50^{\circ}C < T_A \le 85^{\circ}C$

- **Remarks 1.** TYP. values are reference values for when T<sub>A</sub> = 25°C (except for the conditions in **Note 2**) and V<sub>DD</sub> = 5.0 V. The power supply current does not include AV<sub>REF1</sub> to AV<sub>REF3</sub> or the current that flows through software pull-up resistors.

- 2. *\phi*: Internal system clock frequency

| Parameter                                           | Symbol        | (            | Conditions        | MIN.     | TYP.     | MAX.     | Unit |

|-----------------------------------------------------|---------------|--------------|-------------------|----------|----------|----------|------|

| Data hold voltage                                   | Vdddr         | STOP mode    |                   | 1.5      |          | 5.5      | V    |

| Data hold current                                   | Idddr         | μPD70F3003A, | CESEL = 0, Note 1 |          | 0.4Vdddr | 50       | μA   |

|                                                     |               | 70F3003A(A)  | CESEL = 0, Note 2 |          | 0.4Vdddr | 200      | μA   |

|                                                     |               |              | CESEL = 1, Note 1 |          | 6Vdddr   | 200      | μA   |

|                                                     |               |              | CESEL = 1, Note 2 |          | 6Vdddr   | 500      | μA   |

|                                                     |               | μPD70F3025A  | CESEL = 0, Note 1 |          | 0.4Vdddr | 50       | μA   |

|                                                     |               |              | CESEL = 0, Note 2 |          | 0.4Vdddr | 200      | μA   |

|                                                     |               |              | CESEL = 1, Note 1 |          | 12Vdddr  | 300      | μA   |

|                                                     |               |              | CESEL = 1, Note 2 |          | 12VDDDR  | 500      | μA   |

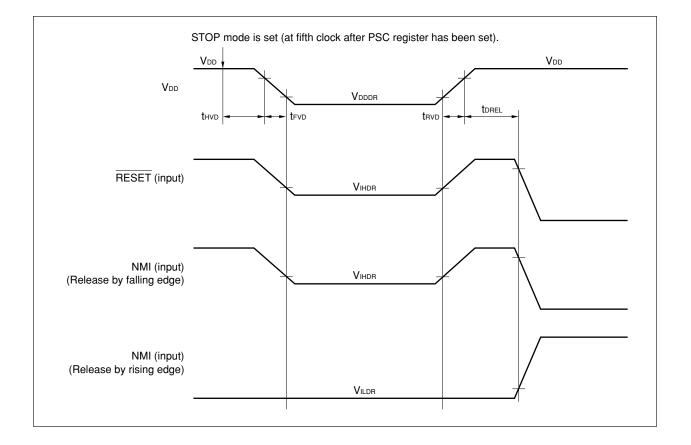

| Supply voltage rise time                            | <b>t</b> RVD  |              |                   | 200      |          |          | μs   |

| Supply voltage fall time                            | <b>t</b> fvd  |              |                   | 200      |          |          | μs   |

| Supply voltage hold time<br>(vs. STOP mode setting) | <b>t</b> hvd  |              |                   | 0        |          |          | ms   |

| STOP mode release signal input time                 | <b>t</b> drel |              |                   | 0        |          |          | ns   |

| Data hold input voltage, high                       | VIHDR         | Note 3       |                   | 0.9Vdddr |          | Vdddr    | V    |

| Data hold input voltage, low                        | Vildr         | Note 3       |                   | 0        |          | 0.1Vdddr | V    |

#### Data Retention Characteristics (TA = -40 to $+85^{\circ}C$ , VDD = VDDDR)

Notes 1.  $-40^{\circ}C \le T_A \le +50^{\circ}C$

- **2.**  $50^{\circ}C < T_{A} \le 85^{\circ}C$

- **3.** P02 to P07, P12 to P17, P23, P24, P26, P27, P32 to P37, P112 to P117, RESET, NMI, MODE, X1, and their alternate-function pins.

- **Remark** TYP. values are reference values for when  $T_A = 25^{\circ}C$  (except for the conditions in **Note 2**) and  $V_{DD} = 5.0 \text{ V}$ .

AC Characteristics (TA = -40 to +85°C, VDD = 5.0 V  $\pm$ 10%, Vss = 0 V)

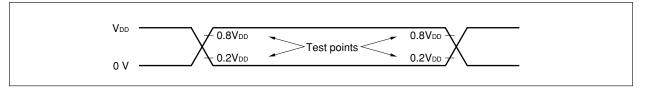

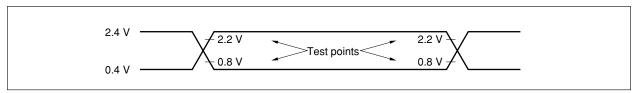

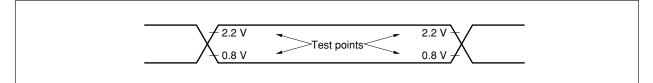

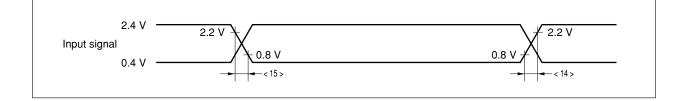

AC test input test points

(a) P02 to P07, P12 to P17, P23, P24, P26, P27, P32 to P37, P112 to P117, RESET, NMI, MODE, X1, and their alternate-function pins

(b) Other than (a)

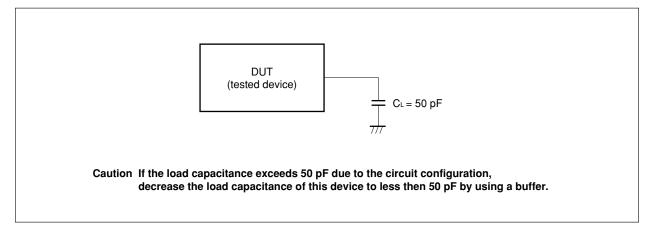

#### AC test output test points

#### Load condition

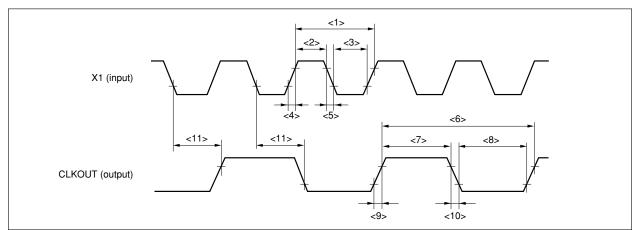

#### (1) Clock timing

| Parameter                                     | S    | /mbol | Conditions                    | MIN.                  | MAX.   | Unit |

|-----------------------------------------------|------|-------|-------------------------------|-----------------------|--------|------|

| X1 input cycle                                | <1>  | tcyx  | Direct mode                   | 15                    | Note 1 | ns   |

|                                               |      |       | PLL mode<br>(PLL lock status) | 151 <sup>Note 2</sup> | Note 3 | ns   |

| X1 input width, high                          | <2>  | twxн  | Direct mode                   | 6                     |        | ns   |

|                                               |      |       | PLL mode                      | 60                    |        | ns   |

| X1 input width, low                           | <3>  | twx∟  | Direct mode                   | 6                     |        | ns   |

|                                               |      |       | PLL mode                      | 60                    |        | ns   |

| X1 input rise time                            | <4>  | tхв   | Direct mode                   |                       | 7      | ns   |

|                                               |      |       | PLL mode                      |                       | 10     | ns   |

| X1 input fall time                            | <5>  | txF   | Direct mode                   |                       | 7      | ns   |

|                                               |      |       | PLL mode                      |                       | 10     | ns   |

| CPU operating frequency                       | _    | φ     |                               | Note 4                | 33     | MHz  |

| CLKOUT output cycle                           | <6>  | tсүк  |                               | 30                    | Note 5 | ns   |

| CLKOUT width, high                            | <7>  | twкн  |                               | 0.5 T – 5             |        | ns   |

| CLKOUT width, low                             | <8>  | twĸ∟  |                               | 0.5 T – 5             |        | ns   |

| CLKOUT rise time                              | <9>  | tхя   |                               |                       | 5      | ns   |

| CLKOUT fall time                              | <10> | txF   |                               |                       | 5      | ns   |

| X1 $\downarrow \rightarrow$ CLKOUT delay time | <11> | tdxк  | Direct mode                   | 3                     | 17     | ns   |

Notes 1. When A/D converter used: 100 ns

When A/D converter not used: 250 ns

**2.** When using A/D converter: The value when  $\phi = 5 \times fxx$  and  $\phi = fxx$  are set. Setting  $\phi = 1/2 \times fxx$  is prohibited.

When not using A/D converter: The value when  $\phi = 5 \times fxx$ ,  $\phi = fxx$ , and  $\phi = 1/2 \times fxx$  are set.

**3.** When using A/D converter: 250 ns (when  $\phi = 5 \times fxx$  is set) and 200 ns (when  $\phi = fxx$  is set). Setting  $\phi = 1/2 \times fxx$  is prohibited.

When not using A/D converter: 250 ns (when  $\phi = 5 \times fxx$ ,  $\phi = fxx$ , and  $\phi = 1/2 \times fxx$  are set).

- When A/D converter used: 5 MHz When A/D converter not used: 2 MHz

- When A/D converter used: 200 ns When A/D converter not used: 500 ns

Remark T = tcyk

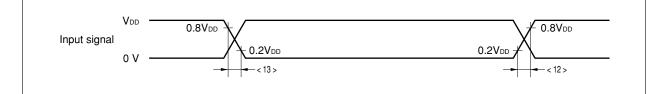

#### (2) Input wave

# (a) P02 to P07, P12 to P17, P23, P24, P26, P27, P32 to P37, P112 to P117, RESET, NMI, MODE, and their alternate-function pins

| Parameter       | Symbol |      | Conditions | MIN. | MAX. | Unit |

|-----------------|--------|------|------------|------|------|------|

| Input rise time | <12>   | tir2 |            |      | 20   | ns   |

| Input fall time | <13>   | tiF2 |            |      | 20   | ns   |

#### (b) Other than (a)

| Parameter       | Symbol |      | Conditions | MIN. | MAX. | Unit |

|-----------------|--------|------|------------|------|------|------|

| Input rise time | <14>   | tin1 |            |      | 10   | ns   |

| Input fall time | <15>   | tiF1 |            |      | 10   | ns   |

#### (3) Output wave (other than CLKOUT)

| Parameter        | Sy   | vmbol | Conditions | MIN. | MAX. | Unit |

|------------------|------|-------|------------|------|------|------|

| Output rise time | <16> | tor   |            |      | 10   | ns   |

| Output fall time | <17> | tof   |            |      | 10   | ns   |

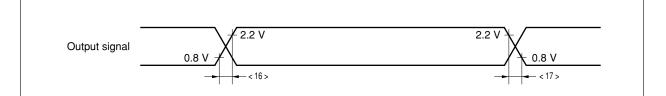

#### (4) Reset timing

| Parameter         | S    | ymbol | Conditions                                                               | MIN.       | MAX. | Unit |

|-------------------|------|-------|--------------------------------------------------------------------------|------------|------|------|

| RESET width, high | <18> | twrsh |                                                                          | 500        |      | ns   |

| RESET width, low  | <19> | twrsl | On power appli-<br>cation, or on<br>releasing STOP<br>mode               | 500 + Tost |      | ns   |

|                   |      |       | Except on power<br>application, or<br>except on releas-<br>ing STOP mode | 500        |      | ns   |

Remark Tost: Oscillation stabilization time

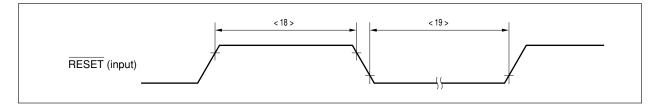

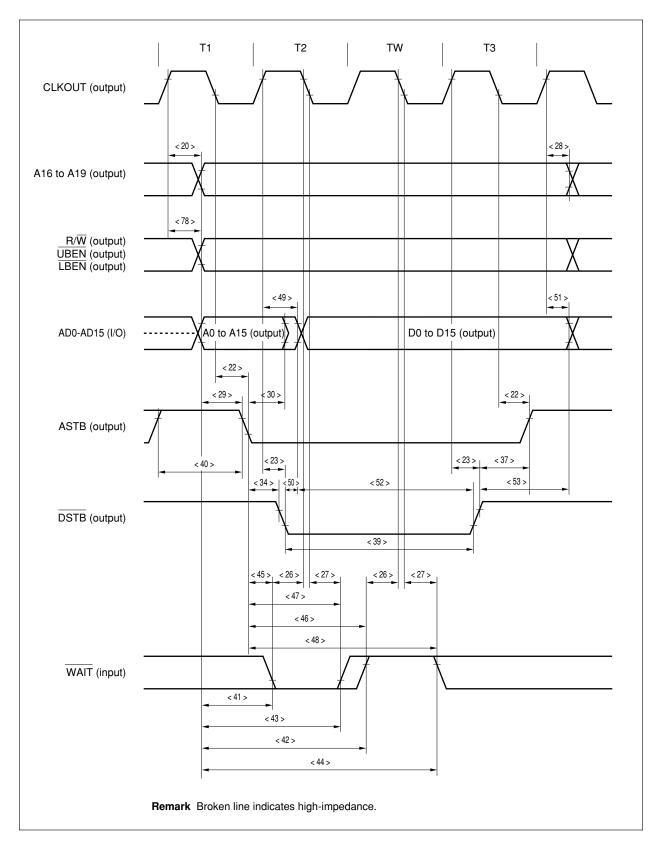

#### (5) Read timing (1/2)

| Parameter                                                             | Sy   | /mbol          | Conditions                                       | MIN.             | MAX.             | Unit |

|-----------------------------------------------------------------------|------|----------------|--------------------------------------------------|------------------|------------------|------|

| Delay time from CLKOUT↑ to address                                    | <20> | <b>t</b> dka   |                                                  | 3                | 20               | ns   |

| Delay time from CLKOUT↑ to R/W, UBEN, LBEN                            | <78> | tdka2          |                                                  | -2               | +13              | ns   |

| Delay time from CLKOUT <sup>↑</sup> to address float                  | <21> | tfka           |                                                  | 3                | 15               | ns   |

| Delay time from CLKOUT↓ to ASTB                                       | <22> | <b>t</b> dkst  |                                                  | 3                | 15               | ns   |

| Delay time from CLKOUT↓ to DSTB                                       | <23> | <b>t</b> dkd   |                                                  | 3                | 15               | ns   |

| Data input setup time (to CLKOUT <sup>↑</sup> )                       | <24> | <b>t</b> sidk  |                                                  | 5                |                  | ns   |

| Data input hold time (from CLKOUT <sup>↑</sup> )                      | <25> | tнкір          |                                                  | 5                |                  | ns   |

| $\overline{\text{WAIT}}$ setup time (to CLKOUT $\downarrow$ )         | <26> | tswтк          |                                                  | 5                |                  | ns   |

| $\overline{\text{WAIT}}$ hold time (from CLKOUT $\downarrow$ )        | <27> | tнкwт          |                                                  | 5                |                  | ns   |

| Address hold time (from CLKOUT <sup>↑</sup> )                         | <28> | tнка           |                                                  | 0                |                  | ns   |

| Address setup time (to ASTB $\downarrow$ )                            | <29> | <b>t</b> sast  | $-40^\circ C \leq T_A \leq +70^\circ C$          | 0.5 T – 10       |                  | ns   |

|                                                                       |      |                | $70^\circ C < T_A \le 85^\circ C$                | 0.5 T – 12       |                  | ns   |

| Address hold time (from ASTB $\downarrow$ )                           | <30> | <b>t</b> hsta  |                                                  | 0.5 T – 10       |                  | ns   |

| Delay time from $\overline{\text{DSTB}}{\downarrow}$ to address float | <31> | <b>t</b> fda   |                                                  |                  | 0                | ns   |

| Data input setup time (to address)                                    | <32> | tsaid          | $-40^\circ C \leq T_A \leq +70^\circ C$          |                  | (2 + n) T – 22   | ns   |

|                                                                       |      |                | $70^\circ C < T_A \le 85^\circ C$                |                  | (2 + n) T – 25   | ns   |

| Data input setup time (to $\overline{\text{DSTB}}\downarrow$ )        | <33> | tsdid          | $-40^\circ C \leq T_A \leq +70^\circ C$          |                  | (1 + n) T - 20   | ns   |

|                                                                       |      |                | $70^\circ C < T_A \le 85^\circ C$                |                  | (1 + n) T – 24   | ns   |

| Delay time from ASTB $\downarrow$ to $\overline{DSTB}\downarrow$      | <34> | <b>t</b> dstd  |                                                  | 0.5 T – 10       |                  | ns   |

| Data input hold time (from $\overline{\text{DSTB}}^{\uparrow}$ )      | <35> | thdid          |                                                  | 0                |                  | ns   |

| Delay time from $\overline{\text{DSTB}}\uparrow$ to address output    | <36> | tdda           |                                                  | (1 + i) T        |                  | ns   |

| Delay time from DSTB↑ to ASTB↑                                        | <37> | <b>t</b> ddsth |                                                  | 0.5 T – 10       |                  | ns   |

| Delay time from $\overline{DSTB}$ to $ASTB\downarrow$                 | <38> | <b>t</b> ddstl |                                                  | (1.5 + i) T – 10 |                  | ns   |

| DSTB low-level width                                                  | <39> | twdl           | $-40^\circ C \leq T_A \leq +70^\circ C$          | (1 + n) T - 10   |                  | ns   |

|                                                                       |      |                | $70^\circ C < T_A \le 85^\circ C$                | (1 + n) T – 13   |                  | ns   |

| ASTB high-level width                                                 | <40> | twsтн          |                                                  | T – 10           |                  | ns   |

| WAIT setup time (to address)                                          | <41> | tsawt1         | $n \geq 1,-40^\circ C \leq T_A \leq +70^\circ C$ |                  | 1.5 T – 20       | ns   |

|                                                                       |      |                | $n \geq 1,~70^\circ C < T_A \leq 85^\circ C$     |                  | 1.5 T – 24       | ns   |

|                                                                       | <42> | tsawt2         | $n \geq 1,-40^\circ C \leq T_A \leq +70^\circ C$ |                  | (1.5 + n) T – 20 | ns   |

|                                                                       |      |                | $n \geq 1, \ 70^\circ C < T_A \leq 85^\circ C$   |                  | (1.5 + n) T – 24 | ns   |

| WAIT hold time (from address)                                         | <43> | thawt1         | $n \ge 1$                                        | (0.5 + n) T      |                  | ns   |

|                                                                       | <44> | thawt2         | n ≥ 1                                            | (1.5 + n) T      |                  | ns   |

| WAIT setup time (to ASTB↓)                                            | <45> | tsstwt1        | $n \geq 1,-40^\circ C \leq T_A \leq +70^\circ C$ |                  | T – 18           | ns   |

|                                                                       |      |                | $n \geq 1,\ 70^\circ C < T_A \leq 85^\circ C$    |                  | T – 20           | ns   |

|                                                                       | <46> | tsstwt2        | n ≥ 1                                            |                  | (1 + n) T – 15   | ns   |

| $\overline{\text{WAIT}}$ hold time (from ASTB $\downarrow$ )          | <47> | thstwt1        | n ≥ 1                                            | nT               |                  | ns   |

|                                                                       | <48> | tHSTWT2        | n ≥ 1                                            | (1 + n) T        |                  | ns   |

#### Remarks 1. T = tcyk

- 2. n indicates the number of wait clocks inserted in the bus cycle. The sampling timing differs when the programmable wait state is inserted.

- **3.** i indicates the number of idle states (0 or 1) t be inserted in the read cycle.

- 4. Be sure to observe at least one of data input hold times their (<25>) and their (<35>).

#### (5) Read Timing (2/2): 1 wait

#### (6) Write timing (1/2)

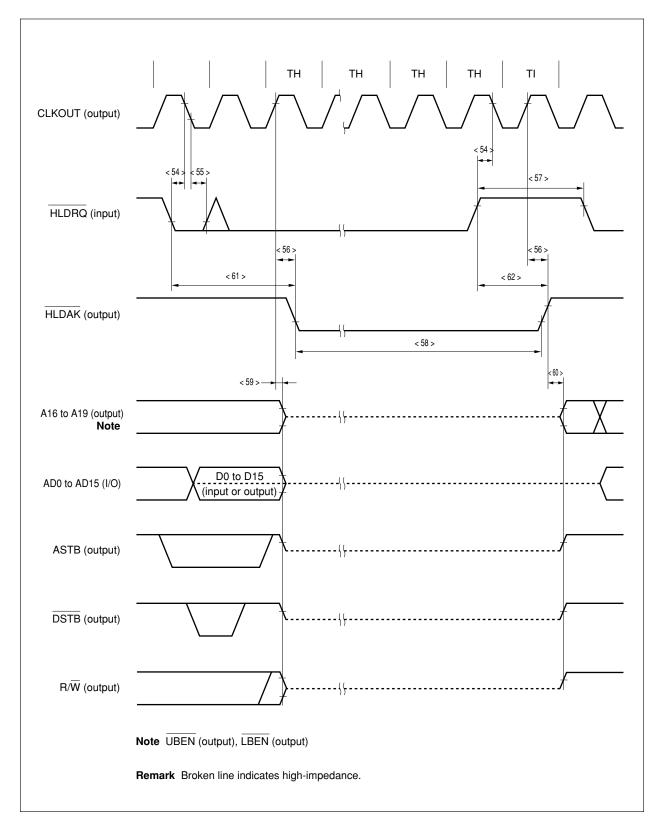

| Parameter                                                               | Sy   | /mbol         | Conditions                                         | MIN.           | MAX.             | Unit |

|-------------------------------------------------------------------------|------|---------------|----------------------------------------------------|----------------|------------------|------|

| Delay time from CLKOUT↑ to address                                      | <20> | <b>t</b> dka  |                                                    | 3              | 20               | ns   |

| Delay time from CLKOUT↑ to R/W, UBEN, LBEN                              | <78> | tdka2         |                                                    | -2             | +13              | ns   |

| Delay time from CLKOUT $\downarrow$ to ASTB                             | <22> | <b>t</b> dkst |                                                    | 3              | 15               | ns   |

| Delay time from CLKOUT↑ to DSTB                                         | <23> | <b>t</b> dkd  |                                                    | 3              | 15               | ns   |

| $\overline{\text{WAIT}}$ setup time (to CLKOUT $\downarrow$ )           | <26> | tswтк         |                                                    | 5              |                  | ns   |

| WAIT hold time (from CLKOUT↓)                                           | <27> | tнкwт         |                                                    | 5              |                  | ns   |

| Address hold time (from CLKOUT <sup>↑</sup> )                           | <28> | tнка          |                                                    | 0              |                  | ns   |

| Address setup time (to ASTB $\downarrow$ )                              | <29> | <b>t</b> sast | $-40^\circ C \leq T_A \leq +70^\circ C$            | 0.5 T – 10     |                  | ns   |

|                                                                         |      |               | $70^\circ C < T_A \le 85^\circ C$                  | 0.5 T – 12     |                  | ns   |

| Address hold time (from ASTB $\downarrow$ )                             | <30> | <b>t</b> hsta |                                                    | 0.5 T – 10     |                  | ns   |

| Delay time from ASTB $\downarrow$ to $\overline{\text{DSTB}}\downarrow$ | <34> | <b>t</b> dstd |                                                    | 0.5 T – 10     |                  | ns   |

| Delay time from DSTB↑ to ASTB↑                                          | <37> | tddsth        |                                                    | 0.5 T – 10     |                  | ns   |

| DSTB low-level width                                                    | <39> | twdl          | $-40^\circ C \leq T_A \leq +70^\circ C$            | (1 + n) T - 10 |                  | ns   |

|                                                                         |      |               | $70^\circ C < T_A \le 85^\circ C$                  | (1 + n) T – 13 |                  | ns   |

| ASTB high-level width                                                   | <40> | twsтн         |                                                    | T — 10         |                  | ns   |

| WAIT setup time (to address)                                            | <41> | tsawt1        | $n \geq 1,  -40^\circ C \leq T_A \leq +70^\circ C$ |                | 1.5 T – 20       | ns   |