#### INTEGRATED CIRCUITS

### DATA SHEET

# SAA8103 Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

Objective specification File under Integrated Circuits, IC02

2001 Oct 22

### **Pulse Pattern Generator for Frame Transfer CCD (PPGFT)**

**SAA8103**

#### **CONTENTS**

| 1                        | FEATURES                                                                         |

|--------------------------|----------------------------------------------------------------------------------|

| 2                        | APPLICATIONS                                                                     |

| 3                        | GENERAL DESCRIPTION                                                              |

| 4                        | QUICK REFERENCE DATA                                                             |

| 5                        | ORDERING INFORMATION                                                             |

| 6                        | BLOCK DIAGRAMS                                                                   |

| 7                        | PINNING INFORMATION                                                              |

| 7.1<br>7.2               | Pinning Pin description                                                          |

| 8                        | FUNCTIONAL DESCRIPTION                                                           |

| 9                        | OPERATING MODES                                                                  |

| 9.1<br>9.2<br>9.3<br>9.4 | Full Frame CCD Frame Transfer CCD Standby control function Standby mode sequence |

| 10                       | SERIAL INTERFACES                                                                |

| 10.1                     | Control for V-driver (TDA9991) and CDS or ADC                                    |

| 11                       | COMMAND LIST                                                                     |

| 12                       | TIMING DIAGRAMS                                                                  |

| 13                       | LIMITING VALUES                                                                  |

| 14                       | THERMAL CHARACTERISTICS                                                          |

| 15                       | DC CHARACTERISTICS                                                               |

| 16                       | APPLICATION INFORMATION                                                          |

| 17                       | PACKAGE OUTLINE                                                                  |

| 18                       | SOLDERING                                                                        |

| 18.1                     | Introduction to soldering surface mount packages                                 |

| 18.2                     | Reflow soldering                                                                 |

| 18.3<br>18.4             | Wave soldering<br>Manual soldering                                               |

| 18.5                     | Suitability of surface mount IC packages for wave and reflow soldering methods   |

| 19                       | DATA SHEET STATUS                                                                |

| 20                       | DEFINITIONS                                                                      |

| 21                       | DISCLAIMERS                                                                      |

| 22                       | PURCHASE OF PHILIPS I2C COMPONENTS                                               |

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

#### 1 FEATURES

- · Sync signal generator

- · Supports progressive scan operation

- Supports monitoring function

- Supports electronic shutter function

- Supports Frame Transfer CCD (FXA, FTF and FTT) 8 × 8-kbyte pixels (maximum)

- Supports 1, 2 and 4 output functions with Full Frame CCD type sensor

- · Generates the system clock for signal processing

- · Base oscillation from 6 to 28 MHz

- I<sup>2</sup>C-bus control.

#### 2 APPLICATIONS

- · CCD camera

- · Digital still camera.

#### 3 GENERAL DESCRIPTION

The SAA8103 is a pulse pattern generator for the Frame Transfer CCD image sensors: FXA1012, FXA1013, FXA1022, FXA1004, FTF2020, FTF3020 and FTT1010 as well as for the front-end analog processing and signal processing circuit.

The circuit generates drive pulses for the CCD, sample-hold pulses for Correlated Double Sampling (CDS), clamp pulses and sync signals.

#### 4 QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                                                                                                                                            | MIN. | TYP. | MAX.     | UNIT |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|

| $V_{DDDx}$          | digital supply voltages: $V_{DDD1}$ , $V_{DDD2}$ , $V_{DDD3}$ , $V_{DDD4}$ and $V_{DD(OSC)}$                                                         | 3.0  | 3.3  | 3.6      | V    |

| $V_{DDAx}$          | analog supply voltages: V <sub>DDA(BUF1)</sub> , V <sub>DDA(BUF2)</sub> , V <sub>DDA(BUF3)</sub> , V <sub>DDA(DLL1)</sub> and V <sub>DDA(DLL2)</sub> | 3.0  | 3.3  | 3.6      | V    |

| I <sub>P(tot)</sub> | total power supply current (f <sub>CLK</sub> = 25 MHz)                                                                                               | _    | 65   | _        | mA   |

| V <sub>IL</sub>     | LOW-level input voltages                                                                                                                             | _    | _    | 0.8      | V    |

| V <sub>IH</sub>     | HIGH-level input voltages                                                                                                                            | 2.3  | _    | $V_{DD}$ | V    |

| V <sub>OL</sub>     | LOW-level output voltages                                                                                                                            | _    | _    | 0.5      | V    |

| V <sub>OH</sub>     | HIGH-level output voltages                                                                                                                           | 2.3  | _    | $V_{DD}$ | V    |

| T <sub>amb</sub>    | operating ambient temperature range                                                                                                                  | -20  | +25  | +70      | °C   |

#### 5 ORDERING INFORMATION

| TYPE NUMBER  |        | PACKAGE                                                                            |          |

|--------------|--------|------------------------------------------------------------------------------------|----------|

| TIPE NOWIBER | NAME   | DESCRIPTION                                                                        | VERSION  |

| SAA8103HL    | LQFP64 | plastic low profile quad flat package; 64 leads; body $10 \times 10 \times 1.4$ mm | SOT314-2 |

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

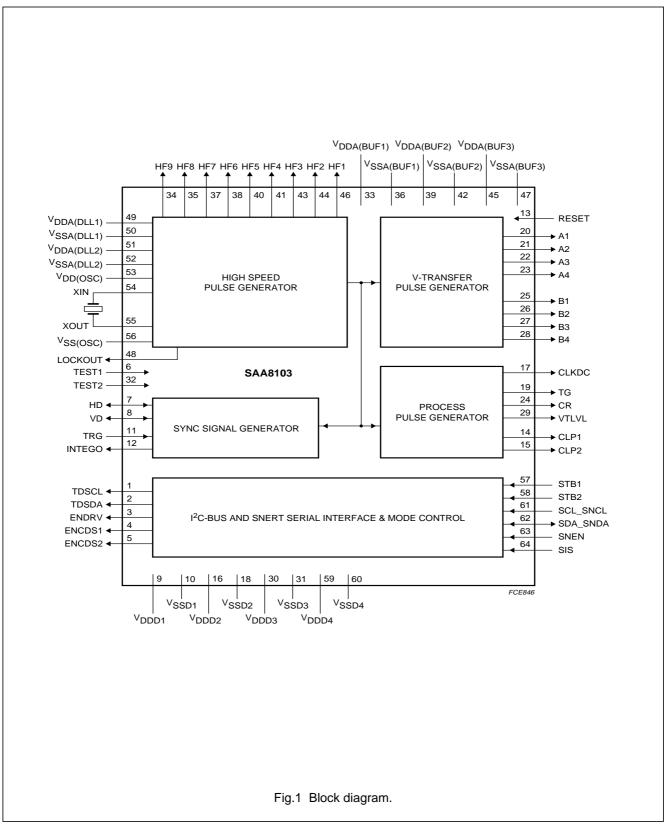

#### 6 BLOCK DIAGRAMS

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

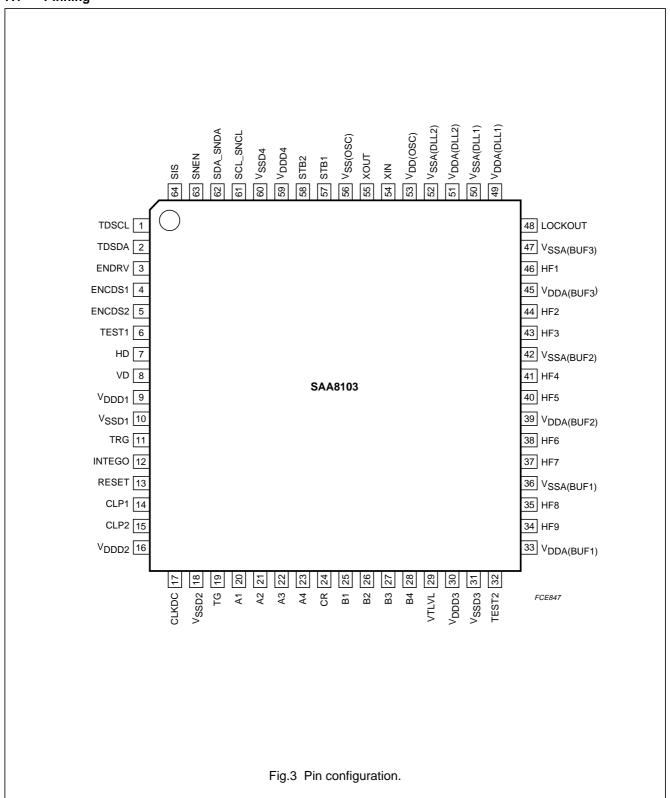

#### 7 PINNING INFORMATION

#### 7.1 Pinning

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

#### 7.2 Pin description

Table 1 Pin description for LQFP64 package

| SYMBOL                 | PIN | I/O    | DESCRIPTION                                                                                                                                        |  |

|------------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

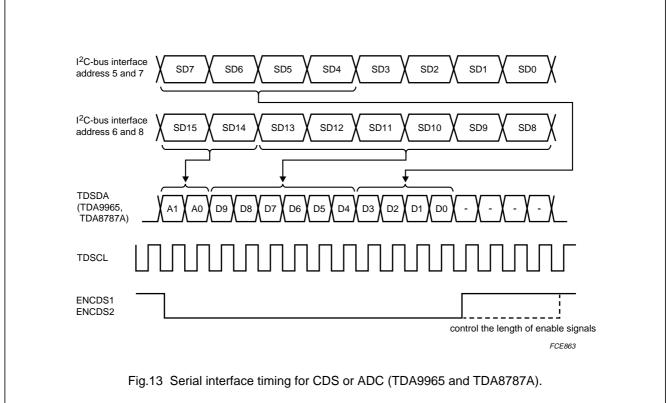

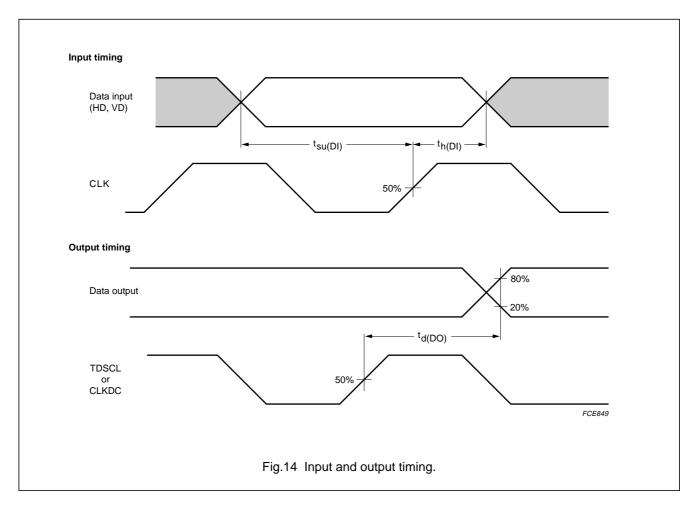

| TDSCL                  | 1   | 0      | serial interface clock output for CDS/ADC and V-driver                                                                                             |  |

| TDSDA                  | 2   | 0      | serial interface data output for CDS/ADC and V-driver                                                                                              |  |

| ENDRV                  | 3   | 0      | serial interface enable output for V-driver                                                                                                        |  |

| ENCDS1                 | 4   | 0      | serial interface enable output 1 for CDS/ADC                                                                                                       |  |

| ENCDS2                 | 5   | 0      | serial interface enable output 2 for CDS/ADC                                                                                                       |  |

| TEST1                  | 6   | I      | test input 1; normally connected to ground                                                                                                         |  |

| HD                     | 7   | I/O    | horizontal drive signal input or output; alternative function HREF signal output is controlled by the serial interface; see Chapter 11, address 12 |  |

| VD                     | 8   | I/O    | vertical drive signal input or output; alternative function VREF signal output is controlled by the serial interface; see Chapter 11, address 12   |  |

| V <sub>DDD1</sub>      | 9   | supply | digital supply voltage 1 for core                                                                                                                  |  |

| V <sub>SSD1</sub>      | 10  | supply | digital ground 1 for core                                                                                                                          |  |

| TRG                    | 11  | I      | trigger signal input                                                                                                                               |  |

| INTEGO                 | 12  | 0      | integration time signal output                                                                                                                     |  |

| RESET                  | 13  | I      | power-on reset, normally connected to ground                                                                                                       |  |

| CLP1                   | 14  | 0      | optical black clamp control pulse output                                                                                                           |  |

| CLP2                   | 15  | 0      | clamp control pulse output for the Analog-to-Digital Convertor (ADC)                                                                               |  |

| $V_{DDD2}$             | 16  | supply | digital supply voltage 2                                                                                                                           |  |

| CLKDC                  | 17  | 0      | clock signal output (for the DC-to-DC convertor of TDA9991)                                                                                        |  |

| V <sub>SSD2</sub>      | 18  | supply | digital ground 2                                                                                                                                   |  |

| TG                     | 19  | 0      | transfer gate pulse output                                                                                                                         |  |

| A1                     | 20  | 0      | clock output 1 for CCD vertical register drive                                                                                                     |  |

| A2                     | 21  | 0      | clock output 2 for CCD vertical register drive                                                                                                     |  |

| A3                     | 22  | 0      | clock output 3 for CCD vertical register drive                                                                                                     |  |

| A4                     | 23  | 0      | clock output 4 for CCD vertical register drive                                                                                                     |  |

| CR                     | 24  | 0      | charge reset pulse output                                                                                                                          |  |

| B1                     | 25  | 0      | clock output 1 for CCD vertical register drive                                                                                                     |  |

| B2                     | 26  | 0      | clock output 2 for CCD vertical register drive                                                                                                     |  |

| B3                     | 27  | 0      | clock output 3 for CCD vertical register drive                                                                                                     |  |

| B4                     | 28  | 0      | clock output 4 for CCD vertical register drive                                                                                                     |  |

| VTLVL                  | 29  | 0      | vertical transport level pulse output                                                                                                              |  |

| $V_{DDD3}$             | 30  | supply | digital supply voltage 3                                                                                                                           |  |

| V <sub>SSD3</sub>      | 31  | supply | digital ground 3                                                                                                                                   |  |

| TEST2                  | 32  | I      | test input 2; normally connected to ground                                                                                                         |  |

| V <sub>DDA(BUF1)</sub> | 33  | supply | analog supply voltage for output buffer 1                                                                                                          |  |

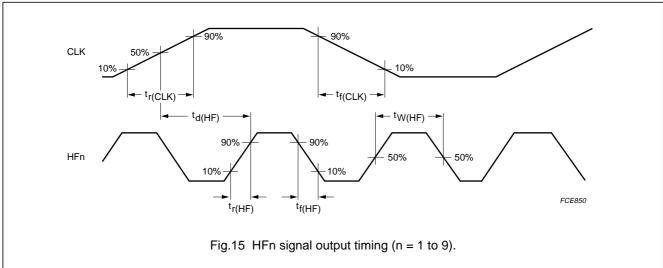

| HF9                    | 34  | 0      | high frequency output 9                                                                                                                            |  |

| HF8                    | 35  | 0      | high frequency output 8                                                                                                                            |  |

| V <sub>SSA(BUF1)</sub> | 36  | supply | analog ground for output buffer 1                                                                                                                  |  |

| HF7                    | 37  | 0      | high frequency output 7                                                                                                                            |  |

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

| SYMBOL                 | PIN | I/O    | DESCRIPTION                                                                     |

|------------------------|-----|--------|---------------------------------------------------------------------------------|

| HF6                    | 38  | 0      | high frequency output 6                                                         |

| V <sub>DDA(BUF2)</sub> | 39  | supply | analog supply voltage for output buffer 2                                       |

| HF5                    | 40  | 0      | high frequency output 5                                                         |

| HF4                    | 41  | 0      | high frequency output 4                                                         |

| V <sub>SSA(BUF2)</sub> | 42  | supply | analog ground for output buffer 2                                               |

| HF3                    | 43  | 0      | high frequency output 3                                                         |

| HF2                    | 44  | 0      | high frequency output 2                                                         |

| V <sub>DDA(BUF3)</sub> | 45  | supply | analog supply voltage for output buffer 3                                       |

| HF1                    | 46  | 0      | high frequency output 1                                                         |

| V <sub>SSA(BUF3)</sub> | 47  | supply | analog ground for output buffer 3                                               |

| LOCKOUT                | 48  | 0      | lock indication of Delayed Locked Loop (DLL)                                    |

| V <sub>DDA(DLL1)</sub> | 49  | supply | analog supply voltage for DLL1 (core)                                           |

| V <sub>SSA(DLL1)</sub> | 50  | supply | analog ground for DLL1 (core)                                                   |

| V <sub>DDA(DLL2)</sub> | 51  | supply | analog supply voltage for DLL2                                                  |

| V <sub>SSA(DLL2)</sub> | 52  | supply | analog ground for DLL2                                                          |

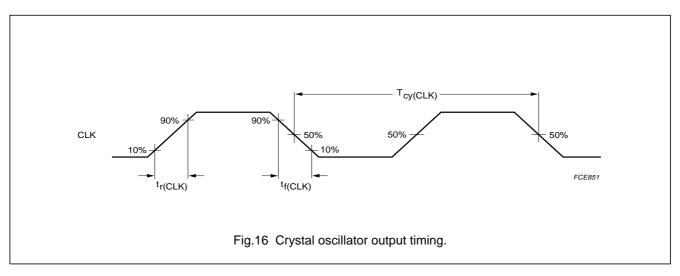

| V <sub>DD(OSC)</sub>   | 53  | supply | digital supply voltage for crystal oscillator                                   |

| XIN                    | 54  | I/O    | inverter input for crystal oscillator                                           |

| XOUT                   | 55  | I/O    | inverter output for crystal oscillator                                          |

| V <sub>SS(OSC)</sub>   | 56  | supply | digital ground for crystal oscillator                                           |

| STB1                   | 57  | I      | standby control function inputs; see Section 9.4                                |

| STB2                   | 58  | I      |                                                                                 |

| V <sub>DDD4</sub>      | 59  | supply | digital supply voltage 4                                                        |

| V <sub>SSD4</sub>      | 60  | supply | digital ground 4                                                                |

| SCL_SNCL               | 61  | I      | I <sup>2</sup> C-bus/SNERT serial interface clock input                         |

| SDA_SNDA               | 62  | I/O    | I <sup>2</sup> C-bus/SNERT serial interface data input/output; 8 mA and 400 kHz |

| SNEN                   | 63  | I      | SNERT enable input                                                              |

| SIS                    | 64  | I      | I <sup>2</sup> C-bus/SNERT selection                                            |

#### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

#### **FUNCTIONAL DESCRIPTION**

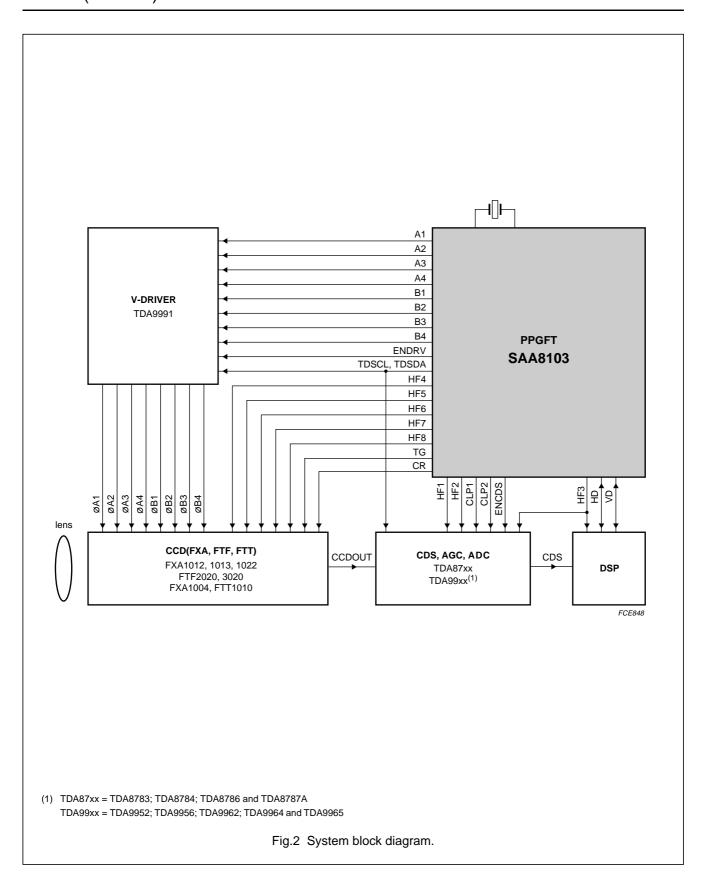

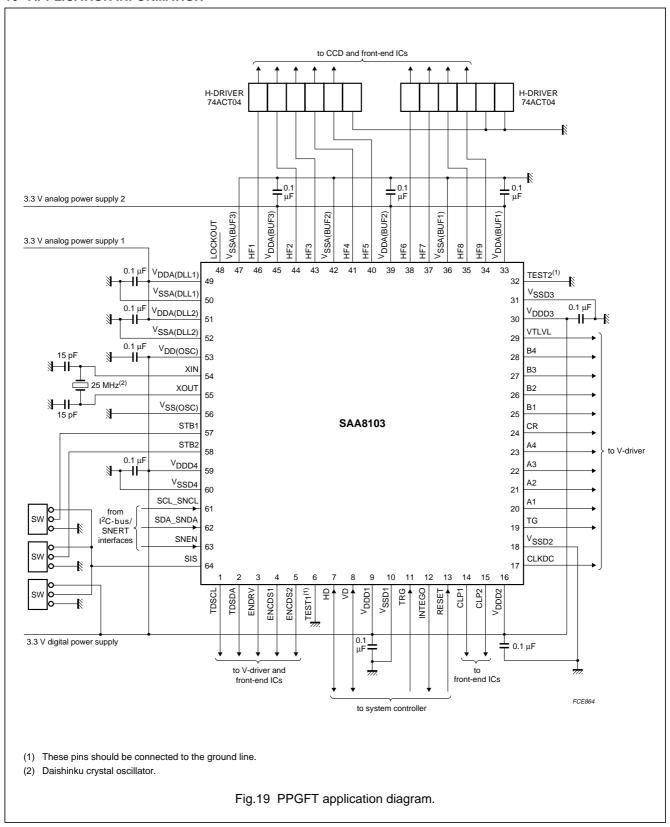

The SAA8103 is a drive pulse generator for the FXA1004, FXA1012, FXA1013, FXA1022, FTF2020, FTF3020 and the FTT1010. The SAA8103 also drives the CDS, ADC front-end, V-driver and the Digital Signal Processor (DSP). The system block diagram is shown in Fig.2.

The SAA8103 generates horizontal and vertical drive signals, summing and reset gate pulses for each CCD, sample-hold pulses and clamp pulses for the front-end devices TDA99xx and TDA87xx(1), and also generates sync signals HD and VD and the reference signals HREF and VREF for the DSP. The SAA8103 can also take sync signals HD and VD as external inputs, the drive signals generated will then be synchronized to these signals.

The SAA8103 is designed to operate with an 8192-line (maximum) × 8192-pixel (maximum) RGB Bayer CCD (FXA, FTF and FTT). Progressive scan and sub-sampling modes for these CCDs can be used.

The device supports three different modes for the data read-out of each CCD: Normal mode, Shot mode and Preview mode. The SAA8103 also supports electronic shutter function and will provide exact settings of shutter speed and exposure time.

The drive signals for CCD are generated from the main oscillator and range from 6 to 28 MHz. The drive signals are generated by a programmable generator from the main oscillator. The vertical drive signals are provided for the TDA9991, horizontal drive signals are provided for the CCD directly or H-driver, sample-hold pulses and clamp pulses are provided for the TDA99xx or TDA87xx, sync signals HD, VD and reference signals HREF and VREF are provided for the DSP.

The drive pulses are controlled by a microcontroller via one of the serial interfaces (I<sup>2</sup>C-bus or SNERT). The SAA8103 takes address and data from the I<sup>2</sup>C-bus or SNERT, and decodes these inputs for internal logic. It also decodes these inputs for the SNERT interface of the TDA99xx, TDA87xx and TDA9991.

The basic digital camera system consists of a CCD image sensor, a vertical driver and a Pulse Pattern Generator (PPG) for the CCD, an analog front-end (CDS, AGC and ADC) and Digital Signal Processor.

The high resolution digital camera system can be built using the FTF3020, TDA9965 and TDA9991 devices.

2001 Oct 22 9

<sup>(1)</sup> TDA99xx = TDA9952; TDA9956; TDA9962; TDA9964; TDA9965

TDA87xx = TDA8783: TDA8784: TDA8786: TDA8787A

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

#### 9 OPERATING MODES

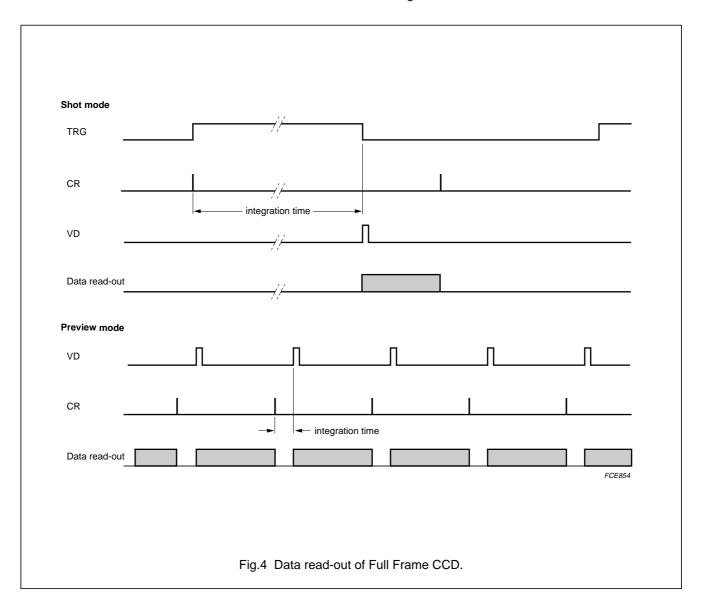

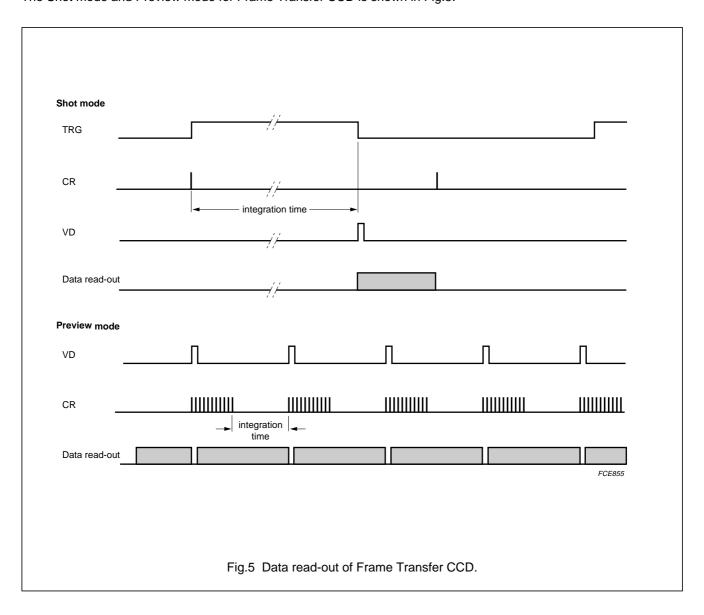

For Full Frame CCD and Frame Transfer CCD there are two modes for data read-out: Shot mode and Preview mode. Shot mode is used to take an image using an external trigger signal; e.g. camera shutter. Preview mode is used to take an image continuously with a fixed (preset) integration; e.g. to show an image on the LCD display of a Digital Still Camera (DSC).

#### 9.1 Full Frame CCD

In the Shot mode, the SAA8103 takes the external input signal TRG, as the trigger signal. After the rising edge of TRG, the charge reset pulses (CR) are generated for the appropriate period. Integration time is held until the falling edge of the TRG signal. A drive signal is generated in each VD period but is not issued until the next event of the TRG signal.

In the Preview mode, the SAA8103 generates a drive signal in every frame. The Preview mode it is not influenced by the TRG signal. The integration time is controlled using the INTTIME command; see Chapter 11, addresses 1 and 2.

The Shot mode and Preview mode for Full Frame CCD is shown in Fig.4.

2001 Oct 22

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

#### 9.2 Frame Transfer CCD

In the Shot mode, the SAA8103 takes the external input signal TRG, as the trigger signal. After the rising edge of TRG the reset gate pulses (CR) are generated for the appropriate period. Integration time is held until the falling edge of TRG. A drive signal is generated in each VD period but is not issued until the next event of the TRG signal.

In the Preview mode, the SAA8103 generates a drive signal in every frame. The Preview mode is not influenced by the TRG signal.

The integration time is controlled using the INTTIME and EXPTIME command; see Chapter 11, addresses 1, 2, 3 and 4. The Shot mode and Preview mode for Frame Transfer CCD is shown in Fig.5.

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

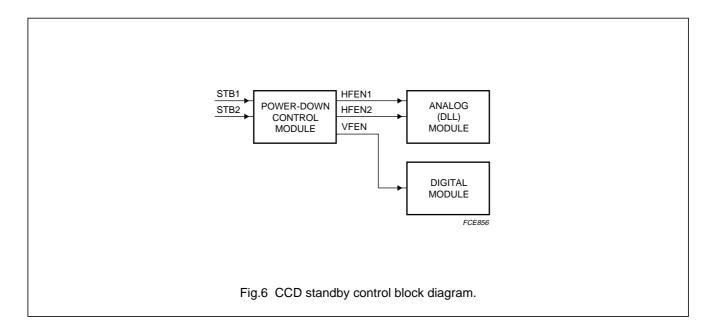

#### 9.3 Standby control function

The SAA8103 has two external inputs STB1 and STB2 which are used to select the Standby control mode, as shown in Table 2.

Table 2 Selection of Standby control mode

| STB2 | STB1 | MODE           | CONDITIONS                                 |

|------|------|----------------|--------------------------------------------|

| 0    | 0    | Normal         | HFEN1 = ON;<br>HFEN2 = ON;<br>VFEN = ON    |

| 0    | 1    | Standby mode 1 | HFEN1 = OFF;<br>HFEN2 = ON;<br>VFEN = ON   |

| 1    | 0    | Standby mode 2 | HFEN1 = ON;<br>HFEN2 = OFF;<br>VFEN = ON   |

| 1    | 1    | Standby mode 3 | HFEN1 = OFF;<br>HFEN2 = OFF;<br>VFEN = OFF |

#### 9.4 Standby modes

#### 9.4.1 STANDBY MODE 1

When Standby mode 1 is selected, the internal signal HFEN1 is inactive (OFF-state) and the data for HF1 to HF3 is masked. Consequently, the outputs of HF1 to HF3 are held LOW when Standby mode 1 is active.

#### 9.4.2 STANDBY MODE 2

When Standby mode 2 is selected, the internal signal HFEN2 is inactive (OFF-state) and the data for HF4 to HF9 is masked. Consequently, the outputs HF4 to HF9 are held LOW when Standby mode 2 is active.

#### 9.4.3 STANDBY MODE 3

When Standby mode 3 is selected, the internal signals HFEN1, HFEN2 and VFEN are inactive (OFF-state) and the data for HF1 to HF9 is masked. Consequently, the outputs HF1 to HF9 are held LOW when Standby mode 3 is active. The effect of VFEN being inactive (OFF-state) is described below.

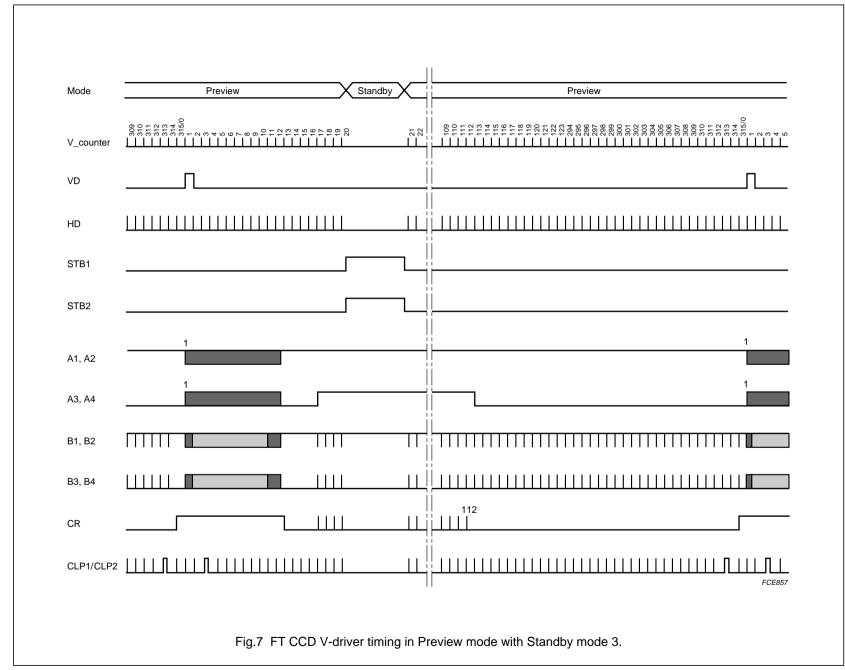

Figure 7 shows the effect of Standby mode 3 on the Preview mode. When the Standby mode 3 is applied on Preview mode, both the V\_counter and H\_counter are halted. The output signals hold their last state until Standby mode 3 is released. All output signals operate continuously after the release of Standby mode 3. This situation also applies when Standby mode 3 is selected whilst in Shot mode.

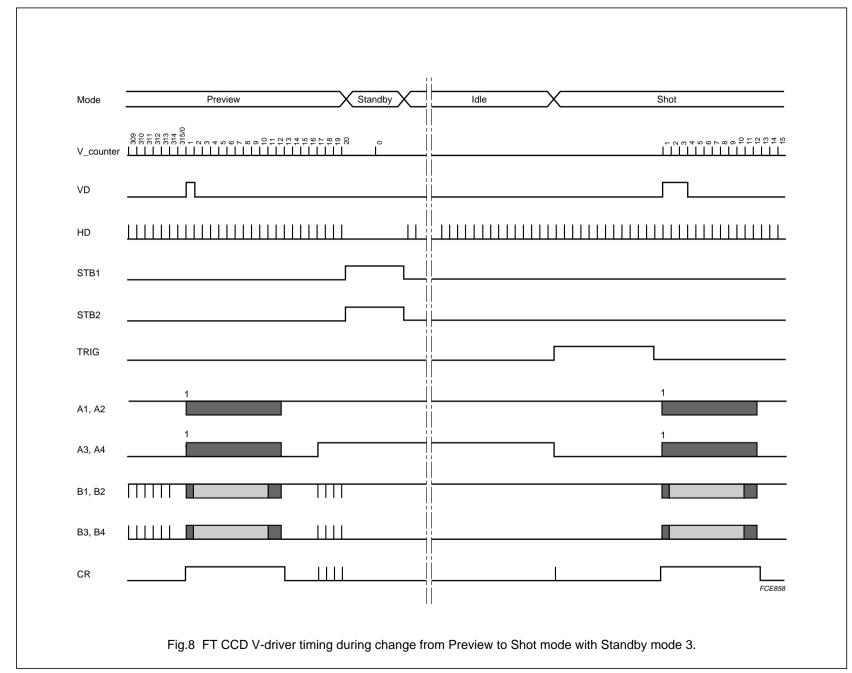

Figure 8 shows the effect of an operation change from Preview mode to Shot mode during Standby mode 3. In this situation, both the V\_counter and H\_counter are reset by the timing of Shot mode detection, and all output signals are reset. The operation is changed to Idle state after the release from Standby mode 3. The SAA8103 is now ready to accept the TRIG signal for Shot mode operation.

Philips Semiconductors

Objective specification

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

#### 10 SERIAL INTERFACES

The SAA8103 has two means by which it can communicate with a microcontroller: the I<sup>2</sup>C-bus serial interface and the SNERT serial interface. The selection of the serial interface is determined by the state of the signal on the SIS pin; see Table 3.

The CDS/ADC1, CDS/ADC2 and the V-driver are programmed by a series of commands sent via one of these interfaces. The command list is given in Table 4. Address and data decoding for the internal logic is carried out within the serial interface block.

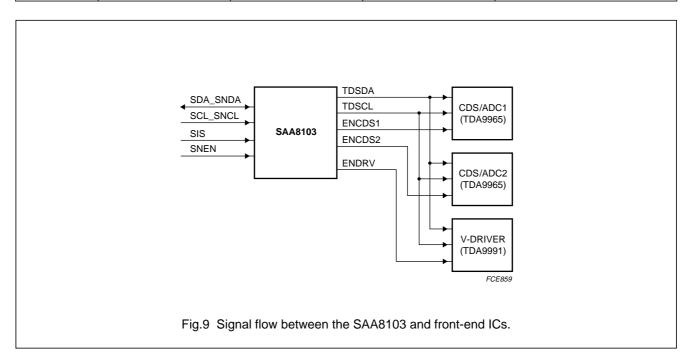

The CCD transfer pattern data is sent to the serial interface block and is held in one of two registers: Register 0 or Register 1. Register 0 is used to store data when the device is in the Shot mode. Register 1 is used to store data when the device is in the Preview mode. Consequently, before any data can be sent, Register 0 or Register 1 must be selected by writing the appropriate data to address 200. The transfer pattern signal will be loaded by the data read out mode and the TRG signal input. The signal flow between the SAA8103 and the front-end ICs is shown in Fig.9.

**Table 3** Serial interface selection

| SIS | SDA_SNDA                  | SCL_SNCL                   | SNEN         | INTERFACE SELECTED                      |

|-----|---------------------------|----------------------------|--------------|-----------------------------------------|

| 0   | I <sup>2</sup> C-bus data | I <sup>2</sup> C-bus clock | _            | I <sup>2</sup> C-bus; slave address 4EH |

| 1   | SNERT data                | SNERT clock                | SNERT enable | SNERT                                   |

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

#### 10.1 Control for V-driver (TDA9991) and CDS or ADC

The SAA8103 can control the V-driver (TDA9991) and the CDS/ADC (TDA99xx and TDA87xx) via the  $I^2C$ -bus serial interface.

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

### Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

**SAA8103**

#### 11 COMMAND LIST

**Table 4** The command list for the serial interfaces: I<sup>2</sup>C-bus and SNERT

| ADDRESS          | COMMAND BIT        | COMMAND DESCRIPTION                                                                                                                                                                                                             |  |  |

|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operating s      | Operating settings |                                                                                                                                                                                                                                 |  |  |

| 0(1)             | 0                  | Operational mode selection.                                                                                                                                                                                                     |  |  |

|                  |                    | 0 = Shot mode selected; default state                                                                                                                                                                                           |  |  |

|                  |                    | 1 = Preview mode selected                                                                                                                                                                                                       |  |  |

|                  | 1                  | CCD type selection.                                                                                                                                                                                                             |  |  |

|                  |                    | 0 = FT type CCD                                                                                                                                                                                                                 |  |  |

|                  |                    | 1 = FF type CCD; default state                                                                                                                                                                                                  |  |  |

|                  | 2 to 3             | These 2 bits are reserved.                                                                                                                                                                                                      |  |  |

|                  | 4                  | Sub-sampling function enable.                                                                                                                                                                                                   |  |  |

|                  |                    | 0 = sub-sampling OFF in FT type CCD; default state                                                                                                                                                                              |  |  |

|                  |                    | 1 = sub-sampling ON in FT type CCD                                                                                                                                                                                              |  |  |

|                  | 5                  | Electronic shutter setting (INTTIMEON).                                                                                                                                                                                         |  |  |

|                  |                    | 0 = integration time is ON; default state                                                                                                                                                                                       |  |  |

|                  |                    | 1 = integration time is OFF                                                                                                                                                                                                     |  |  |

| 1 <sup>(1)</sup> | 7 to 0             | Integration time setting (INTTIME).                                                                                                                                                                                             |  |  |

| 2 <sup>(1)</sup> | 4 to 0             | The data provided by these two commands is combined to form the 13-bit integration time setting. The integration time setting has a range from 0 to 8191; the default value is 3. It is calculated by the following expression: |  |  |

|                  |                    | Integration time = setting value × HD period                                                                                                                                                                                    |  |  |

| 3 <sup>(1)</sup> | 7 to 0             | Exposure time setting for FT CCD (EXPTIME).                                                                                                                                                                                     |  |  |

| 4 <sup>(1)</sup> | 4 to 0             | The data provided by these two commands is combined to form the 13-bit exposure time setting. The exposure time setting has a range from 0 to 8191; the default value is 3. It is calculated by the following expression:       |  |  |

|                  |                    | Exposure time = VD period – (setting value × HD period)                                                                                                                                                                         |  |  |

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

| ADDRESS           | COMMAND BIT                                                             | COMMAND DESCRIPTION                                                                                                                                                                                                                                                 |  |  |  |

|-------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Setting addr      | Setting address, data and enable for serial I/F of analog preprocessing |                                                                                                                                                                                                                                                                     |  |  |  |

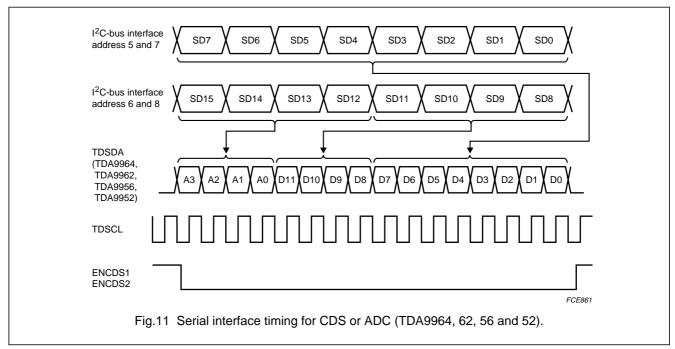

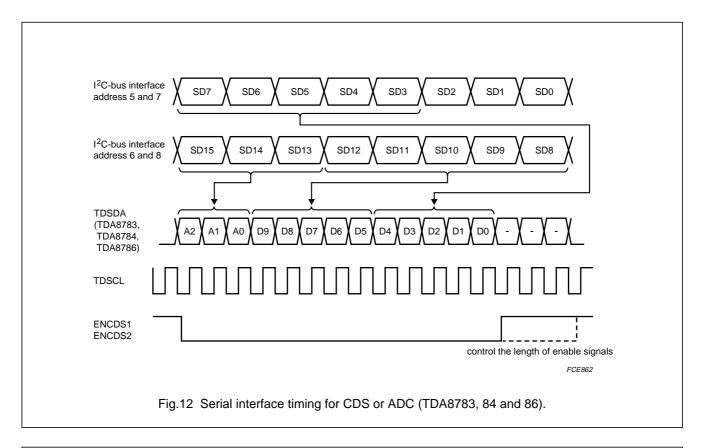

| 5(1)              | 7 to 0                                                                  | Serial data setting for CDS1 and ADC1.                                                                                                                                                                                                                              |  |  |  |

| 6 <sup>(1)</sup>  | 7 to 0                                                                  | The data provided by these two commands is combined to form the 16-bit serial data setting. The data written to address 5 provides serial data SD7 to SD0. The data written to address 6 provides serial data SD15 to SD8. The default value of both commands is 0. |  |  |  |

| 7 <sup>(1)</sup>  | 7 to 0                                                                  | Serial data setting for CDS2 and ADC2.                                                                                                                                                                                                                              |  |  |  |

| 8(1)              | 7 to 0                                                                  | The data provided by these two commands is combined to form the 16-bit serial data setting. The data written to address 7 provides serial data SD7 to SD0. The data written to address 8 provides serial data SD15 to SD8. The default value of both commands is 0. |  |  |  |

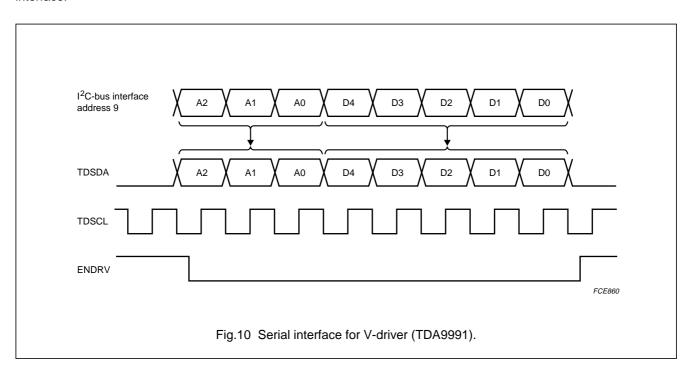

| 9(1)              | 4 to 0                                                                  | Data setting for V-driver. These 5 bits (D4 to D0) provide the data setting for the V-driver. The default value is 0.                                                                                                                                               |  |  |  |

|                   | 7 to 5                                                                  | Address setting for V-driver. These 3 bits (A2 to A0) provide the address for the V-driver. The default value is 0.                                                                                                                                                 |  |  |  |

| 10 <sup>(1)</sup> | 7 to 0                                                                  | Assign the division value of TDSCL generator for TDSCL output (DIVTDSCL). These 8 bits determine the division value for the TDSCL generator. The default value is 3.                                                                                                |  |  |  |

| 11 <sup>(1)</sup> | 0                                                                       | Control signal of serial interface data output (TDSDA) for CDS or ADC.                                                                                                                                                                                              |  |  |  |

|                   |                                                                         | 0 = enable; default state                                                                                                                                                                                                                                           |  |  |  |

|                   |                                                                         | 1 = disable                                                                                                                                                                                                                                                         |  |  |  |

|                   | 1                                                                       | Control signal of serial interface clock output (TDSCL) for CDS or ADC.                                                                                                                                                                                             |  |  |  |

|                   |                                                                         | 0 = enable; default state                                                                                                                                                                                                                                           |  |  |  |

|                   |                                                                         | 1 = disable                                                                                                                                                                                                                                                         |  |  |  |

|                   | 4                                                                       | Enable signal for CDS1 and ADC1 (ENCDS1) enable control (CD1ENBON).                                                                                                                                                                                                 |  |  |  |

|                   |                                                                         | 0 = enable; default state                                                                                                                                                                                                                                           |  |  |  |

|                   |                                                                         | 1 = disable                                                                                                                                                                                                                                                         |  |  |  |

|                   | 5                                                                       | Enable signal for CDS2 and ADC2 (ENCDS2) enable control (CD2ENBON).                                                                                                                                                                                                 |  |  |  |

|                   |                                                                         | 0 = enable; default state                                                                                                                                                                                                                                           |  |  |  |

|                   |                                                                         | 1 = disable                                                                                                                                                                                                                                                         |  |  |  |

|                   | 6                                                                       | Enable signal for V-driver (ENDRV) enable control (DRVENBON).                                                                                                                                                                                                       |  |  |  |

|                   |                                                                         | 0 = enable; default state                                                                                                                                                                                                                                           |  |  |  |

|                   |                                                                         | 1 = disable                                                                                                                                                                                                                                                         |  |  |  |

|                   | 7                                                                       | Control signal for 3-wire interface (GATE3WON).                                                                                                                                                                                                                     |  |  |  |

|                   |                                                                         | 0 = enable; default state                                                                                                                                                                                                                                           |  |  |  |

|                   |                                                                         | 1 = disable                                                                                                                                                                                                                                                         |  |  |  |

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

| ADDRESS           | COMMAND BIT         | COMMAND DESCRIPTION                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 <sup>(1)</sup> | 7 to 4              | Control the length of enable signals for ENCDS1, ENCDS2 and ENDRV.                                                                                                                                                                                                                                              |

|                   |                     | 0000 = 12 bits are generated for CDS; default state                                                                                                                                                                                                                                                             |

|                   |                     | 0010 = 13 bits are generated for CDS                                                                                                                                                                                                                                                                            |

|                   |                     | 0100 = 14 bits are generated for CDS                                                                                                                                                                                                                                                                            |

|                   |                     | 0110 = 15 bits are generated for CDS                                                                                                                                                                                                                                                                            |

|                   |                     | 1000 = 16 bits are generated for CDS                                                                                                                                                                                                                                                                            |

|                   |                     | 0001 = 8 bits are generated for V-driver; default state                                                                                                                                                                                                                                                         |

|                   |                     | 0011 = 9 bits are generated for V-driver                                                                                                                                                                                                                                                                        |

|                   |                     | 0101 = 10 bits are generated for V-driver                                                                                                                                                                                                                                                                       |

|                   |                     | 0111 = 11 bits are generated for V-driver                                                                                                                                                                                                                                                                       |

|                   |                     | 1001 = 12 bits are generated for V-driver                                                                                                                                                                                                                                                                       |

|                   |                     | 1011 = 13 bits are generated for V-driver                                                                                                                                                                                                                                                                       |

|                   |                     | 1101 = 14 bits are generated for V-driver                                                                                                                                                                                                                                                                       |

|                   |                     | 1111 = 15 bits are generated for V-driver                                                                                                                                                                                                                                                                       |

|                   | 2 to 0              | HD, VD and HREF and VREF polarity (HDVDINT).                                                                                                                                                                                                                                                                    |

|                   |                     | 000 = internal mode; negative HD and VD output                                                                                                                                                                                                                                                                  |

|                   |                     | 001 = internal mode; negative HREF and VREF output                                                                                                                                                                                                                                                              |

|                   |                     | 010 = internal mode; positive HD and VD output; default state                                                                                                                                                                                                                                                   |

|                   |                     | 011 = internal mode; positive HREF and VREF output                                                                                                                                                                                                                                                              |

|                   |                     | 100 = external mode; negative HD input and negative VD output                                                                                                                                                                                                                                                   |

|                   |                     | 101 = external mode; negative HD and VD inputs                                                                                                                                                                                                                                                                  |

|                   |                     | 110 = external mode; positive HD input and positive VD output                                                                                                                                                                                                                                                   |

|                   |                     | 111 = external mode; positive HD and VD inputs                                                                                                                                                                                                                                                                  |

| Setting the       | start and stop poin | ts for process timing                                                                                                                                                                                                                                                                                           |

| 13                | 7 to 0              | Horizontal Sync period (HS).                                                                                                                                                                                                                                                                                    |

| 14                | 4 to 0              | The data provided by these two commands is combined to form the 13-bit Horizontal Sync period setting. The data written to address 13 provides data D7 to D0. The data written to address 14 provides data D12 to D8. The Horizontal Sync period setting has a range from 0 to 8191. The default value is 3487. |

| 15                | 7 to 0              | Vertical Sync period (VS).                                                                                                                                                                                                                                                                                      |

| 16                | 4 to 0              | The data provided by these two commands is combined to form the 13-bit Vertical Sync period setting. The data written to address 15 provides data D7 to D0. The data written to address 16 provides data D12 to D8. The Vertical Sync period setting has a range from 0 to 8191. The default value is 2060.     |

| 17                | 7 to 0              | HD stop (HDSTP). The HD stop setting has a range from 0 to 255. The default value is 4. The HD stop value is calculated as shown below.                                                                                                                                                                         |

|                   |                     | HD stop point = 2 × assigned value                                                                                                                                                                                                                                                                              |

| 18                | 7 to 0              | VD stop (VDSTP). The VD stop setting has a range from 0 to 255. The default value is 4. The VD stop value is calculated as shown below.                                                                                                                                                                         |

|                   |                     | VD stop point = 2 × assigned value                                                                                                                                                                                                                                                                              |

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

| ADDRESS       | COMMAND BIT         | COMMAND DESCRIPTION                                                                                                                                                                                                                                                                   |

|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19            | 7 to 0              | HREF start (HREFSTR). The HREF start setting has a range from 0 to 255. The default value is 4. The HREF start value is calculated as shown below.                                                                                                                                    |

|               |                     | HREF start point = 2 × assigned value                                                                                                                                                                                                                                                 |

| 20            | 7 to 0              | HREF stop (HREFSTP).                                                                                                                                                                                                                                                                  |

| 21            | 4 to 0              | The data provided by these two commands is combined to form the 13-bit HREF stop setting. The data written to address 20 provides data D7 to D0. The data written to address 21 provides data D12 to D8. The HREF stop setting has a range from 0 to 8191. The default value is 0.    |

| 22            | 7 to 0              | VREF start (VREFSTR).                                                                                                                                                                                                                                                                 |

| 23            | 4 to 0              | The data provided by these two commands is combined to form the 13-bit VREF start setting. The data written to address 22 provides data D7 to D0. The data written to address 23 provides data D12 to D8. The VREF start setting has a range from 0 to 8191. The default value is 4.  |

| 24            | 7 to 0              | VREF stop (VREFSTP).                                                                                                                                                                                                                                                                  |

| 25            | 4 to 0              | The data provided by these two commands is combined to form the 13-bit VREF stop setting. The data written to address 24 provides data D7 to D0. The data written to address 25 provides data D12 to D8. The VREF stop setting has a range from 0 to 8191. The default value is 0.    |

| Setting the s | start and stop poin | ts for internal signal SSC                                                                                                                                                                                                                                                            |

| 26            | 7 to 0              | SSC start (SSCSTR).                                                                                                                                                                                                                                                                   |

|               |                     | The SSC start setting has a range from 0 to 255. The default value is 0. The SSC start value is calculated as shown below.                                                                                                                                                            |

|               |                     | SSC start point = 2 × assigned value                                                                                                                                                                                                                                                  |

| 27            | 7 to 0              | SSC stop (SSCSTP).                                                                                                                                                                                                                                                                    |

| 28            | 4 to 0              | The data provided by these two commands is combined to form the 13-bit SSC stop setting. The data written to address 27 provides data D7 to D0. The data written to address 28 provides data D12 to D8. The SSC stop setting has a range from 0 to 8191. The default value is 360.    |

| Setting the s | start and stop poin | ts for clamp timings                                                                                                                                                                                                                                                                  |

| 29            | 7 to 0              | Horizontal direction at the left clamp pulse 1 start (HLCLPSTR1).                                                                                                                                                                                                                     |

| 30            | 4 to 0              | The data provided by these two commands is combined to form the 13-bit HLCLPSTR1 setting. The data written to address 29 provides data D7 to D0. The data written to address 30 provides data D12 to D8. The HLCLPSTR1 setting has a range from 0 to 8191. The default value is 371.  |

| 31            | 7 to 0              | Horizontal direction at the left clamp pulse 1 stop (HLCLPSTP1).                                                                                                                                                                                                                      |

| 32            | 4 to 0              | The data provided by these two commands is combined to form the 13-bit HLCLPSTP1 setting. The data written to address 31 provides data D7 to D0. The data written to address 32 provides data D12 to D8. The HLCLPSTP1 setting has a range from 0 to 8191. The default value is 383.  |

| 33            | 7 to 0              | Horizontal direction at the right clamp pulse 1 start (HRCLPSTR1).                                                                                                                                                                                                                    |

| 34            | 4 to 0              | The data provided by these two commands is combined to form the 13-bit HRCLPSTR1 setting. The data written to address 33 provides data D7 to D0. The data written to address 34 provides data D12 to D8. The HRCLPSTR1 setting has a range from 0 to 8191. The default value is 3470. |

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

| ADDRESS | COMMAND BIT | COMMAND DESCRIPTION                                                                                                                                                                                                                                                                    |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35      | 7 to 0      | Horizontal direction at the right clamp pulse 1 stop (HRCLPSTP1).                                                                                                                                                                                                                      |

| 36      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit HRCLPSTP1 setting. The data written to address 35 provides data D7 to D0. The data written to address 36 provides data D12 to D8. The HRCLPSTP1 setting has a range from 0 to 8191. The default value is 3484.  |

| 37      | 7 to 0      | Horizontal direction at the left clamp pulse 2 start (HLCLPSTR2).                                                                                                                                                                                                                      |

| 38      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit HLCLPSTR2 setting. The data written to address 37 provides data D7 to D0. The data written to address 38 provides data D12 to D8. The HLCLPSTR2 setting has a range from 0 to 8191. The default value is 371.   |

| 39      | 7 to 0      | Horizontal direction at the left clamp pulse 2 stop (HLCLPSTP2).                                                                                                                                                                                                                       |

| 40      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit HLCLPSTP2 setting. The data written to address 39 provides data D7 to D0. The data written to address 40 provides data D12 to D8. The HLCLPSTP2 setting has a range from 0 to 8191. The default value is 383.   |

| 41      | 7 to 0      | Horizontal direction at the right clamp pulse 2 start (HRCLPSTR2).                                                                                                                                                                                                                     |

| 42      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit HRCLPSTR2 setting. The data written to address 41 provides data D7 to D0. The data written to address 42 provides data D12 to D8. The HRCLPSTR2 setting has a range from 0 to 8191. The default value is 3470.  |

| 43      | 7 to 0      | Horizontal direction at the right clamp pulse 2 stop (HRCLPSTP2).                                                                                                                                                                                                                      |

| 44      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit HRCLPSTP2 setting. The data written to address 43 provides data D7 to D0. The data written to address 44 provides data D12 to D8. The HRCLPSTP2 setting has a range from 0 to 8191. The default value is 3484.  |

| 45      | 7 to 0      | Vertical direction at the top clamp pulse 1 start (VTCLPSTR1).  The VTCLPSTR1 setting has a range from 0 to 255. The default value is 3.                                                                                                                                               |

| 46      | 7 to 0      | Vertical direction at the top clamp pulse 1 stop (VTCLPSTP1). The VTCLPSTP1 setting has a range from 0 to 255. The default value is 4.                                                                                                                                                 |

| 47      | 7 to 0      | Vertical direction at the top clamp pulse 1 horizontal start (VTHCLPSTR1).                                                                                                                                                                                                             |

| 48      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VTHCLPSTR1 setting. The data written to address 47 provides data D7 to D0. The data written to address 48 provides data D12 to D8. The VTHCLPSTR1 setting has a range from 0 to 8191. The default value is 0.   |

| 49      | 7 to 0      | Vertical direction at the top clamp pulse 1 horizontal stop (VTHCLPSTP1).                                                                                                                                                                                                              |

| 50      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VTHCLPSTP1 setting. The data written to address 49 provides data D7 to D0. The data written to address 50 provides data D12 to D8. The VTHCLPSTP1 setting has a range from 0 to 8191. The default value is 0.   |

| 51      | 7 to 0      | Vertical direction at the bottom clamp pulse 1 start (VBCLPSTR1).                                                                                                                                                                                                                      |

| 52      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VBCLPSTR1 setting. The data written to address 51 provides data D7 to D0. The data written to address 52 provides data D12 to D8. The VTHCLPSTR1 setting has a range from 0 to 8191. The default value is 2060. |

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

| ADDRESS | COMMAND BIT | COMMAND DESCRIPTION                                                                                                                                                                                                                                                                   |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53      | 7 to 0      | Vertical direction at the bottom clamp pulse 1 stop (VBCLPSTP1).                                                                                                                                                                                                                      |

| 54      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VBCLPSTP1 setting. The data written to address 53 provides data D7 to D0. The data written to address 54 provides data D12 to D8. The VBCLPSTP1 setting has a range from 0 to 8191. The default value is 0.    |

| 55      | 7 to 0      | Vertical direction at the bottom clamp pulse 1 horizontal start (VBHCLPSTR1).                                                                                                                                                                                                         |

| 56      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VBHCLPSTR1 setting. The data written to address 55 provides data D7 to D0. The data written to address 56 provides data D12 to D8. The VBHCLPSTR1 setting has a range from 0 to 8191. The default value is 0.  |

| 57      | 7 to 0      | Vertical direction at the bottom clamp pulse 1 horizontal stop (VBHCLPSTP1).                                                                                                                                                                                                          |

| 58      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VBHCLPSTP1 setting. The data written to address 57 provides data D7 to D0. The data written to address 58 provides data D12 to D8. The VBHCLPSTP1 setting has a range from 0 to 8191. The default value is 0.  |

| 59      | 7 to 0      | Vertical direction at the top clamp pulse 2 start (VTCLPSTR2). The VTCLPSTR2 setting has a range from 0 to 255. The default value is 3.                                                                                                                                               |

| 60      | 7 to 0      | Vertical direction at the top clamp pulse 2 stop (VTCLPSTP2). The VTCLPSTP2 setting has a range from 0 to 255. The default value is 4.                                                                                                                                                |

| 61      | 7 to 0      | Vertical direction at the top clamp pulse 2 horizontal start (VTHCLPSTR2).                                                                                                                                                                                                            |

| 62      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VTHCLPSTR2 setting. The data written to address 61 provides data D7 to D0. The data written to address 62 provides data D12 to D8. The VTHCLPSTR2 setting has a range from 0 to 8191. The default value is 0.  |

| 63      | 7 to 0      | Vertical direction at the top clamp pulse 2 horizontal stop (VTHCLPSTP2).                                                                                                                                                                                                             |

| 64      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VTHCLPSTP2 setting. The data written to address 63 provides data D7 to D0. The data written to address 64 provides data D12 to D8. The VTHCLPSTP2 setting has a range from 0 to 8191. The default value is 0.  |

| 65      | 7 to 0      | Vertical direction at the bottom clamp pulse 2 start (VBCLPSTR2).                                                                                                                                                                                                                     |

| 66      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VBCLPSTR2 setting. The data written to address 65 provides data D7 to D0. The data written to address 66 provides data D12 to D8. The VBCLPSTR2 setting has a range from 0 to 8191. The default value is 2060. |

| 67      | 7 to 0      | Vertical direction at the bottom clamp pulse 2 stop (VBCLPSTP2).                                                                                                                                                                                                                      |

| 68      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VBCLPSTP2 setting. The data written to address 67 provides data D7 to D0. The data written to address 68 provides data D12 to D8. The VBCLPSTP2 setting has a range from 0 to 8191. The default value is 0.    |

| 69      | 7 to 0      | Vertical direction at the bottom clamp pulse 2 horizontal start (VBHCLPSTR2).                                                                                                                                                                                                         |

| 70      | 4 to 0      | The data provided by these two commands is combined to form the 13-bit VBHCLPSTR2 setting. The data written to address 69 provides data D7 to D0. The data written to address 70 provides data D12 to D8. The VBHCLPSTR2 setting has a range from 0 to 8191. The default value is 0.  |

# Pulse Pattern Generator for Frame Transfer CCD (PPGFT)

SAA8103

| ADDRESS     | COMMAND BIT         | COMMAND DESCRIPTION                                                                                                                                                                                                                                                               |

|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71<br>72    | 7 to 0<br>4 to 0    | Vertical direction at the bottom clamp pulse 2 horizontal stop (VBHCLPSTP2).  The data provided by these two commands is combined to form the 13-bit                                                                                                                              |

| 72          | 4 10 0              | VBHCLPSTP2 setting. The data written to address 71 provides data D7 to D0. The data written to address 72 provides data D12 to D8. The VBHCLPSTP2 setting has a range from 0 to 8191. The default value is 0.                                                                     |

| Setting the | start and stop poin | ts for charge reset timings                                                                                                                                                                                                                                                       |