# 4 Megabit (5V) CMOS Flash EEPROM

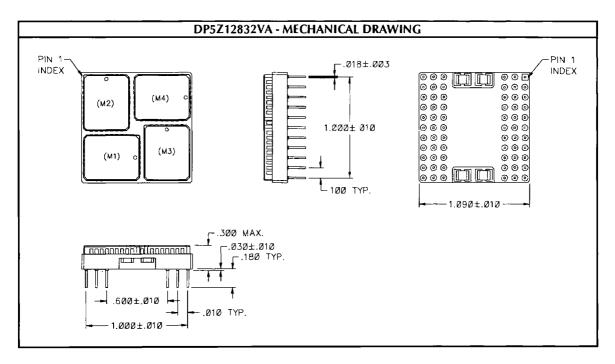

DP5Z12832VA/DP5Z12832VAP

# **PRELIMINARY**

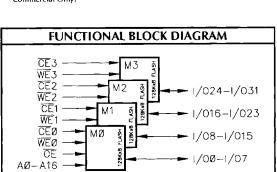

#### **DESCRIPTION:**

The DP5Z12832VA/DP5Z12832VAP is a 4 megabit 5 volt CMOS Flash EEPROM (Electrically In-System Programmable and Erasable ROM Memory) module. The module is built with four 128K x 8 FLASH memory devices. The DP5Z12832VA/DP5Z12832VAP can be user configurable as 512K x 8, 256K x 16 or 128K x 32 bits.

The DP5Z12832VA/DP5Z12832VAP is ideal for use in systems that require In System periodic code updates, or for use as a high speed nonvolatile storage medium.

#### **FEATURES:**

- User Defined Configuration: 512K x 8, 256K x 16 or 128K x 32

- Fast Read Access Times: 45\*, 55, 70, 90, 120ns

- · Low Power:

- 120mA Maximum Active 200µA Maximum Standby (CMOS)

- 10,000 Erase/Program Cycles Minimum

- 5 Volt Only In-System Programming

- TTL-Compatible Inputs and Outputs

Additional Variable Application Applied to the Application Applied to the Applied T

- Military Version Available with all Devices used to construct the Module Compliant to MIL-STD-883; Class B

- · 66-Pin Ceramic PGA

- \* Commercial Only.

| P               | IN NAMES          |

|-----------------|-------------------|

| A0 - A16        | Address Inputs    |

| 1/00 - 1/031    | Data Input/Output |

| CEO - CE3       | Chip Enables      |

| WEO - WE3       | Write Enables     |

| ŌĔ              | Output Enable     |

| V <sub>DD</sub> | Power (+5V)       |

| Vss             | Ground            |

| N.C.            | No Connect        |

| PIN-OUT DIAGRAM                                                                                                                                                  |                                                                                                                                    |    |        |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----|--------|--|--|--|--|--|--|

| 1 I/08   12<br>2 I/09   13<br>3 I/01Ø   14<br>4 A13   15<br>5 A14   16<br>6 A15   17<br>7 A16   18<br>8 N.C.   19<br>9 I/0Ø   2Ø<br>1Ø I/01   21<br>11 I/02   22 | 3 CE1 24 I/O14 4 VSS 25 I/O13 5 I/O11 26 I/O12 6 A1Ø 27 OE 7 A11 28 N.C. 8 A12 29 WEØ 9 VDD 3Ø I/O7 2Ø CEØ 31 I/O6 21 N.C. 32 I/O5 | 10 | 45 VDD |  |  |  |  |  |  |

#### **DEVICE OPERATION:**

The FLASH devices are electrically erasable and programmable memories that function similarly to an EPROM device, but can be erased without being removed from the system and exposed to ultraviolet light. Each 128K x 8 device or sector on any device can be programmed and erased individually elimination the need to re-program the entire module when partial code changes are required.

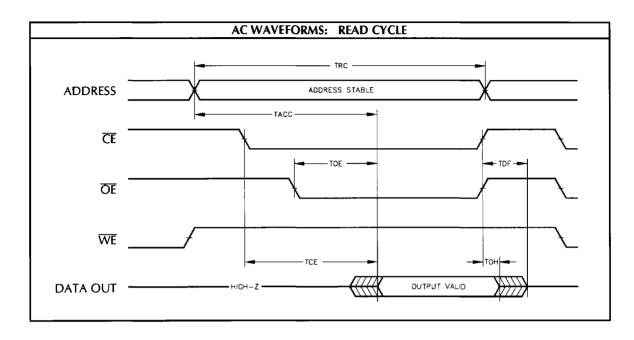

#### READ/RESET:

The Module is accessed like a Static Ram. When  $\overline{CE}$  and  $\overline{OE}$  are Low and  $\overline{WE}$  is High, the data stored at the memory location determined by the address pins is asserted on the outputs. The outputs are put in the high impedance state whenever  $\overline{CE}$  or  $\overline{OE}$  is high. This dual line control gives designers flexibility in preventing bus contention.

The read or reset operation is initiated by writing read/reset command into the command register (see the Command Definition Table). The device remains in the read mode until another valid command is written into the command register. The device will automatically be set to the read/reset mode upon power-up.

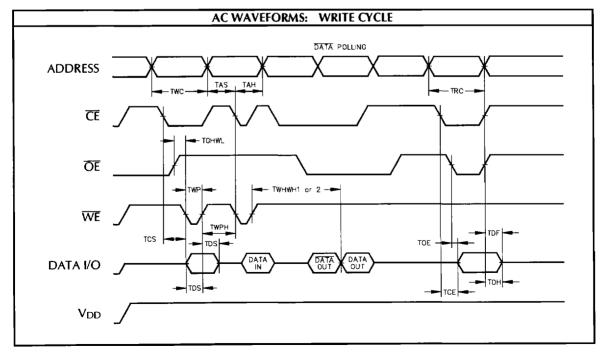

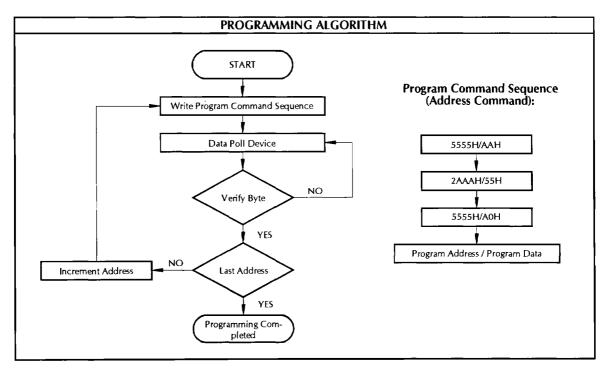

#### **BYTE PROGRAMMING:**

The module is programmed one byte at a time. The program operation is four cycles long. There are two "unlock" write cycles. The "unlock" cycles are followed by the program set-up command and data write cycles.

Addresses are latched on the falling edge of  $\overline{WE}$ , while the data is latched on the rising edge of  $\overline{WE}$ . The program cycle will begin on the rising edge of  $\overline{WE}$ . The program algorithm is internally generated providing all the necessary timing, pulse widths, and margins to reliably complete the program cycle. The program operation is completed when the VO7 bit (or VO15, VO23, VO31) on the devicets) programmed is equivalent to the data written to that bit. The device programmed returns to the read/reset mode upon completion of the program operation.

Programming is allowed in any sequence and across sector boundaries.

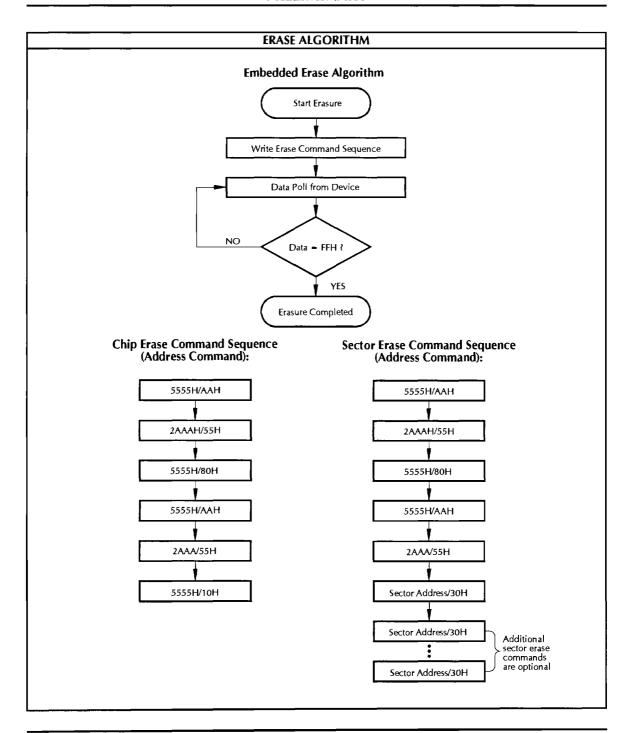

#### **CHIP ERASE:**

The chip erase operation is six cycles long. There are two "unlock" write cycles followed by writing the set-up chip erase command followed by two more "unlock" write cycles.

It is not required to program all of the memory locations to "0" prior to the chip erase operation. At the start of the chip erase operation the device will internally program and verify the entire memory to an all "0" data pattern prior to electrical erase.

The automatic erase begins on the rising edge of the last WE pulse in the command sequence. When the chip erase operation is completed the data on the I/O7 bit (or I/O15, I/O23, I/O31) of the device being erased will equal "1" at which time the device will return to the read/reset mode.

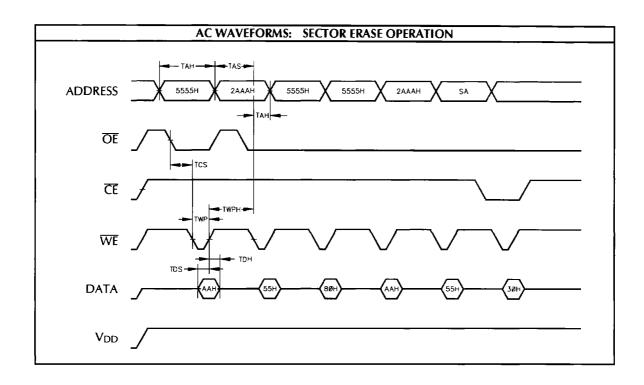

#### **SECTOR ERASE:**

The sector erase operation is six cycles long. There are two "unlock" write cycles followed by writing the set-up sector erase command followed by two more "unlock" write cycles. The sector address (any address within the sector) is latched on the falling edge of  $\overline{WE}$ , while the command (data) is latched on the rising edge of  $\overline{WE}$ . A time-out of 100 $\mu$ s from the rising edge of the last  $\overline{WE}$  will initiate the sector erase command(s).

Multiple sectors may be erased concurrently by writing the six bus cycle operations as described above. This sequence is followed with writes of the sector erase command 30H to addresses in other sectors desired to be concurrently erased. A time-out of 100µs from the rising edge of the last  $\overline{\text{WE}}$  will initiate the sector erase command(s). If another falling edge of the  $\overline{\text{WE}}$  occurs within the 100µs time-out window the timer is reset. Any command other than sector erase within the time-out window will reset the device to the read mode, ignoring the previous command string. Loading the sector erase buffer may be done in any sequence and with any number of sectors (1 to 8).

It is not required to program all of the memory locations to "0" prior to the sector erase operation. During the sector erase operation, any sectors not selected will not be affected.

The sector erase operation is completed when the I/O7 bit (or I/O15, I/O23, I/O31) on the devices being erased is "1". The device erased returns to the read/reset mode upon completion of the sector erase operation.

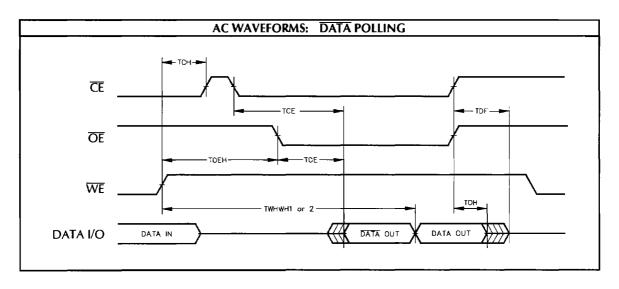

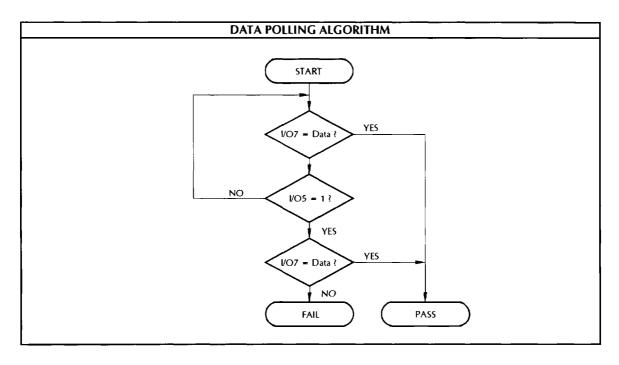

#### **DATA POLLING:**

The module features Data Polling as a method to indicate the end of a program or erase operation.

During a program operation, an attempt to read the device(s) being programmed will produce the compliment data of the last data written to the  $1/\sqrt{1000}$  bit (or  $1/\sqrt{1000}$ ),  $1/\sqrt{1000}$ ) of the device or devices the operation is being performed on. Data Polling is valid after the rising edge of the fourth  $1/\sqrt{1000}$  by pulse in the four write pulse sequence.

During the erase operation, the I/O7 bit of the device(s) being erased will be "0" until the erase operation is completed. Upon completion the data on the I/O7 bit will be "1". For chip erase, the  $\overline{Data}$  Polling is valid after the rising edge of the sixth  $\overline{WE}$  pulse in the six write pulse sequence. For sector erase, the  $\overline{Data}$  Polling is valid after the last rising edge of the sector erase  $\overline{WE}$  pulse.

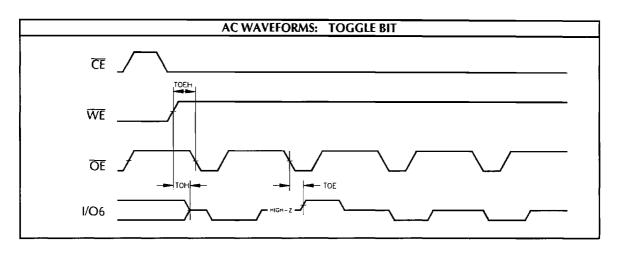

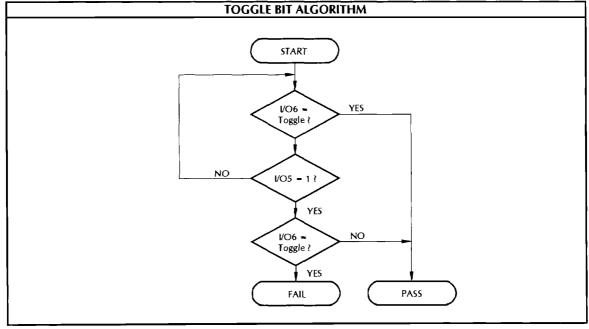

#### TOGGLE BIT:

The module also features the Toggle Bit function for determining the completion of a program or erase operation.

During a program or erase operation, successive attempts to read data from the device(s) will result in the VO6 (or VO14, VO22, VO30) bit toggling between "1" and "0". Once the program or erase operation has completed, the VO pin will stop toggling and valid data can be read. During the program operation, the Toggle Bit is valid after the rising edge of the fourth  $\overline{WE}$  pulse in the four write pulse sequence. For chip erase, the Toggle Bit is valid after the rising edge of the sixth  $\overline{WE}$  pulse in the six write pulse sequence. For sector erase, the Toggle Bit is valid after the last rising edge of the sector erase  $\overline{WE}$  pulse. The Toggle Bit is active during the sector time out.

#### PRODUCT I.D. COMMAND:

The product I.D. command operation outputs the manufacturer code (01H) and the device code (20H). This allows programming equipment to match the device with the proper erase and programming algorithms.

To activate this mode, the programming equipment must force  $V_{ID}$  (11.5V to 13.0V) on address pin A9. With  $\overline{CE}$  and  $\overline{OE}$  =  $V_{IL}$  and  $\overline{WE}$  =  $V_{IH}$ , the two I.D. bytes may then be read from the device outputs by toggling address A0 from  $V_{IL}$  to  $V_{IH}$ . All addresses are don't cares except A0 and A1.

The I.D. codes can also be accessed via the command register. There are two "unlock" write cycles followed by a write of the read product I.D. command. Following the read product I.D. command, a read from address XXX0H will return 01H and a read from address XXX1H will return 20H. The sector protect status can also be read while in this mode. If the sector is protected, performing a read operation at address location XXX2H with A16, A15, and A14 set for the proper sector address will return a "1" on the I/O0 (or I/O8, I/O16, I/O24) bit of the device the operation is being performed on.

#### SECTOR PROTECT:

The module also features hardware sector protection. This feature will disable both program and erase operations in any number of sectors (1 through 8). The sector protect feature is enabled using programming equipment at the user's site. The module is shipped with all sectors unprotected.

To activate this mode, the programming equipment must force  $V_{1D}$  on A9 and  $\overline{OE}$ . The sector addresses (A16, A15, and A14) should be set to the sector to be protected. Programming of the protection circuitry begins on the falling edge of the  $\overline{WE}$  pulse and is terminated with the rising edge of  $\overline{WE}$ . Sector addresses must remain stable during the  $\overline{WE}$  pulse.

To verify programming of the protection circuitry, the programming equipment must force  $V_{ID}$  on address pin A9 with  $\overline{CE}$  and  $\overline{OE} = V_{IL}$  and  $\overline{WE} = V_{IH}$ . Selecting the sector with A16, A15, and A14 set for the proper sector address will return a "1" on the VO0 (or VO8, VO16, VO24) bit of the device the operation is being performed on. In this mode, the lower order addresses, except for A0 and A1, are don't care. Address location 00H and 01H are reserved for product ID codes. If a sector protect verify is performed at one of these locations in sector 0, the device would return the manufacturer and device codes respectively (A0 =  $V_{IL}$ , A0 =  $V_{IH}$ ).

It is also possible to determine if a sector is protected in the system by writing the product I.D. command sequence. Performing a read operation at address location XXX2H with the higher order addresses (A16, A15, and A14) set to the proper sector address will return a "1" on the I/O0 (or I/O8, I/O16, I/O24) bit of the device the operation is being performed on.

#### TIMING LIMIT FLAG:

The VO5 (or VO13, VO21, VO29) bit will indicate if the program or erase time has exceeded the specified limits. Under these conditions these VO's will produce a "1" if the program or erase function was not successfully completed.  $\overline{Data}$  Polling is the only operating function of the device under this condition. The  $\overline{CE}$  circuit will partially power down the device under these conditions. The  $\overline{OE}$  and  $\overline{WE}$  pins will control the output disable function. To reset the device, write the Reset command sequence to the device. This allows the system to continue to use the other active sectors in the device.

#### HARDWARE SEQUENCE FLAG:

If the device has exceeded the specified erase or program time and the VO5 bit is "1", then the VO4 (or VO12, VO20, VO28) bit will indicate

which step in the algorithm the device exceeded the limits. A "0" indicates in programming, a "1" indicates an erase.

#### SECTOR ERASE TIMER:

After the completion of the initial sector erase command sequence the sector erase time-out will begin. The I/O3 (or I/O11, I/O19, I/O27) bit will remain low until the time-out is complete. Data Polling and Toggle Bit are also valid after the initial sector erase command sequence.

If Data Polling or the Toggle Bit indicates the device has been written a valid erase command, the I/O3 bit may be used to determine if the sector erase timer window is still open. If the I/O3 bit is high ("1"), the internally controlled erase cycle has begun suspending access to the command register until the erase operation is completed as indicated by Data Polling or Toggle Bit. If the I/O3 bit is low ("0"), the device will accept additional sector erase commands. To insure the command has been accepted, the software should check the status of the I/O3 bit prior to and following each sector erase command. If the I/O3 bit was high on the second status check, the command may not have been accepted.

#### DATA PROTECTION:

The devices used in the construction of the module are designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transitions. The devices power up in the read state only. Also, with a control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences.

The device also incorporates several features to prevent inadvertent write cycles resulting from  $V_{DD}$  power-up and power-down transitions or system noise.

#### LOW VDD WRITE INHIBIT;

To avoid initiation of a write cycle during  $V_{DD}$  power-up or power-down, a write cycle is locked out for  $V_{DD}$  less than 3.2V (typically 3.7V). If  $V_{DD}$   $V_{LKO}$ , the command register is disabled and all internal program/erase circuits are disabled. The device will reset to the read mode. Subsequent writes will be ignored until the  $V_{DD}$  level is greater than  $V_{LKO}$ . It is the users responsibility to ensure that the control pins are logically correct to prevent unintentional writes when  $V_{DD}$  is above 3.2V.

#### WRITE PULSE "GLITCH" PROTECTION:

Noise pulses of less than 5ns (typical) on  $\overrightarrow{OE}$ ,  $\overrightarrow{CE}$ , and  $\overrightarrow{WE}$  will not initiate a write cycle.

#### **LOGICAL INHIBIT:**

Writing is inhibited by holding any one of  $\overline{OE} = V_{IL}$ ,  $\overline{CE} = V_{IH}$ , or  $\overline{WE} = V_{IH}$ . To initiate a write cycle  $\overline{CE}$  and  $\overline{WE}$  must be  $= V_{IL}$  while  $\overline{OE} = V_{IL}$ .

#### **POWER-UP WRITE INHIBIT:**

If power-up is performed with  $\overline{WE}=\overline{CE}=V_{1L}$  and  $\overline{OE}=V_{1H}$ , the command register will not latch a command on the rising edge of  $\overline{WE}$ . The command register is automatically reset to the read mode on power-up.

|                                    |    | TRUTH           | TABLE |    |     |                 |                     |

|------------------------------------|----|-----------------|-------|----|-----|-----------------|---------------------|

| Mode                               | CE | ŌĒ              | WE    | A0 | A1_ | A9              | I/O Pin             |

| Product I.D. Manufacturer Code [1] | L  | L               | Н     | L  | L   | VID             | CODE                |

| Product I.D. Device Code [1]       | L  | L               | Н     | Ι  | L   | V <sub>ID</sub> | CODE                |

| Read                               |    | L               | X     | A0 | A1  | A9              | Dout                |

| Standby                            | Ŧ  | X               | X     | X  | Χ   | Х               | HIGH-Z              |

| Output Disable                     | L  | H               | Н     | Х  | Х   | X               | HIGH-Z              |

| Write                              | L_ | H               | L     | A0 | A1  | A9              | D <sub>IN</sub> [2] |

| Enable Sector Protect              | Ĺ  | V <sub>ID</sub> | L     | Х  | X   | V <sub>ID</sub> | Х                   |

| Verify Sector Protect [3]          | L  | L               | H     | L  | Н   | V <sub>ID</sub> | CODE                |

**LEGEND:**  $L = V_{1L}$ ,  $H = V_{1H}$ , X = Don't Care

|                | COMMAND DEFINITIONS TABLE [4, 5, 6, 7] |         |      |         |      |         |      |         |         |              |                          |         |      |

|----------------|----------------------------------------|---------|------|---------|------|---------|------|---------|---------|--------------|--------------------------|---------|------|

| COMMAND        | Bus First Bus<br>Write Write Cycle     |         |      |         |      |         |      |         |         | Bus<br>Cycle | Sixth Bus<br>Write Cycle |         |      |

| SEQUENCE       | Cycles<br>Req'd                        | Address | Data | Address | Data | Address | Data | Address | Data    | Address      | Data                     | Address | Data |

| Read / Reset   | 4                                      | 5555H   | AAH  | 2AAAH   | 55H  | 5555H   | FOH  | RA      | RD      | -            | -                        | -       | -    |

| Auto Select    | 4                                      | 5555H   | AAH  | 2AAAH   | 55H  | 5555H   | 90H  | 00H/01H | 01H/20H | -            | -                        | -       | -    |

| Byte Program   | 4                                      | 5555H   | AAH  | 2AAAH   | 55H  | 5555H   | A0H  | PA      | PD      | -            | -                        | -       | -    |

| Chip Erase     | 6                                      | 5555H   | AAH  | 2AAAH   | 55H  | 5555H   | 80H  | 5555H   | AAH     | 2AAAH        | 55H                      | 5555H   | 10H  |

| Selector Erase | 6                                      | 5555H   | AAH  | 2AAAH   | 55H  | 5555H   | 80H  | 5555H   | AAH     | 2AAAH        | 55H                      | SA      | 30H  |

|             | WRITE OPERATION STATUS FLAGS  Status   1/O7(8)   1/O6(8)   1/O5(8)   1/O4(8)   1/O3(8)   1/O2 - 1/O0(8) |         |                     |                     |                     |                            |              |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------|---------|---------------------|---------------------|---------------------|----------------------------|--------------|--|--|--|

|             | I/O7 <sup>[8]</sup>                                                                                     | 1/06[8] | I/O5 <sup>[8]</sup> | I/O4 <sup>[8]</sup> | I/O3 <sup>[8]</sup> | 1/O2 - 1/O0 <sup>[8]</sup> |              |  |  |  |

| In Progress | Auto - Programming                                                                                      | 1/07    | Toggle              | 0                   | 0                   | 0                          | Reserved for |  |  |  |

|             | Programming in Auto - Erase                                                                             | 0       | Toggle              | 0                   | 0                   | 0                          |              |  |  |  |

| -           | Erase in Auto - Erase                                                                                   | 0       | Toggle              | 0                   | 1                   | 1                          | Future Use   |  |  |  |

| Exceeded    | Auto - Programming                                                                                      | 1/07    | Toggle              | 1                   | 0                   | 1                          | Reserved for |  |  |  |

| Time Limits | Programming in Auto - Erase                                                                             | 0       | Toggle              | 1                   | 0                   | 1                          | Future Use   |  |  |  |

|             | Erase in Auto - Erase                                                                                   | 0       | Toggle              | 1                   | 1                   | 1                          | Future Ose   |  |  |  |

| PRODUCT I.D. CODES |      |         |      |          |     |                    |      |             |             |             |             |             |             |             |

|--------------------|------|---------|------|----------|-----|--------------------|------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Туре               | A16  | A15     | A14  | A1       | A0  | Code<br>(HEX)      | I/O7 | I/O6<br>[8] | I/O5<br>[8] | I/O4<br>[8] | I/O3<br>[8] | I/O2<br>[8] | I/O1<br>[8] | I/O0<br>[8] |

| Manufacturer Code  | X    | Х       | X    | VIL      | VIL | 01H                | 0    | 0           | 0           | 0           | 0           | 0           | 0           | . 1         |

| Device Code        | X    | Х       | Х    | VIL      | ViH | 20H                | 0    | 0           | 1           | 0           | 0           | 0           | 0           | 0           |

| Sector Protection  | Sect | tor Add | ress | $V_{1H}$ | ViL | 01H <sup>[9]</sup> | 0    | 0           | 0           | 0           | 0           | 0           | 0           | 1           |

#### NOTES:

- [1] Manufacturer and device codes may also be accessed via a command register write sequence.

- [2] Refer to Command Definition Table for valid DIN during write operations.

- [3] Refer to the section on Sector Address.

- [4] Address bit A16 = X = Don't Care for all address commands except for Programming Address (PA) and Sector Address (SA).

- [5] Bus Operations are defined in Truth Table.

- [6] RA = Address of the memory located on read; PA = Address of the memory located to be programmed. Addresses are latched on the falling edge of the WE pulse; SA = Address of the sector to be erased. The combination of A16, A15, A14 will uniquely select any sector.

- [7] RD = Data read from location RA during read operations;  $\mathsf{DP}$  = Data to be programmed at location PA. Data is latched on the Falling edge of  $\overline{\mathsf{WE}}$ .

- [8] 1/O7 = 1/O7 and/or 1/O15, 1/O23, 1/O31 1/O6 = 1/O6 and/or 1/O14, 1/O22, 1/O30 1/O5 = 1/O5 and/or 1/O13, 1/O21, 1/O29

- I/O4 = I/O4 and/or I/O12, I/O20, I/O28

- I/O3 = I/O3 and/or VO11, I/O19, I/O27 I/O2 = I/O2 and/or I/O10, I/O18, I/O26

- I/O1 = I/O1 and/or I/O9, I/O17, I/O25

- 1/00 = 1/00 and/or 1/08, 1/016, 1/024

- [9] Outputs 01H at protected sector address.

|                         | ERASE A | ND PROGR | AMMING P | ERFORMAN | CE                                         |  |  |

|-------------------------|---------|----------|----------|----------|--------------------------------------------|--|--|

| Donomodou               |         | Limits   |          | Units    | Comments                                   |  |  |

| Parameter<br>           | Min.    | Тур.     | Max.     | Onits    | Comments                                   |  |  |

| Chip/Sector Erase Time  |         | 1        | 30 [1]   | 5        | Excluding 00H programming prior to erasure |  |  |

| Sector Programming Time | -       | 0.25     | -        | ms       |                                            |  |  |

| Chip Programming Time   | -       | 2        | 24 [2]   | 5        | Excludes system - level overhead           |  |  |

| Erase/Program Cycles    | 100,000 | -        | -        | Cycles   |                                            |  |  |

#### **NOTES:**

- [1] The Embedded Algorithm allows for 60 second erase time for military temperature range operation.

- [2] The Embedded Algorithm allows for a longer chip algorithm program time. However, the actual time will considerably less since most bytes program significantly faster than the worst case.

|                   | ABSOLUTE MAXIMUN                | A RATING 3                   |      |

|-------------------|---------------------------------|------------------------------|------|

| Symbol            | Parameter                       | Value                        | Unit |

| Tstc              | Storage Temperature             | -65 to + 150                 | °C   |

| TBIAS             | Temperature Under Bias          | -55 to +125                  | °    |

| $V_{ID}$          | Voltage on A9 <sup>2</sup>      | -0.5 to +13.5                | V    |

| Юит               | Output Short<br>Circuit Current | 100                          | mA   |

| V <sub>I/O</sub>  | Input/Output Voltage 2          | -0.5 to V <sub>DD</sub> +0.5 | V    |

| $V_{\mathrm{DD}}$ | Supply Voltage <sup>2</sup>     | -0.5 to + 7.0                | V    |

| R        | RECOMMENDED OPERATING RANGE |       |                   |      |                |      |  |  |  |  |  |

|----------|-----------------------------|-------|-------------------|------|----------------|------|--|--|--|--|--|

| Symbol   | Characteristi               | c     | Min.              | Тур. | Max.           | Unit |  |  |  |  |  |

| $V_{DD}$ | Supply Voltage              |       | 4.5               | 5.0  | 5.5            | V    |  |  |  |  |  |

| VIL      | Input LOW Vol               | tage  | -0.5 <sup>2</sup> |      | 0.8            | V    |  |  |  |  |  |

| ViH      | Input HIGH Vo               | ltage | 2.0               |      | $V_{DD} + 0.5$ | V    |  |  |  |  |  |

|          | On anating                  | С     | 0                 | +25  | +70            |      |  |  |  |  |  |

| TA       | Operating<br>Temperature    |       | -40               | +25  | +85            | °C   |  |  |  |  |  |

|          | remperature                 | M/Β   | -55               | +25  | +125           |      |  |  |  |  |  |

| VID      | A9 I.D. Voltage             |       | 11.5              |      | 13.0           | ν    |  |  |  |  |  |

| CAI              | PACITANCE 4: TA = | 25°C, | F = 1. | 0MHz      |  |  |

|------------------|-------------------|-------|--------|-----------|--|--|

| Symbol           | Parameter         | Max.  | Unit   | Condition |  |  |

| CCE              | Chip Enable       | 30    |        |           |  |  |

| C <sub>ADR</sub> | Address Input     | 70    |        |           |  |  |

| CwE              | Write Enable      | 70    | pΕ     | VIN - 0V  |  |  |

| COE              | Output Enable     | 70    |        |           |  |  |

| C <sub>I/O</sub> | Data Input/Output | 30    |        |           |  |  |

|        | DO OUTPUT CHARACTERISTICS |              |      |      |      |  |  |  |  |  |  |

|--------|---------------------------|--------------|------|------|------|--|--|--|--|--|--|

| Symbol | Parameter                 | Conditions   | Min. | Max. | Unit |  |  |  |  |  |  |

| Vон    | HIGH Voltage              | Iон = -2.5mA | 2.4  |      | ٧    |  |  |  |  |  |  |

| Vol    | LOW Voltage               | IOL = 12mA   | -    | 0.45 | V    |  |  |  |  |  |  |

|                  | DC OPERATING                                        | <b>CHARACTERISTICS:</b> Over the operation                                                    | ing ranges. | •              |      |

|------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------|----------------|------|

| Symbol           | Characteristics                                     | Test Conditions                                                                               | Min.        | Max.           | Unit |

| lu               | Input Load Current                                  | V <sub>DD</sub> = V <sub>DD</sub> Max., V <sub>IN</sub> = V <sub>SS</sub> to V <sub>DD</sub>  |             | ±4.0           | μΑ   |

| ILO              | Output Leakage Current                              | V <sub>DD</sub> = V <sub>DD</sub> Max., V <sub>OUT</sub> = V <sub>SS</sub> to V <sub>DD</sub> |             | ±4.0           | μА   |

| I <sub>CC1</sub> | V <sub>DD</sub> Active Current for Read             | CE - VIL, OE - VIH                                                                            |             | 120            | mΑ   |

| lcc2             | V <sub>DD</sub> Active Current<br>for Program Erase | CE = VIL, OE = VIH                                                                            |             | 200            | mA   |

| I <sub>SB1</sub> | Standby Current (TTL)                               | CE = V <sub>IH</sub> , OE = V <sub>IL</sub>                                                   |             | 4.0            | mA   |

| I <sub>SB2</sub> | Full Standby Current (CMOS)                         | CE ≥ V <sub>DD</sub> -0.2V                                                                    |             | 200            | μΑ   |

| VIL              | Input Voltage LOW                                   |                                                                                               | -5.0        | 0.8            | V    |

| V <sub>IH</sub>  | Input Voltage HIGH                                  |                                                                                               | 2.0         | $V_{DD} + 0.5$ | V    |

| V <sub>ID</sub>  | A9 Voltage for Auto Select                          | V <sub>DD</sub> +5.0V                                                                         | 11.5        | 13.0           | V    |

| Vol              | Output Voltage LOW                                  | $I_{OUT} = 12$ mA, $V_{DD} = V_{DD}$ Min.                                                     |             | 0.45           | V    |

| Von              | Output Voltage HIGH                                 | lout = -2.5mA, V <sub>DD</sub> = V <sub>DD</sub> Min.                                         | 2.4         |                | V    |

| VIKO             | LOW V <sub>DD</sub> Lock-Out Voltage                |                                                                                               | 3.2         |                | V    |

| AC TEST CONDITIONS                          |            |  |  |  |  |  |  |  |

|---------------------------------------------|------------|--|--|--|--|--|--|--|

| Input Pulse Level                           | 0V to 3.0V |  |  |  |  |  |  |  |

| Input Pulse Rise and Fall Times             | 5ns*       |  |  |  |  |  |  |  |

| Input and Output<br>Timing Reference Levels | 1.5 V      |  |  |  |  |  |  |  |

| OUTPUT LOAD |         |                        |  |  |  |  |  |  |  |

|-------------|---------|------------------------|--|--|--|--|--|--|--|

| Float       | $C_{L}$ | Parameters Measured    |  |  |  |  |  |  |  |

| 1           | 100pF   | except t <sub>DF</sub> |  |  |  |  |  |  |  |

| 2           | 5pF     | t <sub>DF</sub>        |  |  |  |  |  |  |  |

| AC OPERATING CONDITIONS AND CHARACTERISTICS - READ CYCLE: Over operating ranges |                 |                                                                                   |      |      |      |      |      |      |      |      |       |      |      |

|---------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|-------|------|------|

| No.                                                                             | Symbol          | Parameter                                                                         | 45ns |      | 55ns |      | 70ns |      | 90ns |      | 120ns |      | Unit |

|                                                                                 |                 |                                                                                   | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Min.  | Max. | Onit |

| 1                                                                               | trc             | Read Cycle Time                                                                   | 45   |      | 55   |      | 70   |      | 90   |      | 120   |      | ns   |

| 2                                                                               | tacc            | Address to Output Delay                                                           |      | 45   |      | 55   |      | 70   |      | 90   |       | 120  | ns   |

| 3                                                                               | tce             | Chip Enable to Output Valid                                                       |      | 45   |      | 55   |      | 70   |      | 90   |       | 120  | ns   |

| 4                                                                               | toe             | Output Enable to Output Valid                                                     |      | 15   |      | 18   |      | 25   |      | 30   |       | 50   | ns   |

| 5                                                                               | t <sub>DF</sub> | Chip Enable to Output in LOW-Z 4                                                  | 0    | 15   | 0    | 18   | 0    | 25   | 0    | 30   | 0     | 30   | ns   |

| 6                                                                               | tor             | Output Enable to Output in HIGH-Z 4                                               | 0    | 15   | 0    | 18   | 0    | 25   | 0    | 30   | 0     | 30   | ns   |

| 7                                                                               | tон             | Output Hold from Address, Chip Enable or<br>Output Enable, Whichever Occurs First | 0    |      | 0    |      | 0    |      | 0    |      | 0     |      | ns   |

| AC OPERATING CONDITIONS AND CHARACTERISTICS - WRITE CYCLE: Over operating ranges |                 |                              |                         |      |      |      |      |      |      |      |       |      |      |                |

|----------------------------------------------------------------------------------|-----------------|------------------------------|-------------------------|------|------|------|------|------|------|------|-------|------|------|----------------|

| No. Symbol                                                                       | Symbol          | Parameter                    | 45ns                    |      | 55ns |      | 70ns |      | 90ns |      | 120ns |      | Unit |                |

|                                                                                  | Syllibol        | rarameter                    |                         | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max.  | Min. | Max. | Oille          |

| 8                                                                                | twc             | Write Cycle Time             |                         | 45   |      | 55   |      | 70   |      | 90   |       | 120  |      | ns             |

| 9                                                                                | tas             | Address Setup Tin            | ne                      | 0    |      | 0    |      | 0    |      | 0    |       | 0    |      | ns             |

| 10                                                                               | ŧан             | Address Hold Tim             | e                       | 35   |      | 45   |      | 45   |      | 45   |       | 50   |      | ns             |

| 11                                                                               | t <sub>Ds</sub> | Data Setup Time              |                         | 20   |      | 20   |      | 30   |      | 40   |       | 50   |      | ns             |

| 12                                                                               | tрн             | Data Hold Time               |                         | 0    |      | 0    |      | 0    |      | 0    |       | 0    |      | ns             |

| 13                                                                               | toes            | Output Enable Setup Time     |                         | 0    |      | 0    |      | 0    |      | 0    |       | 0    |      | ns             |

| 14                                                                               |                 | Output Enable                | Read                    | 0    |      | 0    |      | 0    |      | 0    |       | 0    |      | n <sub>c</sub> |

| 14                                                                               | <b>t</b> OEH    | Hold Time                    | Toggle and DATA Polling | 10   |      | 10   |      | 10   |      | 10   |       | 10   |      | ns             |

| 15                                                                               | tGHWL           | Read Recovery Ti             | me before Write         | 0    |      | 0    |      | 0    |      | 0    | L     | 0    |      | ns             |

| 16                                                                               | tcs             | Chip Enable Setup Time       |                         | 0    |      | 0    |      | 0    |      | 0    |       | 0    |      | ns             |

| 17                                                                               | tсн             | Chip Enable Hold Time        |                         | 0    |      | 0    |      | 0    |      | 0    |       | 0    |      | ns             |

| 18                                                                               | twp             | Write Pulse Width            |                         | 25   |      | 30   |      | 35   |      | 40   |       | 50   |      | ns             |

| 19                                                                               | twph            | Write Pulse Width HIGH       |                         | 15   |      | 20   |      | 20   |      | 20   |       | 20   |      | ns             |

| 20_                                                                              | twnwh1          | Programming Operation (Min.) |                         | 16   |      | 16   |      | 16   |      | 16   |       | 16   |      | μs             |

| 21                                                                               | twnwH2          | Erase Operation (Min.)       |                         | 1    |      | 1    |      | 1    |      | 1    |       | 1    |      | 5_             |

| 22                                                                               | tvcs            | V <sub>PP</sub> Setup Time   |                         |      |      | 2    |      | 2    |      | 2    |       | 2    |      | μs             |

<sup>\*</sup> Transition between 0.8 and 2.2V.

#### NOTES:

- 1. All voltages are with respect to Vs s.

- 2. -2.0V min, for pulse width less than 20ns (VIL min. = -0.5V at DC level).

- 3. Stresses greater than those under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 4. This parameter is guaranteed and not 100% tested.

- 5. A7 through A16 specify the page address during each high to low transition of WE (or CE) after the software code has been entered.

Dense-Pac Microsystems, Inc.

7321 Lincoln Way ◆ Garden Grove, California 92641-1428 (714) 898-0007 ◆ (800) 642-4477 (Outside CA) ◆ FAX: (714) 897-1772