# SPARCore® Dual-CPU Module

#### **Features**

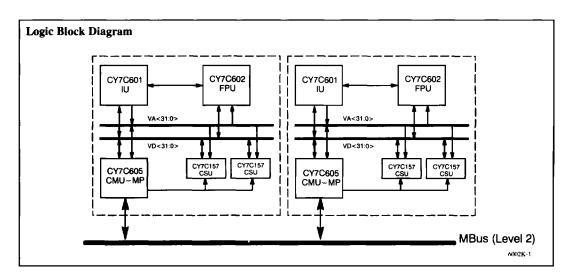

- Complete SPARC<sup>®</sup> Dual-CPU module, including cache

- Two CY7C601 Integer Units (IU)

- Two CY7C602 Floating-Point Units (FPU)

- Two CY7C605 Cache Controller and Memory Management Units for Multiprocessing (CMU-MP)

- Four CY7C157 Cache Storage Units (CSU)

- Full multiprocessing implementation

- Two complete SPARC CPUs

- Hardware support for symmetric, shared-memory multiprocessing

- Level 2 MBus support for cache consistency

- Direct data intervention

- Reflective memory support

# • SPARC compliant

- SPARC Instruction Set Architecture (ISA) compliant

- Conforms to SPARC Reference MMU Architecture

- Conforms to SPARC Level 2 MBus Module Specification (Revision 1.2)

- Available at 25, 33, and 40 MHz

- Each SPARC CPU features:

- SPARC integer and floating-point processing

- Zero-wait-state, 64-Kbyte cache

- Demand-paged virtual memory management

- management

Surface-mount packaging for more compact design

- Provides CPU upgrade path at module level

#### Module design

- Two power and two ground planes

- Minimum-skew clock distribution

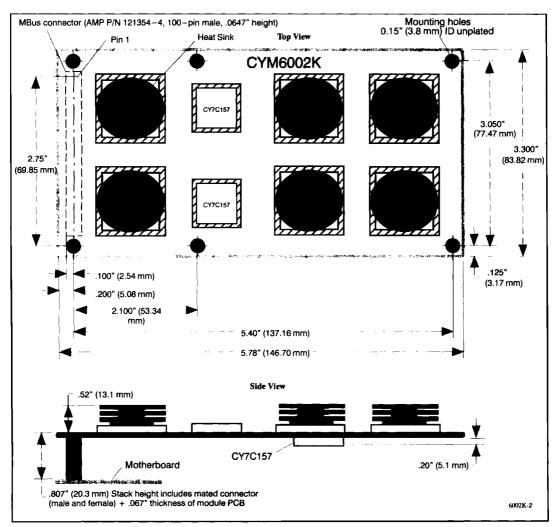

- -- MBus-standard form factor: 3.30" (8.34 cm) x 5.78" (14.67 cm)

- SPARCore MBus connector

- SPARC standard

- Separate power and ground blades (100 active pins)

- Designed for high frequency (low capacitance, low inductance)

- High performance

- -- 59 MIPS (sustained)

- 13 MFLOPS [SP], 9 MFLOPS [DP] (sustained)

- 51 SPECthruput

## **Selection Guide**

|                                   |                   | 6002K-40 | 6002K-33 | 6002K-25 |

|-----------------------------------|-------------------|----------|----------|----------|

| Operating Frequency (MHz)         |                   | 40       | 33       | 25       |

| Typical Supply Current (mA)       | Commercial        | 3700     | 3380     | 3040     |

| Maximum Supply Current (mA)       | Commercial        | 5600     | 5100     | 4600     |

| Required Ambient Airflow - Module | Top Side (LFM)    | 300      | 300      | 300      |

| Required Ambient Airflow - Module | Bottom Side (LFM) | 200      | 200      | 200      |

SPARCore is a trademark of ROSS Technology, Inc. SPARC is a trademark of SPARC International

#### **Functional Description**

The CYM6002K SPARCore Module is a complete dual-SPARC CPU board. It is packaged as a compact PCB and interfaces to the remainder of the system via a SPARC-standard MBus connector. Each of the two CPUs on the CYM6002K consists of a high-speed integer unit (CY7C601), floating-point unit (CY7C602), cache controller and memory management unit for multiprocessing systems (CY7C605), and two 16K x 16 CY7C157 cache storage units (providing a 64-Kbyte cache for the CPU). The CYM6002K deliverssustained performance of 59 MIPS and 13/9 (single precision/double precision) MFLOPS at an operating frequency of 40 MHz. The CYM6002K also achieves a SPECthruput rating of 51. IC components are surface mounted for a compact footprint and high frequency of operation. The CYM6002K fits within the clearance envelope for MBus modules per the SPARC MBus Specification.

The CYM6002K interfaces to the rest of the system via the SPARC MBus and conforms to the SPARC Reference MMU. This standardization allows the CYM6002K to be replaced by other Cypress SPARC MBus-based CPU modules without having to modify any portion of the memory system or I/O. This CPU "building block" strategy not only decreases the user's time to market, but provides a mechanism for upgrading in the field. For a more complete description of the individual SPARC components used in the CYM6002K (i.e., the CY7C601 IU, the CY7C602 FPU, the CY7C605 CMU-MP, and the CY7C157 CSUs), please refer to the Cypress SPARC RISC User's Guide.

#### **Module Design**

#### Clock Distribution

The CYM6002K uses four module clock signals (MCLK0, MCLK1, MCLK2, and MCLK3) as defined in the MBus Specification. MCLK0 and MCLK2 are used for CPU0, and MCLK1 and MCLK3 for CPU1. In order to minimize clock skew, all traces have

been carefully routed. All clock lines are routed on inner layers of the module PCB, and their impedances have been matched. All clock lines have diode termination to reduce signal undershoot and overshoot.

#### MBus Connector (Module)

The CYM6002K interface is via the 100-pin SPARC MBus connector, which is a two-row male connector with 0.0501 spacing (AMP "microstrip" part number 121354-4). The connector is a controlled impedance-type (500 ±10%) based on a microstrip configurationthat provides a controlled characteristic impedance plus very low inductance and capacitance. Separate power and groundblades are provided for isolation to prevent noise transference. Table 1 details the CYM6002K standard connector pinout. This MBus connector supports Level 2 MBus.

#### Mating MBus Connector (System Interface Board)

The module connects to the system interface by means of a standard MBus female connector (AMP vertical receptacle assembly, part number 121340-4).

#### Reset and Interrupt Signals

A power-on reset signal is generated to the module from the MBus via the RSTIN signal. Each CPU has its own direct set of interrupt lines. Level sensitive interrupts (15 max) are generated to each CY7C601 via the IRL0[3:0] and IRL1[3:0] lines from the MBus. A value of 0000b means that there is no interrupt, while a value of 1111b means an NMI is being asserted. IRL values between 0 and 14 represent interrupt requests that can be masked by the processor.

#### MBus Request and Grant Signals

Two separate sets of request and grant signals (MBR[0], MBG[0], MBR[1], and MBG[1]), one for each CPU, are generated to/from the CYM6002K modules to arbitration logic on the motherboard.

Table 1. MBus Connector Pinout[1]

|      |             |          |      | able 1. Mibus C |    |      |               | Blade    | Pin# | Signal Name |

|------|-------------|----------|------|-----------------|----|------|---------------|----------|------|-------------|

| Pin# | Signal Name | Blade    | Pin# | Signal Name     | l  | Pin# | Signal Name   |          |      | MERR        |

| 1    | RES1        | Blade #1 | 2    | RES2            | -[ | 51   | MCLK2         | Ground   | 52   | MAS         |

| 3    | RES3        | Ground   | 4    | RES4            | -  | 53   | MCLK3         | _        | 54   | MAS<br>MBB  |

| 5    | RES5        |          | 6    | IRL0[1]         |    | 55   | MBR[1]        | Ground   | 56   |             |

| 7    | IRL0[0]     | Ground   | 8    | IRL0[3]         |    | 57   | <u>MBG[1]</u> |          | 58   | SPARE1      |

| 9    | IRL0[2]     |          | 10   | RES6            |    | 59   | MAD[32]       |          | 60   | MAD[33]     |

| 11   | MAD[0]      | Ground   | 12   | MAD[1]          |    | 61   | MAD[34]       | Blade #4 | 62   | MAD[35]     |

| 13   | MAD[2]      |          | 14   | MAD[3]          |    | 63   | MAD[36]       | +5V      | 64   | MAD[37]     |

| 15   | MAD[2]      | Ground   | 16   | MAD[5]          |    | 65   | MAD[38]       | Ì        | 66   | MAD[39]     |

| 17   | MAD[4]      | 0.04     | 18   | MAD[7]          | 1  | 67   | MAD[40]       | +5V      | 68   | MAD[41]     |

| 19   | MAD[8]      |          | 20   | MAD[9]          |    | 69   | MAD[42]       |          | 70   | MAD[43]     |

| 21   | MAD[10]     | Blade #2 | 22   | MAD[11]         |    | 71   | MAD[44]       | +5V      | 72   | MAD[45]     |

|      | MAD[10]     | +5V      | 24   | MAD[13]         |    | 73   | MAD[46]       |          | 74   | MAD[47]     |

| 23   | MAD[12]     | '3'      | 26   | MAD[15]         |    | 75   | MAD[48]       | +5V      | 76   | MAD[49]     |

| 25   | 1           | +5V      | 28   | MAD[17]         |    | 77   | MAD[50]       |          | 78   | MAD[51]     |

| 27   | MAD[16]     | '3'      | 30   | MAD[19]         | 1  | 79   | MAD[52]       | 1        | 80   | MAD[53]     |

| 29   | MAD[18]     | +5V      | 32   | MAD[21]         |    | 81   | MAD[54]       | Blade #5 | 82   | MAD[55]     |

| 31   | MAD[20]     | ""       | 34   | MAD[23]         |    | 83   | MAD[56]       | Ground   | 84   | MAD[57]     |

| 33   | MAD[22]     | +5V      | 36   | MAD[25]         |    | 85   | MAD[58]       |          | 86   | MAD[59]     |

| 35   | MAD[24]     | +3V      | 38   | MAD[27]         | 1  | 87   | MAD[60]       | Ground   | 88   | MAD[61]     |

| 37   | MAD[26]     |          | 40   | MAD[27]         |    | 89   | MAD[62]       |          | 90   | MAD[63]     |

| 39   | MAD[28]     | DI 1 #2  | 40   | MAD[23]         |    | 91   | SPARE2        | Ground   | 92   | IRL1[0]     |

| 41   | MAD[30]     | Blade #3 | 42   | MSH             | 1  | 93   | IRL1[1]       |          | 94   | IRL1[2]     |

| 43   | MBR[0]      | Ground   | 1    | MIH             | 1  | 95   | IRL1[3]       | Ground   | 96   | AERR        |

| 45   | MBG[0]      |          | 46   | MRTY            |    | 97   | RSTIN         |          | 98   | RES7        |

| 47   | MCLK0       | Ground   | 48   | 1               | 1  | 99   | RES8          | 1        | 100  | RES9        |

| 49   | MCLK1       |          | 50   | MRDY            | ┚  |      | IXLO0         |          |      |             |

Note:

1. RES pins are not used in the CYM6002K but are reserved for other MBus module upgrades. See the System Design Considerations section for the assignments of these reserved pins per the SPARC MBus Specification.

# Maximum Ratings[2]

(Provided as guidelines; not tested.)

| Storage Temperature $-20^{\circ}$ C to $+75^{\circ}$  | C |

|-------------------------------------------------------|---|

| Ambient Temperature with                              |   |

| Power Applied $0^{\circ}$ C to $+50^{\circ}$          | C |

| Supply Voltage to Ground Potential $-0.5$ V to $+7.0$ | V |

| Input Voltage - 0.3V to +7.0                          | v |

# **Operating Range**

| Range      | Ambient<br>Temperature <sup>[3]</sup> | V <sub>CC</sub> |

|------------|---------------------------------------|-----------------|

| Commercial | 0°C to +50°C                          | 5V ±5%          |

# DC Electrical Characteristics Over the Operating Rangel<sup>4</sup>]

| Parameters        | Description                                 | Test Conditions                                  | Min.  | Max.     | Units |

|-------------------|---------------------------------------------|--------------------------------------------------|-------|----------|-------|

| V <sub>OH</sub>   | Output HIGH Voltage                         | $V_{\rm CC} = Min., I_{\rm OH} = -2.0 \text{mA}$ | 2.4   |          | V     |

| V <sub>OL</sub>   | Output LOW Voltage                          | $V_{CC} = Min., I_{OL} = 8.0 \text{ mA}$         |       | 0.5      | V     |

| V <sub>IH</sub>   | Input HIGH Voltage                          |                                                  | 2.1   | $V_{CC}$ | v     |

| V <sub>IL</sub>   | Input LOW Voltage                           |                                                  | - 0.5 | 0.8      | V     |

| I <sub>IZ</sub>   | Input Leakage Current (non-clock pins)      | $V_{CC} = Max., V_{SS} \le V_{OUT} \le V_{CC}$   | - 10  | +10      | mA    |

| I <sub>CLKZ</sub> | Input Leakage Current (clock pins)          | $V_{CC} = Max., V_{SS} \le V_{OUT} \le V_{CC}$   | - 40  | +40      | mA    |

| I <sub>OZ</sub>   | Output LeakageCurrent                       | $V_{CC} = Max., V_{SS} \le V_{OUT} \le V_{CC}$   | - 15  | +15      | mA    |

| I <sub>SC</sub>   | Output Short Circuit Current <sup>[4]</sup> | $V_{CC} = Max., V_{OUT} = 0V$                    | - 30  | - 350    | mA    |

### Capacitance<sup>[5]</sup>

| Parameters         | Description             | Test Conditions                   | Max. | Units |

|--------------------|-------------------------|-----------------------------------|------|-------|

| C <sub>IN</sub>    | InputCapacitance        | $V_{CC} = 5.0V$                   | 20   | pF    |

| C <sub>OUT</sub>   | Output Capacitance      | $T_A = 25^{\circ}C$ , $f = 1 MHz$ | 24   | pF    |

| C <sub>IO</sub>    | Input/OutputCapacitance | 1                                 | 30   | pF    |

| C <sub>INCLK</sub> | Clock Input Capacitance |                                   | 70   | pF    |

### Notes:

- All power and ground pins must be connected to other pins of the same type before any power is applied to the module. At least one clock cycle must be applied to the module to set up the internal chip drivers properly.

- Ambient temperature is the temperature of the air in immediate proximity of the module.

- 4. Not more than one output should be tested at one time. Duration of the short circuit should not be more than one second.

- Tested initially and after any design or process changes that may affect these parameters.

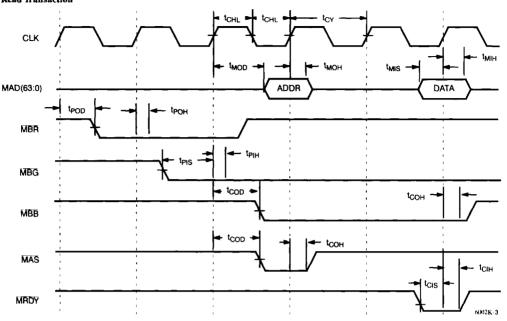

#### AC Electrical Characteristics Over the Operating Rangel<sup>6,7</sup>] Synchronous signals[8]

|                                |                                             | Signal | CYM60 | 02K-40 | CYM60 | 02K-33 | CYM60 | 02K-25 |                  |

|--------------------------------|---------------------------------------------|--------|-------|--------|-------|--------|-------|--------|------------------|

| Parameter                      | Description                                 | Edge   | Min.  | Max.   | Min.  | Max.   | Min.  | Max.   | Units            |

| tCY                            | Clock Cycle                                 |        | 25    |        | 30    |        | 40    |        | ns               |

| t <sub>CHL</sub>               | Clock High and Low                          |        | 11.5  | 13.5   | 13.5  | 16.5   | 18.5  | 21.5   | ns               |

| t <sub>R</sub> ,t <sub>F</sub> | Clock Rise and Fall (between 0.8V and 2.0V) |        | 0.8   |        | 0.8   |        | 0.8   |        | v <sub>/ns</sub> |

| tsku                           | Clock Skew <sup>[9]</sup>                   |        |       | 1.0    |       | 2.0    |       | 2.0    | ns               |

| t <sub>MOD</sub>               | MAD(63:0) Output Delay                      | CLK+   |       | 20     |       | 22     |       | 30     | ns               |

| t <sub>MOH</sub>               | MAD(63:0) Output Valid                      | CLK+   | 4     |        | 4     |        | 4     |        | ns               |

| t <sub>MIS</sub>               | MAD(63:0) Input Set-Up                      | CLK+   | 3.5   |        | 5.5   |        | 7.5   |        | ns               |

| t <sub>MIH</sub>               | MAD(63:0) Input Hold                        | CLK+   | 4.5   |        | 4.5   |        | 4.5   |        | ns               |

| t <sub>COD</sub>               | MBus Bused Control Output Delay             | CLK+   |       | 19     |       | 21     |       | 29     | ns               |

| t <sub>COH</sub>               | MBus Bused Control Output Valid             | CLK+   | 4     |        | 4     |        | 4     |        | ns               |

| t <sub>CIS</sub>               | MBus Bused Control Input Set-Up             | CLK+   | 5.5   |        | 8     |        | 10    |        | ns               |

| t <sub>ClH</sub>               | MBus Bused Control Input Hold               | CLK+   | 4.5   |        | 4.5   |        | 4.5   |        | ns               |

| t <sub>POD</sub>               | MBus Point-to-Point Control Output Delay    | CLK+   |       | 17     |       | 19     |       | 27     | ns               |

| tPOH                           | MBus Point-to-Point Control Output Valid    | CLK+   | 3.5   |        | 3.5   |        | 3.5   |        | ns               |

| tpiS                           | MBus Point-to-Point Control Input Set-Up    | CLK+   | 7.5   |        | 9     |        | 11    |        | ns               |

| tPIH                           | MBus Point-to-Point Control Input Hold      | CLK+   | 4     |        | 4     |        | 4     |        | ns               |

| t <sub>RIS</sub>               | POR Input Setup                             | CLK+   | 5     |        | 5     |        | 5     |        | ns               |

| t <sub>RIH</sub>               | POR Input Hold                              | CLK+   | 6     |        | 6     |        | 6     |        | ns               |

| t <sub>IIS</sub>               | IRL Input Setup                             | CLK+   | 5     |        | 5     |        | 5     |        | ns               |

| tIIH                           | IRL Input Hold                              | CLK+   | 7     | ļ      | 7     |        | 7     |        | ns               |

# Asynchronous signals [10, 11]

|                       | · · · · · · · · · · · · · · · · · · · | Signal | CYM60 | 02K-40 | CYM60 | 02K-33 | CYM60 | D2K-25 |       |

|-----------------------|---------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|

| Parameter             | Description                           | Type   | Min.  | Max.   | Min.  | Max.   | Min.  | Max.   | Units |

| RSTIN <sup>[12]</sup> | MBus Reset                            | Input  | 500   |        | 500   |        | 500   |        | ms    |

# Notes:

- Notes:

6. Test conditions assume signal transition times of 3 ns or less, a timing reference level of 1.5V, input levels of 0 to 3.0V, and output loading of 80-pF capacitance, not including the module itself (with the exception of MBR, tested with an output loading of 40 pF).

7. All measurements made at MBus connector.

- All timing parameters are relative to one of the two processors (e.g.,  $t_{MOD}$  is guaranteed relative to MCLK0 for Processor 0 and relative to MCLK1 for Processor 1.)

- Measured between any two CLK signals. The relaxed skew requirements for 25 and 33 MHz should be considered carefully since upgrading to 40 MHz requires a 1.0-ns or shorter clock skew.

- 10. The module requires that the interrupt lines (IRL0[0:3]) remain valid until the interrupt is cleared by software with a minimum of two clock cycles.

- The asynchronous error signal, ĀĒRR, will remain asserted until the AFAR register in the CY7C605 is read by software.

- 12. Measured at room temperature.

# Mechanical Dimensions[13, 14, 15]

- Notes: 13. Drawing is not to scale.

- All tolerances are per ANSI/IPC-D-300G Specification (Class B).

These dimensions are CYM6002K-specific but are also within the mechanical limits specified for MBus modules. To ensure compliance with all future MBus modules, systems developers should design to the MBus module envelope per the SPARC MBus Specification.

# MBus Timing Diagram Single Read Transaction

### **System Design Considerations**

The CYM6002K implements a subset of all possible MBus signals; signals that are optional and/or specifically for JTAG test capabilities may not be supported. However, the MBus connector, per the SPARC MBus Specification, defines the assignments listed in *Table 2* for pins reserved on the CYM6002K. Systems designers should be aware of these assignments in order to more easily upgrade to other and future MBus modules.

Table 2. Pins Reserved on CYM6002K

| Pin# | Signal Name | Pin# | Signal Name |

|------|-------------|------|-------------|

| 1    | SCANDI      | 2    | SCANTMS1    |

| 3    | SCANDO      | 4    | SCANTMS2    |

| 5    | SCANCLK     | 10   | INTOUT      |

| 98   | ID[1]       | 99   | ID[2]       |

| 100  | ID[3]       |      | 1           |

Document #: 38-R-00008

All MAD, bused control, and point-to-point control signals use 8-mA drivers (with the exception of  $\overline{MAS}$ , which uses a 16-mA driver). The  $\overline{MSH}$  and  $\overline{AERR}$  signals use an open drain driver.

The following pull-up resistors are recommended for the MBus signals:  $\overrightarrow{MSH}$  is pulled up to 5V with a 620 $\Omega$  resistor;  $\overrightarrow{AERR}$  is pulled up to 5V with a 1.5 K $\Omega$  resistor; all other MBus signals are pulled up to 5V with 10 K $\Omega$  resistors.

As the frequency of operation increases, transmission line effects play a bigger role. Care must be taken to keep skew between any two clock signals at the MBus connector within the specifications given in the Synchronous Signals table in the ACCharacteristics section. MBus signal lines must be routed carefully to minimize crosstalk and interference. A thorough SPICE analysis of the motherboard design is recommended. For a discussion of the intricacies of high-frequency design, see the application note titled "High-SpeedSPARC CMOS System Design" in the *Cypress Applications Handbook*.

Use of HH Smith #4387 (3/4" length by 1/4" OD) stand-offs on the motherboard or equivalent is recommended to support the module and prevent damage to the connector.