# PRELIMINARY DATA SHEET

# MOS INTEGRATED CIRCUIT $\mu PD9611$

# FOUR-CHANNEL PCM CODEC

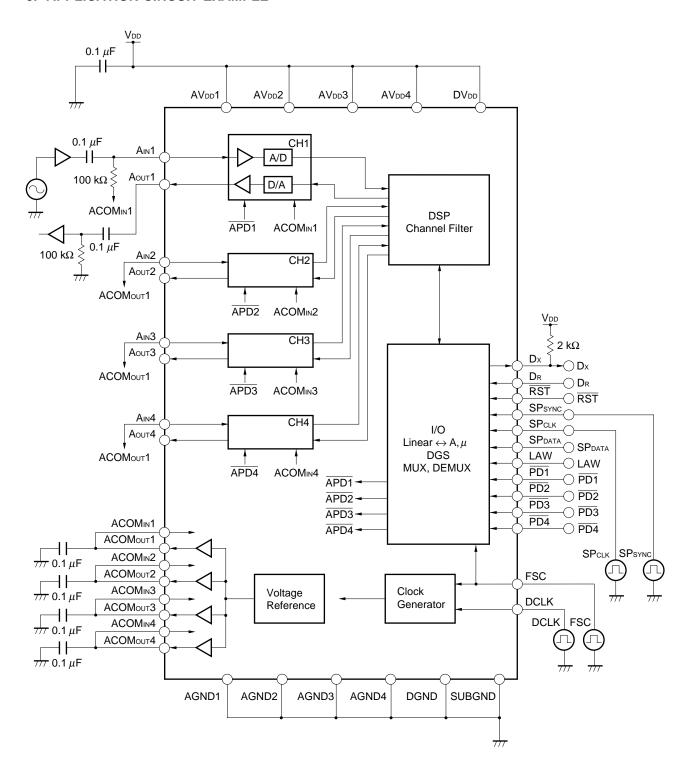

The  $\mu$ PD9611 incorporates 4-channel A-law/ $\mu$ -law PCM CODECs compliant with ITU-T Recommendation G.711/ G.714 and is suitable for applications such as PBX analog subscriber line circuits.

Its gain setting circuit allows transmit/receive gain to be set for 4 channels independently by externally inputting digital signals.

#### **FEATURES**

- Single-chip CMOS monolithic LSI

- ITU-T Recommendation G.711/G.714 compliant

- Four-channel PCM CODECs integrated on a single chip

- Compatible with A-law and μ-law

- Digital gain setting for each channel

- Transmit: +7.5 to -8.0 dB (0.5 dB step)

- Receive: 0 to -15.5 dB (0.5 dB step)

- Data transfer system: Transmit/receive synchronization

- Data rate: 2048 kHz

- +5 V single power supply

- Power down function for each channel

- Low power consumption

## **ORDERING INFORMATION**

| Part Number | Package                     |

|-------------|-----------------------------|

| μPD9611GT   | 48-pin shrink SOP (375 mil) |

The information in this document is subject to change without notice.

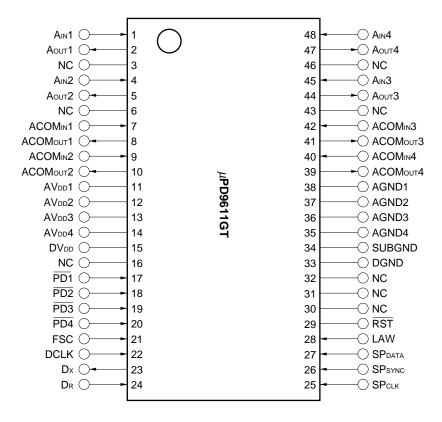

## PIN CONFIGURATION (Top View)

## 48-pin shrink SOP (375 mil)

ACOMIN1-ACOMIN4 : Analog common voltage in Dx : Transmit PCM data out ACOMOUT1-ACOMOUT4: Analog common voltage out FSC : Frame synchronous clock in

AGND1-AGND4 : Analog ground LAW : A-law/ $\mu$ -law control in AIN1-AIN4 : Analog signal in NC : No connection AOUT1-AOUT4 : Analog signal out  $\overline{PD1}$ - $\overline{PD4}$  : Power down control AVDD1-AVDD4 : Analog power supply  $\overline{RST}$  : Reset in

DCLK : Data clock in SPclk : Serial port data clock in DGND : Digital ground SPDATA : Serial port data in

DR : Receive PCM data in SPsync : Serial port synchronous clock in

DVDD : Digital power supply SUBGND : Sub ground

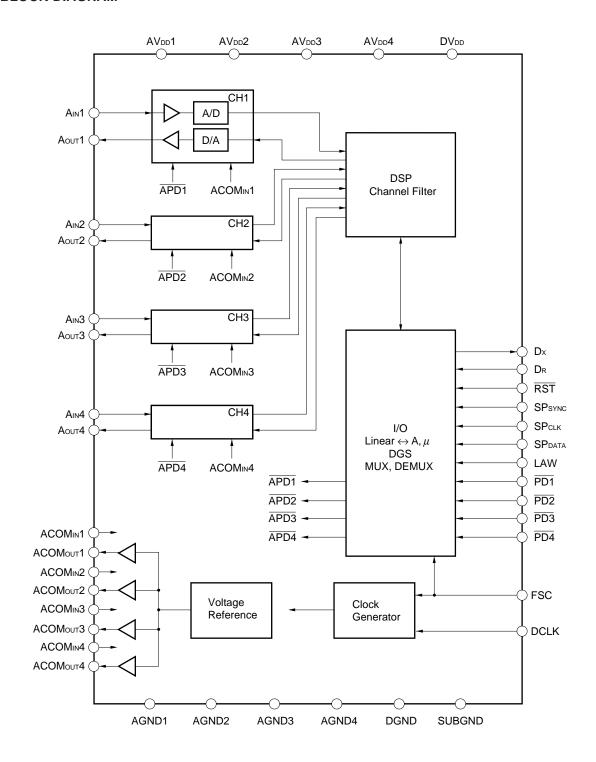

## **BLOCK DIAGRAM**

# 1. PIN DESCRIPTION

| Pin No. | Symbol               | I/O | Name and Function                                                                                                                                                                                                                       |

|---------|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Ain1                 | I   | Transmit analog input pin for channel 1 When not used, connect to ACOMou⊤1 pin.                                                                                                                                                         |

| 2       | Аоит1                | 0   | Receive analog output pin for channel 1                                                                                                                                                                                                 |

| 3       | NC                   | _   | Leave this pin open.                                                                                                                                                                                                                    |

| 4       | Ain2                 | I   | Receive analog input pin for channel 2 When not used, connect to ACOMoυτ1 pin.                                                                                                                                                          |

| 5       | Аоит2                | 0   | Transmit analog output pin for channel 2                                                                                                                                                                                                |

| 6       | NC                   | -   | Leave this pin open.                                                                                                                                                                                                                    |

| 7       | ACOM <sub>IN</sub> 1 | I   | Signal reference voltage input for channel 1                                                                                                                                                                                            |

| 8       | АСОМоит1             | 0   | Signal reference voltage output for channel 1                                                                                                                                                                                           |

| 9       | ACOM <sub>IN</sub> 2 | I   | Signal reference voltage input for channel 2                                                                                                                                                                                            |

| 10      | АСОМоит2             | 0   | Signal reference voltage output for channel 2                                                                                                                                                                                           |

| 11      | AV <sub>DD</sub> 1   | -   | Analog power supply pin for channel 1 $+5 \pm 0.25 \text{ V}$                                                                                                                                                                           |

| 12      | AV <sub>DD</sub> 2   | -   | Analog power supply pin for channel 2 $\pm 5 \pm 0.25 \text{ V}$                                                                                                                                                                        |

| 13      | AV <sub>DD</sub> 3   | -   | Analog power supply pin for channel 3 $+5 \pm 0.25 \text{ V}$                                                                                                                                                                           |

| 14      | AV <sub>DD</sub> 4   | -   | Analog power supply pin for channel 4 $+5 \pm 0.25 \text{ V}$                                                                                                                                                                           |

| 15      | DV <sub>DD</sub>     | -   | Digital power supply pin $+5 \pm 0.25 \text{ V}$                                                                                                                                                                                        |

| 16      | NC                   | _   | Leave this pin open.                                                                                                                                                                                                                    |

| 17      | PD1                  | I   | Power-down control input pin for channel 1 Channel 1 enters power-down mode when this signal is low level. The output of Dx pin for channel 1 becomes high-impedance and Aout1 becomes signal reference voltage in the power-down mode. |

| 18      | PD2                  | I   | Power-down control input pin for channel 2 Channel 2 enters power-down mode when this signal is low level. The output of Dx pin for channel 2 becomes high-impedance and Aout2 becomes signal reference voltage in the power-down mode. |

| 19      | PD3                  | _   | Power-down control input pin for channel 3 Channel 3 enters power-down mode when this signal is low level. The output of Dx pin for channel 3 becomes high-impedance and Aout3 becomes signal reference voltage in the power-down mode. |

| 20      | PD4                  | 1   | Power-down control input pin for channel 4 Channel 4 enters power-down mode when this signal is low level. The output of Dx pin for channel 4 becomes high-impedance and Aout4 becomes signal reference voltage in the power-down mode. |

| 21      | FSC                  | I   | Frame synchronous clock input pin (8 kHz)                                                                                                                                                                                               |

| 22      | DCLK                 | I   | Data clock input pin (2048 kHz)                                                                                                                                                                                                         |

| 23      | Dx                   | 0   | Transmit PCM data output pin  This pin outputs PCM data for channel 1 to 4 in synchronization with rising edges of DCLK after rising edges of FSC. It becomes high-impedance for other timings.                                         |

| 24      | Dr                   | I   | Receive PCM data input pin  This pin inputs PCM data for channel 1 to 4 in synchronization with falling edges of DCLK after rising edges of FSC.                                                                                        |

| 25      | SPclk                | I   | Setting data clock input pin                                                                                                                                                                                                            |

| 26      | SPsync               | I   | Setting synchronous clock input pin                                                                                                                                                                                                     |

| 27      | SPDATA               | I   | Setting data input pin                                                                                                                                                                                                                  |

| Pin No. | Symbol               | I/O | Name and Function                                 |

|---------|----------------------|-----|---------------------------------------------------|

| 28      | LAW                  | I   | A-law/μ-law select pin in common to four channels |

|         |                      |     | L: A-law, H: μ-law                                |

| 29      | RST                  | _   | Reset input, power-on reset pin                   |

|         |                      |     | H: normal operation                               |

|         |                      |     | L: internal registers are in the default status.  |

| 30-32   | NC                   | _   | Leave this pin open.                              |

| 33      | DGND                 | -   | Digital ground pin                                |

| 34      | SUBGND               | _   | Substrate ground pin                              |

| 35      | AGND4                | _   | Analog ground pin for channel 4                   |

| 36      | AGND3                | _   | Analog ground pin for channel 3                   |

| 37      | AGND2                | _   | Analog ground pin for channel 2                   |

| 38      | AGND1                | _   | Analog ground pin for channel 1                   |

| 39      | АСОМоит4             | 0   | Signal reference voltage output for channel 4     |

| 40      | ACOMin4              | I   | Signal reference voltage input for channel 4      |

| 41      | АСОМоит3             | 0   | Signal reference voltage output for channel 3     |

| 42      | ACOM <sub>IN</sub> 3 | I   | Signal reference voltage input for channel 3      |

| 43      | NC                   | _   | Leave this pin open.                              |

| 44      | Аоит3                | 0   | Receive analog output pin for channel 3           |

| 45      | Ain3                 | - 1 | Transmit analog input pin for channel 3           |

|         |                      |     | When not used, connect to ACOMou⊤1 pin.           |

| 46      | NC                   | _   | Leave this pin open.                              |

| 47      | Аоит4                | 0   | Receive analog output pin for channel 4           |

| 48      | Ain4                 | I   | Transmit analog input pin for channel 4           |

|         |                      |     | When not used, connect to ACOMou⊤1 pin.           |

#### 2. CAUTIONS ON USE

#### (1) Absolute maximum ratings

Application of voltage or current in excess of the absolute maximum ratings to the  $\mu$ PD9611 may result in damage due to latch up, etc. Be especially cautions about power supply noise, etc.

#### (2) Wiring pattern

The design of the ground pattern is extremely important for operating the  $\mu$ PD9611 with high precision. Connect the analog ground pins (AGND1 to AGND4), digital ground pin (DGND) and substrate ground pin (SUBGND) close to the IC pins, and connect to a wide analog ground line on the board.

#### (3) Addition of bypass capacitors for power supply pins

Because the  $\mu$ PD9611 uses many internal high-frequency operational amplifiers, high power supply impedance can cause instability (such as oscillation) in these internal operational amplifiers. To suppress such instability and eliminate power supply noise, connect all power supply pins (AV<sub>DD</sub>1 to AV<sub>DD</sub>4, DV<sub>DD</sub>) close to the IC pins, and put bypass capacitors (C<sub>VDD</sub> = approximately 0.1  $\mu$ F) having superior high-frequency characteristics very close to the pins.

#### (4) Addition of bypass capacitors for ACOM pins

The  $\mu$ PD9611 incorporates references voltages for signal sources. Superposing of noise on these reference voltages may have adverse effects on transmission characteristics, etc. Therefore, connect the ACOMout pin and ACOMin pin close to the IC pins, and put bypass capacitors (Cacom = approximately 0.1  $\mu$ F) having superior high-frequency characteristics very close to the pins.

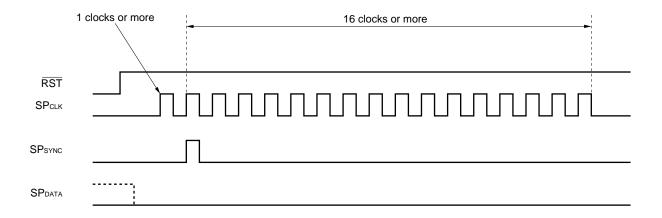

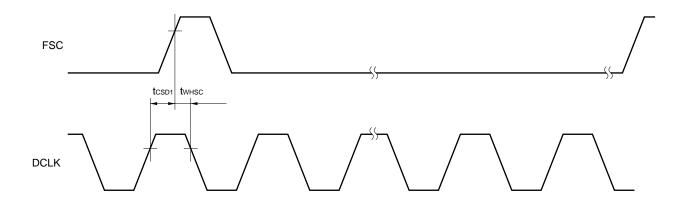

#### (5) Control or SPDATA pin on reset

When inputting the setting data from the SPDATA pin after the  $\mu$ PD9611 is reset, first input the following patterns to reset to 0 the couter used to fetch data from the SPDATA pin.

After ther RST pin has been set to the high level, input 1 clock or more to the SPclk pin, set the SPsyNc pin to the high level and input 16 clocks more to the SPclk pin.

During this operation, the SPDATA pin is held at the low level. Afterwards, input the setting data.

#### 3. GENERAL OPERATION

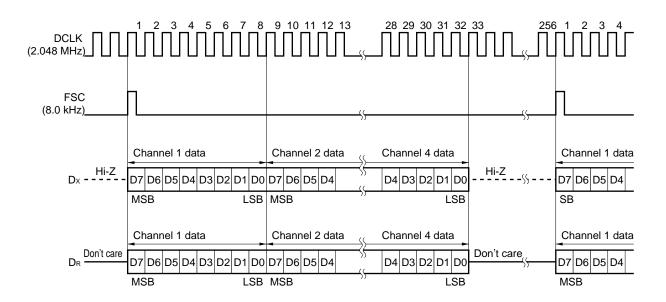

#### (1) PCM data transfer

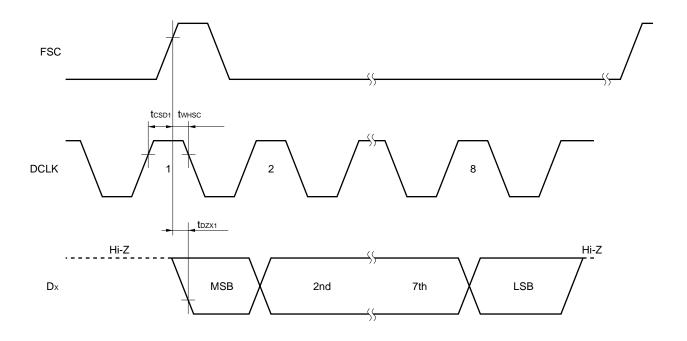

In the transmit section, if FSC pin is set to the high level in synchronization with the rising edge  $(\uparrow)$  of the data clock applied to the DCLK pin, the Dx pin becomes active and sign bit data (MSB) of channel 1 is output. The following data of 7 bits is clocked out in synchronization with the rising edge  $(\uparrow)$  of each data clock. Sign bit data (MSB) of channel 2 is output in synchronization with the rising edge  $(\uparrow)$  of the 9th data clock. In the same manner, each data up to channel 4 is output and the rising edge  $(\uparrow)$  of the 33rd data clock then sets the Dx pin to high-impedance state.

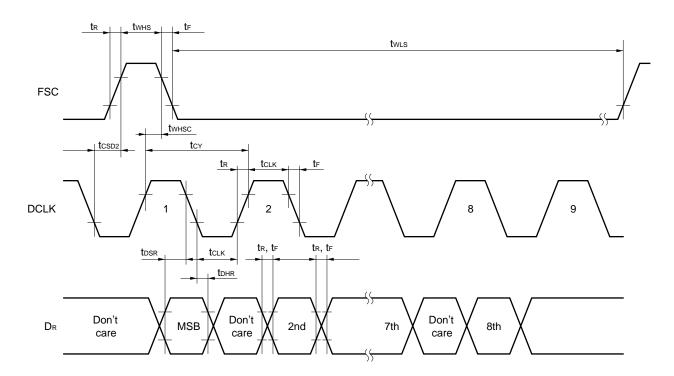

Similarly, in the receive section, if the FSC pin is set to the high level in synchronization with the rising edge ( $\uparrow$ ) of the data clock applied to the DCLK pin, data of D<sub>R</sub> pin is latched by the falling edges ( $\downarrow$ ) of the data clock and consecutively clocked in.

#### (2) Power down control

The  $\mu$ PD9611 has the following two methods for power down control and is able to control power-down independently for each channel.

- Sets pins  $\overline{PD1}$  to  $\overline{PD4}$  to high or low level.

- Inputs 8-bit setting data from SPDATA pin (see (5) Control of SPDATA pin).

Internal data is the logical sum of PD1 to PD4 pin state and 8-bit setting data input.

If the internal data is 0, the channel enters the power-down state. If the internal data is 1, the channel enters the power-up state. In the power down state, PCM data in the channel goes to high-impedance state and analog output becomes the signal reference voltage level.

| 8-Bit Setting Data<br>(Channel 1) | PD1 Pin | Internal Data |

|-----------------------------------|---------|---------------|

| 0                                 | 0       | 0             |

| 1                                 | 0       | 1             |

| 0                                 | 1       | 1             |

| 1                                 | 1       | 1             |

Remarks 1. 0: Power down, 1: Power up

2. The settings are the same for channel 2 to channel 4.

#### (3) A-law/ $\mu$ -law control

The  $\mu$ PD9611 has the following two methods for A-law/ $\mu$ -law control.

- · Sets LAW pin to high or low level.

- Inputs 8-bit setting data from SPDATA pin (see (5) Control of SPDATA pin).

Internal data is the logical sum of LAW pin state and 8-bit setting data input.

If the internal data is 0, the  $\mu$ PD9611 enters A-law mode. If the internal data is 1, the  $\mu$ PD9611 enters  $\mu$ -law mode.

| 8-Bit Setting Data | LAW Pin | Internal Data |

|--------------------|---------|---------------|

| 0                  | 0       | 0             |

| 1                  | 0       | 1             |

| 0                  | 1       | 1             |

| 1                  | 1       | 1             |

**Remark** 0: A-law, 1:  $\mu$ -law

#### (4) Gain Setting control for transmit/receive

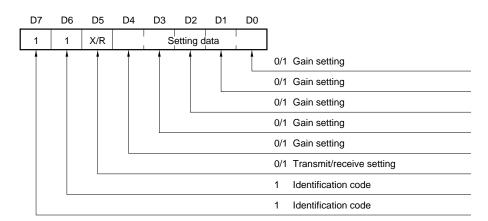

The  $\mu$ PD9611 can control gain settings independently for the transmit/receive by inputting 8-bit setting data (see **(5) Control of SPDATA pin**) from the SPDATA pin for four channels. Gain can be set from +7.5 to -8.0 dB for the transmit and +0.0 dB to -15.5 dB for the receive in 0.5 dB steps.

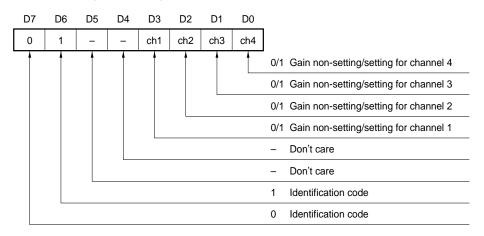

8-bit setting data input from SPDATA pin specifies the channel set in the first 8 bits, and performs selection of transmit/receive and gain setting in the second 8 bits.

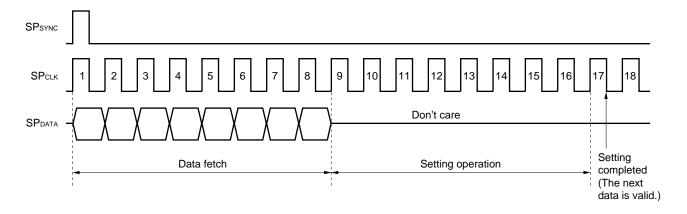

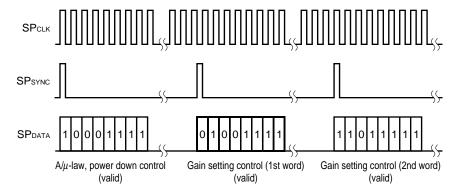

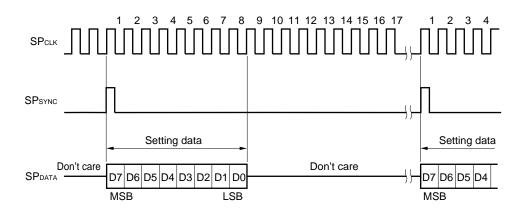

#### (5) Control of SPDATA pin

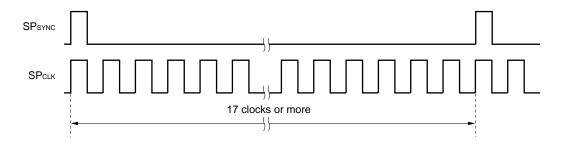

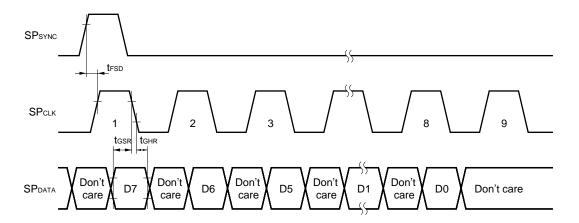

If SPsync pin is set to the high level in synchronization with the rising edge  $(\uparrow)$  of the data clock applied to the SPclk pin, data of the SPdata pin is latched by the falling edge  $(\downarrow)$  of the data clock and consecutively fetched in.

After the 8-bit data has been fetched, the setting operation is performed according to the data.

This setting operation is performed during the 8 clocks after fetching the data and the next data is valid at the 17th clock.

Therefore, when setting 1 word (8 bits) of data, input 17 clocks or more to the SPCLK pin.

Ensure that 17 clocks or more are input to the SPclk pin between the rising of SPsyNc and the rising of the next SPsyNc.

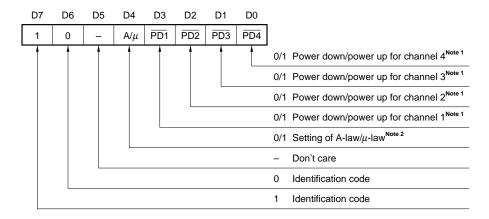

• A/μ-law, power down control

- Notes 1. Default setting is power down mode.

- 2. Default setting is A-law mode.

- Transmit/receive gain setting control (1st word)

#### Transmit/receive gain setting control (2nd word)

# **Table of Gain Setting Codes**

(1/2)

| Setting Item              | Setting                |    |    |    | 1st \ | Nord |      |      |      |    |    |    | 2nd \ | Nord | 1  |    | (1/2) |

|---------------------------|------------------------|----|----|----|-------|------|------|------|------|----|----|----|-------|------|----|----|-------|

| Journal Hom               | Level                  | D7 | D6 | D5 | D4    | D3   | D2   | D1   | D0   | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0    |

| Gain setting for transmit | +7.5 dB                | 0  | 1  | _  | _     | ch1  |      | ch3  |      | 1  | 1  | 0  | 1     | 0    | 0  | 0  | 0     |

|                           | +7.0 dB                | ľ  | ľ  |    |       | 0111 | 0112 | 0110 | 0111 | 1  | 1  | 0  | 1     | 0    | 0  | 0  | 1     |

|                           | +6.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 0    | 0  | 1  | 0     |

|                           | +6.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 0    | 0  | 1  | 1     |

|                           | +5.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 0    | 1  | 0  | 0     |

|                           | +5.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 0    | 1  | 0  | 1     |

|                           | +4.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 0    | 1  | 1  | 0     |

|                           | +4.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 0    | 1  | 1  | 1     |

|                           | +3.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 0  | 0  | 0     |

|                           | +3.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 0  | 0  | 1     |

|                           | +2.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 0  | 1  | 0     |

|                           | +2.0 dB<br>+1.5 dB     |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 0  | 1  | 1     |

|                           |                        |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 1  | 0  | 0     |

|                           | +1.0 dB                | 1  |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 1  | 0  | 1     |

|                           | +0.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 1  | 1  | 0     |

|                           | 0.0 dB <sup>Note</sup> |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 1     | 1    | 1  | 1  | 1     |

|                           | -0.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 0  | 0  | 0     |

|                           | -1.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 0  | 0  | 1     |

|                           | -1.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 0  | 1  | 0     |

|                           | -2.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 0  | 1  | 1     |

|                           | -2.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 1  | 0  | 0     |

|                           | -3.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 1  | 0  | 1     |

|                           | -3.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 1  | 1  | 0     |

|                           | -4.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 0    | 1  | 1  | 1     |

|                           | -4.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 0  | 0  | 0     |

|                           | -5.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 0  | 0  | 1     |

|                           | -5.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 0  | 1  | 0     |

|                           | -6.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 0  | 1  | 1     |

|                           | -6.5 dB                | IB |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 1  | 0  | 0     |

|                           | -7.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 1  | 0  | 1     |

|                           | -7.5 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 1  | 1  | 0     |

|                           | -8.0 dB                |    |    |    |       |      |      |      |      | 1  | 1  | 0  | 0     | 1    | 1  | 1  | 1     |

Note Default setting

(2/2)

| Setting Item             | Setting                |    |    |    | 1st \ | Nord |     |     |     |    |    |    | 2nd \ | Word |    |    |    |

|--------------------------|------------------------|----|----|----|-------|------|-----|-----|-----|----|----|----|-------|------|----|----|----|

|                          | Level                  | D7 | D6 | D5 | D4    | D3   | D2  | D1  | D0  | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

| Gain setting for receive | 0.0 dB <sup>Note</sup> | 0  | 1  | _  | -     | ch1  | ch2 | ch3 | ch4 | 1  | 1  | 1  | 1     | 1    | 1  | 1  | 1  |

|                          | -0.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 1    | 1  | 1  | 0  |

|                          | -1.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 1    | 1  | 0  | 1  |

|                          | -1.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 1    | 1  | 0  | 0  |

|                          | -2.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 1    | 0  | 1  | 1  |

|                          | -2.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 1    | 0  | 1  | 0  |

|                          | -3.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 1    | 0  | 0  | 1  |

|                          | -3.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 1    | 0  | 0  | 0  |

|                          | -4.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 1  | 1  | 1  |

|                          | -4.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 1  | 1  | 0  |

|                          | -5.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 1  | 0  | 1  |

|                          | -5.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 1  | 0  | 0  |

|                          | -6.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 0  | 1  | 1  |

|                          | -6.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 0  | 1  | 0  |

|                          | -7.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 0  | 0  | 1  |

|                          | -7.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 1     | 0    | 0  | 0  | 0  |

|                          | -8.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 1  | 1  | 1  |

|                          | -8.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 1  | 1  | 0  |

|                          | -9.0 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 1  | 0  | 1  |

|                          | -9.5 dB                |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 1  | 0  | 0  |

|                          | -10.0 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 0  | 1  | 1  |

|                          | -10.5 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 0  | 1  | 0  |

|                          | -11.0 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 0  | 0  | 1  |

|                          | -11.5 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 1    | 0  | 0  | 0  |

|                          | -12.0 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 1  | 1  | 1  |

|                          | -12.5 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 1  | 1  | 0  |

|                          | -13.0 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 1  | 0  | 1  |

|                          | -13.5 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 1  | 0  | 0  |

|                          | -14.0 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 0  | 1  | 1  |

|                          | -14.5 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 0  | 1  | 0  |

|                          | -15.0 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 0  | 0  | 1  |

|                          | -15.5 dB               |    |    |    |       |      |     |     |     | 1  | 1  | 1  | 0     | 0    | 0  | 0  | 0  |

Note Default setting

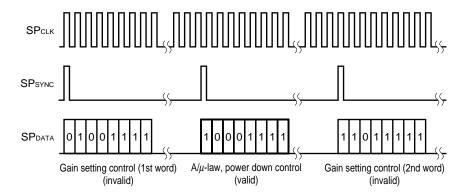

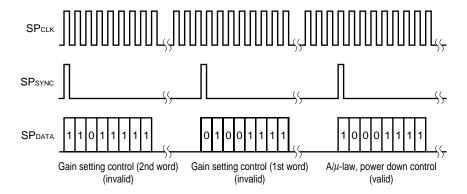

Gain setting control is set by inputting 8-bit data fo the 1st word first and inputting 8-bit data of the 2nd word in synchronization with the next rising edge of SPsync. However, if data other than the identification code of the 2nd word is input after the input of the 1st word, the contents of the 1st word are ignored.

#### (i) When gain setting control is valid

## (ii) When gain setting control is invalid -1

**Remark** Because A/ $\mu$ -law, power down control is input after input of gain setting control (1st word), gain setting control (1st word) becomes invalid and gain setting control (2nd word) also becomes invalid.

#### (iii) When gain setting control is invalid -2

**Remark** Because gain setting control (2nd word) is input before gain setting control (1st word), gain setting control (1st word) becomes invalid. Then, because  $A/\mu$ -law, power down control is input even if gain setting control (1st word) is input, gain setting control (1st word) becomes invalid.

# 4. ELECTRICAL SPECIFICATIONS (PRELIMINARY)

# ABSOLUTE MAXIMUM RATINGS ( $T_A = 25$ °C)

| Item                                  | Symbol             | Condition                                                          | Rating                       | Unit |

|---------------------------------------|--------------------|--------------------------------------------------------------------|------------------------------|------|

| Supply voltage                        | V <sub>DD</sub>    | AVDD1, AVDD2, AVDD3, AVDD4, DVDD                                   | -0.3 to +7.0                 | V    |

| Analog input voltage                  | Vain               | Ain1, Ain2, Ain3, Ain4, ACOMin1,<br>ACOMin2, ACOMin3, ACOMin4      | -0.3 to V <sub>DD</sub> +0.3 |      |

| Digital input voltage                 | VDIN               | DR, DCLR, FSC, LAW, PD1, PD2, PD3, PD4, SPCLK, SPSYNC, SPDATA, RST | -0.3 to V <sub>DD</sub> +0.3 |      |

| Voltage applied to analog output pin  | VAOUT              | Aout1, Aout2, Aout3, Aout4, ACOMout1, ACOMout2, ACOMout3, ACOMout4 | -0.3 to V <sub>DD</sub> +0.3 |      |

| Voltage applied to digital output pin | V <sub>D</sub> OUT | Dx                                                                 | -0.3 to V <sub>DD</sub> +0.3 |      |

| Power dissipation                     | Рт                 |                                                                    | 500                          | mW   |

| Ambient operating temperature         | TA                 |                                                                    | -20 to +85                   | °C   |

| Storage temperature                   | Tstg               |                                                                    | -65 to +150                  |      |

Caution Product quality may suffer if the absolute maximum rating is exceeded for even a single parameter or even momentarily. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions which ensure that the absolute maximum ratings are not exceeded.

RECOMMENDED OPERATION CONDITIONS (TA = -20 to +85 °C, VDD = 5 V  $\pm$  5 %, GND = 0 V, fDCLK = 2048 kHz)

## (1) DC condition

| Item                           | Symbol           | Condition                                                     | MIN.    | TYP. | MAX.                | Unit |

|--------------------------------|------------------|---------------------------------------------------------------|---------|------|---------------------|------|

| Ambient operating temperature  | TA               |                                                               | -20     | +25  | +85                 | °C   |

| Supply voltage                 | V <sub>DD</sub>  | AVDD1, AVDD2, AVDD3, AVDD4, DVDD                              | 4.75    | 5.0  | 5.25                | V    |

| Analog input voltage           | Vai              | Ain1, Ain2, Ain3, Ain4 (ACOM as reference)                    | -1.0    |      | +1.0                |      |

| Analog output load resistance  | RLOAD            | Аоит1, Аоит2, Аоит3, Аоит4                                    | 50      |      |                     | kΩ   |

| Analog output load capacitance | CLOAD            |                                                               |         |      | 50                  | pF   |

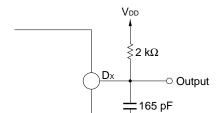

| High level input voltage       | V <sub>IH1</sub> | DR, DCLK, FSC, LAW, PD1, PD2, PD3, PD4, SPCLK, SPSYNC, SPDATA | 2.0     |      | V <sub>DD</sub>     | V    |

|                                | V <sub>IH2</sub> | RST                                                           | 0.8×VDD |      | V <sub>DD</sub>     |      |

| Low level input voltage        | V <sub>IL1</sub> | DR, DCLK, FSC, LAW, PD1, PD2, PD3, PD4, SPCLK, SPSYNC, SPDATA | 0       |      | 0.8                 |      |

|                                | V <sub>IL2</sub> | RST                                                           | 0       |      | 0.2×V <sub>DD</sub> |      |

# (2) AC condition

| Item                                                    | Symbol | Condition         | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------|--------|-------------------|------|------|------|------|

| Data clock frequency                                    | fclk   | (= 1/tcr) ±50 ppm |      | 2048 |      | kHz  |

| Data clock pulse width                                  | tclk   |                   | 200  |      |      | ns   |

| Frame synchronous clock frequency                       | fs     | ±50 ppm           |      | 8.0  |      | kHz  |

| High level frame synchronous pulse width                | twns   |                   | 200  |      |      | ns   |

| Low level frame synchronous pulse width                 | twLs   |                   | 8    |      |      | μs   |

| Clock rise time                                         | tr     |                   |      |      | 50   | ns   |

| Clock fall time                                         | tr     |                   |      |      | 50   | ns   |

| Float in synchronous timing                             | tcsD1  |                   |      |      | 100  | ns   |

|                                                         | tcsD2  |                   | 40   |      |      | ns   |

| Frame synchronous clock and data clock high level width | twnsc  |                   | 100  |      |      | ns   |

| D <sub>R</sub> setup time                               | tosr   | Note              | 65   |      |      | ns   |

| D <sub>R</sub> hold time                                | tohr   | Note              | 120  |      |      | ns   |

| SPDATA clock frequency                                  | fspclk |                   |      |      | 2048 | kHz  |

| SPDATA setup time                                       | tgsr   | Note              | 100  |      |      | ns   |

| SPDATA hold time                                        | tghr   | Note              | 100  |      |      | ns   |

| Float in SP synchronous timing                          | trsp   |                   | 40   |      |      | ns   |

**Note** Set the rise time and fall time of the digital input waveform and clock signal used for measuring timings to 5 ns.

## **DC CHARACTERISTICS**

(Ta = -20 to +85  $^{\circ}$ C, Vdd = 5  $\pm$  0.25 V, GND = 0 V, fdclk = 2048 kHz, and all output pins are unloaded.)

## (1) Power consumption

| Item                       | Symbol | Condition                        | MIN. | TYP. | MAX. | Unit |

|----------------------------|--------|----------------------------------|------|------|------|------|

| Circuit current            | IDD    | All channels in normal operation |      | 23   | 30   | mA   |

| Power-down circuit current | IDDPD  | All channels in power-down mode  |      | 5    | 6    |      |

# (2) Digital interface

| Item                                  | Symbol | Condition                                                                        | MIN.    | TYP. | MAX. | Unit |

|---------------------------------------|--------|----------------------------------------------------------------------------------|---------|------|------|------|

| Digital input current                 | lıd    | $D_R$ , DCLK, FSC, LAW, $\overline{PD1}$ , $\overline{PD2}$ , $\overline{PD3}$ , | -10     |      | +10  | μΑ   |

|                                       |        | PD4, SPCLK, SPSYNC, SPDATA, RST                                                  |         |      |      |      |

|                                       |        | Each pin $0 \le V_{DIN} \le V_{DD}$                                              |         |      |      |      |

| 3-state leakage current               | Iι     | $Dx pin 0 \le V_{DIN} \le V_{DD}$                                                | -10     |      | +10  |      |

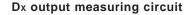

| High level output voltage             | Vон    | Dx pin Iон = $-150 \mu$ A                                                        | VDD-0.3 |      |      | V    |

| Low level output voltage              | Vol    | Dx pin loL = 0.8 mA                                                              |         |      | 0.4  |      |

| Digital output pin output capacitance | Сор    | f = 1 MHz, 0 V other than unmeasured pins                                        |         |      | 15   | pF   |

| Digital input pin input capacitance   | Cid    | f = 1  MHz, 0  V other than unmeasured pins                                      |         |      | 10   |      |

# (3) Transmit amplifier (AIN1, AIN2, AIN3, AIN4 pins)

| Item               | Symbol | Condition | MIN. | TYP. | MAX. | Unit |

|--------------------|--------|-----------|------|------|------|------|

| Input bias current | Ів     |           | -10  |      | +10  | μΑ   |

| Input resistance   | Rin    |           | 1    |      |      | МΩ   |

| Input capacitance  | Cin    |           |      |      | 10   | pF   |

## (4) Receive power amplifier (Aout1, Aout2, Aout3, Aout4 pins)

| Item                   | Symbol | Condition                                     | MIN.  | TYP. | MAX.  | Unit |

|------------------------|--------|-----------------------------------------------|-------|------|-------|------|

| Output offset voltage  | Voa    | D <sub>R</sub> = +0 code<br>ACOM as reference | -50   |      | +50   | mV   |

| Maximum output voltage | Vом    | ACOM as reference                             | -1.02 |      | +1.02 | V    |

| Output resistance      | Rоит   |                                               |       | 1    |       | Ω    |

## (5) Signal reference voltage output (ACOMout1, ACOMout2, ACOMout3, ACOMout4 pins)

| Item           | Symbol | Condition | MIN. | TYP. | MAX. | Unit |

|----------------|--------|-----------|------|------|------|------|

| Output voltage | Vасом  |           | 2.35 | 2.4  | 2.45 | V    |

# AC CHARACTERISTICS (Ta = -20 to +85 $^{\circ}\text{C},~\text{Vdd}$ = 5 $\pm$ 0.25 V, GND = 0 V, fdclk = 2048 kHz)

| Item                   | Symbol            | Condition                    |  | TYP. | MAX. | Unit |

|------------------------|-------------------|------------------------------|--|------|------|------|

| Data enable delay time | t <sub>DZX1</sub> | Dx when FSC is behind DCLK   |  |      | 100  | ns   |

|                        | t <sub>DZX2</sub> | Dx when FSC is ahead of DCLK |  |      | 100  | ns   |

| Data delay time        | todx              | Dx pin                       |  |      | 100  | ns   |

| Data hold time         | tHZX              | Dx pin                       |  | 25   |      | ns   |

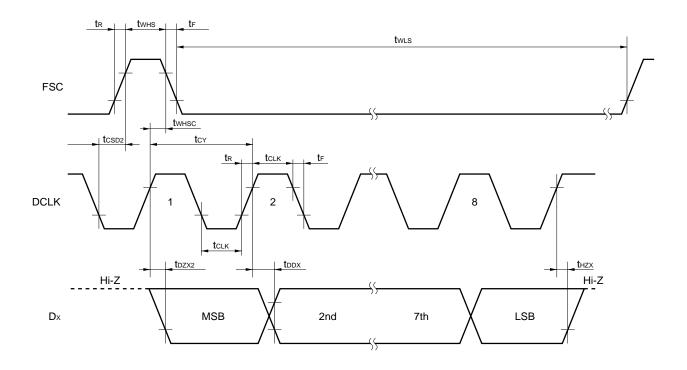

## **TIMING CHARTS**

# (1) Transmit timing

# (a) When FSC is ahead of DCLK

# (b) When FSC is behind DCLK

# (2) Receive timing

# (a) When FSC is ahead of DCLK

# (b) When FSC is behind DCLK

#### (3) Gain setting timing

Remark The relationship between SPsync and SPclk is the same as in the receive timing.

#### (4) Transmit, receive PCM data input/output timing charts

# (5) Setting data input timing

# TRANSMISSION CHARACTERISTICS (Ta = -20 to +85 $^{\circ}$ C, Vdd = 5 $\pm$ 0.25 V, GND = 0 V, fdclk = 2048 kHz)

| Item                                     | Symbol | Condition                  | Setting Value | Unit |

|------------------------------------------|--------|----------------------------|---------------|------|

| Zero transmission level point (transmit) | OTLPx  | Referenced to 600 $\Omega$ | -3.8          | dBm  |

| Zero transmission level point (receive)  | OTLPx  | Referenced to 600 $\Omega$ | -3.8          | dBm  |

| Item                           | Symbol | Condition                         |                 | MIN.  | TYP. | MAX.  | Unit   |

|--------------------------------|--------|-----------------------------------|-----------------|-------|------|-------|--------|

| Insertion loss                 | IL     | A/D input signal<br>0 dBm0 1 kHz  |                 | -0.3  |      | +0.3  | dB     |

|                                |        | D/A input signal<br>0 dBm0 1 kHz  |                 |       |      | +0.3  |        |

| Transmission loss frequency    | FRX    | A/D                               | 60 Hz           | 24.0  |      | _     | dB     |

| characteristics                |        | Reference input signal            | 200 Hz          | 0     |      | 2.0   |        |

|                                |        | 1015 Hz 0 dBm0                    | 300 to 3000 Hz  | -0.15 |      | +0.15 |        |

|                                |        |                                   | 3200 Hz         | -0.15 |      | +0.65 |        |

|                                |        |                                   | 3400 Hz         | 0     |      | 0.8   |        |

|                                |        |                                   | 3780 Hz         | +6.5  |      |       |        |

|                                | FRR    | D/A                               | 0 to 3000 Hz    | -0.15 |      | +0.15 |        |

|                                |        | Reference input signal            | 3200 Hz         | -0.15 |      | +0.65 | 1      |

|                                |        | 1015 Hz 0 dBm0                    | 3400 Hz         | 0     |      | +0.8  |        |

|                                |        |                                   | 3780 Hz         | +6.5  |      |       |        |

| Gain tracking (tone method)    | GTx    | A/D                               | +3 to -40 dBm0  | -0.2  |      | +0.2  | dB     |

|                                |        | Reference input signal            | -50 dBm0        | -0.5  |      | +0.5  |        |

|                                |        | -10 dBm0<br>f = 700 to 1100 Hz    | -55 dBm0        | -1.0  |      | +1.0  |        |

|                                | GTR    | D/A                               | +3 to -40 dBm0  | -0.2  |      | +0.2  |        |

|                                |        | Reference input signal            | -50 dBm0        | -0.5  |      | +0.5  |        |

|                                |        | -10 dBm0<br>f = 700 to 1100 Hz    | -55 dBm0        | -1.0  |      | +1.0  |        |

| Transmit/receive channel       | SDx    | A/D                               | +3 to -30 dBm0  | 36    |      |       | dB     |

| overall power distortion ratio |        | Input signal                      | -40 dBm0        | 30    |      |       |        |

| (tone method)                  |        | f = 700 to 1100 Hz                | -45 dBm0        | 25    |      |       |        |

|                                | SDR    | D/A                               | +3 to -30 dBm0  | 36    |      |       |        |

|                                |        | Input signal                      | -40 dBm0        | 30    |      |       |        |

|                                |        | f = 700 to 1100 Hz                | -45 dBm0        | 25    |      |       |        |

| Absolute delay characteristic  | DA     | A/A<br>Input signal = 0 dBm0      | •               |       |      | 540   | μs     |

| Absolute delay distortion      | Do A/A | 500 Hz                            |                 |       | 1400 | μs    |        |

| frequency characteristics      |        |                                   | 600 Hz          |       |      | 700   |        |

|                                |        |                                   | 1000 to 2600 Hz |       |      | 200   | 1      |

|                                |        |                                   | 2800 Hz         |       |      | 1400  |        |

| Idle channel noise             | ICNADA | A/D A-law Psophometric weig       | ghted           |       |      | -72   | dBm0p  |

|                                | ICNDAA | D/A A-law Psophometric weig       | ghted           |       |      | -80   | 1      |

|                                | ICNADμ | A/D $\mu$ -law C-message weighted |                 |       |      | 18    | dBrnc0 |

|                                | ICNDAμ | D/A μ-law C-message weight        | ed              |       |      | 10    |        |

| Item                         | Symbol | Condition                                                                                                                             | MIN.  | TYP. | MAX.  | Unit |

|------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Cross talk between channels  | СТ     | A/A<br>Input signal = 0 dBm0                                                                                                          |       |      | -70   | dB   |

| Power supply rejection ratio | PSRR   | AV <sub>DD</sub> 1, AV <sub>DD</sub> 2, AV <sub>DD</sub> 3, AV <sub>DD</sub> 4,<br>DV <sub>DD</sub> = 5 V $\pm$ 100 mV <sub>P-P</sub> |       |      | -25   | dB   |

| Coder offset                 |        | A/D<br>Input signal 0 V                                                                                                               | -5    |      | +5    | _    |

| Mutual modulation (2 tones)  | IMD    | A/D Input signal: f1, f2; 300 to 3400 Hz, -4 to -21 dBm0 Measuring signal: 2 × f1 - f2 level (2 × f1 - f2) vs level (f1, f2)          | 44.0  |      |       | dB   |

|                              |        | D/A Input signal: f1, f2; 300 to 3400Hz, -4 to -21 dBm0 Measuring signal: 2 × f1 - f2 level (2 × f1 - f2) vs level (f1, f2)           | 44.0  |      |       | dB   |

| Discrimination               |        | A/D Input signal: f; 4396 to 7796 Hz 0 dBm0 Measuring signal: 8000 - fHz                                                              |       |      | -27   | dB   |

| Out-of-band spurious         |        | D/A Input signal: f; 204 to 3604 Hz 0 dBm0 Measuring signal: 8000 - fHz                                                               |       |      | -27   | dB   |

| In-band spurious             |        | A/D Input signal: f; 700 to 1100 Hz 0 dBm0 Measuring signal: Any frequency                                                            |       |      | -45   | dB   |

|                              |        | D/A Input signal: f; 700 to 1100 Hz 0 dBm0 Measuring signal: Any frequency                                                            |       |      | -45   | dB   |

| Single frequency noise       | Nsf    | D/A Gain setting = 0 dB Measuring signal: f = up to 256 kHz                                                                           |       |      | -54   | dBm0 |

| Transmit gain setting        | ΔDGSx  | A/D difference from reference setting value                                                                                           | -0.15 |      | +0.15 | dB   |

| Receive gain setting         | ΔDGSR  | D/A difference from reference setting value                                                                                           | -0.15 |      | +0.15 |      |

#### 5. APPLICATION CIRCUIT EXAMPLE

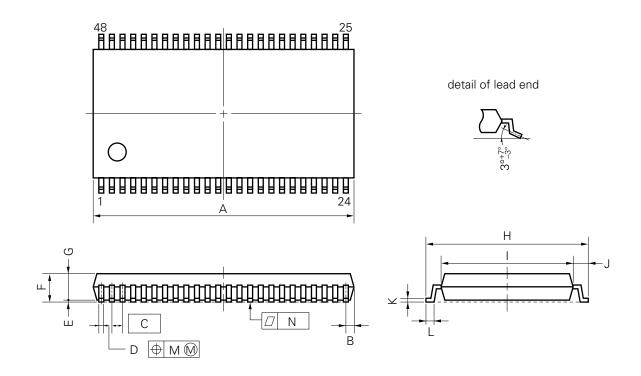

# 6. PACKAGE DRAWINGS

# 48 PIN PLASTIC SHRINK SOP (375 mil)

## NOTE

Each lead centerline is located within 0.10 mm (0.004 inch) of its true position (T.P.) at maximum material condition.

P48GT-65-375B-1

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| А    | 16.21 MAX.             | 0.639 MAX.                |

| В    | 0.63 MAX.              | 0.025 MAX.                |

| С    | 0.65 (T.P.)            | 0.026 (T.P.)              |

| D    | 0.30±0.10              | $0.012^{+0.004}_{-0.005}$ |

| Е    | 0.125±0.075            | 0.005±0.003               |

| F    | 2.0 MAX.               | 0.079 MAX.                |

| G    | 1.7±0.1                | 0.067±0.004               |

| Н    | 10.0±0.3               | 0.394+0.012               |

| I    | 8.0±0.2                | 0.315±0.008               |

| J    | 1.0±0.2                | 0.039+0.009               |

| K    | $0.15^{+0.10}_{-0.05}$ | $0.006^{+0.004}_{-0.002}$ |

| L    | 0.5±0.2                | $0.020^{+0.008}_{-0.009}$ |

| М    | 0.10                   | 0.004                     |

| N    | 0.10                   | 0.004                     |

## 7. RECOMMENDED SOLDERING CONDITIONS

This product should be soldered and mounted under the conditions recommended below.

For details of recommended soldering conditions, refer to the information document **Semiconductor Device Mounting Technology Manual (C10535E)**.

For soldering methods and conditions other than those recommended, please contact your NEC sales representative.

#### SURFACE MOUNT TYPE

$\mu$ PD9611GT: 48-pin shrink SOP (375 mil)

| Soldering Method | Soldering Conditions                                                                                                                                                                                                                                                                                                                                                                                 | Recommended<br>Condition Symbol |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Infrared reflow  | Package peak temperature: 235 °C Duration: 30 sec. max. (210 °C or above) Number of times: 2 max. Time limit: 3 days <sup>Note</sup> (thereafter, 10-hour prebaking at 125 °C required.) <cautions> (1) Wait for the device temperature to return to normal after the first reflow before starting the second reflow. (2) Do not perform flux cleaning with water after the first reflow.</cautions> | IR-35-103-2                     |

| Pin heating      | Pin temperature: 300 °C max.  Duration: 3 sec. max. (per side of device)                                                                                                                                                                                                                                                                                                                             | _                               |

Note For the storage period after unpacking from the dry-pack, storage conditions are max. 25 °C, 65 % RH.

# **NOTES FOR CMOS DEVICES -**

# 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS device behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

## [MEMO]

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5