# Five Channel Programmable DC-DC System Power Manager

### **FEATURES & APPLICATIONS**

- Digital programming of all major parameters via I<sup>2</sup>C interface and non-volatile memory

- o Output voltage set point

- Output power-up/down sequencing

- o Input/Battery voltage monitoring

- o Digital soft-start and output slew rate

- o Output voltage margining

- UV/OV monitoring of all outputs

- o Enable/Disable outputs independently

- · Five output channels

- o Two synchronous step-down (buck) channels

- o One step-up (boost) channel

- o One inverting (buck-boost) channel

- o One fixed output +3.3V LDO

- User friendly Graphical User Interface (GUI)

- +2.7V to +6.0V Input Range

- Highly accurate reference and output voltage (<0.5%) with Active DC Output Control (ADOC™) technology

- Undervoltage Lockout (UVLO) with hysteresis

- 800 kHz operating frequency

- 96 bytes of user configurable nonvolatile memory

### **Applications**

- Digital camcorders/still cameras

- Portable DVD/MP3/GPS

- Camera/smart phones

- TFT Displays/Monitors/TV's

- Mobile Computing/PDA's

- Consumer battery-operated equipment

### INTRODUCTION

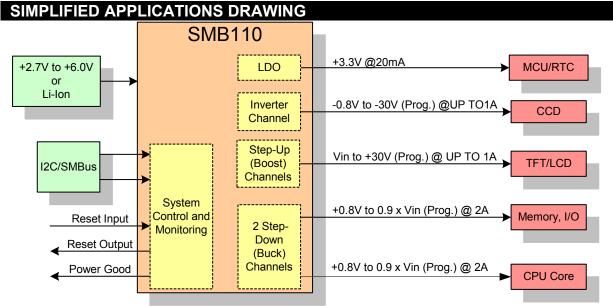

The SMB110 is a highly integrated and flexible five-channel power manager designed for use in a wide range of portable applications. The built-in digital programmability allows system designers to custom tailor the device to suit almost any multichannel power supply application from digital camcorders to mobile phones. Complete with a user friendly GUI, all programmable settings including output voltages and input/output voltage monitoring can be customized with ease.

The SMB110 integrates all the essential blocks required to implement a complete five-channel power subsystem including two synchronous step-down "buck" controllers, one step-up "boost" controller, one inverting "buck-boost" controller and one fixed output +3.3V LDO. Additionally sophisticated power control/monitoring functions required by complex systems are built-in. These include digitally programmable output voltage set point, power-up/down sequencing, enable/disable, margining and UV/OV/input/output monitoring on all channels.

The integration of features and built-in flexibility of the SMB110 allows the system designer to create a "platform solution" that can be easily modified via software without major hardware changes. Combined with the re-programmability of the SMB110 this facilitates rapid design cycles and proliferation from a base design to future generations of product.

The SMB110 is suited to battery-powered applications with an input range of +2.7V to +6.0V. Output voltages are extremely accurate (<0.5%) employing proprietary ADOC<sup>™</sup> technology. Communication is via the industry standard I<sup>2</sup>C bus. All user-programmed settings are stored in non-volatile EEPROM of which 96 bytes may be used for general-purpose memory applications. The operating temperature range is +0C to +70C and the available package is a lead-free, Green, RoHS compliant, 32-pad QFN-32.

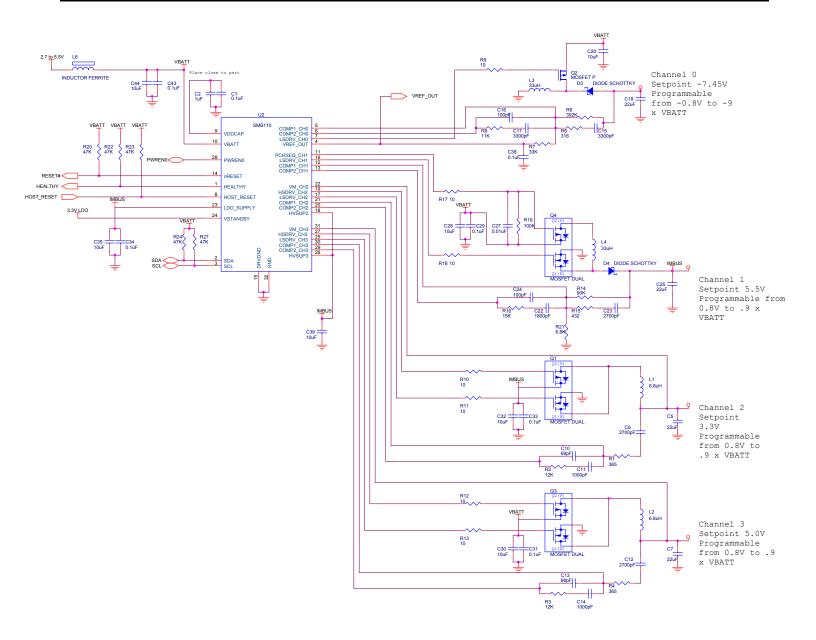

Figure 1 – Applications diagram featuring the SMB110 five-channel, programmable DC-DC controller Note: This is an applications example only. Some pins, components and values are not shown.

# **SMB110**

### Preliminary Information

# **TABLE OF CONTENTS**

| General Description                                            | 3        |

|----------------------------------------------------------------|----------|

| Typical Application                                            |          |

| Internal Block Diagram                                         |          |

| Pin Descriptions                                               | 6-8      |

| Package and Pin Configuration                                  | 9        |

| Absolute Maximum Ratings                                       | 10       |

| Recommended Operating Conditions                               | 10       |

| DC Operating Characteristics                                   | .10-13   |

| AC Operating Characteristics                                   | .14-15   |

| I <sup>2</sup> C 2-Wire Serial Interface AC Operating Characte | ristics- |

| 100khz                                                         | 16       |

| Timing Diagrams: I <sup>2</sup> C                              | 16       |

| Efficiency Graphs                                              | 17       |

| Transient Response                                             |          |

| Timing Diagrams: Power-On Sequence                             | 19       |

| Applications Information: Device Operation                     |          |

| Power Supply                                                   | 20       |

| Enable                                                         |          |

| Power-On Sequencing                                            |          |

| Normal Sequencing                                              | 20       |

| Sequencing With Enable                                         |          |

| Sequencing with channel bypass                                 |          |

| Manual Mode                                                    |          |

| Monitoring                              | 21 |

|-----------------------------------------|----|

| Output Voltage                          | 21 |

| LDO Standby Voltage                     | 22 |

| Soft Start                              | 22 |

| Power-On Sequencing FlowChart           | 23 |

| Minimum Load                            |    |

| Margining                               | 24 |

| Application Schematic                   | 25 |

| Bill of materials                       |    |

| Programming information                 |    |

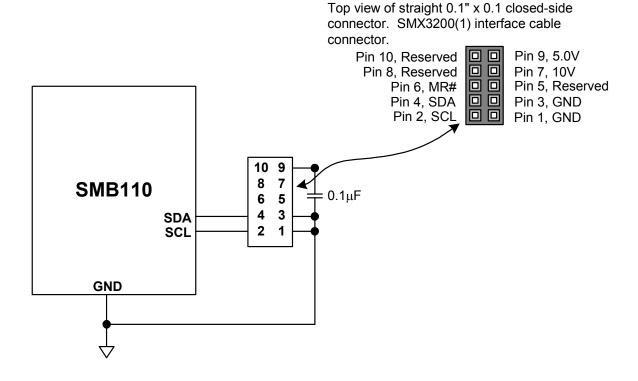

| Development Hardware & Software         | 28 |

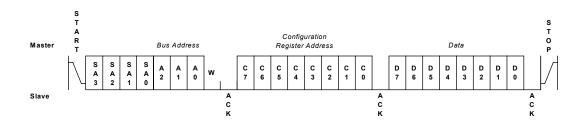

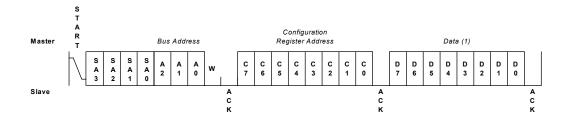

| Serial Interface                        | 29 |

| Write                                   | 29 |

| Read                                    |    |

| Configuration Registers                 | 29 |

| General Purpose Memory                  | 29 |

| GUI                                     |    |

| I <sup>2</sup> C memory read and writes | 31 |

| Default Configuration Register Setting  | 32 |

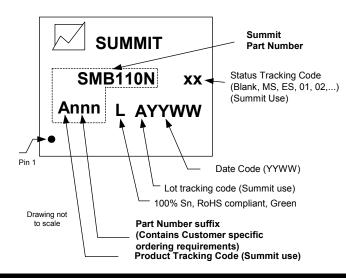

| Part Marking                            |    |

| Package                                 |    |

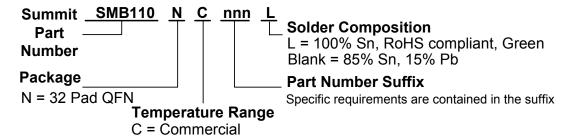

| Ordering Information                    |    |

| Legal Notice                            |    |

### **GENERAL DESCRIPTION**

The SMB110 is a fully programmable DC-DC controller that monitors, margins, and cascade sequences. It has 5 voltage outputs, consisting of: two synchronous "buck" step-down controllers, one "boost" step-up controller, one "boost-buck" negative DC-DC controller, and one LDO.

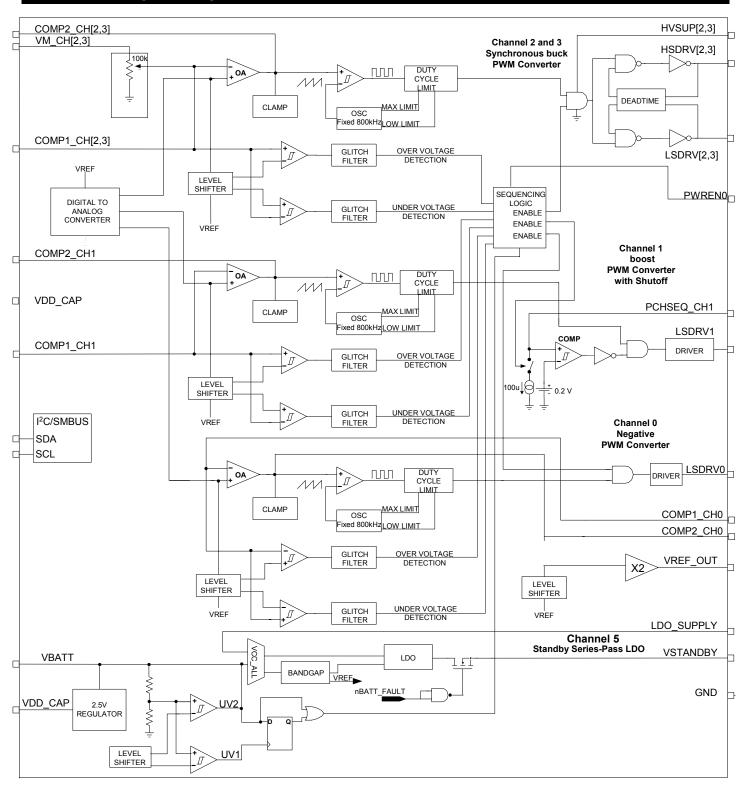

The SMB110 uses a fixed 800 kHz Pulse Width Modulation (PWM) control circuit. A type three voltage mode compensation network is used offering a cost effective solution without compromising the transient response. By utilizing external n and p-type MOSFET transistors the efficiency and load current can be customized to fit a wide array of system requirements.

The SMB110 integrates two buck outputs that are capable of producing an output voltage less than the input voltage. Each buck output voltage is set by an internal resistor divider and a programmable voltage reference. The integrated resistor divider eliminates the cost and space necessary for external components and has several programmable values. Through the programmability of the reference and the resistor divider, practically any output voltage less than the battery can be produced without the need to change external components.

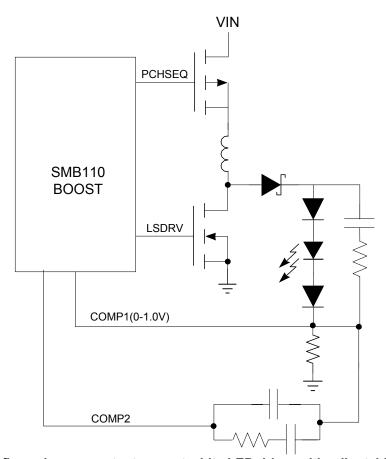

In addition, the SMB110 integrates one boost output capable of producing an output voltage greater than the input voltage. The boost topology is asynchronous, using a rectifying Schottky diode and eliminating the need for an additional external MOSFET driver. An external p-channel sequencing MOSFET's accompanies the boost channel in order to isolate the switching MOSFET from the battery when disabled.

The SMB110 also contains one inverting buck-boost output capable of producing a negative output voltage less than or greater than, the input voltage. The buck boost output is asynchronous and drives an external p-channel MOSFET.

A Low DropOut linear regulator with fixed 3.3 volt output provides a low current supply for "always on" microcontrollers. The LDO has a special input supply that is internally multiplexed between the LDO supply pin and the battery. This ensures that the LDO will always be active over the recommended operating voltages (2.7V-6.0V).

The SMB110 is capable of power-on/off cascade sequencing where each channel can be assigned one of

four unique sequence positions. During sequencing each channel in a given sequence position is guaranteed to reach its programmed output voltage before the channel(s) occupying the next sequence position initiate their respective soft-start sequence. A unique programmable delay exists between each power on/off sequence position. In addition to power on/off sequencing all supplies can be powered on/off individually through an I<sup>2</sup>C command or by assertion of an enable pin.

Each output voltage is monitored for under-voltage and over-voltage (UV/OV) conditions, using a comparator-based circuit where the output voltage is compared against an internal programmable reference. An additional feature of the output voltage monitoring is a programmable glitch filter capable of digitally filtering a transient OV/UV fault condition from a true system error. When a fault is detected for a period in excess of the glitch filter, all supplies may be sequenced down or immediately disabled and one of two output status pins can be asserted. The current system status is always accessible via internal registers containing the status of all four channels.

The SMB110 possesses an Undervoltage Lockout (UVLO) circuit to ensure the SMB110 will not power up until the battery voltage has reached a safe operating voltage. The UVLO function exhibits hysteresis, ensuring that noise or a brown out voltage on the supply rail does not inadvertently lead to a system failure.

The SMB110 provides margining control over all of its output voltages. Through an I<sup>2</sup>C command, all outputs can be margined to any voltage setting within the nominal output voltage rage. Margining creates three pre-programmed settings that each channel can be set to via an I<sup>2</sup>C command. Margining is ideal when used with the boost channel configured as an LED driver where margining provides three brightness settings.

In addition, each output is slew rate limited by soft-start circuitry that is user programmable and requires no external capacitors.

All programmable settings on the SMB110 are stored in non-volatile registers and are easily accessed and modified over an industry standard I<sup>2</sup>C serial bus. For fastest prototype development times Summit offers an evaluation card and a Graphical User Interface (GUI).

# **TYPICAL APPLICATION**

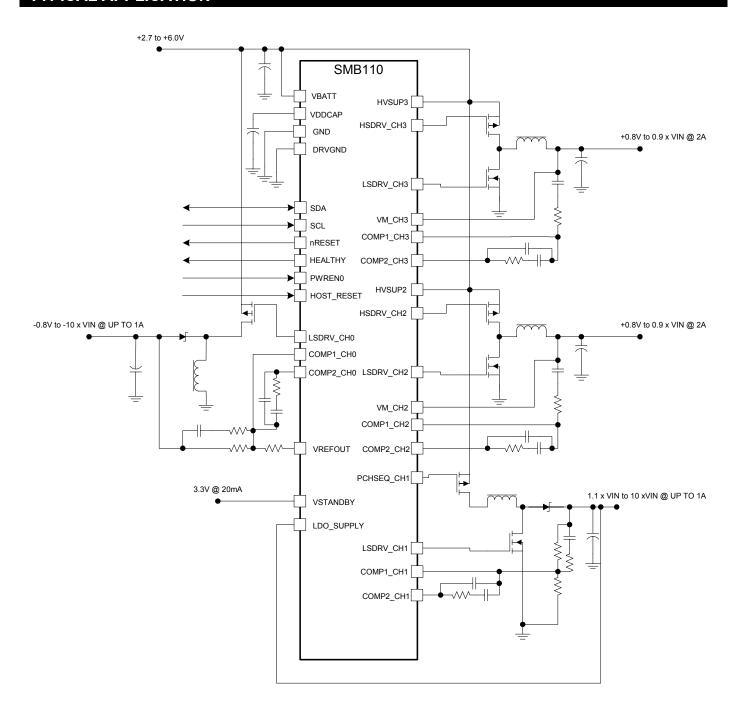

Figure 2 – Typical application schematic showing external circuitry necessary to configure the SMB110 channels as: step-up, step-down, and inverting outputs

### **INTERNAL BLOCK DIAGRAM**

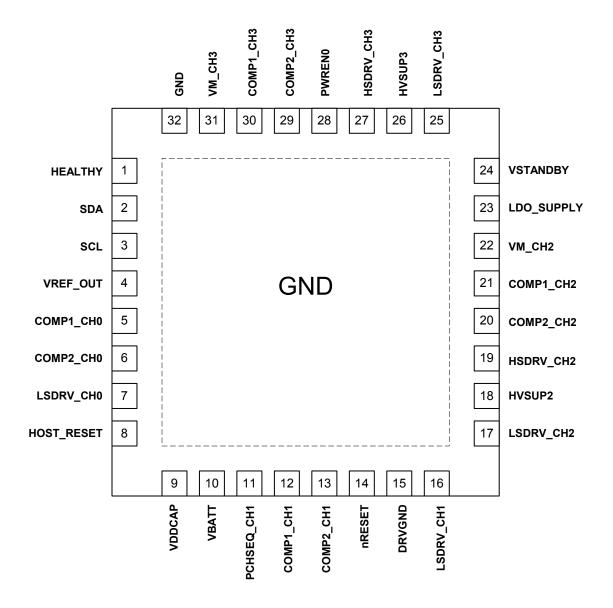

| PIN DESCR  | RIPTIONS |            |                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Pin Type | Pin Name   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                    |

| 1          | OUT      | HEALTHY    | The HEALTHY pin is an open drain output. High when all enabled output supplies are within the programmed levels. HEALTHY will ignore any disabled supply. There is a programmable glitch filter on the under-voltage and over-voltage sensors so that short transients outside of the limits will be ignored by HEALTHY. When used this pin should be pulled high by an external pull-up resistor. |

| 2          | I/O      | SDA        | SDA (Serial Data) is an open drain bi-directional pin used as the I <sup>2</sup> C data line. SDA must be tied high through a pull-up resistor.                                                                                                                                                                                                                                                    |

| 3          | IN       | SCL        | SCL (Serial Clock) is an open drain input pin used as the I <sup>2</sup> C clock line. SCL must be tied high through a pull-up resistor.                                                                                                                                                                                                                                                           |

| 4          | OUT      | VREF_OUT   | The VREF_OUT (Voltage Reference) pin is a precision reference output. When an inverting output is used, this pin acts as a level shifting reference for the feedback circuitry. When the inverting output is not used, this pin may be used as a programmable reference.                                                                                                                           |

| 5          | IN       | COMP1_CH0  | COMP1_CH0 (Channel 0 primary Compensation) pin is the primary feedback input of the inverting controller.                                                                                                                                                                                                                                                                                          |

| 6          | IN       | COMP2_CH0  | COMP2_CH0 (Channel 0 secondary Compensation) pin is the second feedback input of the inverting controller                                                                                                                                                                                                                                                                                          |

| 7          | OUT      | LSDRV_CH0  | The LSDRV_CH0 (Channel 0 Low-side Driver) pin is the switching node of the inverting buck-boost controller. The output of this pin should be attached to the gate of an external p-channel MOSFET driver.                                                                                                                                                                                          |

| 8          | IN       | HOST_RESET | The HOST_RESET pin is an active high reset input. When this pin is asserted high, the nRESET output will immediately go low. When HOST_RESET is brought low, nRESET will go high after a programmed reset delay.                                                                                                                                                                                   |

| 9          | CAP      | VBATT_CAP  | The VBATT_CAP (VBATT Capacitor) pin is an external capacitor input used to filter the internal supply.                                                                                                                                                                                                                                                                                             |

| 10         | PWR      | VBATT      | Power supply to part.                                                                                                                                                                                                                                                                                                                                                                              |

| 11         | OUT      | PCHSEQ_CH1 | The PCHSEQ_CH1 (Channel 1 Sequence) pin is attached to an external p-channel MOSFET and is used to enable the corresponding channel 1 boost controller. PCHSEQ_CH1 uses an internal 100μA current sink for sequencing. This pin should be pulled high through a parallel RC connection.                                                                                                            |

| 12         | IN       | COMP1_CH1  | The COMP1_CH1 (Channel 1 primary Compensation) pin is the primary compensation input of the channel 1 boost controller.                                                                                                                                                                                                                                                                            |

| 13         | IN       | COMP2_CH1  | The COMP2_CH1 (Channel 1 secondary Compensation) pin is the second compensation input of the channel 1 boost controller.                                                                                                                                                                                                                                                                           |

| PIN DESCR  | RIPTIONS |            |                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Pin Type | Pin Name   | Pin Description                                                                                                                                                                                                                                                                                                                                 |

| 14         | OUT      | nRESET     | The nRESET (Reset) pin is an active low open drain output. Active when the SMB110 is powered up. Remains low for a user programmable period of 25, 50, 100, or 200 ms after all enabled supplies have exceeded their programmed thresholds. When used, this pin should be pulled high by an external pull up resistor.                          |

| 15         | PWR      | DRVGND     | DRVGND (Driver Ground). Each DRVGND pin should be attached externally to ground through a short wide wire.                                                                                                                                                                                                                                      |

| 16         | OUT      | LSDRV_CH1  | The LSDRV_CH1 (Channel 1 Low-side Driver) pin is the lower switching node of the synchronous boost controller. This pin attaches to an external n-channel MOSFET                                                                                                                                                                                |

| 17         | OUT      | LSDRV_CH2  | The LSDRV_CH2 (Channel 2 Low-side Driver) pin is the lower switching node of the channel 2 synchronous buck controller. Attaches to the gate of n-channel MOSFET.                                                                                                                                                                               |

| 18         | PWR      | HVSUP2     | Supply for Channel 2 buck driver.                                                                                                                                                                                                                                                                                                               |

| 19         | OUT      | HSDRV_CH2  | The HSDRV_CH2 (Channel 2 High-side Driver) pin is the upper switching node of the channel 2 synchronous buck controller. Attach to the gate of p-channel MOSFET. A delay exists between the assertion of HSDRV_CH2 and assertion of LSDRV_CH2 to prevent excessive current flow during switching.                                               |

| 20         | IN       | COMP2_CH2  | The COMP2_CH2 (Channel 2 secondary Compensation) pin is the secondary compensation input of the channel 2 buck controller.                                                                                                                                                                                                                      |

| 21         | IN       | COMP1_CH2  | The COMP1_CH2 (Channel 2 primary Compensation) pin is the primary compensation input of the channel 2 buck controller. Each pin is internally connected to a programmable resistor divider.                                                                                                                                                     |

| 22         | IN       | VM_CH2     | The VM_CH2 (Channel 2 Voltage Monitor) pin connects the channel 6 controller output. Internally the VM_CH2 pin connects to an internal programmable resistor divider.                                                                                                                                                                           |

| 23         | PWR      | LDO_SUPPLY | The LDO_ SUPPLY pin powers the 3.3V VSTANDBY LDO output. The LDO_ SUPPLY pin should be connected to the output of a boost output (usually the intermediate bus). When the battery voltage drops below the UV1 threshold, this pin will no longer supply the LDO. Do not apply a voltage in excess of the recommended input voltage to this pin. |

| 24         | OUT      | VSTANDBY   | The VSTANDBY (Voltage Standby) pin is a 3.3V LDO output. VSTANDBY is supplied from the output of the intermediate bus through the LDO_SUPP pin. When PWR_FAIL is asserted an internal analog multiplexer will power VSTANDBY directly from the VBATT pin.                                                                                       |

| 25         | OUT      | LSDRV_CH3  | The LSDRV_CH3 (Channel 3 Low-side Driver) pin is the lower switching node of the channel 3 synchronous buck controller. Attaches to the gate of n-channel MOSFET.                                                                                                                                                                               |

| 26         | PWR      | HVSUP3     | Supply for Channel 3 buck driver.                                                                                                                                                                                                                                                                                                               |

| PIN DESCRIPT | ION      |           |                                                                                                                                                                                                                                                                                                   |

|--------------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number   | Pin Type | Pin Name  | Pin Description                                                                                                                                                                                                                                                                                   |

| 27           | OUT      | HSDRV_CH3 | The HSDRV_CH3 (Channel 3 High-side Driver) pin is the upper switching node of the channel 3 synchronous buck controller. Attach to the gate of p-channel MOSFET. A delay exists between the assertion of HSDRV_CH3 and assertion of LSDRV_CH3 to prevent excessive current flow during switching. |

| 28           | IN       | PWREN0    | The PWREN0 (Power Enable 0) pin is a programmable input used to enable (disable) selected supplies. When unused this pin should be tied to a solid logic level.                                                                                                                                   |

| 29           | IN       | COMP2_CH3 | The COMP2_CH3 (Channel 3 secondary Compensation) pin is the secondary compensation input of the channel 3 buck controller.                                                                                                                                                                        |

| 30           | IN       | COMP1_CH3 | The COMP1_CH3 (Channel 3 primary Compensation) pin is the primary compensation input of the channel 3 buck controller. Each pin is internally connected to a programmable resistor divider.                                                                                                       |

| 31           | IN       | VM_CH3    | The VM_CH3 (Channel 3 Voltage Monitor) pin connects the channel 3 controller output. Internally the VM_CH3 pin connects to an internal programmable resistor divider.                                                                                                                             |

| 32           | PWR      | GND       | The GND pin should be connected to the common ground plane through a short fat wire.                                                                                                                                                                                                              |

| PAD          | PWR      | GND       | The exposed metal pad should be attached to ground.                                                                                                                                                                                                                                               |

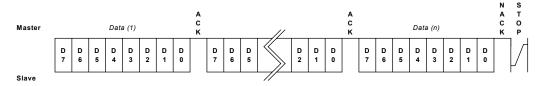

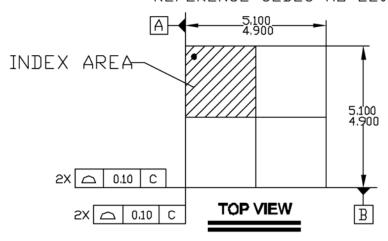

# **PACKAGE AND PIN DESCRIPTION**

Top view SMB110 5mm x 5mm QFN-32

### **ABSOLUTE MAXIMUM RATINGS**

| Temperature Under Bias               | -55°C to +125°C |

|--------------------------------------|-----------------|

| Storage Temperature                  | -65°C to +150°C |

| Terminal Voltage with Respect to     |                 |

| VBATT Supply Voltage                 | 0.3V to +6.5V   |

| HVSUP Supply Voltage                 | 0.3V to +6.5V   |

| LDO_SUPPLY                           | 0.3V to +6.5V   |

| All Others                           | 0.3V to VBATT   |

| Output Short Circuit Current         | 100mA           |

| Reflow Solder Temperature (30 secs). | 260°C           |

| Junction Temperature                 | 150°C           |

| ESD Rating per JEDEC                 | 2000V           |

| Latch-Up testing per JEDEC           | ±100mA          |

### RECOMMENDED OPERATING CONDITIONS

| 0°C to +70°C     |

|------------------|

| 2.7V to +6.0V    |

| 2.7V to +6.0V    |

| GND to +6.0V     |

| GND to VBATT     |

|                  |

| TBD              |

| ) per J-STD- 020 |

|                  |

| 100 Years        |

| 100,000 Cycle    |

| 0°C to +70°C     |

|                  |

Note - The device is not guaranteed to function outside its operating rating. Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions outside those listed in the operational sections of the specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability. Devices are ESD sensitive. Handling precautions are recommended.

|                         | TING CHARACTERISTICS commended operating conditions, u | nless otherwise noted. All volt                                                                   | ages are | relative | e to GND | ).)  |

|-------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------|----------|----------|------|

| Symbol                  | Parameter                                              | Conditions                                                                                        | Min      | Тур      | Max      | Unit |

| VBATT                   | Input supply voltage                                   | Input supply voltage (operational)                                                                | 2.7      |          | 6.0      | V    |

| V <sub>LDO_SUPP</sub>   | Linear regulator supply voltage                        | Internally multiplexed with VBATT                                                                 | 2.7      |          | 6.0      | V    |

| V <sub>HVSUP</sub>      | Buck driver supply voltage                             | Gate drive voltage                                                                                | 2.7      |          | 6.0      | V    |

| V <sub>UVLO</sub>       | Lindervoltage lockout                                  | VBATT rising                                                                                      |          | 2.2      |          | V    |

| VUVLO                   | Undervoltage lockout                                   | VBATT falling                                                                                     |          | 2.0      |          | v    |

| I <sub>DD-MONITOR</sub> | Monitoring current                                     | All voltage inputs monitored. No supplies switching, VBATT at 4.2V, LDO on with no output enabled |          |          | 330      | μA   |

| I <sub>SD</sub>         | Switching current for one output enabled               | Current drawn when one output enabled                                                             |          | 1.2      |          | mA   |

| I <sub>DD-</sub>        | Total current all channels switching. <sup>1</sup>     | VBATT at 4.2V, LDO on with no load                                                                |          |          | 2.2      | mA   |

| $V_{REF(INT)}$          | Internal voltage reference                             |                                                                                                   | 0.995    |          | 1.005    | V    |

| Oscillator              |                                                        |                                                                                                   | •        | ·        |          | ·    |

| f <sub>OSC</sub>        | Oscillator frequency                                   |                                                                                                   |          | 800      |          | kHz  |

| $\Delta f_{OSC}$        | Oscillator frequency accuracy                          |                                                                                                   | -10      |          | +10      | %    |

| O <sub>PP</sub>         | Oscillator peak to peak <sup>2</sup> voltage           |                                                                                                   |          | 1        |          | V    |

| $\Delta f_{SV}$         | Frequency stability for voltage                        |                                                                                                   |          | 0.1      |          | %/V  |

| $\Delta f_{ST}$         | Frequency stability for temperature                    |                                                                                                   |          | 0.04     |          | %/°C |

| •                         | mmended operating conditions, unle   |                                                     | B.C  |      | NA   | 1114 |

|---------------------------|--------------------------------------|-----------------------------------------------------|------|------|------|------|

| Symbol                    | Parameter                            | Conditions                                          | Min  | Тур  | Max  | Unit |

| Error Amp                 | lifier                               |                                                     |      |      |      |      |

| $V_{ACC}$                 | Threshold Voltage accuracy           |                                                     |      | 0.2  |      | %    |

| TS                        | Temperature stability                |                                                     |      | 0.2  |      | %    |

| A <sub>VOL</sub>          | Open loop voltage Gain               | At DC                                               |      | 60   |      | dB   |

| BW                        | Frequency bandwidth                  | At AV=0 dB                                          |      | 30   |      | MHz  |

| I <sub>SOURCE</sub>       | Output source current                | At 0.5V                                             |      | 20   |      | μΑ   |

| I <sub>SINK</sub>         | Output sink current                  | At 0.5V                                             |      | 800  |      | μΑ   |

| LDO                       | •                                    |                                                     |      |      |      |      |

| V <sub>OUT</sub>          | Nominal output voltage               | LDO_SUPPLY = 4.2V,<br>I <sub>LOAD</sub> =0A         |      | 3.3  |      | V    |

| $\Delta V_{OUT}$          | Output voltage accuracy              | Percent of 3.3V output @<br>10mA, LDO_SUPPLY = 4.2V |      | 0.3  |      | %    |

| $\Delta V_{LOAD}$         | Load regulation error                |                                                     |      | 0.3  |      | %/V  |

| $\Delta V_{LINE}$         | Line regulation error                | No load                                             |      | 0.17 |      | %/mA |

| PSRR                      | Power supply rejection ratio         | 20log(Vout/Vin) @ 10kHz                             |      | 50   |      | dB   |

| IQ                        | Quiescent current                    | VBATT = 4.2V, I <sub>LOAD</sub> =0A                 |      | 50   |      | μΑ   |

|                           |                                      | I <sub>OUT</sub> = 1 mA                             |      | 20   |      |      |

|                           |                                      | I <sub>OUT</sub> = 5 mA                             |      | 100  |      |      |

| $V_{DO}$                  | Dropout voltage                      | I <sub>OUT</sub> = 10 mA                            |      | 200  |      | mV   |

|                           |                                      | I <sub>OUT</sub> = 15 mA                            |      | 300  |      |      |

|                           |                                      | I <sub>OUT</sub> = 20 mA                            |      | 400  |      |      |

| I <sub>LIMIT</sub>        | Maximum output current               |                                                     |      |      | 40   | mA   |

| $V_N$                     | Output Noise voltage                 | Peak to peak                                        |      | 1    |      | mV   |

| Inverting C               | Output Block Channel 0               |                                                     |      |      |      |      |

| V <sub>OUT</sub>          | Programmable voltage set point range | VBATT=4.2V, I <sub>LOAD</sub> =0                    | -35  |      | -0.5 | V    |

| $\Delta V_{OUT}$          | Output accuracy                      | Excluding external resistor divider accuracy        |      | 0.5  |      | %    |

| V <sub>COMP1</sub>        | Feedback voltage reference           | COMP1 pin                                           |      | 1.0  |      | V    |

| $\Delta V_{\text{COMP1}}$ | Feedback voltage reference accuracy  | COMP1 pin                                           | -0.2 |      | +0.2 | %    |

| R <sub>ON</sub>           | LSDRV Output ON resistance           | R <sub>OH</sub>                                     |      | 17   |      | Ω    |

| - *UN                     |                                      | R <sub>OL</sub>                                     |      | 3    |      |      |

| D.C.                      | LSDRV Duty Cycle                     | High                                                | 85   |      | 95   | %    |

|                           | Lobitt Daty Syste                    | Low                                                 | 5    |      | 15   | /0   |

| V <sub>REF_OUT</sub>      | Level shift voltage reference        | VREF_OUT pin programmable in 8mV steps              | 1    |      | 2    | V    |

| •                                     | commended operating conditions, unl  | 0                                                                             | B4*  | _    |      | 11!4 |

|---------------------------------------|--------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| Symbol                                | Parameter                            | Conditions                                                                    | Min  | Тур  | Max  | Unit |

| Inverting Out                         | put Block Channel 0 (Continued)      |                                                                               | T    |      | T    | 1    |

| I <sub>REF_OUT</sub>                  | VREF_OUT source current              | VREF_OUT = 1.5V                                                               |      |      | 100  | μA   |

| ML                                    | Minimum load <sup>3</sup>            | L=33uF, V <sub>O</sub> =-7.5V,<br>V <sub>IN</sub> =4.2V, V <sub>D</sub> =0.3V |      | 10.1 |      | kΩ   |

| <b>Boost Output</b>                   | Block Channel 1                      |                                                                               |      |      |      |      |

| V <sub>OUT</sub>                      | Programmable voltage set point range | VBATT=4.2V, I <sub>LOAD</sub> =0                                              | 4.5  |      | 35   | V    |

| $\Delta V_{OUT}$                      | Output accuracy                      | Excluding external resistor divider accuracy                                  |      | 0.5  |      | %    |

| В                                     | HSDRV ON resistance                  | Output high                                                                   |      | 17   |      | Ω    |

| $R_{DRVH}$                            | HSDRV ON TESISIATICE                 | Output low                                                                    |      | 3    |      | 12   |

| D.C.                                  | Duty Cycle                           | High                                                                          | 85   |      | 95   | %    |

| D.C.                                  | Duty Cycle                           | Low                                                                           | 5    |      | 15   | 1 %  |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Foodbook valtage reference           | COMP1 pin                                                                     |      |      |      | V    |

| $V_{COMP1}$                           | Feedback voltage reference           | Programmable in 4mV steps                                                     |      | 1.0  |      | V    |

| $\Delta V_{\text{COMP1}}$             | Feedback voltage reference accuracy  | COMP1 pin                                                                     | -0.5 |      | +0.5 | %    |

| ML                                    | Minimum load <sup>4</sup>            | L=33uF, V <sub>O</sub> =12V, V <sub>IN</sub> =4.2V, V <sub>D</sub> =0.3V      |      | 29   |      | kΩ   |

| I <sub>PCHSEQ</sub>                   | PCHSEQ sink current                  |                                                                               | 50   |      | 100  | μΑ   |

| EN <sub>TH</sub>                      | Enable threshold                     | Voltage on PCHSEQ pin when LSDRV output is enabled                            |      | 200  |      | mV   |

| <b>Buck Output</b>                    | Block Channels 2 and 3               |                                                                               | I.   |      | I.   | I    |

| V                                     | Valtage naminal set neigt range      | VBATT = 4.2V, I <sub>LOAD</sub> = 0                                           | 0.5  |      | 3.8  | V    |

| $V_{OUT}$                             | Voltage nominal set point range      | VBATT = 6.0V, I <sub>LOAD</sub> = 0                                           | 0.6  |      | 5.4  | V    |

| $\Delta V_{OUT}$                      | Output accuracy                      | Including internal resistor divider                                           |      | 0.5  |      | %    |

| В                                     | HSDRV ON resistance                  | Output high                                                                   |      | 8    |      | Ω    |

| $R_{DRVH}$                            | HSDRV ON TESISIATICE                 | Output low                                                                    |      | 8    |      | 12   |

| D                                     | LODDY ON resistance                  | Output high                                                                   |      | 17   |      |      |

| $R_{DRVL}$                            | LSDRV ON resistance                  | Output low                                                                    |      | 3    |      |      |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Facility of the second second        | COMP1 pin                                                                     |      |      |      | .,   |

| $V_{COMP1}$                           | Feedback voltage reference           | Programmable in 4mV steps                                                     |      | 1.0  |      | V    |

| $\Delta V_{\text{COMP1}}$             | Feedback voltage reference accuracy  | COMP1 pin                                                                     | -0.5 |      | +0.5 | mV   |

| D.0                                   | D. t. O. d.                          | High                                                                          | 85   |      | 95   | 01   |

| D.C.                                  | Duty Cycle                           | Low                                                                           | 5    |      | 15   | %    |

| Cumbel                               | Parameter                             | s, unless otherwise noted.  Conditions                                                 | N#:  | T           | Mass | Unit |

|--------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------|------|-------------|------|------|

| Symbol                               |                                       | Conditions                                                                             | Min  | Тур         | Max  | Unit |

| Miscellaneou                         |                                       | T                                                                                      |      | T           |      |      |

| V <sub>IH</sub>                      | Input high voltage                    |                                                                                        |      | 0.9xVDD_CAP |      | V    |

| V <sub>IL</sub>                      | Input low voltage                     |                                                                                        |      | 0.1xVDD_CAP |      | V    |

| V <sub>OL</sub>                      | Open drain outputs                    | I <sub>SINK</sub> = 1mA                                                                | 0    |             | 0.4  | V    |

| l <sub>OL</sub>                      | Output low current                    |                                                                                        | 0    |             | 1.0  | mA   |

| Programmab                           | le Monitoring Thresholds              | 15 11 1877                                                                             |      | T           |      | 1    |

| V <sub>PUV1</sub>                    | Programmable UV1 threshold            | Programmable UV1<br>threshold voltage<br>measured on VBATT pin<br>in 150 mV increments | 2.55 |             | 3.60 | V    |

| $\Delta V_{\text{PUV1}}$             | UV1 accuracy                          |                                                                                        | -20  |             | +20  | mV   |

| $V_{\text{PUV2}}$                    | Programmable UV2 threshold            | Programmable UV2<br>threshold voltage<br>measured on VBATT pin<br>in 150 mV increments | 2.55 |             | 3.60 | V    |

| $\Delta V_{PUV2}$                    | UV2 accuracy                          |                                                                                        | -20  |             | +20  | mV   |

|                                      |                                       | For channels 1-3.                                                                      |      | -5          |      | 0/   |

| Programmable under voltage threshold | Programmable under                    |                                                                                        |      | -10         |      |      |

|                                      | Relative to nominal set point voltage |                                                                                        | -15  |             | - %  |      |

|                                      |                                       | panne vannage                                                                          |      | -20         |      |      |

|                                      |                                       | For channels 1-3. Relative to nominal set point voltage                                |      | +5          |      |      |

| D                                    | Programmable over voltage             |                                                                                        |      | +10         |      | %    |

| P <sub>OVTH</sub>                    | threshold                             |                                                                                        |      | +15         |      | 70   |

|                                      |                                       |                                                                                        |      | +20         |      | -    |

|                                      |                                       |                                                                                        |      | -6.2        |      |      |

|                                      | Programmable under                    | For channel 0. V <sub>o</sub> =-7.5V,                                                  |      | -12.4       |      | 0,   |

| $P_{UVTH}$                           | voltage threshold <sup>5</sup>        | R1=392K, R2=33.2K                                                                      |      | -18.6       |      | - %  |

|                                      |                                       |                                                                                        |      | -24.8       |      |      |

|                                      |                                       |                                                                                        |      | +6.2        |      |      |

|                                      | Programmable over voltage             | For channel 0. V <sub>o</sub> =-7.5V,                                                  |      | +12.4       |      |      |

| P <sub>OVTH</sub>                    | threshold <sup>6</sup>                | R1=392K, R2=33.2K                                                                      |      | +18.6       |      | %    |

|                                      |                                       |                                                                                        |      | +24.8       |      | 1    |

| Symbol             | Parameter                                      | ions, unless otherwise noted. All voltages Conditions                                                                                                 | Min  | Тур  | Max  | Unit  |

|--------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Зуппоот            | 1 drameter                                     | Conditions                                                                                                                                            |      |      |      | Oiiit |

|                    |                                                | Programmable power-On sequence position to sequence position delay.                                                                                   | 1.3  | 1.5  | 1.7  | ms    |

| t <sub>PPTO</sub>  | Programmable power-On sequence timeout period. |                                                                                                                                                       | 10.6 | 12.5 | 14.4 |       |

|                    | sequence unredut period.                       |                                                                                                                                                       | 21.3 | 25   | 28.8 |       |

|                    |                                                |                                                                                                                                                       | 42.5 | 50   | 57.5 |       |

|                    |                                                |                                                                                                                                                       | 1.3  | 1.5  | 1.7  |       |

| t <sub>DPOFF</sub> | Programmable power-off                         | Programmable power-off sequence                                                                                                                       | 10.6 | 12.5 | 14.4 | ms    |

| DPOPP              | sequence timeout period.                       | position to sequence position delay.                                                                                                                  | 21.3 | 25   | 28.8 | 1115  |

|                    |                                                |                                                                                                                                                       | 42.5 | 50   | 57.5 |       |

|                    | Programmable reset                             | Programmable time following assertion of last supply before nRESET pin is released                                                                    | 21.3 | 25   | 28.8 | ms    |

|                    |                                                |                                                                                                                                                       | 42.5 | 50   | 57.5 |       |

| t <sub>PRTO</sub>  | time-out delay                                 | high.                                                                                                                                                 | 85   | 100  | 115  |       |

|                    |                                                |                                                                                                                                                       | 170  | 200  | 230  |       |

|                    |                                                | Time between active enable in which corresponding outputs must exceed there programmed under voltage threshold. If exceeded, a force shutdown will be |      | OFF  |      | - ms  |

|                    | Programmable sequence                          |                                                                                                                                                       | 42.5 | 50   | 57.5 |       |

| t <sub>PST</sub>   | termination period                             |                                                                                                                                                       | 85   | 100  | 115  |       |

|                    |                                                | initiated.                                                                                                                                            | 170  | 200  | 230  |       |

|                    |                                                | Period for which fault must persist before                                                                                                            |      | 0    |      |       |

| t <sub>PGF</sub>   | Programmable glitch filter                     | fault triggered actions are taken. Present on all buck, boost, and inverting supplies.                                                                | 6.8  | 8    | 9.2  | μS    |

|                    |                                                |                                                                                                                                                       | 340  | 400  | 460  |       |

|                    |                                                |                                                                                                                                                       | 170  | 200  | 230  |       |

|                    |                                                |                                                                                                                                                       | 85   | 100  | 115  |       |

|                    | Programmable slew rate                         | Adjustable slew rate factor proportional to                                                                                                           | 56.7 | 66.7 | 76.7 |       |

| $SR_{REF}$         | reference                                      | output slew rate.                                                                                                                                     | 42.5 | 50   | 57.5 | V/s   |

|                    |                                                |                                                                                                                                                       | 28.3 | 33.3 | 38.3 |       |

|                    |                                                |                                                                                                                                                       | 21.3 | 25   | 28.8 |       |

|                    |                                                |                                                                                                                                                       | 17.0 | 20   | 23   |       |

**SMB110**

Preliminary Information

| Symbol          | Parameter                  | Conditions                           | Min | Тур | Max | Unit |

|-----------------|----------------------------|--------------------------------------|-----|-----|-----|------|

| Inverting (     | Output Block Channel 0     |                                      |     |     |     |      |

| t <sub>RH</sub> | HS Driver output rise time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 10  |     | ns   |

| t <sub>FH</sub> | HS Driver output fall time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 10  |     | ns   |

| Boost Out       | put Block Channel 1        |                                      |     |     |     |      |

| $t_{RL}$        | LS Driver output rise time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 10  |     | ns   |

| t <sub>FL</sub> | LS Driver output fall time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 10  |     | ns   |

| Buck Out        | out Block Channels 2 and 3 |                                      |     |     |     |      |

| $t_{RL}$        | LS Driver output rise time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 10  |     | ns   |

| t <sub>FL</sub> | LS Driver output fall time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 10  |     | ns   |

| t <sub>RH</sub> | HS Driver output rise time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 15  |     | ns   |

| t <sub>FH</sub> | HS Driver output fall time | C <sub>G</sub> =100pF, VBATT=4.2V    |     | 5   |     | ns   |

| t <sub>DT</sub> | Driver pen everlan delay   | High to low transition on HSDRV      |     |     | 20  |      |

|                 | Driver non-overlap delay   | Low to high transition on buck HSDRV |     |     | 10  | ns   |

<sup>1.</sup> The total current drawn when all supplies are switching will not equal the sum of the buck, boost, and inverting buck-boost channels current consumption when switching independently. This is due to current overhead to commence sequencing.

3. The minimum load for the Inverting Boost-Buck channel is defined by the following equation: where  $V_0$  = Programmed output voltage, VIN =P-Channel MOSFET source voltage, L = inductance, Vd = forward diode drop (0.6V silicon, 0.3V Schottky). Lesser values may exist

Rmax =

$$\frac{2*L*Vout*(Vout-Vd)}{VIN^{2*}1.25E-8}$$

4. The minimum load for Boost channels is defined by the following equation: where  $V_0$  = Programmed output voltage, VIN =P-Channel MOSFET source voltage, L = inductance, and Vd = forward diode drop (0.6V silicon, 0.3V Schottky. Lesser values may exist

$$Rmax = \frac{2*L*Vout*(Vout - VIN + Vd)}{VIN^2*1.25E-8}$$

5. The Channel 0 programmable under voltage setting is calculated from the following formula: where VREF\_OUT is the voltage o the VREF\_OUT pin and R1 and R2 are the upper and lower resistors in the external voltage divider, n corresponds to the available user programmable settings

Ch 0 P<sub>UVTH</sub> = -100n

$$\left[1 - \left[\frac{V_{REF\_OUT} - .95(1 + R2/R1)}{V_{REF\_OUT} - (1 + R2/R1)}\right]\right]$$

% n= 1,2,3,4

6. The Channel 0 programmable over voltage setting is calculated from the following formula: where VREF\_OUT is the voltage o the VREF\_OUT pin and R1 and R2 are the upper and lower resistors in the external voltage divider, n corresponds to the available user programmable settings

Ch 0 P<sub>OVTH</sub> = 100n

$$\left[1 - \left[\frac{V_{REF\_OUT} - .95(1 + R2/R1)}{V_{REF\_OUT} - (1 + R2/R1)}\right]\right]$$

% n= 1,2,3,4

<sup>2.</sup> Guaranteed by design.

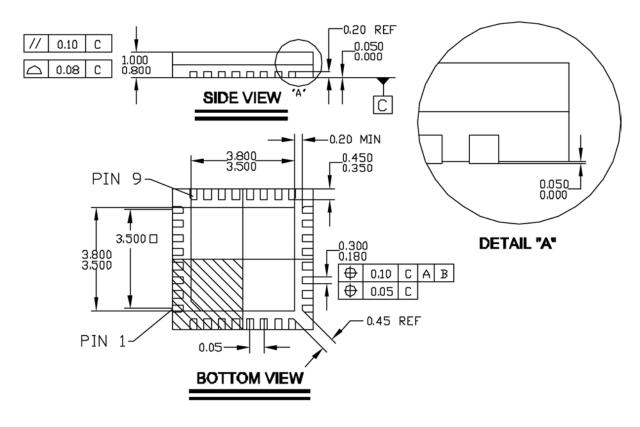

| Symbol              | Description                                             | ons, unless otherwise noted. All volt | 100kHz |     |      | <del>'</del> |

|---------------------|---------------------------------------------------------|---------------------------------------|--------|-----|------|--------------|

|                     |                                                         | Conditions                            | Min    | Тур | Max  | Units        |

| f <sub>SCL</sub>    | SCL clock frequency                                     |                                       | 0      |     | 100  | kHz          |

| $T_LOW$             | Clock low period                                        |                                       | 4.7    |     |      | μS           |

| T <sub>HIGH</sub>   | Clock high period                                       |                                       | 4.0    |     |      | μS           |

| t <sub>BUF</sub>    | Bus free time                                           | Before new transmission - Note 1/     | 4.7    |     |      | μS           |

| t <sub>SU:STA</sub> | Start condition setup time                              |                                       | 4.7    |     |      | μS           |

| t <sub>HD:STA</sub> | Start condition hold time                               |                                       | 4.0    |     |      | μS           |

| t <sub>SU:STO</sub> | Stop condition setup time                               |                                       | 4.7    |     |      | μS           |

| t <sub>AA</sub>     | Clock edge to data valid                                | SCL low to valid SDA (cycle n)        | 0.2    |     | 3.5  | μS           |

| $t_{DH}$            | Data output hold time SCL low (cycle n+1) to SDA change |                                       | 0.2    |     |      | μS           |

| t <sub>R</sub>      | SCL and SDA rise time                                   | Note <u>1</u> /                       |        |     | 1000 | ns           |

| t <sub>F</sub>      | SCL and SDA fall time                                   | Note <u>1</u> /                       |        |     | 300  | ns           |

| t <sub>SU:DAT</sub> | Data in setup time                                      |                                       | 250    |     |      | ns           |

| t <sub>HD:DAT</sub> | Data in hold time                                       |                                       | 0      |     |      | ns           |

| TI                  | Noise filter SCL and SDA                                | Noise suppression                     |        | 100 |      | ns           |

| WR_CONFIG           | Write cycle time config                                 | Configuration registers               |        |     | 10   | ms           |

| t <sub>WR_EE</sub>  | Write cycle time EE                                     | Memory array                          |        |     | 5    | ms           |

Note: 1/ - Guaranteed by Design.

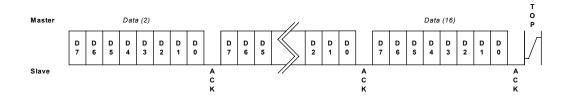

# **TIMING DIAGRAMS**

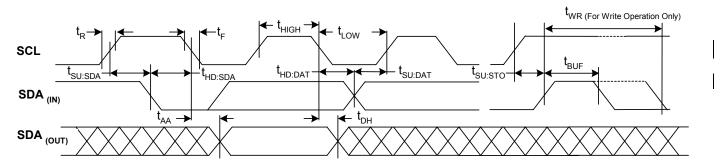

Figure 4 – I<sup>2</sup>C timing diagram

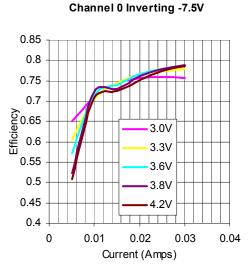

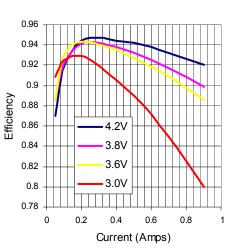

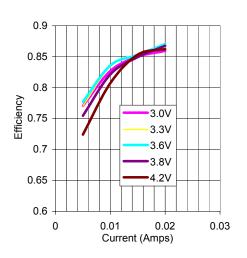

# **EFFICIENCY GRAPHS**

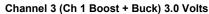

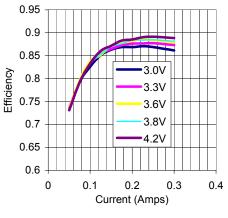

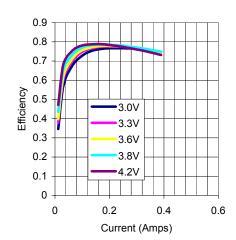

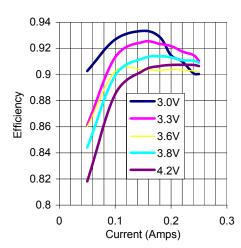

Channel 1 Boost 6.0V

Channel 1 Boost 12V

Channel 3 (Ch 1 Boost + Buck) 5.0 Volts

Channel 2 Buck 1.2V

0.85 8.0 Efficiency 3.0V 3.3V 3.6V 0.7 3.8V 4.2V 0.65 0.6 0.01 0.11 0.21 0.31 Current (Amps)

Channel 2 Buck 2.5 Volts

(All measurements are taken at 25°C, and are based on the Applications Schematic.)

0.9

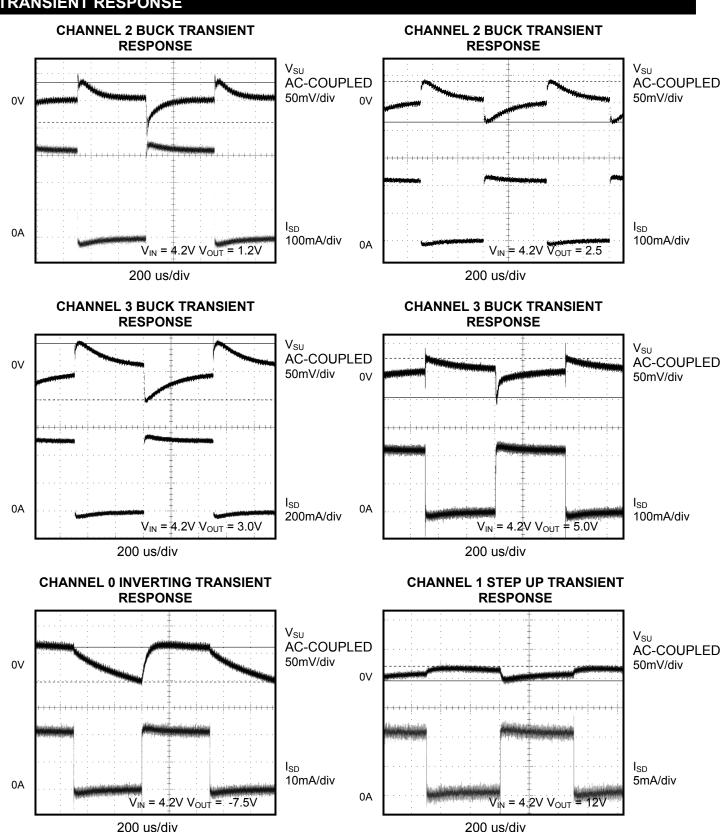

### TRANSIENT RESPONSE

(All measurements are taken at 25°C, and are based on the Applications Schematic.)

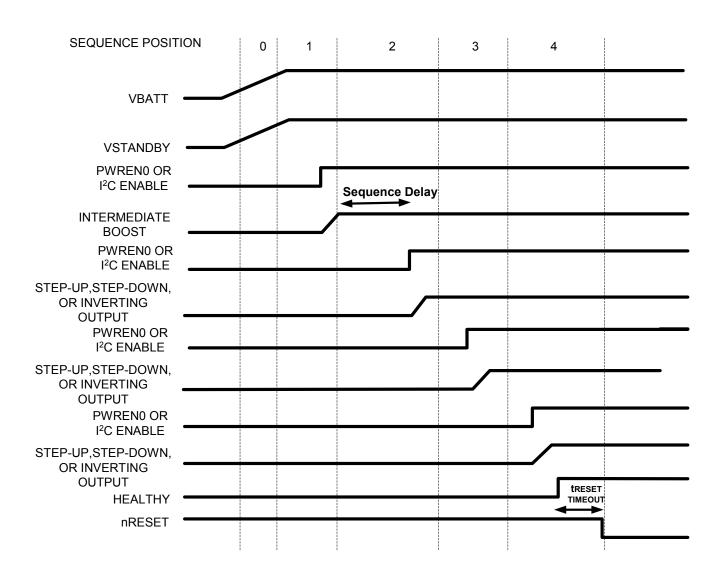

# TIMING DIAGRAMS: POWER-ON SEQUENCE

Figure 5 – SMB110 power-On sequence. Any PWM channel may be enabled or disabled through an  $I^2$ C command or by the PWREN0 pin.

# **APPLICATIONS INFORMATION**

#### **DEVICE OPERATION**

#### **POWER SUPPLY**

The SMB110 can be powered from an input voltage between 2.7-6.0 volts applied between the VBATT pin and ground. The input voltage applied to the VBATT pin is internally regulated and used as an internal VBATT supply. The VBATT pin is monitored by an UnderVoltage Lockout (UVLO) circuit, which prevents the device from turning on when the voltage at this node is less than the UVLO threshold.

#### POWER-ON/OFF CONTROL

The outputs on the SMB110 can be turned on in one of three ways: first a general purpose enable input pin PWREN0, second an I<sup>2</sup>C **Power on** command can be issued, or third if a programmable bit is set to initiate the power on process when the UVLO threshold is exceeded. a restart will only occur if the power-on pin is toggled or an I<sup>2</sup>C **Power on** command is issued.

#### **ENABLE**

Once a power on command has been issued, the power on process can be controlled by means of an enable signal. Each channel can be controlled by one of four enable signals and the assignment type can be mixed and matched for each of the four channels. The enable signal can stall the power-on process until the enable is valid, or disable a controller once all supplies have been enabled. There are two ways to generate the enable signal; the first approach allows the enable signal to be assigned the PWREN0 pin, and the second approach allows the enable to be controlled by the contents of a volatile register that can be written to at any time. This volatile register will be automatically initialized once the UVLO threshold has been exceeded to a known programmed state.

#### **POWER-ON SEQUENCING**

Each channel on the SMB110 may be placed in any one of four unique sequence positions. To provide programmable order, the SMB110 navigates between these sequence positions using a feedback-based cascade-sequencing circuit. Cascade sequencing is the process in which each channel is continually compared against a programmable reference voltage until the voltage on the monitored channel exceeds the reference voltage, at which point an internal sequence position counter is incremented and the next sequence position is entered.

Once power-on sequencing has been initiated, automated sequencing may commence in one of three ways (Figure 7): normal sequencing, sequencing with

enable, and sequencing with channel bypass. In addition, each channel may be powered on in a manual mode, independent of the sequence position. The power-on sequencing mode selection is programmable over the I<sup>2</sup>C bus and stored in the non-volatile memory.

#### NORMAL CASCADE SEQUENCING

During Normal Sequencing, the sequence position counter is initialized to the first sequence position (position 1), each channel occupying this position then waits an individual programmable timeout period (tppto) of 1.5, 12.5, 25, or 50 ms. Once enabled, all channels occupying the first sequence position will begin a softstart. As the output voltage of the channel is ramped up, it is monitored by a comparator based, user programmable, under-voltage threshold sensor. After this threshold is exceeded, indicating that the selected channel(s) have reached their nominal operating range the sequence position counter is incremented, and fault monitoring begins for that channel. Once all channels occupying the first sequence position have surpassed their under-voltage thresholds, the power-on delay for the next sequence position will begin. This process continues until all channels have been sequenced on and are above their under-voltage threshold.

#### **SEQUENCING WITH ENABLE**

During the Sequencing With Enable mode, sequencing commences as with the Normal Sequencing, except that prior to a channel beginning to soft-start, the enable corresponding to that channel must be asserted. In the event that the enable is not asserted, sequencing will halt indefinitely until a valid enable is provided. Once a valid enable is provided, a soft-start function will begin for that channel. This process will continue until all channels occupying the first sequence position are above their under-voltage settings, at which point the sequence position counter will be incremented.

#### **SEQUENCING WITH CHANNEL BYPASS**

When the Sequencing With Channel Bypass mode is selected, sequencing will commence as with the Sequencing With Enable, except that if the enable signal is not asserted by the end of the power-on delay period, that channel will be bypassed. If no other channels occupy the current sequence position, the sequence position counter will be incremented beginning the power-on delay for all channels in the next sequence position. Once a channel has been bypassed, it may still be enabled any time prior to a power off operation.

### **APPLICATIONS INFORMATION (CONTINUED)**

#### MANUAL MODE

The SMB110 also provides a manual power-on mode in which each channel may be enabled individually irrespective of the state of other channels. In this mode, the enable has complete control over the channel, and all sequencing is ignored. In Manual mode channels will not be disabled in the event of a fault.

#### POWER OFF OPTIONS

#### **FORCE-SHUTDOWN**

When a battery fault occurs, a UV or OV is detected on any PWM channel, or an I<sup>2</sup>C force-shutdown command is issued, all channels will be immediately disabled.

#### **SEQUENCE TERMINATION TIMER**

At the beginning of each sequence position, an internal programmable timer will begin to time out. When this timer has expired, the SMB110 will automatically perform a force-shutdown operation. This timer is user programmable with a programmable sequence termination period ( $t_{PST}$ ) of 50,100,200 ms; this function can also be disabled.

#### **POWER OFF SEQUENCING**

The SMB110 has a power-off sequencing operation. During a power off operation the supplies will be powered off in the reverse order they where powered on in. During the power off sequencing, all enables are ignored.

When a power-off command is issued the SMB110 will set the sequence position counter to the last sequence position and disable that channel without soft-start control; once off, the power off delay for the channel(s) in the next to last sequence position will begin to timeout, after which that channel(s) will be disabled. This process will continue until all channels have been disabled and are off. The programmable power-off sequence timeout period ( $t_{DPOFF}$ ) can be set to 1.5, 12.5, 25, or 50 ms.

If a channel fails to turn off within the sequence termination period, the sequence termination timer will initiate a force shutdown, if enabled.

#### **MONITORING**

The SMB110 monitors all 4 PWM outputs for undervoltage (UV) and over-voltage (OV) faults. The monitored levels are user programmable, and may be set at 5,10, 15, and 20 percent of the nominal output voltage.

Each output possesses a glitch filter to ensure that short violations in the UV or OV settings will not result in a fault-triggered action. All glitch filters on the SMB110 are user programmable and may be set to either 0 or 8 µs.

In the event that one or more channels violate their respective UV/OV setting for a period exceeding that specified by the glitch filter, all channels (not set to Manual mode) can optionally be powered off and-or, the healthy pin can be triggered. The programmable power off conditions that may result from a threshold violation include the immediate power off all supplies (force-shutdown) or the sequence of all supplies off.

Monitoring is accomplished by a comparator-based approach, in which a programmable voltage reference is compared against the monitored signal. Each channel possesses a dedicated reference voltage generated by a programmable level shifting digital to analog converter. Each of which can be set from 0-1.0 volts in 4mV increments.

#### **BATTERY MONITORING**

The battery voltage is monitored for two user programmable UV settings via the VBATT pin

The SMB110 contains two user programmable voltagemonitoring levels, UV1 and UV2. Battery voltage, like all monitored voltages, is compared against a user programmable voltage set internally by a digital to analog converter.

Once the voltage on the VBATT pin has fallen below either of the programmable under voltage set points the SMB110 can be programmed to respond in one of three ways, it can perform: a power-off operation, a force-shutdown operation, or take no action. When programmed to perform a power-off or force-shutdown operation the SMB110 can optionally be programmed to latch the outputs off until an I<sup>2</sup>C power-on command is issued or immediately restart once the UV condition has been removed.

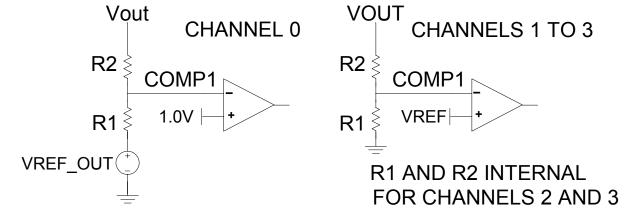

#### **OUTPUT VOLTAGE**

The PWM output voltages are set by a resistor divider from the output to the COMP1 node; see Figure 6. For the buck channels (Ch[2:3]), the voltage divider is internal to the part and programmable. The resistor divider may be set by adjusting a 100 k $\Omega$  resistor string with 8 taps from R1 = 20-90 k $\Omega$ . For the boost output (Ch1), the resistor divider is external and any appropriate value of R1 an R2 can be chosen. The reference voltage that sets the output is user programmable, and may be set anywhere from 0-1.0V in 4 mV increments for channels 1 to 3, channel 0 is fixed at 1.0V. The Channel 0 inverting output is set by the external resistor divider and the VREF\_OUT

# **APPLICATIONS INFORMATION (CONTINUED)**

voltage, which varies from 1.0 - 2.0V in 8 mV increments

#### LDO STANDBY VOLTAGE

The SMB110 has an internal 3.3 volt Low Dropout (LDO) linear regulator. While the battery voltage is above the UV2 level this supply is powered from the LDO\_SUPPLY pin, however, when the battery voltage drops below the UV2 level the LDO supply voltage will be routed to the battery through an internal analog multiplexer. The LDO will continue to be supplied by the battery until the latched UV2 pin is released. The LDO will be disabled once the Battery voltage falls below the UV2 level.

#### **SOFT START**

The SMB110 provides a programmable soft-start function for all PWM outputs. The soft-start control limits the slew rate that each output is allowed to ramp up without the need for an external capacitor. The soft start slew rate is proportional to the product of the output voltage and a slew rate reference; see Figure 5. This global reference is programmable and may be set to 400,200,100,67,50,33,25, and 20 volts per second. The slew rate control can also be disabled on any channel not requiring the feature.

Figure 6: The output voltage is set by the resistor divider. The resistor divider is internal for all buck channels. VREF is programmable from 0 to 1.0V in 4 mV increments and VREF\_OUT is programmable from 1.0 to 2.0V in 8 mV increments. All voltage references are programmable via the I<sup>2</sup>C interface.

# **APPLICATIONS INFORMATION (CONTINUED)** RESTART AFTER POWER-OFF OR FORCE-SHUTDOWN 1<sup>2</sup>C POWER ON COMMAND B E G IN S E Q U E N C IN G SEQUENCE POSITION 1 CURRENT SEQUENCE POSITION NEXT SEQUENCE POSITION CHANNEL-SPECIFIC PROGRAMMABLE OPTIONS NORMAL SEQUENCING SEQUENCING WITH CHANNEL BYPASS SEQUENCING WITH ENABLE ENABLE = PWRENO PIN XOR I2C PWRENABLE BIT ENABLE = PWRENO PIN XOR I2C PWRENABLE BIT POWER ON DELAY POWER ON DELAY POWER ON DELAY W AIT FOR ENABLE E N A B L E L O W ENABLE ENABLE LOW ENABLE HIGH HIGH SOFT-START W AIT FOR ENABLE ENABLE ENABLE LOW MONITOR SOFT-START V O U T < = U V V O U T < = U V

Figure 7 – Power-on sequencing flow chart: There are three automated power-on sequencing modes, and a manual mode.

### **APPLICATIONS INFORMATION (CONTINUED)**

#### MINIMUM LOAD

The duty cycle is limited to a 10-90% range. Consequently, the boost channels require a minimum load to prevent over voltage conditions from occurring.

This may be overcome by attaching a resistor preload to the output that matches the minimum load requirements. This approach will result in a constant current consumption while the outputs are enabled. Alternatively, a zener diode (with a higher breakdown voltage than the output) can be connected across the output clamping the output voltage. This approach will not draw current when the load is enabled on the output.

#### **MARGINING**

The SMB110 has two additional voltage settings for channels 0-3, margin high and margin low. The margin high and margin low voltage settings have the same voltage range as the controllers' nominal output voltage. These settings are stored in the configuration registers and are loaded into the voltage setting by margin commands issued via the I<sup>2</sup>C bus.