# ColdFire 2/2M Integrated Microprocessor User's Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and eregistered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### DOCUMENTATION FEEDBACK

FAX 512-895-8593—Documentation Comments Only (no technical questions please) http://www.mot.com/hpesd/docs\_survey.html—Documentation Feedback Only

The Technical Communications Department welcomes your suggestions for improving our documentation and encourages you to complete the documentation feedback form at the World Wide Web address listed above. Your help helps us measure how well we are serving your information requirements.

The Technical Communications Department also provides a fax number for you to submit any questions or comments about this document or how to order other documents. Please provide the part number and revision number (located in upper right-hand corner of the cover) and the title of the document. When referring to items in the manual, please reference by the page number, paragraph number, figure number, table number, and line number if needed. **Please do not fax technical questions to this number.**

When sending a fax, please provide your name, company, fax number, and phone number including area code.

#### For Internet Access:

Web Only: http://www.mot.com/aesop

#### For Hotline Questions:

FAX (US or Canada): 1-800-248-8567

## **Applications and Technical Information**

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

## — Sales Offices —

Field Applications Engineering Available Through All Sales Offices

|                                                                           |                                  | <b></b>                                                                                                        | 10/511/3700011                          |

|---------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| UNITED STATES                                                             | ()                               | GERMANY, Langenhagen/ Hanover                                                                                  |                                         |

| ALABAMA, Huntsville<br>ARIZONA, Tempe                                     | (205) 464-6800                   | GERMANY, Munich                                                                                                | 49 89 92103-0                           |

|                                                                           | (602) 897-5056                   | GERMANY, Nuremberg                                                                                             | 49 911 64-3044                          |

| CALIFORNIA, Agoura Hills                                                  | (818) 706-1929                   | GERMANY, Sindelfingen                                                                                          | 49 7031 69 910                          |

| CALIFORNIA, Agoura Hills<br>CALIFORNIA, Los Angeles<br>CALIFORNIA, Irvine | (310) 417-8848<br>(714) 753-7360 | GERMANY, Nuremberg GERMANY, Sindelfingen GERMANY, Wiesbaden HONG KONG, Kwai Fong Tai Po                        | 49 611 761921                           |

| CALIFORNIA, RosevIlle                                                     | (916) 922-7152                   | HONG KONG, Kwai Fong                                                                                           | 852-4808333                             |

| CALIFORNIA, San Diego                                                     | (619) 541-2163                   | Tai Po                                                                                                         | 852-6668333                             |

| CALIFORNIA, Sunnyvale                                                     | (408) 749-0510                   | INDIA, Bangalore                                                                                               | (91-812)627094                          |

| COLORADO, Colorado Springs                                                | (719) 599-7497                   | ISRAEL, Tel Aviv                                                                                               | 972(3)753-8222                          |

| COLORADO. Denver                                                          | (303) 337-3434                   | ITALY, Milan                                                                                                   | `39(2)82201                             |

| CONNECTICUT, Wallingford                                                  | (203) 949-4100                   | <b>JAPAŃ</b> , Aizu                                                                                            | 81(241)272231                           |

| FLORIDA, Maitland                                                         | (407) 628-2636                   | JAPAN, Atsugi                                                                                                  | 81(0462)23-0761                         |

| FLORIDA, Pompano Beach/                                                   | (005) 100 0770                   | JAPAN, Kumagaya                                                                                                | 81(0485)26-2600                         |

| Fort Lauderdale                                                           | (305) 486-9776                   | JAPAN, Kyushu                                                                                                  | 81(092)771-4212                         |

| FLORIDA, Clearwater                                                       | (813) 538-7750                   | IAPAN Mito                                                                                                     | 81(0292)26-2340                         |

| GEORGIA, Atlanta                                                          | (404) 729-7100<br>(208) 323-9413 | JAPAN, Nagoya                                                                                                  | 81(052)232-1621                         |

| IDAHO, Boise                                                              | (708) 490-9500                   | JAPAN, Osaka                                                                                                   | 81(06)305-1801                          |

| ILLINOIS, Chicago/Hoffman Estates INDIANA, Fort Wayne                     | (219) 436-5818                   | JAPAN, Sendai                                                                                                  | 81(22)268-4333                          |

| INDIANA, Indianapolis                                                     | (317) 571-0400                   | JAPAN Tachikawa                                                                                                | 81(0425)23-6700                         |

| INDIANA, Kokomo                                                           | (317) 457-6634                   | JAPAN, Tachikawa<br>JAPAN, Tokyo                                                                               | 81(03)3440-3311                         |

| IOWA, Cedar Rapids                                                        | (319) 373-1328                   | IADAN Vokobama                                                                                                 | 81(045)472-2751                         |

| KANSAS, Kansas City/Mission                                               | (913) 451-8555                   | JAPAN, Yokohama<br>KORFA Pusan                                                                                 | 82(51)4635-035                          |

| MARYLAND. Columbia                                                        | (410) 381-1570                   | 11 <b>0</b> 11 <b>2</b> 11, 1 dod:                                                                             | 02(31)4033-033                          |

| MASSACHUSETTS, Marborough                                                 | (508) 481-8100                   | KOREA, Seoul<br>MALAYSIA, Penang                                                                               | 82(2)554-5188<br>60(4)374514            |

| MASSACHUSETTS, Woburn                                                     | (617) 932-9700                   | MEXICO, Mexico City                                                                                            | 52(5)282-2864                           |

| MICHIGAN, Detroit                                                         | (313) 347-6800                   | MEXICO, Mexico City                                                                                            | 52(36)21-8977                           |

| MINNESOTA, Minnetonka<br>MISSOURI, St. Louis                              | (612) 932-1500<br>(314) 275-7380 | MEXICO, Guadalajara<br>Marketing                                                                               | 52(36)21-9023                           |

| NEW JERSEY, Fairfield                                                     | (201) 808-2400                   | Marketing                                                                                                      | 52(36)660 0160                          |

| NEW YORK, Fairport                                                        | (716) 425-4000                   | Customer Service NETHERLANDS, Best PUERTO RICO, San Juan SINGAPORE                                             | 52(36)669-9160<br>(31)49988 612 11      |

| NEW YORK, Hauppauge                                                       | (516) 361-7000                   | DIJECTO DICO San Juan                                                                                          | (809)793-2170                           |

| NEW YORK, Poughkeepsie/Fishkill                                           | (914) 473-8102                   | SINGADODE                                                                                                      | (6E)204E429                             |

| NORTH CAROLINA, Raleigh                                                   | (919) 870-4355                   | SINGAPURE<br>SDAIN Modrid                                                                                      |                                         |

| OHIO, Cleveland                                                           | (216) 349-3100                   | SPAIN, Madrid                                                                                                  | 34(1)457-8204                           |

| OHIO, Columbus/Worthington                                                | (614) 431-8492                   | Of<br>CMEDEN Color                                                                                             | 34(1)457-8254                           |

| OHIO, Dayton                                                              | (513) 495-6800                   | SWEDEN, Solna                                                                                                  | 46(8)734-8800                           |

| OKLAHOMA, Tulsa<br>OREGON, Portland                                       | (800) 544-9496<br>(503) 641-3681 | SWITZERLAND, Geneva                                                                                            | 41(22)7991111                           |

| PENNSYLVANIA, Colmar                                                      | (215) 041-3001                   | SWITZERLAND, ZURICH                                                                                            | 41(1)730 4074                           |

| Philadelphia/Horsham                                                      | (215) 997-1020<br>(215) 957-4100 | TAIWAN, Taipei                                                                                                 | 886(2)717-7089                          |

| TENNESSEE, Knoxville                                                      | (615) 584-4841                   | SWITZERLAND, Geneva<br>SWITZERLAND, Zurich<br>TAIWAN, Taipei<br>THAILAND, Bangkok<br>UNITED KINGDOM, Aylesbury | (66-2)254-4910                          |

| TEXAS. Austin                                                             | (512) 873-2000                   | UNITED KINGDOM, Aylesbury                                                                                      | 44(296)395-252                          |

| IEXAS, Houston                                                            | (800) 343-2692                   | FULL LINE REPRESENT                                                                                            | ATIVES                                  |

| TEXAS, Plano                                                              | (214) 516-5100                   | COLORADO, Grand Junction                                                                                       |                                         |

| VIRGINIA, Richmond                                                        | (804) 285-2100                   | Cheryl Lee Whitely                                                                                             | (303) 243-9658                          |

| WASHINGTON, Bellevue                                                      | (206) 454-4160                   | KANSAS, Wichita                                                                                                |                                         |

| Seattle Access                                                            | (206) 622-9960<br>(414) 792-0122 | Melinda Shores/Kelly Greiving                                                                                  | (316) 838 0190                          |

| WISCONSIN, Milwaukee/Brookfield                                           | (414) / 92-0122                  | NEVADA, Reno                                                                                                   |                                         |

| CANADA                                                                    | (a.a. () a.a.a. =====            | Galena Technology Group                                                                                        | (702) 746 0642                          |

| BRITISH COLUMBIA, Vancouver                                               | (604) 293-7605                   | NEW MEXICO, Albuquerque<br>S&S Technologies, Inc.                                                              |                                         |

| ONTARIO, Toronto                                                          | (416) 497-8181                   | S&S Technologies, Inc.                                                                                         | (505) 298-7177                          |

| ONTARIO, Ottawa                                                           | (613) 226-3491                   | UTAH, Salt Lake City                                                                                           |                                         |

| QUEBEC, Montreal                                                          | (514) 731-6881                   | Utah Component Sales, Inc.                                                                                     | (801) 561-5099                          |

| INTERNATIONAL                                                             |                                  | WASHINGTON, Spokane                                                                                            | , ,                                     |

| AUSTRALIA, Melbourne                                                      | (61-3)887-0711                   | Doug Kenley                                                                                                    | (509) 924-2322                          |

| AUSTRALIA, Sydney                                                         | (61(2)906-3855                   | ARGENTINA, Buenos Aires                                                                                        |                                         |

| BRAZIL, Sao Paulo                                                         | 55(11)815-4200                   | Argonics, S.A.                                                                                                 | (541) 343-1787                          |

| CHINA, Beijing                                                            | 86 505-2180                      | HYBRID COMPONENTS RE                                                                                           | SELLERS                                 |

| FINLAND, Heľsinki                                                         | 358-0-35161191                   | Elmo Semiconductor                                                                                             | (818) 768-7400                          |

| Car Phone                                                                 | 358(49)211501                    | Minco Technology Labs Inc.                                                                                     | (512) 834-2022                          |

| FRANCE, Paris/Vanves                                                      | 33(1)40 955 900                  | Semi Dice Inc.                                                                                                 | (310) 594-4631                          |

|                                                                           | •                                | =                                                                                                              | , , , , , , , , , , , , , , , , , , , , |

## **PREFACE**

The ColdFire2/2M Integrated Microprocessor User's Manual describes the programming, capabilities, and operation of the ColdFire2/2M device. Refer to the MCF5200 ColdFire Family Programmer's Reference Manual Rev. 1.0 for information on the ColdFire Family of microprocessors.

Throughout this document, the ColdFire2/2M integrated microprocessor is referred to as "the ColdFire2/2M."

#### **CONTENTS**

This user manual is organized as follows:

Section 1: Overview

Section 2: Signal Summary

Section 3: Master Bus Operations

Section 4: Exception Processing

Section 5: Integrated Memories

Section 6: Multiply-Accumulate Unit

Section 7: Debug Support

Section 8: Test Operation

Section 9: Instruction Execution Timing Section 10: Electrical Characteristics

Appendix A: Register Summary

Appendix B: New MAC Instructions

Index

## **TABLE OF CONTENTS**

| Paragrap<br>Number |                                     | Page<br>Number |

|--------------------|-------------------------------------|----------------|

|                    | Section 1 Overview                  |                |

| 1.1                | FlexCore Integrated Processors      | 1-2            |

| 1.1.1              | FlexCore Advantages                 | 1-4            |

| 1.1.2              | FlexCore Module Types               |                |

| 1.2                | Development Cycle                   | 1-5            |

| 1.3                | System Architecture                 |                |

| 1.3.1              | Internal Bus Structure              |                |

| 1.3.1.1            | Master Bus                          | 1-8            |

| 1.3.1.2            | Slave Bus                           | 1-9            |

| 1.3.1.3            | External Bus                        | 1-9            |

| 1.3.1.4            | Test Bus                            | 1-9            |

| 1.3.2              | System Functional Blocks            | 1-9            |

| 1.3.2.1            | Alternate Master                    | 1-9            |

| 1.3.2.2            | ColdFire2/2M                        | 1-9            |

| 1.3.2.3            | I-Cache Data Array                  | 1-10           |

| 1.3.2.4            | I-Cache Tag Array                   | 1-10           |

| 1.3.2.5            | Master Bus Arbiter (MARB)           | 1-10           |

| 1.3.2.6            | ROM Array                           | 1-11           |

| 1.3.2.7            | Slave Modules                       | 1-11           |

| 1.3.2.8            | SRAM Array                          | 1-11           |

| 1.3.2.9            | System Bus Controller (SBC)         | 1-11           |

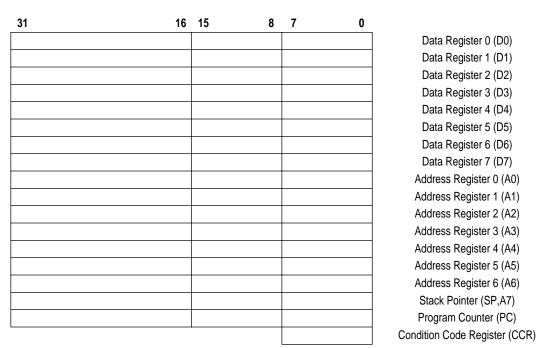

| 1.4                | Programming Model                   |                |

| 1.4.1              | Integer Unit User Programming Model |                |

| 1.4.1.1            | Data Registers (D0 – D7)            |                |

| 1.4.1.2            | Address Registers (A0 – A6)         | 1-12           |

| 1.4.1.3            | Stack Pointer (A7,SP)               | 1-12           |

| 1.4.1.4            | Program Counter (PC)                | 1-12           |

| 1.4.1.5            | Condition Code Register (CCR)       |                |

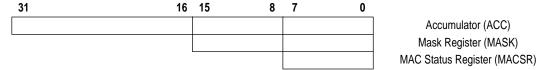

| 1.4.2              | MAC Unit User Programming Model     |                |

| 1.4.2.1            | Accumulator (ACC)                   |                |

| 1.4.2.2            | Mask Register (MASK)                |                |

| 1.4.2.3            | MAC Status Register (MACSR)         |                |

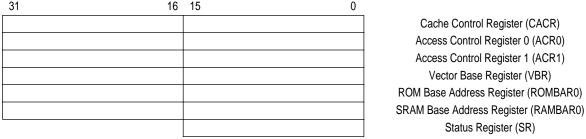

| 1.4.3              | Supervisor Programming Model        | 1-14           |

| Paragrap<br>Number | n<br>Title                                        | Page<br>Number |

|--------------------|---------------------------------------------------|----------------|

| 1.4.3.1            | Status Register (SR)                              | 1-14           |

| 1.4.3.2            | Cache Control Register (CACR)                     | 1-15           |

| 1.4.3.3            | Access Control Registers (ACR0, ACR1)             | 1-15           |

| 1.4.3.4            | Vector Base Register (VBR)                        |                |

| 1.4.3.5            | ROM Base Address Register (ROMBAR0)               | 1-15           |

| 1.4.3.6            | SRAM Base Address Register (RAMBAR0)              | 1-15           |

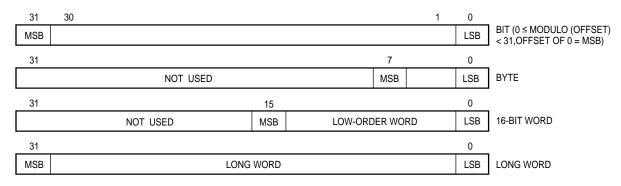

| 1.5                | Integer Data Formats                              | 1-16           |

| 1.6                | Organization of Data in Registers                 | 1-16           |

| 1.6.1              | Organization of Integer Data Formats in Registers | 1-16           |

| 1.6.2              | Organization of Integer Data Formats in Memory    | 1-17           |

| 1.7                | Addressing Mode Summary                           | 1-18           |

| 1.8                | Instruction Set Summary                           | 1-19           |

|                    | Section 2                                         |                |

|                    | Signal Summary                                    |                |

| 2.1                | Introduction                                      | 2-1            |

| 2.2                | Master Bus Signals                                | 2-3            |

| 2.2.1              | 68K Interrupt Acknowledge Mode Enable (IACK_68K)  | 2-3            |

| 2.2.2              | Master Address Bus (MADDR[31:0])                  | 2-3            |

| 2.2.3              | Master Arbiter Control (MARBC[1:0])               | 2-3            |

| 2.2.4              | Master Freeze (MFRZB)                             | 2-4            |

| 2.2.5              | Master Kill (MKILLB)                              |                |

| 2.2.6              | Master Read Data Bus (MRDATA[31:0])               | 2-4            |

| 2.2.7              | Master Read Data Input Enable (MIE)               | 2-4            |

| 2.2.8              | Master Read/Write (MRWB)                          | 2-4            |

| 2.2.9              | Master Reset (MRSTB)                              | 2-4            |

| 2.2.10             | Master Size (MSIZ[1:0])                           |                |

| 2.2.11             | Master Transfer Acknowledge (MTAB)                | 2-5            |

| 2.2.12             | Master Transfer Error Acknowledge (MTEAB)         | 2-5            |

| 2.2.13             | Master Transfer Modifier (MTM[2:0])               | 2-5            |

| 2.2.14             | Master Transfer Start (MTSB)                      |                |

| 2.2.15             | Master Transfer Type (MTT[1:0])                   | 2-6            |

| 2.2.16             | Master Write Data Bus (MWDATA[31:0])              | 2-6            |

| 2.2.17             | Master Write Data Output Enable (MWDATAOE)        | 2-6            |

| 2.3                | General Control Signals                           |                |

| 2.3.1              | Clock (CLK)                                       | 2-6            |

| 2.3.2              | Interrupt Priority Level (IPLB[2:0])              | 2-6            |

| 2.4                | Integrated Memory Signals                         |                |

| 2.4.1              | Instruction Cache Signals                         | 2-7            |

| Paragraph<br>Number | h<br>Title                                        | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

| 2.4.1.1             | Instruction Cache Address Bus (ICH_ADDR[14:2])    | 2-7            |

| 2.4.1.2             | Instruction Cache Data Chip-Select (ICHD_CSB)     | 2-7            |

| 2.4.1.3             | Instruction Cache Data Input Bus (ICHD_DI[31:0])  | 2-7            |

| 2.4.1.4             | Instruction Cache Data Output Bus (ICHD_DO[31:0]) | 2-7            |

| 2.4.1.5             | Instruction Cache Data Strobe (ICHD_ST)           | 2-7            |

| 2.4.1.6             | Instruction Cache Data Read/Write (ICHD_RWB)      | 2-7            |

| 2.4.1.7             | Instruction Cache Size (ICH_SZ[2:0])              |                |

| 2.4.1.8             | Instruction Cache Tag Chip-Select (ICHT_CSB)      | 2-8            |

| 2.4.1.9             | Instruction Cache Tag Input Bus (ICHT_DI[31:8])   | 2-8            |

| 2.4.1.10            | Instruction Cache Tag Output Bus (ICHT_DO[31:8])  | 2-8            |

| 2.4.1.11            | Instruction Cache Tag Strobe (ICHT_ST)            |                |

| 2.4.1.12            | Instruction Cache Tag Read/Write (ICHT_RWB)       | 2-9            |

| 2.4.2               | Integrated ROM Signals                            |                |

| 2.4.2.1             | ROM Address Bus (ROM_ADDR[14:2])                  |                |

| 2.4.2.2             | ROM Data Output Bus (ROM_DO[31:0])                | 2-9            |

| 2.4.2.3             | ROM Enable (ROM_ENB[1:0])                         |                |

| 2.4.2.4             | ROM Size (ROM_SZ[2:0])                            |                |

| 2.4.2.5             | ROM Valid (ROM_VLD)                               |                |

| 2.4.3               | Integrated SRAM Signals                           |                |

| 2.4.3.1             | SRAM Address Bus (SRAM_ADDR[14:2])                |                |

| 2.4.3.2             | SRAM Chip-Select (SRAM_CSB)                       |                |

| 2.4.3.3             | SRAM Data Input Bus (SRAM_DI[31:0])               |                |

| 2.4.3.4             | SRAM Data Output Bus (SRAM_DO[31:0])              |                |

| 2.4.3.5             | SRAM Size (SRAM_SZ[2:0])                          |                |

| 2.4.3.6             | SRAM Strobe (SRAM_ST[3:0])                        | 2-11           |

| 2.4.3.7             | SRAM Read/Write (SRAM_RWB[3:0])                   |                |

| 2.5                 | Debug Signals                                     |                |

| 2.5.1               | Break Point (BKPTB)                               |                |

| 2.5.2               | Debug Data (DDATA[3:0])                           |                |

| 2.5.3               | Development Serial Clock (DSCLK)                  |                |

| 2.5.4               | Development Serial Input (DSI)                    |                |

| 2.5.5               | Development Serial Output (DSO)                   |                |

| 2.5.6               | Processor Status (PST[3:0])                       |                |

| 2.6                 | Test Signals                                      |                |

| 2.6.1               | Integrated Memory Test Signals                    | 2-12           |

| Paragrap<br>Number | h<br>Title                                       | Page<br>Number |

|--------------------|--------------------------------------------------|----------------|

| 2.6.1.1            | Test Address Bus (TEST_ADDR[14:2])               | 2-13           |

| 2.6.1.2            | Test Control (TEST CTRL)                         | 2-13           |

| 2.6.1.3            | Test IDATA Read (TEST_IDATA_RD)                  | 2-13           |

| 2.6.1.4            | Test IDATA Write (TEST_IDATA_WRT)                | 2-13           |

| 2.6.1.5            | Test Instruction Cache Read Hit (TEST_RHIT)      |                |

| 2.6.1.6            | Test Invalidate Inhibit (TEST_IVLD_INH)          |                |

| 2.6.1.7            | Test ITAG Write (TEST_ITAG_WRT)                  | 2-13           |

| 2.6.1.8            | Test KTA Mode Enable (TEST_KTA)                  |                |

| 2.6.1.9            | Test Mode Enable (TEST_MODE)                     | 2-13           |

| 2.6.1.10           | Test SRAM Read (TEST_SRAM_RD)                    | 2-13           |

| 2.6.1.11           | Test SRAM Write (TEST_SRAM_WRT)                  | 2-13           |

| 2.6.1.12           | Test Read (TEST_RD)                              | 2-13           |

| 2.6.1.13           | Test ROM Read (TEST_ROM_RD)                      | 2-13           |

| 2.6.1.14           | Test Write Inhibit (TEST_WR_INH)                 |                |

| 2.6.2              | Scan Signal Description                          |                |

| 2.6.2.1            | Scan Enable (SCAN_ENABLE)                        |                |

| 2.6.2.2            | Scan Exercise Array (SCAN_XARRAY)                |                |

| 2.6.2.3            | Scan Input (SCAN_IN[15:0])                       |                |

| 2.6.2.4            | Scan Mode (SCAN_MODE)                            |                |

| 2.6.2.5            | Scan Output (SCAN_OUT[15:0])                     |                |

| 2.6.2.6            | Scan Test Ring Clock (TR_CLK)                    |                |

| 2.6.2.7            | Scan Test Ring Core Mode Enable (TR_CORE_EN)     |                |

| 2.6.2.8            | Scan Test Ring Data Input 0 (TR_DI0)             |                |

| 2.6.2.9            | Scan Test Ring Data Input 1 (TR_DI1)             |                |

| 2.6.2.10           | Scan Test Ring Data Output 0 (TR_DO0)            |                |

| 2.6.2.11           | Scan Test Ring Data Output 1 (TR_DO1)            |                |

| 2.6.2.12           | Scan Test Ring Enable (TR_EN)                    |                |

| 2.6.2.13           | Scan Test Ring Mode (TR_MODE)                    | 2-14           |

|                    | Section 3                                        |                |

|                    | Master Bus Operation                             |                |

| 3.1                | Signal Description                               |                |

| 3.1.1              | 68K Interrupt Acknowledge Mode Enable (IACK_68K) |                |

| 3.1.2              | Master Address Bus (MADDR[31:0])                 | 3-1            |

| 3.1.3              | Master Arbiter Control (MARBC[1:0])              |                |

| 3.1.4              | Master Freeze (MFRZB)                            |                |

| 3.1.5              | Master Kill (MKILLB)                             | 3-2            |

| 3.1.6              | Master Read Data Bus (MRDATA[31:0])              |                |

| 3.1.7              | Master Read Data Input Enable (MIE)              |                |

| 3.1.8              | Master Read/Write (MRWB)                         |                |

| 3.1.9              | Master Reset (MRSTB)                             | 3-2            |

| Paragrap<br>Number | h<br>Title                                            | Page<br>Number |

|--------------------|-------------------------------------------------------|----------------|

| 3.1.10             | Master Size (MSIZ[1:0])                               | 3-2            |

| 3.1.11             | Master Transfer Acknowledge (MTAB)                    | 3-2            |

| 3.1.12             | Master Transfer Error Acknowledge (MTEAB)             | 3-3            |

| 3.1.13             | Master Transfer Modifier (MTM[2:0])                   | 3-3            |

| 3.1.14             | Master Transfer Start (MTSB)                          | 3-3            |

| 3.1.15             | Master Transfer Type (MTT[1:0])                       | 3-3            |

| 3.1.16             | Master Write Data Bus (MWDATA[31:0])                  | 3-4            |

| 3.1.17             | Master Write Data Output Enable (MWDATAOE)            | 3-4            |

| 3.2                | Data Transfer Mechanism                               | 3-4            |

| 3.2.1              | Transfer Type Control Signals                         | 3-4            |

| 3.2.1.1            | ColdFire2/2M Access                                   | 3-4            |

| 3.2.1.2            | Alternate Master Access                               | 3-5            |

| 3.2.1.3            | Emulator Mode Access                                  |                |

| 3.2.1.4            | Interrupt Acknowledge Access                          | 3-5            |

| 3.2.1.5            | CPU Space Access                                      | 3-5            |

| 3.2.2              | Data Bus Requirements                                 |                |

| 3.3                | Data Transfers                                        |                |

| 3.3.1              | Byte, Word, and Longword Read Transfers               |                |

| 3.3.2              | Byte, Word, and Longword Write Transfers              |                |

| 3.3.3              | Line Read Transfer                                    |                |

| 3.3.4              | Line Write Transfers                                  |                |

| 3.4                | Misaligned Operands                                   |                |

| 3.5                | Invalid Master Bus Cycles                             |                |

| 3.6                | Pipeline Stalls                                       |                |

| 3.7                | Interrupt Acknowledge Bus Cycles                      |                |

| 3.7.1              | Interrupt Acknowledge Bus Cycle (Terminated normally) |                |

| 3.7.2              | Spurious Interrupt Acknowledge Bus Cycle              |                |

| 3.8                | Master Bus Exception Control Cycles                   |                |

| 3.8.1              | Bus Errors                                            |                |

| 3.8.2              | Fault-on-Fault Halt                                   |                |

| 3.9                | Reset Operation                                       |                |

| 3.10               | Master Bus Arbitration                                |                |

| 3.10.1             | Master Bus Arbitration Algorithm                      |                |

| 3.10.1.1           | Park on ColdFire2/2M                                  |                |

| 3.10.1.2           | Park on Alternate Master                              |                |

| 3.10.1.3           | Park on Current Master                                |                |

| 3.10.2             | Bus Arbitration Programming Model                     | 3-31           |

|                    | Section 4 Exception Processing                        |                |

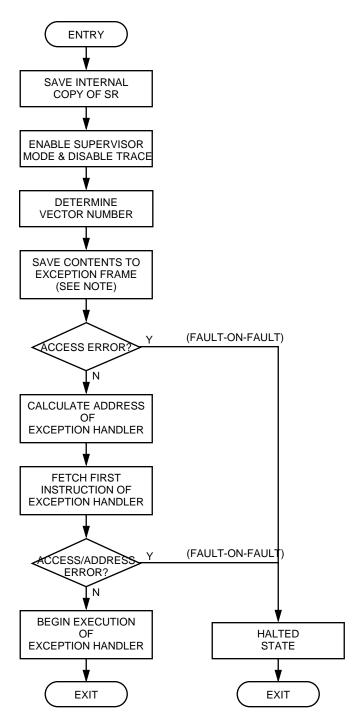

| 4.1                | Exception Processing Overview                         | 4-1            |

| Paragrap |                                                      | Page   |

|----------|------------------------------------------------------|--------|

| Number   | Title                                                | Number |

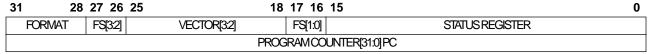

| 4.1.1    | Exception Stack Frame Definition                     |        |

| 4.1.1.1  | Self-Aligning Stack                                  |        |

| 4.1.2    | Exception Vectors                                    |        |

| 4.1.3    | Multiple Exceptions                                  |        |

| 4.1.4    | Fault-on-Fault Halt                                  |        |

| 4.2      | Exceptions                                           | 4-7    |

| 4.2.1    | Reset Exception                                      |        |

| 4.2.2    | Access Error Exception                               | 4-7    |

| 4.2.3    | Address Error Exception                              | 4-8    |

| 4.2.4    | Illegal Instruction Exception                        | 4-9    |

| 4.2.5    | Privilege Violation Exception                        | 4-9    |

| 4.2.6    | Trace Exception                                      | 4-9    |

| 4.2.7    | Unimplemented Opcode Exception                       | 4-9    |

| 4.2.8    | Debug Interrupt                                      |        |

| 4.2.9    | Format Error Exceptions                              |        |

| 4.2.10   | TRAP Instruction Exceptions                          | 4-10   |

| 4.2.11   | Interrupt Exception                                  | 4-10   |

| 4.2.11.1 | Level Seven Interrupts                               | 4-11   |

| 4.2.11.2 | Spurious, Autovectored, and Uninitialized Interrupts | 4-12   |

|          | Section 5                                            |        |

|          | Integrated Memories                                  |        |

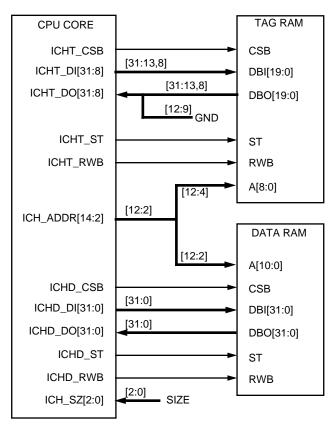

| 5.1      | Instruction Cache                                    | 5-1    |

| 5.1.1    | Instruction Cache Signal Description                 |        |

| 5.1.1.1  | Instruction Cache Address Bus (ICH_ADDR[14:2])       | 5-2    |

| 5.1.1.2  | Instruction Cache Data Chip-Select (ICHD_CSB)        | 5-2    |

| 5.1.1.3  | Instruction Cache Data Input Bus (ICHD_DI[31:0])     |        |

| 5.1.1.4  | Instruction Cache Data Output Bus (ICHD_DO[31:0])    | 5-2    |

| 5.1.1.5  | Instruction Cache Data Strobe (ICHD_ST)              | 5-2    |

| 5.1.1.6  | Instruction Cache Data Read/Write (ICHD_RWB)         | 5-3    |

| 5.1.1.7  | Instruction Cache Size (ICH_SZ[2:0])                 |        |

| 5.1.1.8  | Instruction Cache Tag Chip-Select (ICHT_CSB)         | 5-3    |

| 5.1.1.9  | Instruction Cache Tag Input Bus (ICHT_DI[31:8])      |        |

| 5.1.1.10 | Instruction Cache Tag Output Bus (ICHT_DO[31:8])     | 5-3    |

| 5.1.1.11 | Instruction Cache Tag Strobe (ICHT_ST)               | 5-4    |

| 5.1.1.12 | Instruction Cache Tag Read/Write (ICHT_RWB)          | 5-4    |

| 5.1.2    | Instruction Cache Physical Organization              |        |

| 5.1.3    | Interaction With Other Modules                       | 5-4    |

| 5.1.4    | Cache Miss Fetch Algorithm/Line Fills                | 5-4    |

| 5.1.5    | Cacheability                                         | 5-5    |

| 5.1.6    | Invalidating Cache Entries                           | 5-5    |

| Paragrap<br>Number |                                      | Page<br>Number |

|--------------------|--------------------------------------|----------------|

| 5.1.7              | Cache Coherency                      | 5-6            |

| 5.1.8              | Reset                                |                |

| 5.1.9              | Instruction Cache Programming Model  |                |

| 5.2                | Access Control Registers             |                |

| 5.2.1              | ACR Programming Model                |                |

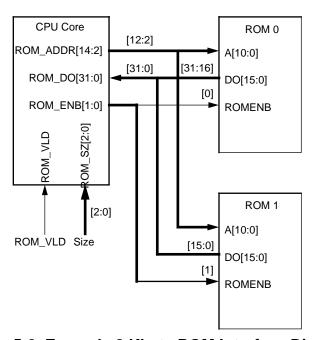

| 5.3                | ROM Module                           |                |

| 5.3.1              | ROM Signal Description               |                |

| 5.3.1.1            | ROM Address Bus (ROM_ADDR[14:2])     |                |

| 5.3.1.2            | ROM Data Output Bus (ROM_DO[31:0])   |                |

| 5.3.1.3            | ROM Enable (ROM_ENB[1:0])            |                |

| 5.3.1.4            | ROM Size (ROM_SZ[2:0])               |                |

| 5.3.1.5            | ROM Valid (ROM_VLD)                  |                |

| 5.3.2              | ROM Programming Model                |                |

| 5.4                | SRAM Module                          |                |

| 5.4.1              | SRAM Signal Description              | 5-14           |

| 5.4.1.1            | SRAM Address Bus (SRAM_ADDR[14:2])   |                |

| 5.4.1.2            | SRAM Chip-Select (SRAM_CSB)          |                |

| 5.4.1.3            | SRAM Data Input Bus (SRAM_DI[31:0])  |                |

| 5.4.1.4            | SRAM Data Output Bus (SRAM_DO[31:0]) |                |

| 5.4.1.5            | SRAM Size (SRAM_SZ[2:0])             |                |

| 5.4.1.6            | SRAM Strobe (SRAM_ST[3:0])           |                |

| 5.4.1.7            | SRAM Read/Write (SRAM_RWB[3:0])      |                |

| 5.4.2              | SRAM Programming Model               |                |

|                    | Section 6                            |                |

|                    | Multiply-Accumulate Unit             |                |

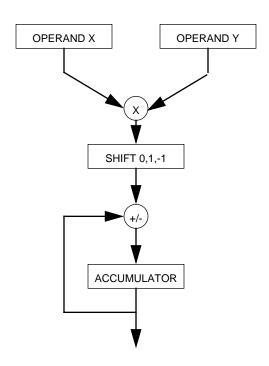

| 6.1                | Introduction                         | 6-1            |

| 6.2                | MAC Programming Model                |                |

| 6.2.1              | Accumulator (ACC)                    | 6-2            |

| 6.2.2              | MAC Status Register (MACSR)          |                |

| 6.2.3              | Mask Register (MASK)                 | 6-3            |

| 6.3                | Shifting Operations                  |                |

| 6.4                | Overflow Mode                        |                |

| 6.5                | MAC Instruction Set Summary          | 6-5            |

|                    | Section 7                            |                |

|                    | Debug Support                        |                |

| 7.1                | Signal Description                   |                |

| 7.1.1              | Break Point (BKPTB)                  | 7-1            |

| 7.1.2              | Debug Data (DDATA[3:0])              | 7-2            |

| 7.1.3 Development Serial Clock (DSCLK)                                  |  |

|-------------------------------------------------------------------------|--|

|                                                                         |  |

| 7.1.4 Development Serial Input (DSI)                                    |  |

| 7.1.5 Development Serial Output (DSO)7-2                                |  |

| 7.1.6 Processor Status (PST[3:0])7-2                                    |  |

| 7.2 Real-Time Trace7-2                                                  |  |

| 7.2.1 Processor Status Signal Encoding7-3                               |  |

| 7.2.1.1 Continue Execution (PST = \$0)                                  |  |

| 7.2.1.2 Begin Execution of an Instruction (PST = \$1)                   |  |

| 7.2.1.3 Entry into User Mode (PST = \$3)                                |  |

| 7.2.1.4 Begin Execution of PULSE or WDDATA instructions (PST = \$4) 7-3 |  |

| 7.2.1.5 Begin Execution of Taken Branch (PST = \$5)7-4                  |  |

| 7.2.1.6 Begin Execution of RTE Instruction (PST = \$7)                  |  |

| 7.2.1.7 Begin Data Transfer (PST = \$8 - \$A)                           |  |

| 7.2.1.8 Exception Processing (PST = \$C)                                |  |

| 7.2.1.9 Emulator-Mode Exception Processing (PST = \$D)7-5               |  |

| 7.2.1.10 Processor Stopped (PST = \$E)                                  |  |

| 7.2.1.11 Processor Halted (PST = $\$F$ )                                |  |

| 7.3 Background Debug Mode (BDM)                                         |  |

| 7.3.1 CPU Halt                                                          |  |

| 7.3.2 BDM Serial Interface                                              |  |

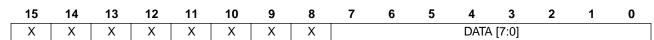

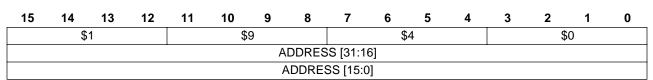

| 7.3.2.1 Receive Packet Format                                           |  |

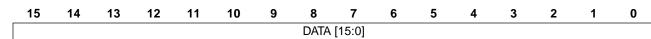

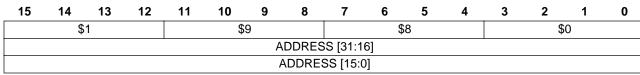

| 7.3.2.2 Transmit Packet Format                                          |  |

| 7.3.3 BDM Command Set                                                   |  |

| 7.3.3.1 BDM Command Set Summary                                         |  |

| 7.3.3.2 ColdFire BDM Commands                                           |  |

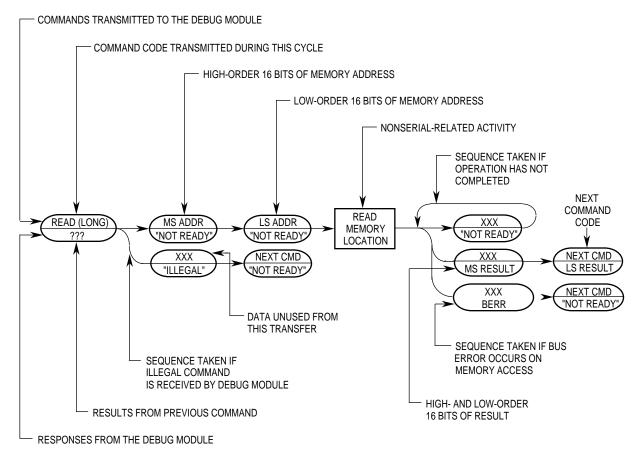

| 7.3.3.3 Command Sequence Diagram                                        |  |

| 7.3.3.4 Command Set Descriptions                                        |  |

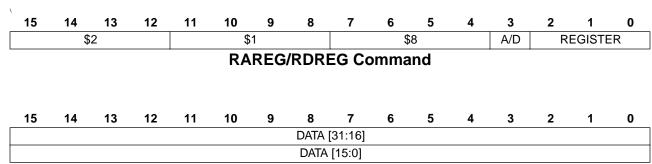

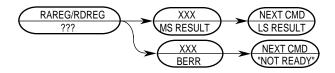

| 7.3.3.4.1 Read A/D Register (RAREG/RDREG)                               |  |

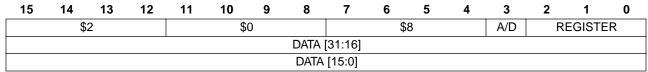

| 7.3.3.4.2 Write A/D Register (WAREG/WDREG)                              |  |

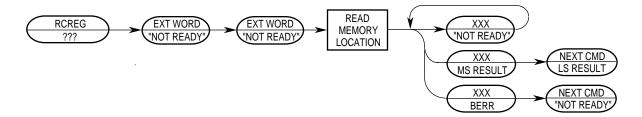

| 7.3.3.4.3 Read Memory Location (READ)                                   |  |

| 7.3.3.4.4 Write Memory Location (WRITE)                                 |  |

| 7.3.3.4.5 Dump Memory Block (DUMP)                                      |  |

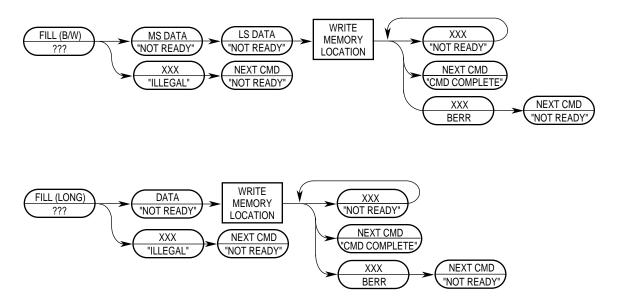

| 7.3.3.4.6 Fill Memory Block (FILL)                                      |  |

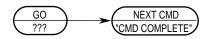

| 7.3.3.4.7 Resume Execution (GO)                                         |  |

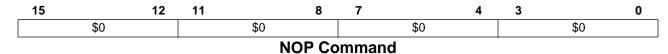

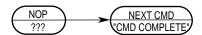

| 7.3.3.4.8 No Operation (NOP)                                            |  |

| 7.3.3.4.9 Read Control Register (RCREG)                                 |  |

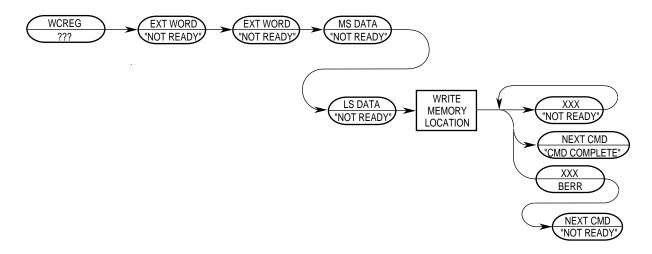

| 7.3.3.4.10 Write Control Register (WCREG)                               |  |

| 7.3.3.4.11 Read Debug Module Register (RDMREG)                          |  |

| 7.3.3.4.12 Write Debug Module Register (WDMREG)                         |  |

| 7.3.3.4.13                                                              |  |

| 7.4 Real-Time Debug Support                                             |  |

| 7.4.1 Theory of Operation                                               |  |

| Paragrap<br>Number | h<br>Title                                             | Page<br>Numbei |

|--------------------|--------------------------------------------------------|----------------|

| 7.4.1.1            | Emulator Mode                                          | 7-27           |

| 7.4.1.2            | Reuse of Debug Module Hardware                         | 7-28           |

| 7.4.2              | Programming Model                                      |                |

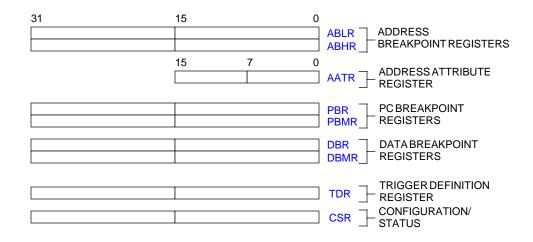

| 7.4.2.1            | Address Breakpoint Registers (ABLR, ABHR)              |                |

| 7.4.2.2            | Address Attribute Register (AATR)                      |                |

| 7.4.2.3            | Program Counter Breakpoint Register (PBR, PBMR)        |                |

| 7.4.2.4            | Data Breakpoint Register (DBR, DBMR)                   |                |

| 7.4.2.5            | Trigger Definition Register (TDR)                      |                |

| 7.4.2.6            | Configuration/Status Register (CSR)                    |                |

| 7.4.3              | Concurrent BDM and Processor Operation                 |                |

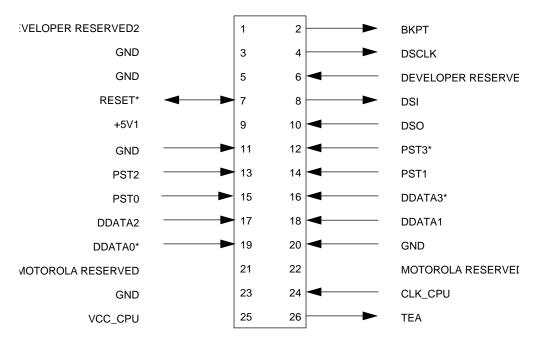

| 7.4.4              | Motorola Recommended BDM Pinout                        |                |

| 7.4.5              | Differences Between the ColdFire2/2M BDM and CPU32 BDM |                |

|                    | Section 8                                              |                |

|                    | Test Operation                                         |                |

| 8.1                | Integrated Memory Testing                              | 8-1            |

| 8.1.1              | Test Bus Signal Description                            | 8-1            |

| 8.1.1.1            | Test Address Bus (TEST_ADDR[14:2])                     |                |

| 8.1.1.2            | Test Control (TEST_CTRL)                               | 8-1            |

| 8.1.1.3            | Test IDATA Read (TEST_IDATA_RD)                        | 8-1            |

| 8.1.1.4            | Test IDATA Write (TEST_IDATA_WRT)                      | 8-2            |

| 8.1.1.5            | Test Instruction Cache Read Hit (TEST_RHIT)            |                |

| 8.1.1.6            | Test Invalidate Inhibit (TEST_IVLD_INH)                | 8-2            |

| 8.1.1.7            | Test ITAG Write (TEST_ITAG_WRT)                        |                |

| 8.1.1.8            | Test KTA Mode Enable (TEST_KTA)                        |                |

| 8.1.1.9            | Test Mode Enable (TEST_MODE)                           |                |

| 8.1.1.10           | Test SRAM Read (TEST_SRAM_RD)                          |                |

| 8.1.1.11           | Test SRAM Write (TEST_SRAM_WRT)                        | 8-2            |

| 8.1.1.12           | Test Read (TEST_RD)                                    | 8-2            |

| 8.1.1.13           | Test ROM Read (TEST_ROM_RD)                            | 8-2            |

| 8.1.1.14           | Test Write Inhibit (TEST_WR_INH)                       |                |

| 8.1.2              | Theory of Operation                                    |                |

| 8.1.3              | Test Mode                                              |                |

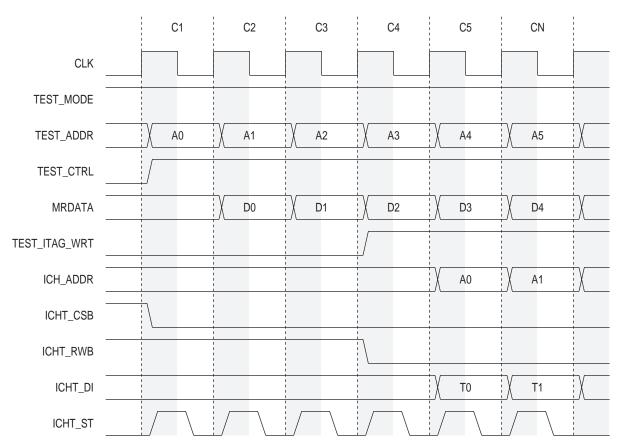

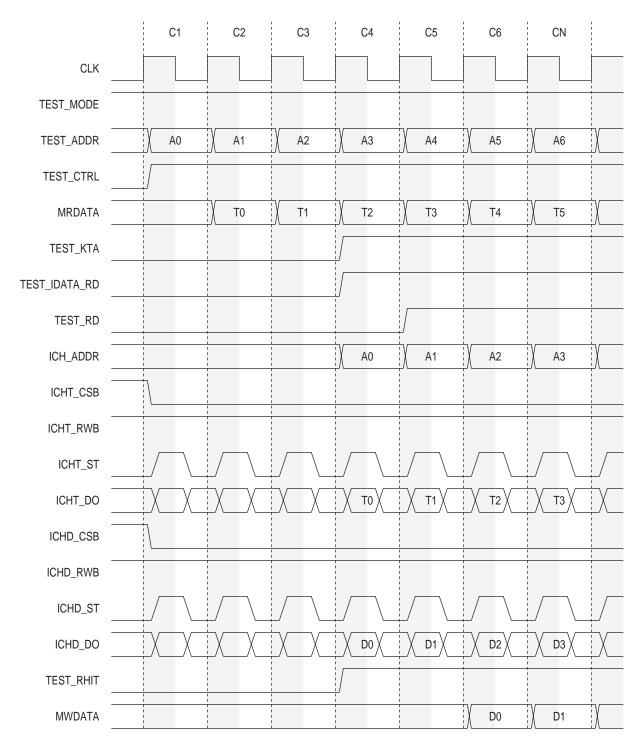

| 8.1.4              | Instruction Cache Tag RAM Testing                      | 8-3            |

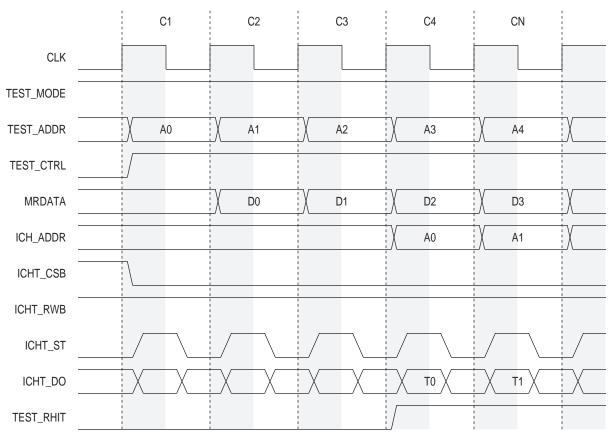

| 8.1.4.1            | Instruction Cache Tag RAM Write Function               |                |

| 8.1.4.2            | Instruction Cache Tag RAM Read Function                |                |

| 8.1.5              | Instruction Cache Data RAM Testing                     |                |

| 8.1.5.1            | Instruction Cache Data RAM Write Function              |                |

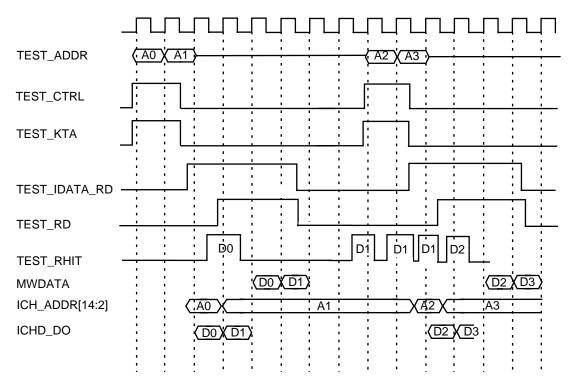

| 8.1.5.2            | Instruction Cache Data RAM Read Function               |                |

| 8.1.6              | Instruction Cache KTA Mode Testing                     |                |

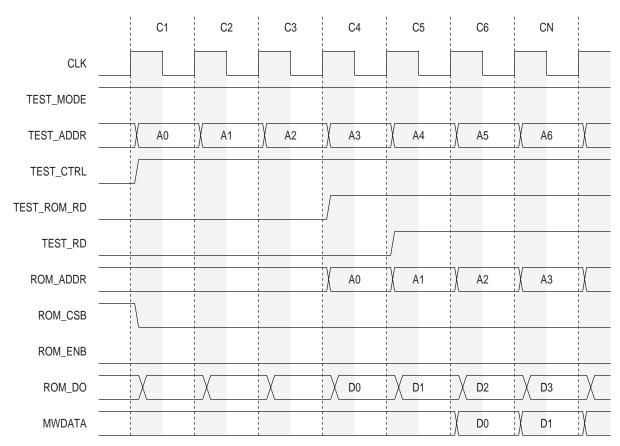

| 8.1.7              | ROM Testing                                            |                |

| Paragrap<br>Number | h<br>Title                                       | Page<br>Number |

|--------------------|--------------------------------------------------|----------------|

| 8.1.7.1            | ROM Read Function                                | 8-11           |

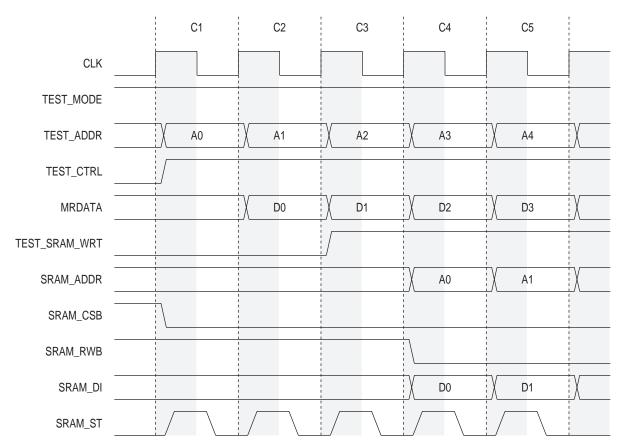

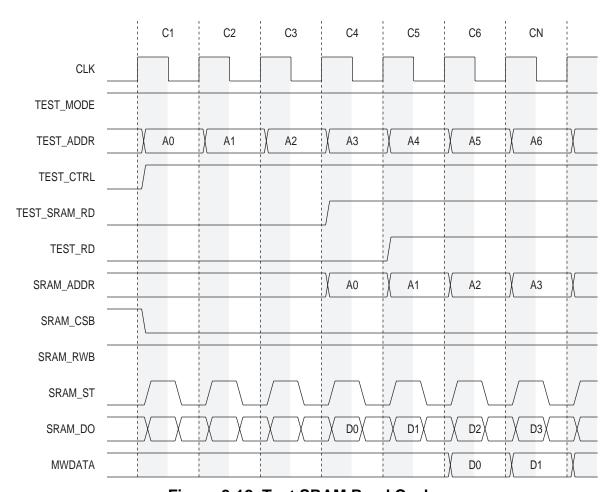

| 8.1.8              | SRAM Testing                                     | 8-13           |

| 8.1.8.1            | SRAM Write Function                              | 8-13           |

| 8.1.8.2            | SRAM Read Function                               | 8-15           |

| 8.2                | Scan Testing                                     | 8-16           |

| 8.2.1              | Scan Signal Description                          |                |

| 8.2.1.1            | Scan Enable (SCAN_ENABLE)                        | 8-16           |

| 8.2.1.2            | Scan Exercise Array (SCAN_XARRAY)                | 8-16           |

| 8.2.1.3            | Scan Input (SCAN_IN[15:0])                       | 8-16           |

| 8.2.1.4            | Scan Mode (SCAN_MODE)                            | 8-17           |

| 8.2.1.5            | Scan Output (SCAN_OUT[15:0])                     | 8-17           |

| 8.2.1.6            | Scan Test Ring Clock (TR_CLK)                    |                |

| 8.2.1.7            | Scan Test Ring Core Mode Enable (TR_CORE_EN)     | 8-17           |

| 8.2.1.8            | Scan Test Ring Data Input 0 (TR_DI0)             | 8-17           |

| 8.2.1.9            | Scan Test Ring Data Input 1 (TR_DI1)             |                |

| 8.2.1.10           | Scan Test Ring Data Output 0 (TR_DO0)            | 8-17           |

| 8.2.1.11           | Scan Test Ring Data Output 1 (TR_DO1)            | 8-17           |

| 8.2.1.12           | Scan Test Ring Enable (TR_EN)                    |                |

| 8.2.1.13           | Scan Test Ring Mode (TR_MODE)                    | 8-17           |

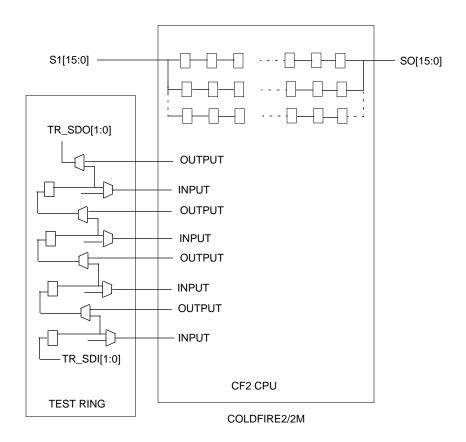

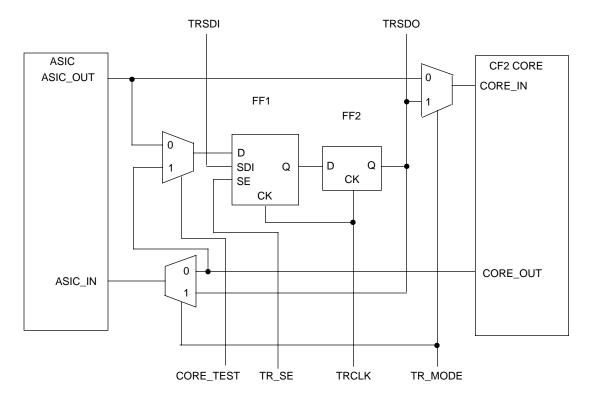

| 8.2.2              | Test Ring                                        |                |

| 8.3                | Burn-In Testing                                  |                |

| 8.4                | Data Retention Testing                           | 8-18           |

|                    | Section 9 Instruction Execution Timing           |                |

| 9.1                | Timing Assumptions                               | 9-1            |

| 9.2                | MOVE Instruction Execution Times                 |                |

| 9.3                | Standard One-Operand Instruction Execution Times |                |

| 9.4                | Standard Two-Operand Instruction Execution Times |                |

| 9.5                | Miscellaneous Instruction Execution Times        |                |

| 9.6                | MAC Instruction Execution Timing                 |                |

| 9.7                | Branch Instruction Execution Times               |                |

|                    | Section 10                                       |                |

|                    | Electrical Chacteristics                         |                |

| 10.1               | Definitions of Specifications                    |                |

| 10.1.1             | Current                                          |                |

| 10.1.2             | Voltage                                          |                |

| 10.1.3             | Capacitance                                      |                |

| 10.1.4             | AC Switching Parameters and Waveforms            | 10-2           |

| Paragra<br>Numb | •                                                            | Page<br>Number |

|-----------------|--------------------------------------------------------------|----------------|

| 10.2            | ColdFire2 Data Sheet                                         | 10-6           |

|                 | Appendix A<br>Register Summary                               |                |

| A.1<br>A.2      | Register Access MethodsRegister Formats                      | A-1<br>A-2     |

|                 | Appendix B New MAC Instructions                              |                |

| B.1<br>B.2      | Enhanced Integer Multiply Instructions  New MAC Instructions | B-1            |

| B.3             | New Register Instructions                                    |                |

| B.4             | Operation Code Map                                           | B-22           |

## LIST OF ILLUSTRATIONS

| Figu<br>Num |                                                           | Page<br>Numbe |

|-------------|-----------------------------------------------------------|---------------|

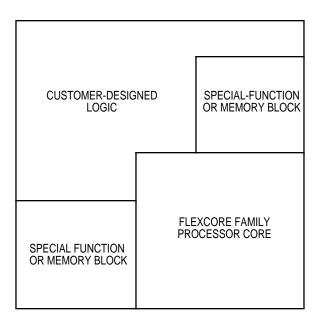

| 1-1         | FlexCore Integrated Processor Typical Die Layout          | 1-3           |

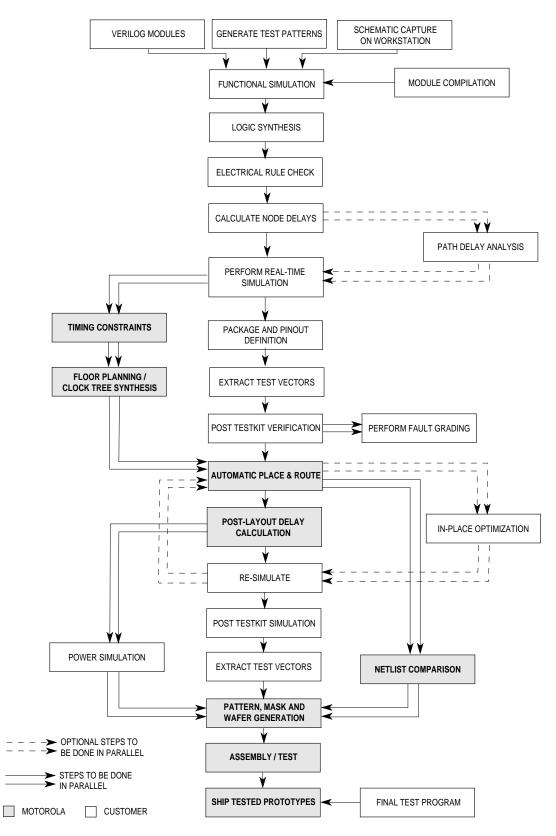

| 1-2         | Design System Overview                                    | 1-7           |

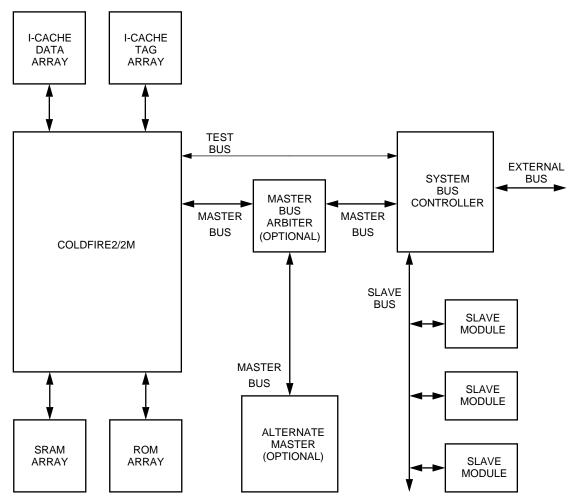

| 1-3         | ColdFire2/2M System Diagram                               | 1-8           |

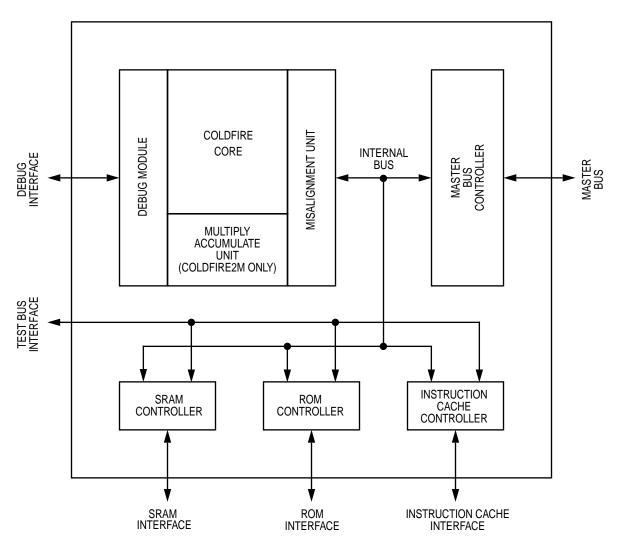

| 1-4         | ColdFire2/2M Block Diagram                                | 1-10          |

| 1-5         | Integer Unit User Programming Model                       | 1-12          |

| 1-6         | Condition Code Register (CCR)                             | 1-13          |

| 1-7         | MAC Unit User Programming Model                           | 1-13          |

| 1-8         | Supervisor Programming Model                              | 1-14          |

| 1-9         | Status Register (SR)                                      | 1-15          |

| 1-10        | Organization of Integer Data Formats in Data Registers    | 1-16          |

| 1-11        | Organization of Integer Data Formats in Address Registers |               |

| 1-12        | Memory Operand Addressing                                 | 1-18          |

| 2-1         | ColdFire2/2M Detailed Block Diagram                       |               |

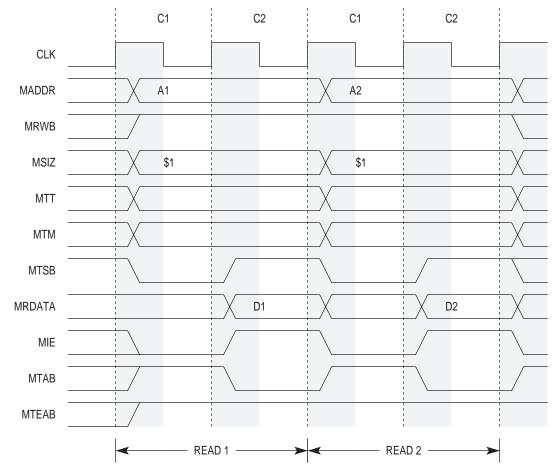

| 3-1         | Byte, Word, and Longword Read Transfer Flowchart          | 3-7           |

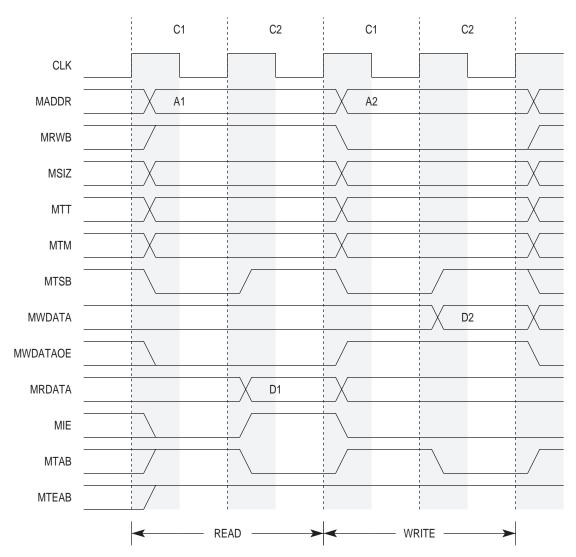

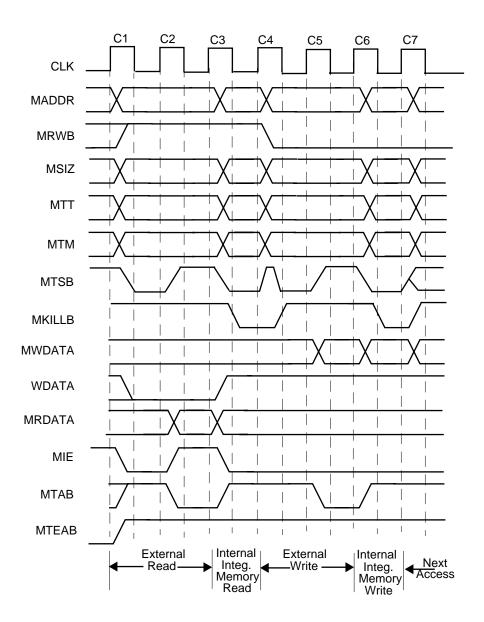

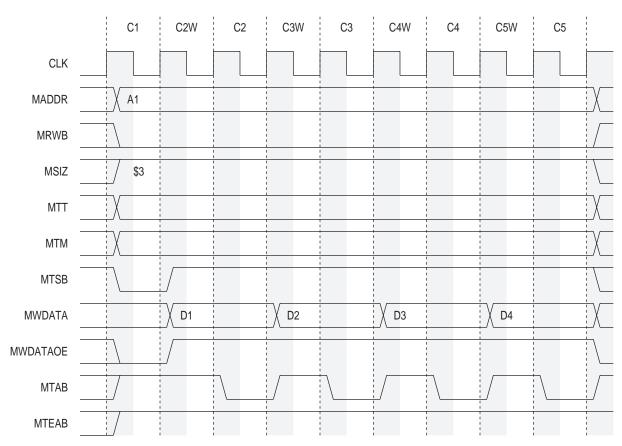

| 3-2         | Normal Transfer (without Wait States)                     | 3-8           |

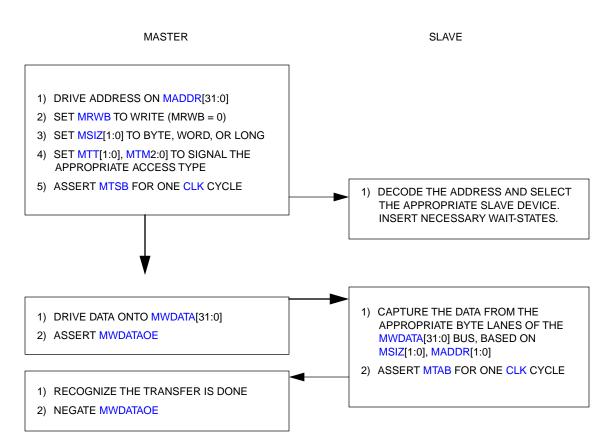

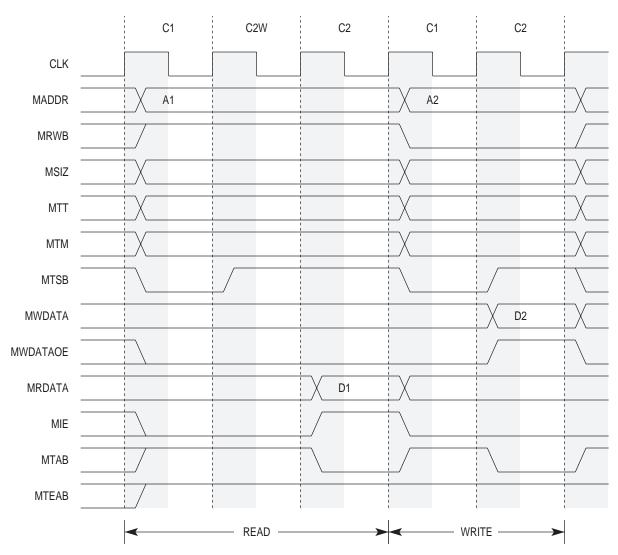

| 3-3         | Byte, Word, and Longword Write Transfer Flowchart         |               |

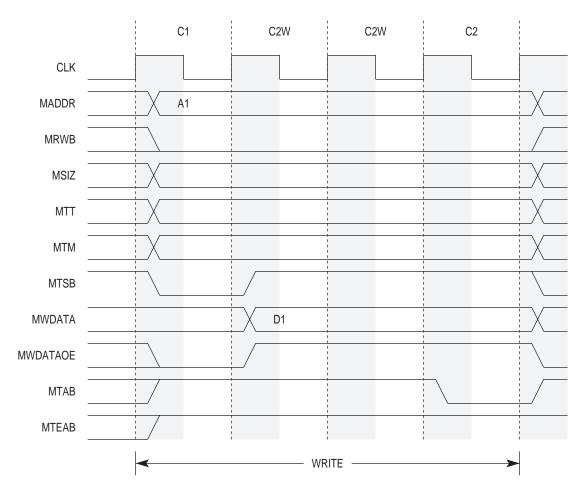

| 3-4         | Normal Write Transfer (with wait states)                  |               |

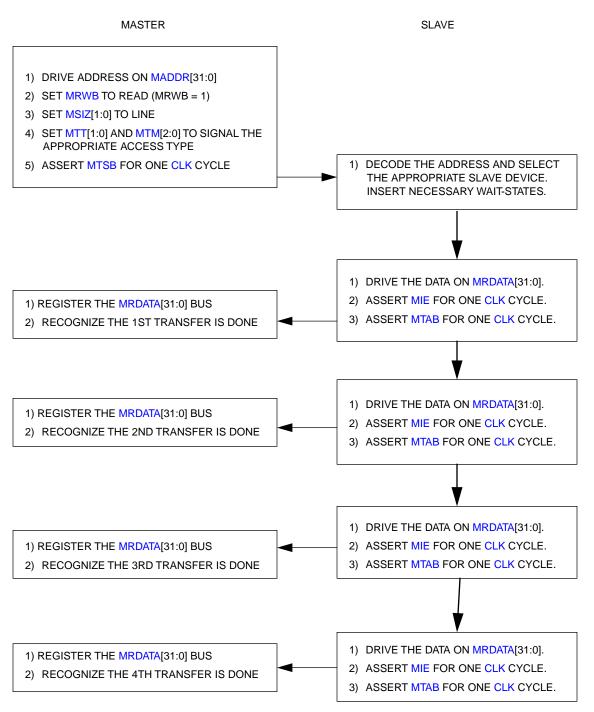

| 3-5         | Line Read Transfer Flowchart                              |               |

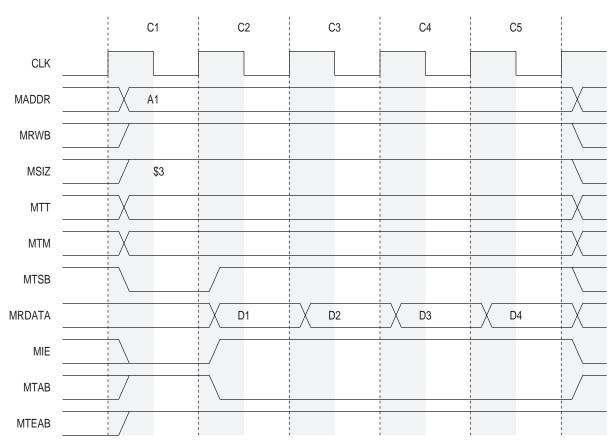

| 3-6         | Line Read Transfer (without wait states)                  |               |

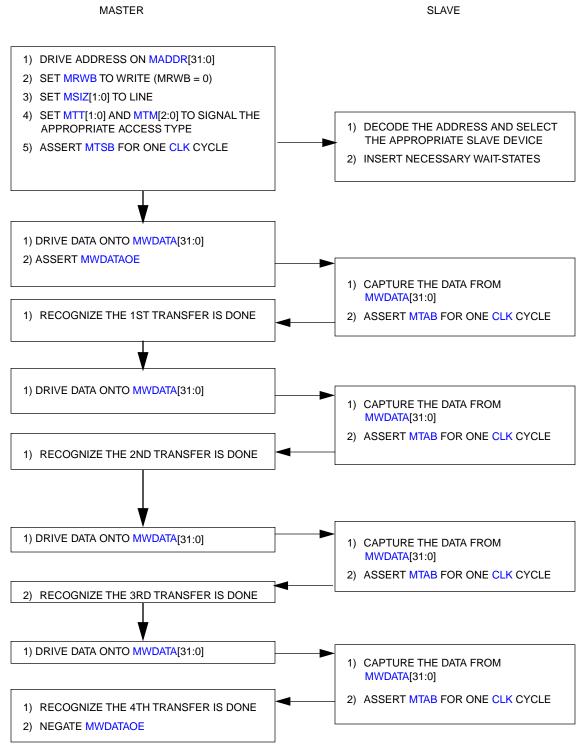

| 3-7         | Line Write Transfer Flowchart                             |               |

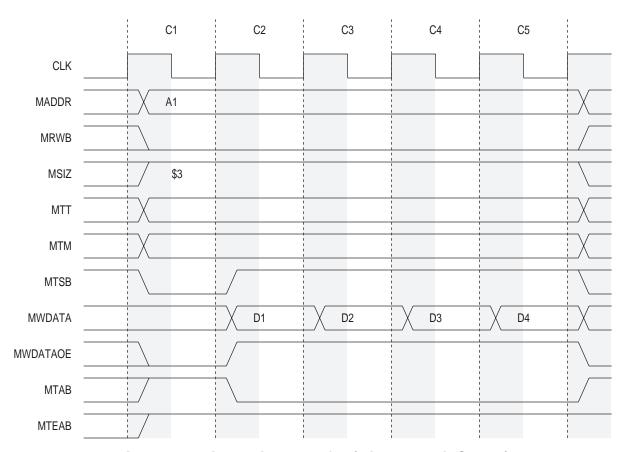

| 3-8         | Line Write Transfer (without wait states)                 |               |

| 3-9         | Line Write Transfer (with wait states)                    |               |

| 3-10        | Example of a Misaligned Longword Transfer                 |               |

| 3-11        | Example of a Misaligned Word Transfer                     |               |

| 3-12        | Misaligned Word Read Transfer                             |               |

| 3-13        | Example Master Bus Wait State                             |               |

| 3-14        | Interrupt Acknowledge Bus Cycle Flowchart                 |               |

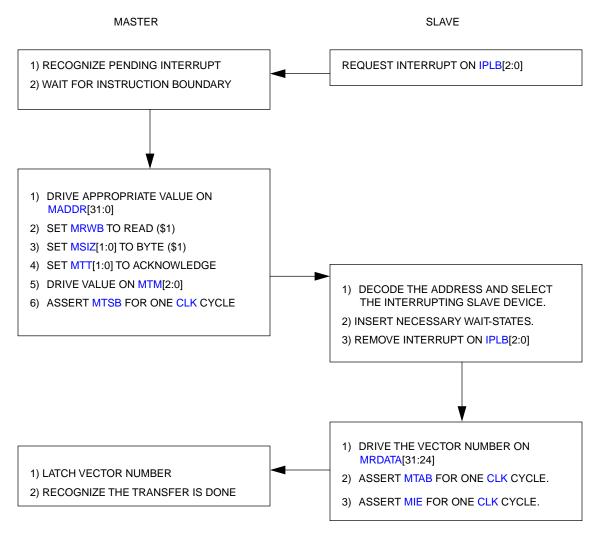

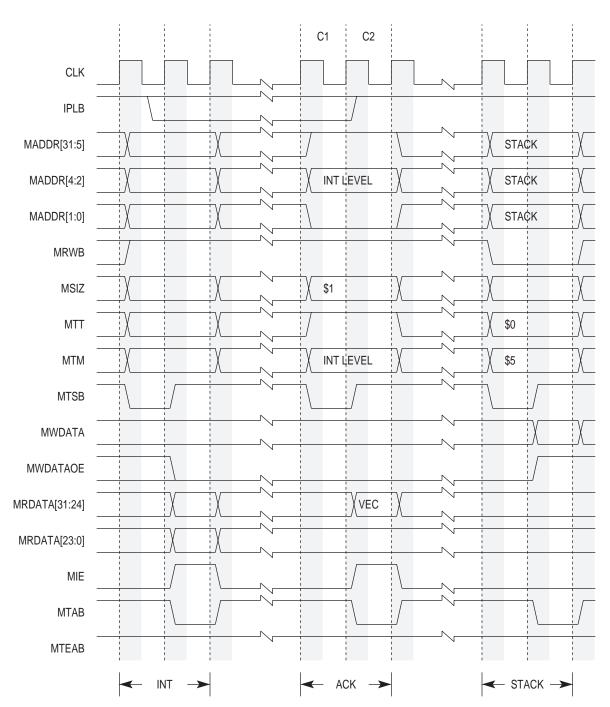

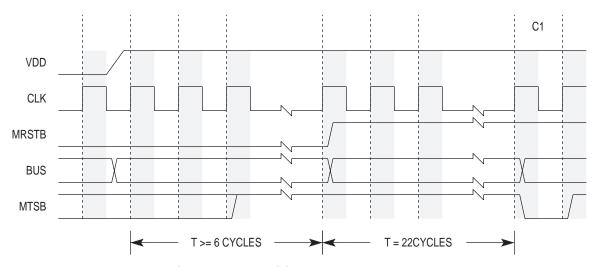

| 3-15        | ColdFire Mode Interrupt Acknowledge Bus Cycle             |               |

| 3-16        | 68K Mode Interrupt Acknowledge Bus Cycle                  |               |

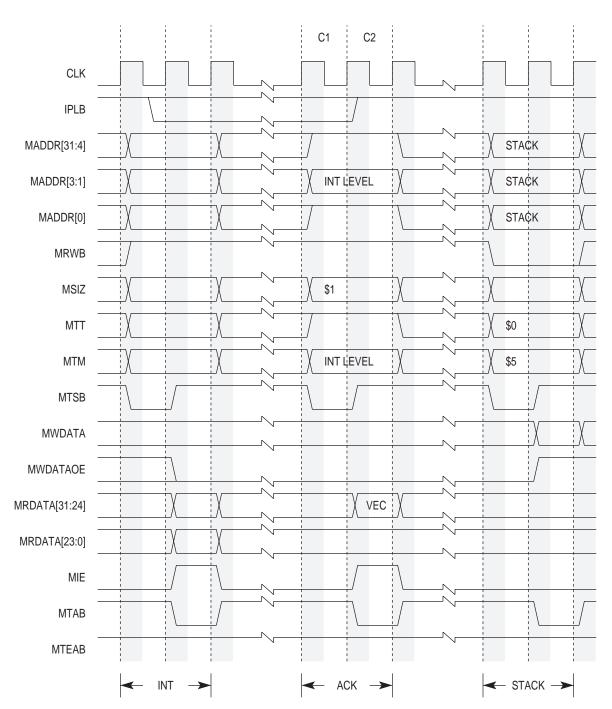

| 3-17        | Bus Exception Cycle                                       |               |

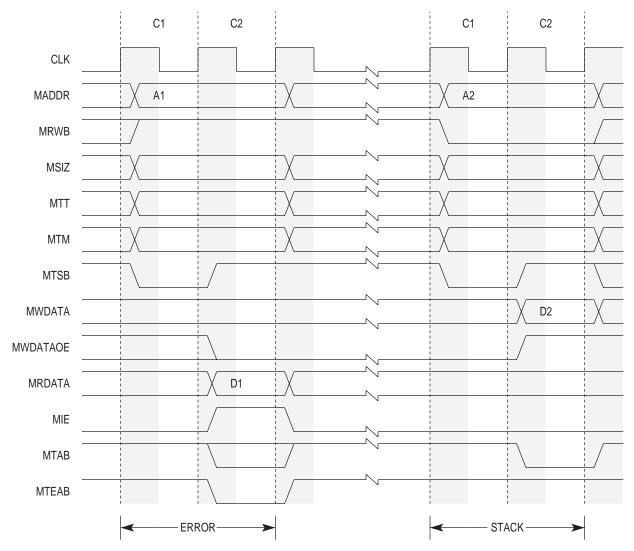

| 3-18        | Initial Power-On Reset                                    |               |

| 4-1         | Exception Processing Flowchart                            |               |

| 4-2         | Exception Stack Frame Form                                |               |

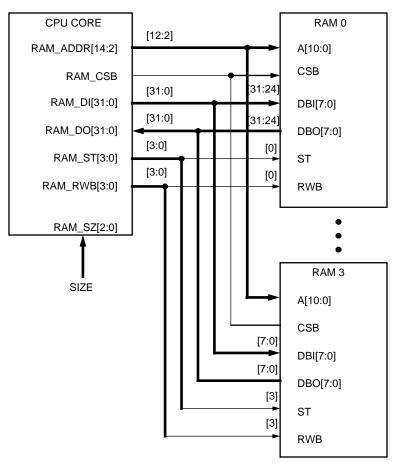

| 5-1         | Example 8 Kbyte Instruction Cache Interface Diagram       |               |

| 5-2         | Cache Control Register (CACR)                             | 5-6           |

| 5-3         | Access Control Register (ACR0, ACR1)                      |               |

| 5-4         | Example 8 Kbyte ROM Interface Diagram                     |               |

| 5-5         | ROM Base Address Register (ROMBAR0)                       | 5-12          |

# **LIST OF ILLUSTRATIONS (Continued)**

| Figu |                                                                                   | Page   |

|------|-----------------------------------------------------------------------------------|--------|

| Numk | per Title                                                                         | Number |

| 5-6  | Example 8 Kbyte SRAM Interface Diagram                                            | 5-15   |

| 5-7  | SRAM Base Address Register (RAMBAR0)                                              | 5-17   |

| 6-1  | MAC Flow Diagram                                                                  |        |

| 6-2  | MAC Status Register (MACSR)                                                       | 6-3    |

| 6-3  | MAC Mask Register (MASK)                                                          | 6-4    |

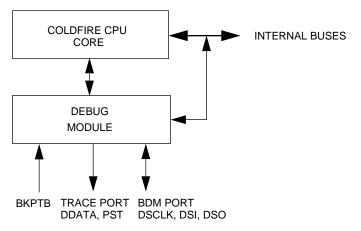

| 7-1  | Processor/Debug Module Interface                                                  | 7-1    |

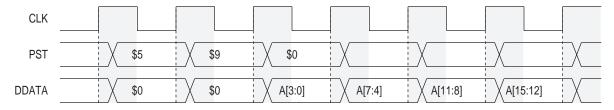

| 7-2  | Example PST Diagram                                                               | 7-4    |

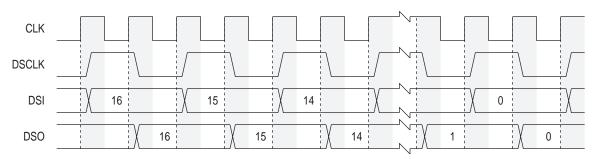

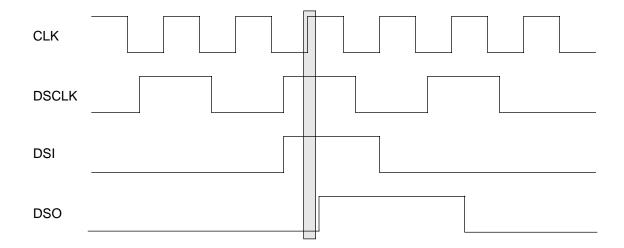

| 7-3  | BDM Serial Transfer                                                               | 7-8    |

| 7-4  | BDM Signal Sampling                                                               | 7-8    |

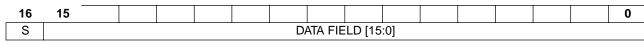

| 7-5  | Receive BDM Packet                                                                | 7-8    |

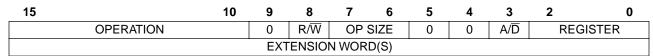

| 7-6  | Transmit BDM Packet                                                               | 7-9    |

| 7-7  | Command Sequence Diagram                                                          | 7-12   |

| 7-8  | Debug Programming Model                                                           |        |

| 7-9  | Address Breakpoint Low Register (ABLR)                                            | 7-29   |

| 7-10 | Address Breakpoint High Register (ABHR)                                           | 7-30   |

| 7-11 | Address Attribute Register (AATR)                                                 | 7-30   |

| 7-12 | Program Counter Breakpoint Register (PBR)                                         | 7-32   |

| 7-13 | Program Counter Breakpoint Mask Register (PBMR)                                   | 7-33   |

| 7-14 | Data Breakpoint Register (DBR)                                                    | 7-33   |

| 7-15 | Data Breakpoint Mask Register (DBMR)                                              | 7-33   |

| 7-16 | Trigger Definition Register (TDR)                                                 |        |

| 7-17 | Configuration/Status Register (CSR)                                               | 7-37   |

| 7-18 | Recommended BDM Connector                                                         | 7-40   |

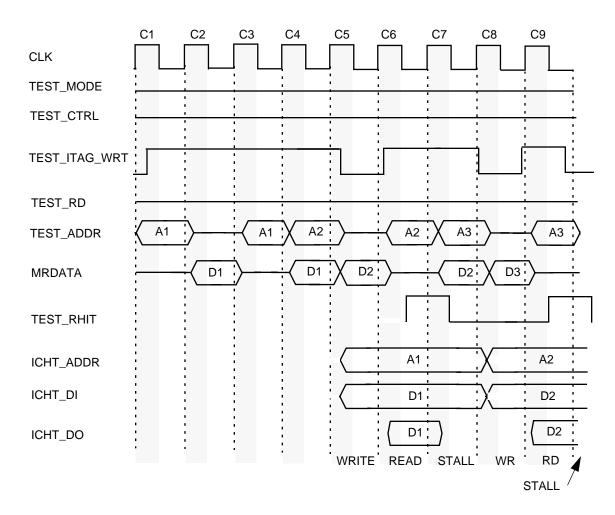

| 8-1  | Test Instruction Cache Tag Write Cycles                                           | 8-4    |

| 8-2  | Test Instruction Cache Tag Read Cycles                                            | 8-5    |

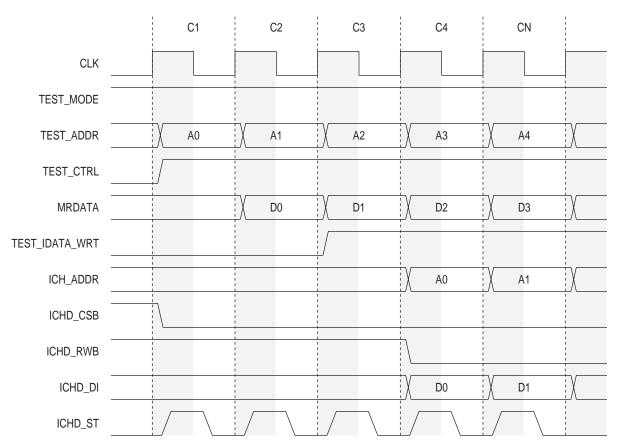

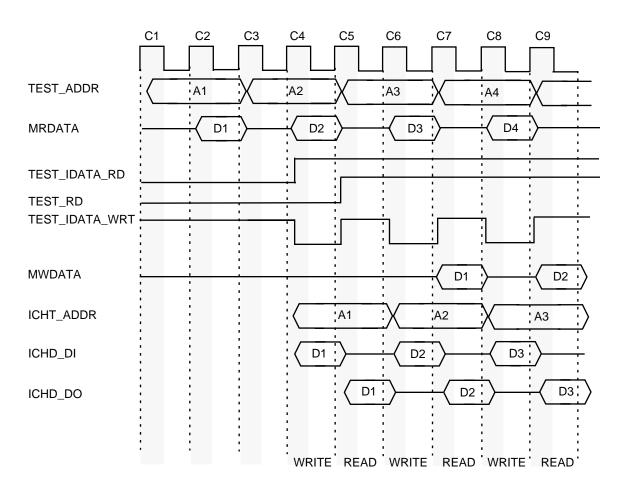

| 8-3  | Test Instruction Cache Data Write Cycles                                          | 8-7    |

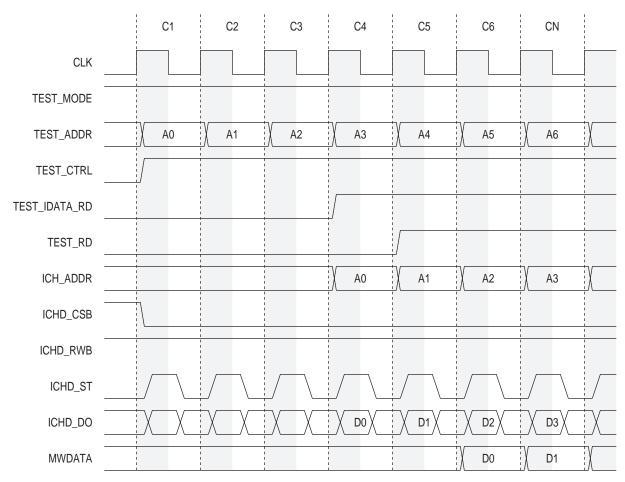

| 8-4  | Test Instruction Cache Data Read Cycles                                           | 8-8    |

| 8-5  | KTA Mode Cycles                                                                   | 8-10   |

| 8-6  | Test ROM Read Cycles                                                              | 8-12   |

| 8-7  | Test SRAM Write Cycles                                                            | 8-14   |

| 8-8  | Test SRAM Read Cycles                                                             | 8-15   |

| 10-1 | t <sub>PLH</sub> and t <sub>PHL</sub> Measurements                                |        |

| 10-2 | t <sub>r</sub> and t <sub>f</sub> Measurements                                    | 10-2   |

| 10-3 | Internal Cell Three-State Measurements and Example Circuits                       | 10-3   |

| 10-4 | t <sub>rec</sub> Recovery Time                                                    | 10-4   |

| 10-5 | t <sub>su</sub> and t <sub>h</sub> Measurements Between Data and a Control Signal | 10-4   |

| 10-6 | t <sub>su</sub> and t <sub>h</sub> Measurements Between Data and Clock Signals    |        |

| 10-7 | Switching Waveforms Showing t <sub>w(L)</sub> and t <sub>w(H)</sub> Measurements  |        |

| A-1  | Address Attribute Register (AATR)                                                 | A-2    |

| A-2  | Address Breakpoint High Register (ABHR)                                           |        |

| A-3  | Address Breakpoint Low Register (ABLR)                                            |        |

| A-4  | Access Control Register (ACR0, ACR1)                                              |        |

# **LIST OF ILLUSTRATIONS (Continued)**

| Figu<br>Numb |                                                 | Page<br>Number |

|--------------|-------------------------------------------------|----------------|

| A-5          | Cache Control Register (CACR)                   | A-3            |

| A-6          | Condition Code Register (CCR)                   | A-3            |

| A-7          | Configuration/Status Register (CSR)             |                |

| 1-8          | Data Breakpoint Mask Register (DBMR)            |                |

| 1-9          | Data Breakpoint Register (DBR)                  | A-4            |

| 1-10         | MAC Status Register (MACSR)                     |                |

| 1-11         | MAC Mask Register (MASK)                        |                |

| 1-12         | Program Counter Breakpoint Mask Register (PBMR) |                |

| 1-13         | Program Counter Breakpoint Register (PBR)       | A-5            |

| A-14         | SRAM Base Address Register (RAMBAR0)            | A-5            |

| A-15         | ROM Base Address Register (ROMBAR0)             |                |

| A-16         | Status Register (SR)                            |                |

| A-17         | Trigger Definition Register (TDR)               |                |

## **LIST OF TABLES**

| Tabl<br>Numl |                                             | Page<br>Number |

|--------------|---------------------------------------------|----------------|

| 1-1          | MOVEC Register Map                          | 1-14           |

| 1-2          | Integer Data Formats                        |                |

| 1-3          | Effective Addressing Modes and Categories   | 1-19           |

| 1-4          | Notational Conventions                      | 1-19           |

| 1-5          | Instruction Set Summary                     | 1-21           |

| 2-1          | Signal Summary                              | 2-2            |

| 2-2          | Master Arbiter Control Encoding             | 2-4            |

| 2-3          | Master Bus Transfer Size Encoding           | 2-5            |

| 2-4          | Master Bus Transfer Modifier Encoding       | 2-5            |

| 2-5          | Master Bus Transfer Type Encoding           | 2-6            |

| 2-6          | Interrupt Levels and Mask Values            |                |

| 2-7          | Cache Configuration Encoding                |                |

| 2-8          | Valid Tag RAM Data Signals                  |                |

| 2-9          | Valid ROM Address Bits                      |                |

| 2-10         | ROM Configuration Encoding                  |                |

| 2-11         | Valid SRAM Address Bits                     |                |

| 2-12         | SRAM Configuration Encoding                 |                |

| 2-13         | Processor Status Encoding                   |                |

| 3-1          | Master Arbiter Control Encoding             |                |

| 3-2          | Master Bus Transfer Size Encoding           |                |

| 3-3          | Master Bus Transfer Modifier Encoding       |                |

| 3-4          | Master Bus Transfer Type Encoding           |                |

| 3-5          | MRDATA Requirements for Read Transfers      |                |

| 3-6          | MWDATA Bus Requirements for Write Transfers |                |

| 3-7          | Allowable Line Access Patterns              |                |

| 3-8          | Memory Alignment Cycles                     |                |

| 3-9          | MTAB and MTEAB Assertion Results            |                |

| 4-1          | Stack Pointer Alignment                     |                |

| 4-2          | Exception Vector Assignments                | 4-5            |

| 4-3          | Exception Priority Groups                   |                |

| 4-4          | Interrupt Levels and Mask Values            |                |

| 5-1          | Cache Configuration Encoding                |                |

| 5-2          | Valid Tag RAM Data Signals                  |                |

| 5-3          | Initial Fetch Offset and CLNF Bits          |                |

| 5-4          | Cache Line Fill Encoding                    |                |

| 5-5          | Valid ROM Address Bits                      |                |

| 5-6          | ROM Configuration Encoding                  |                |

| 5-7          | Valid ROM Base Address Bits                 | 5-13           |

# **LIST OF TABLES (Continued)**

| Figui<br>Numb |                                            | Page<br>Number |

|---------------|--------------------------------------------|----------------|

| 5-8           | Valid SRAM Address Bits                    | 5-15           |

| 5-9           | SRAM Configuration Encoding                | 5-16           |

| 5-10          | Valid SRAM Base Address Bits               | 5-17           |

| 6-1           | Mask Addressing Mode                       |                |

| 6-2           | Accumulator Result in Saturation Mode      | 6-5            |

| 6-3           | MAC Instruction Set Summary                | 6-6            |

| 7-1           | Processor Status Encoding                  | 7-2            |

| 7-2           | CPU-Generated Message Encoding             | 7-9            |

| 7-3           | BDM Command Summary                        | 7-10           |

| 7-4           | BDM Size Field Encoding                    | 7-11           |

| 7-5           | Control Register Map                       |                |

| 7-6           | Definition of DRc Encoding - Read          | 7-24           |

| 7-7           | Definition of DRc Encoding - Write         | 7-25           |

| 7-8           | DDATA, CSR[31:28] Breakpoint Response      | 7-26           |

| 7-9           | Shared BDM/Breakpoint Hardware             | 7-28           |

| 7-10          | Misaligned Data Operand References         |                |

| 7-11          | BDM Connector Correlation                  | 7-40           |

| 9-1           | Misaligned Operand References              |                |

| 9-2           | Move Byte and Word Execution Times         | 9-3            |

| 9-3           | Move Long Execution Times                  |                |

| 9-4           | One Operand Instruction Execution Times    |                |

| 9-5           | Two Operand Instruction Execution Times    |                |

| 9-6           | Miscellaneous Instruction Execution Times  |                |

| 9-7           | MAC Instruction Execution Times            | 9-8            |

| 9-8           | General Branch Instruction Execution Times | 9-8            |

| 9-9           | BRA, BCC Instruction Execution Times       | 9-8            |

| A-1           | Register Summary                           | Α-1            |

## **LIST OF ACRONYMS**

| Acronym | Definition                         |

|---------|------------------------------------|

| BCD     | . binary coded decimal             |

| BDM     | . background debug mode            |

| CAD     | . computer-aided design            |

| CPU     | . central processing unit          |

| DSP     | . digital signal processing        |

| ET      | . execution time                   |

| IACK    | . interrupt acknowledge            |

| IFP     | instruction fetch pipeline         |

| LRU     | . least recently used              |

| LSB     | . least significant bit            |

| LSW     | . least significant word           |

| MAC     | . multiply-accumulate              |

| MARB    | . master bus arbiter               |

| MSB     | . most significant bit             |

| MSW     | . most significant word            |

| OEP     | . operand execution pipeline       |

| RISC    | . reduced instruction set computer |

| ROM     | . read-only memory                 |

| SBC     | . system bus controller            |

| SRAM    | . static random access memory      |

| TA      | .transfer acknowledge              |

| TS      | . transfer start                   |

## SECTION 1 OVERVIEW

This is a summary of the use and operation of the FlexCore ColdFire® microprocessor core (referred to as the ColdFire2) and FlexCore ColdFire microprocessor core with the Multiply-Accumulate unit (MAC), referred to as the ColdFire2M. It also contains a detailed set of timing and electrical specifications. All references to ColdFire2/2M will apply to both the ColdFire2 and the ColdFire2M devices. Refer to the *ColdFire Programmer's Reference Manual Rev 1.0* (MCF5200PRM/AD) for detailed information on the operation of the instruction set and addressing modes.

The ColdFire2/2M is part of the FlexCore Program, a semicustom, standard-cell based design program. Based on the concept of variable-length Reduced Instruction Set Computer (RISC) technology, ColdFire combines the architectural simplicity of conventional 32-bit RISC with a memory-saving, variable-length instruction set. In the FlexCore program, high-volume manufacturers can create their own integrated microprocessor containing a core processor (such as the ColdFire2/2M) and their own proprietary technology. A FlexCore integrated processor allows significant reductions in component count, power consumption, board space, and cost—resulting in higher system reliability and performance.

The main features of the ColdFire2/2M processor include:

- 32-bit address bus which can directly address up to 4 Gbytes

- 32-bit data bus

- Variable-length RISC

- Optimized instruction set for high-level language constructs

- Sixteen general-purpose 32-bit data- and address- registers

- Multiply Accumulate (MAC) unit for DSP applications (ColdFire2M only)

- Supervisor/user modes for system protection

- Vector-base register to relocate exception-vector table

- Special core interfacing signals for integrated memories

- Full debug support

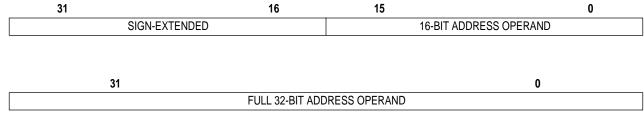

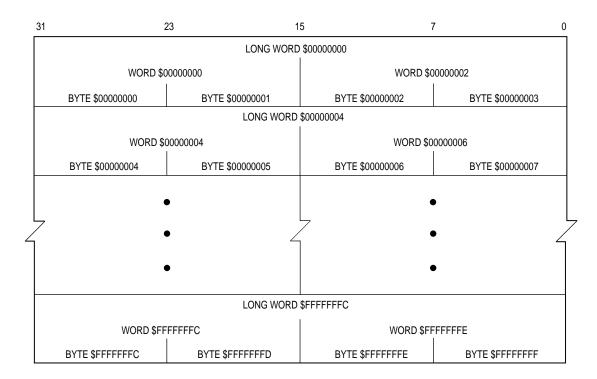

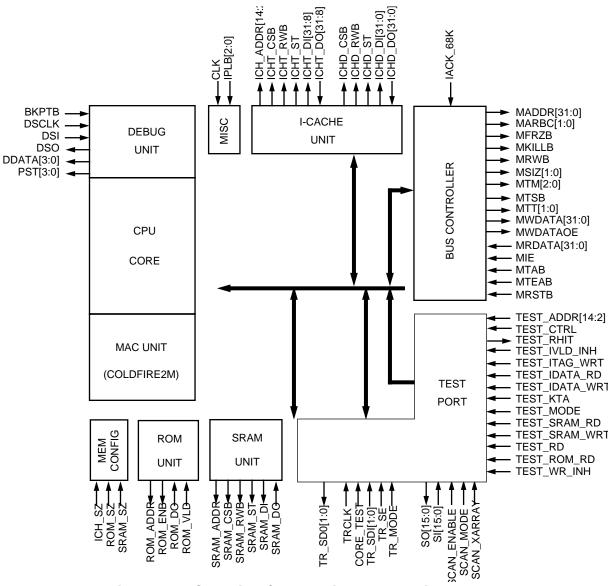

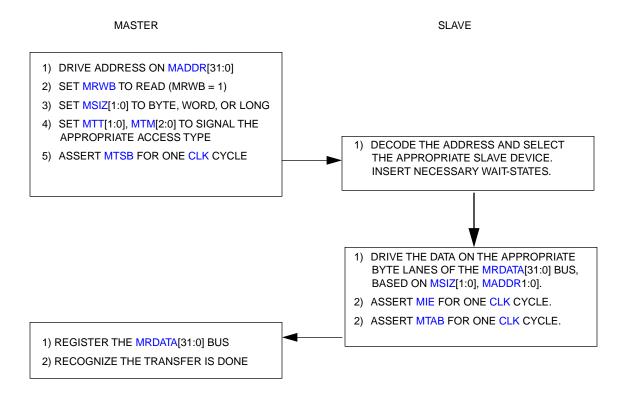

The ColdFire2/2M has 32-bit address and data busses. The 32-bit address bus allows direct addressing of up to 4 Gbytes. A misalignment unit provides support for misaligned data accesses, and an optional bus arbitration unit provides support for additional bus masters. The ColdFire2/2M also supports an integrated instruction cache, SRAM, and ROM (maximum of 32 Kbyte each.)