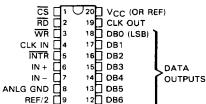

DGTL GND 110

11 DB7 (MSB)

- 8-Bit Resolution

- Ratiometric Conversion

- 100 μs Conversion Time

- 135 ns Access Time

- Guaranteed Monotonicity

- High Reference Ladder Impedance

8 kΩ Typical

- No Zero Adjust Requirement

- On-Chip Clock Generator

- Single 5-Volt Power Supply

- Operates With Microprocessor or as Stand-Alone

- Designed to be Interchangeable with National Semiconductor ADC0801, ADC0802, ADC0803, ADC0805

# description

The ADC0801, ADC0802, ADC0803, and ADC0805 are CMOS 8-bit successive-approximation analog-to-digital converters that use a modified potentiometric (256R) ladder. These devices are designed to operate from common microprocessor control buses, with the three-state output latches driving the data bus. The devices can be made to appear to the microprocessor as a memory location or an I/O port.

A differential analog voltage input allows increased common-mode rejection and offset of the zero-input analog voltage value. Although a reference input (REF/2) is available to allow 8-bit conversion over smaller analog voltage spans or to make use of an external reference, ratiometric conversion is possible with the REF/2 input open. Without an external reference, the conversion takes place over a span from VCC to analog ground (ANLG GND). The devices can operate with an external clock signal or, with an additional resistor and capacitor, can operate using an on-chip clock generator.

The ADC08011, ADC08021, ADC08031, and ADC08051 will be characterized for operation from -40 °C to 85 °C.

Data Acquisition

7

1183

Texas Instruments 1183

POST DEFICE BOX 225012 . DALLAS, TEXAS 75265

# TYPES ADC0801, ADC0802, ADC0803, ADC0805 8-BIT ANALOG-TO-DIGITAL CONVERTERS WITH DIFFERENTIAL INPUTS

| absolute maximum ratings over operating free-air temperature range (unless otherwise noted) |

|---------------------------------------------------------------------------------------------|

| Supply voltage, VCC (see Note 1)                                                            |

| Input voltage range CS, RD, WR0.3 V to 18 V                                                 |

| Other inputs                                                                                |

| Output voltage range                                                                        |

| Continuous total power dissipation at 25 °C free-air temperature (see Note 2)               |

| Operating free-air temperature range                                                        |

| Storage temperature range65°C to 150°C                                                      |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                                |

NOTES: 1. All voltage values are with respect to digital ground (DGTL GND) with DGTL GND and ANLG GND connected together (unless otherwise noted).

2. For operation above 25°C free-air temperature, refer to Dissipation Derating Curves, section 2.

### recommended operating conditions

1183

|                             | MIN                                                                                                                                                        | NOM                  | MAX                    | UNIT                 |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|----------------------|

| 9                           | 4.5                                                                                                                                                        | 5                    | 6.3                    | ٧                    |

| F/2 (see Note 3)            | 0.25                                                                                                                                                       | 2.5                  |                        | ٧                    |

| ut voltage at CS, RD, or WR | 2                                                                                                                                                          |                      | 15                     | >                    |

| t voltage at CS, RD, or WR  |                                                                                                                                                            |                      | 0.8                    | >                    |

| voltage (see Note 4)        | -0.05                                                                                                                                                      | 0                    | 1                      | >                    |

| /oltage (see Note 5)        | GND - 0.05                                                                                                                                                 |                      | V <sub>CC</sub> + 0.05 | ٧                    |

| equency (see Note 6)        | 100                                                                                                                                                        | 640                  | 1460                   | kHz                  |

| ove 640 kHz (see Note 6)    | 40                                                                                                                                                         |                      | 60                     | %                    |

| clock input (high or low)   | 275                                                                                                                                                        | 781                  |                        | ns                   |

| , WR input low              | 100                                                                                                                                                        |                      |                        | ns                   |

| -air temperature            | -40 .                                                                                                                                                      |                      | 85                     | °C                   |

|                             | d voltage (see Note 4)  voltage (see Note 5)  sequency (see Note 6)  ove 640 kHz (see Note 6)  clock input (high or low)  , WR input low  -air temperature | Voltage (see Note 4) | voltage (see Note 4)   | Voltage (see Note 4) |

NOTES: 3. Proper operation is achieved over a differential input range of 0 V to V<sub>CC</sub> when the REF/2 input is open.

4. These values are with respect to digital ground (pin 10).

5. When the positive analog input with respect to the negative analog input (Vin + Vin - 1 is zero or negative, the output code is 0000 0000.

6. Total unadjusted error is guaranteed only at an f<sub>clock</sub> of 640 kHz with a duty cycle of 40% to 60% (pulse duration 625 ns to 937 ns). For frequencies above this limit or pulse duration below 625 ns, error may increase. The duty cycle limits should be observed for an f<sub>clock</sub> greater than 640 kHz. Below 640 kHz, this duty cycle limit can be exceeded provided t<sub>W(CLK)</sub> remains within limits.

| PARAMETER                                               |                                        |              | TEST CONDITIONS                         |                                       | MIN  | TYP <sup>†</sup> | MAX | UNIT |  |

|---------------------------------------------------------|----------------------------------------|--------------|-----------------------------------------|---------------------------------------|------|------------------|-----|------|--|

| Vон                                                     | High-level                             | All outputs  | $V_{CC} = 4.75 \text{ V},$              | I <sub>OH</sub> = -360 μA             | 2.4  |                  |     | v    |  |

|                                                         | output voltage                         | DB and INTR  | $V_{CC} = 4.75 \text{ V},$              | I <sub>OH</sub> = -10 μA              | 4.5  |                  |     | 1 °  |  |

| VOL                                                     | Low-level                              | Data outputs | $V_{CC} = 4.75 \text{ V},$              | I <sub>OL</sub> = 1.6 mA              |      |                  | 0.4 |      |  |

|                                                         | output                                 | INTR output  | $V_{CC} = 4.75 V$ ,                     | IOL = 1 mA                            |      |                  | 0.4 | _ v  |  |

|                                                         | voltage                                | CLK OUT      | $V_{CC} = 4.75 V$ ,                     | I <sub>OL</sub> = 360 μA              |      |                  | 0.4 | 1    |  |

| V <sub>T+</sub>                                         | Clock positive-going threshold voltage |              |                                         |                                       | 2.7  | 3.1              | 3.5 | ٧    |  |

| V <sub>T</sub> –                                        | Clock negative-going threshold voltage |              |                                         |                                       | 1.5  | 1.8              | 2.1 | V    |  |

| V <sub>T+</sub> -V <sub>T-</sub> Clock input hysteresis |                                        |              |                                         | 0.6                                   | 1.3  | 2                | V   |      |  |

| I <sub>IH</sub>                                         | High-level input current               |              |                                         | · · · · · · · · · · · · · · · · · · · |      | 0.005            | 1   | μΑ   |  |

| IIL                                                     | Low-level input current                |              |                                         |                                       |      | -0.005           | 1   | μА   |  |

|                                                         | Off-state output current               |              | V <sub>O</sub> = 0                      |                                       |      |                  | -3  | μА   |  |

| loz                                                     |                                        |              | V <sub>O</sub> = 5 V                    |                                       |      |                  | 3   | ] #^ |  |

| lons                                                    | Short-current output current           | Output high  | V <sub>O</sub> = 0,                     | T <sub>A</sub> = 25 °C                | -4.5 | - 6              |     | mA   |  |

| lors                                                    | Short-circuit output current           | Output low   | V <sub>O</sub> = 5 V,                   | T <sub>A</sub> = 25°C                 | 9    | 16               |     | mA   |  |

| Icc                                                     | Supply current plus reference current  |              | V <sub>REF/2</sub> = open,<br>CS at 5 V | T <sub>A</sub> = 25°C,                |      | 1.1              | 1.8 | mA   |  |

| R <sub>REF/2</sub>                                      | Input resistance to reference ladder   |              | See Note 7                              |                                       | 2.5  | 8                |     | kΩ   |  |

| Ci                                                      | Input capacitance (control)            |              |                                         |                                       |      | 5                | 7.5 | pF   |  |

| Со                                                      | Output capacitance (DB)                |              |                                         |                                       | T    | 5                | 7.5 | pF   |  |

NOTE 7: Resistance is calculated from the current drawn from a 5-volt supply applied to pins 8 and 9.

operating characteristics over recommended operating free-air temperature,  $V_{CC}=5$  V,  $V_{REF/2}=2.5$  V,  $f_{clock}=640$  kHz (unless otherwise noted)

|                  | PARAMETER Supply-voltage-variation error |         | TEST CONDITIONS                                          |                        | MIN | TYP†   | MAX   | UNIT            |

|------------------|------------------------------------------|---------|----------------------------------------------------------|------------------------|-----|--------|-------|-----------------|

|                  |                                          |         | V <sub>CC</sub> = 4.5 V to 5.5 V, See Note 8             |                        |     | ± 1/16 | ± 1/8 | LSB             |

|                  | Total adversed some                      | ADC0801 | With full-scale adjust, See Notes 8 and 9                |                        |     | ± 1/4  | LSB   |                 |

|                  | Total adjusted error                     | ADC0803 |                                                          | See Notes 6 and 9      |     |        | ± 1/2 | LOB             |

|                  | Total upadjusted error                   | ADC0802 | $V_{REF/2} = 2.5 V$ ,                                    | See Notes 8 and 9      |     |        | ± 1/2 | LSB             |

|                  |                                          | ADC0805 | VREF/2 open,                                             | See Notes 8 and 9      | T   |        | ± 1   | LSB             |

|                  | DC common-mode error                     |         | See Note 8 and 9                                         |                        |     | ± 1/16 | ± 1/8 | LSB             |

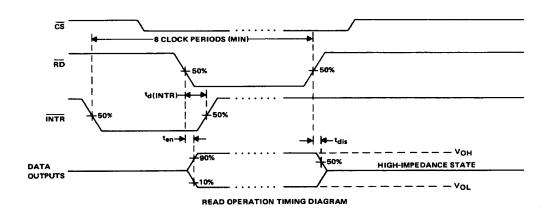

| ten              | Output enable time                       |         | C <sub>L</sub> = 100 pF                                  |                        |     | 135    | 200   | ns              |

| <sup>t</sup> dis | Output disable time                      |         | C <sub>L</sub> = 10 pF,                                  | R <sub>L</sub> = 10 kΩ |     | 125    | 200   | ns              |

| td(INTR)         | Delay time to reset INTR                 |         |                                                          |                        |     | 300    | 450   | ns              |

| tconv            | Conversion cycle time                    |         | f <sub>clock</sub> = 100 kHz to 1.46 MHz,<br>See Note 10 |                        | 66  |        | 73    | clock<br>cycles |

| CR               | Free-running conversion rate             |         | INTR connected to WR, CS at 0 V                          |                        |     |        | 8770  | conv/s          |

$^{\dagger}$ Ail typical values are at  $T_{A} = 25\,^{\circ}$ C.

NOTES: 8. These parameters are guaranteed over the recommended analog input voltage range.

9. All errors are measured with reference to an ideal straight line through the end-points of the analog-to-digital transfer characteristic.

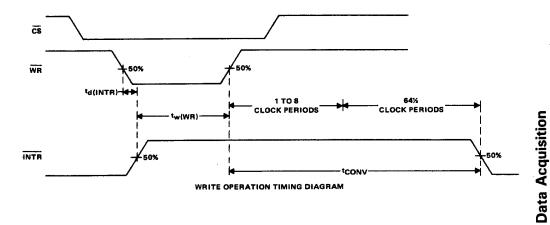

10. Although internal conversion is completed in 84 clock periods, a CS or WR low-to-high transition is followed by 1 to 8 clock periods before

Although internal conversion is completed in 84 clock periods, a CS or WR low-to-high transition is followed by 1 to 8 clock periods before

conversion starts. After conversion is completed, part of another clock period is required before a high-to-low transition of INTR completes the cycle.

1183

Data Acquisition

## PARAMETER MEASUREMENT INFORMATION

7

TEXAS

INSTRUMENTS

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

7-9

1183

#### PRINCIPLES OF OPERATION

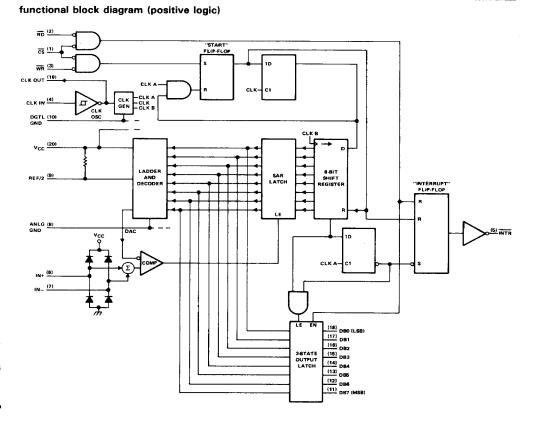

The ADC0801, ADC0802, ADC0803, and ADC0805 each contain a circuit equivalent to a 256-resistor network. Analog switches are sequenced by successive approximation logic to match an analog differential input voltage ( $V_{in} + -V_{in} - 1$ ) to a corresponding tap on the 256R network. The most-significant bit (MSB) is tested first. After eight comparisons (64 clock periods), an eight-bit binary code (1111 1111 = full scale) is transferred to an output latch and the interrupt ( $\overline{INTR}$ ) output goes low. The device can be operated in a free-running mode by connecting the  $\overline{INTR}$  output to the write ( $\overline{IWR}$ ) input and holding the conversion start ( $\overline{CS}$ ) input at a low level. To ensure start-up under all conditions, a low-level  $\overline{WR}$  input is required during the power-up cycle. Taking  $\overline{CS}$  low anytime after that will interrupt a conversion in process.

When the  $\overline{WR}$  input goes low, the internal successive approximation register (SAR) and eight-bit shift register are reset. As long as both  $\overline{CS}$  and  $\overline{WR}$  remain low, the analog-to-digital converter will remain in a reset state. One to eight clock periods after  $\overline{CS}$  or  $\overline{WR}$  makes a low-to-high transition, conversion starts.

When the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  inputs are low, the start flip-flop is set and the interrupt flip-flop and eight-bit register are reset. The next clock pulse transfers a logic high to the output of the start flip-flop. The logic high is ANDed with the next clock pulse placing a logic high on the reset input of the start flip-flop. If either  $\overline{\text{CS}}$  or  $\overline{\text{WR}}$  have gone high, the set signal to the start flip-flop is removed causing it to be reset. A logic high is placed on the D input of the eight-bit shift register and the conversion process is started. If the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  inputs are still low, the start flip-flop, the eight-bit shift register, and the SAR remain reset. This action allows for wide  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  inputs with conversion starting from one to eight clock periods after one of the inputs goes high.

When the logic high input has been clocked through the eight-bit shift register, completing the SAR search, it is applied to an AND gate controlling the output latches and to the D input of a flip-flop. On the next clock pulse, the digital word is transferred to the three-state output latches and the interrupt flip-flop is set. The output of the interrupt flip-flop is inverted to provide an INTR output that is high during conversion and low when the conversion is completed.

When a low is at both the  $\overline{CS}$  and  $\overline{RD}$  inputs, an output is applied to the DB0 through DB7 outputs and the interrupt flip-flop is reset. When either the  $\overline{CS}$  or  $\overline{RD}$  inputs return to a high state, the DB0 through DB7 outputs are disabled (returned to the high-impedance state). The interrupt flip-flop remains reset.

Texas Instruments