# Military Standard Products

# UT69RH051 MicroController

**Product Brief**

March 1995

# **FEATURES**

- ☐ Three 16-bit timer/counters

- High speed output

- Compare/capture

- Pulse width modulator

- Watchdog timer capabilities

- ☐ 256 bytes of on-chip data RAM

- ☐ 32 programmable I/O lines

- ☐ 7 interrupt sources

- Programmable serial channel with:

- Framing error detection

- Automatic address recognition

- ☐ TTL and CMOS compatible logic levels

- ☐ 64K external data and program memory space

- ☐ MCS®-51 fully compatible instruction set

- ☐ Flexible clock operation

- 1Hz to 20MHz with external clock

- 2MHz to 20MHz using internal oscillator with external crystal

- ☐ Radiation-hardened process and design; total dose irradiation testing MIL-STD-883 Method 1019

- Total dose: 1.0E6 rads(Si)

- Single event upset: <25.6E-6 errors/device-day

- Latchup immune

- ☐ Post-radiation AC/DC performance characteristics guaranteed to MIL-STD-883 Method 1019 testing at 1.0E6 rads (Si)

- ☐ Built on low-power, 1.2μ CMOS process

- ☐ Packaging options:

- 40-pin DIP

- 44-lead flatpack

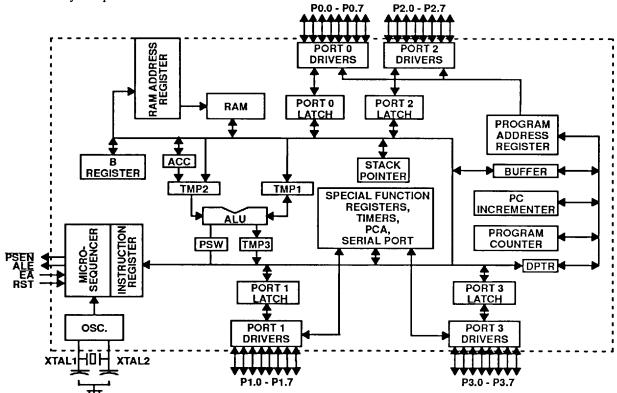

Figure 1. UT69RH051 MicroController Block Diagram

🕶 9343947 OOO4970 77T 🖿

#### 1.0 INTRODUCTION

The UT69RH051 is a radiation-tolerant 8-bit microcontroller that is pin equivalent to the Intel 8XC51FC microcontroller. The UT69RH051's static design allows operation from 1Hz to 20MHz. This product brief will describe hardware and software interfaces to the UT69RH051.

## 2.0 SIGNAL DESCRIPTION

V<sub>DD</sub>: +5V Supply voltage

VSS: Circuit Ground

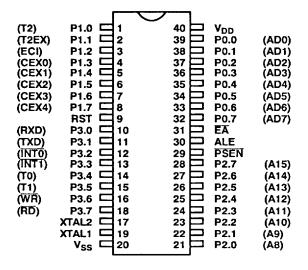

**Port 0 (P0.0 - P0.7):** Port 0 is an 8-bit port. Its pins are used as the low-order multiplexed address and data bus during accesses to external program and data memory. Port 0 pins use strong internal pullups when emitting 1's, and are TTL compatible.

Port 1 (P1.0 - P1.7): Port 1 is an 8-bit bidirectional I/O port with internal pullups. The output buffers can drive TTL loads. When the Port 1 pins have 1's written to them, they are pulled high by the internal pullups and can be used as inputs in this state. As inputs, any pins that are externally pulled low will source current because of the pullups. In addition, Port 1 pins have the alternate uses shown in table 1.

Port 2 (P2.0 - P2.7): Port 2 is an 8-bit port. Its pins are used as the high-order address bus during accesses to external Program Memory and during accesses to external Data Memory that uses 16-bit addresses (i.e., MOVX@DPTR). It uses strong internal pullups when emitting 1's in this mode. During operations that do not require a 16-bit address, Port 2 emits the contents of the P2 Special Function Registers (SFR). The pins have internal pullups and can drive TTL loads.

Port 3 (p3.0 - p3.7): Port3 is an 8-bit bidirectional I/O port with internal pullups. The output buffers can drive TTL loads. When the Port 3 pins have 1's written to them, they are pulled high by the internal pullups and can be used as inputs in this state. As inputs, any pins that are externally pulled low will source current because of the pullups. In addition, Port 3 pins have the alternate uses shown in table 2.

Table 1. Port 1 Alternate Functions

| Port<br>Pin | Alternate<br>Name | Alternate Function                                           |

|-------------|-------------------|--------------------------------------------------------------|

| P1.0        | T2                | External clock input to Timer/<br>Counter 2                  |

| P1.1        | T2EX              | Timer/Counter 2 Capture/Reload trigger and direction control |

| P1.2        | ECI               | External count input to PCA                                  |

| P1.3        | CEX0              | External I/O for PCA capture/<br>compare Module 0            |

| P1.4        | CEX1              | External I/O for PCA capture/<br>compare Module 1            |

| P1.5        | CEX2              | External I/O for PCA capture/<br>compare Module 2            |

| P1.6        | CEX3              | External I/O for PCA capture/<br>compare Module 3            |

| P1.7        | CEX4              | External I/O for PCA capture/<br>compare Module 4            |

**Table 2. Port 3 Alternate Functions**

| Port<br>Pin | Alternate<br>Name | Alternate Function                |

|-------------|-------------------|-----------------------------------|

| P3.0        | RXD               | Serial port input                 |

| P3.1        | TXD               | Serial port output                |

| P3.2        | ĪNT0              | External interrupt 0              |

| P3.3        | ĪNTĪ              | External interrupt 1              |

| P3.4        | ТО                | External clock input for Timer 0  |

| P3.5        | T1                | External clock input for Timer 1  |

| P3.6        | WR                | External Data Memory write strobe |

| P3.7        | RD                | External Data Memory read strobe  |

RST: Reset Input. A high on this input for one oscillator period while the oscillator is running resets the device. All ports and SFRs reset to their default conditions. Internal data memory is undefined after reset. Program execution begins within 12 oscillator periods (one machine cycle) after the RST signal is brought low. RST contains an internal pulldown resistor to allow implementing power-up reset with only an external capacitor.

ALE: Address Latch Enable. The ALE output is a pulse for latching the low byte of the address during accesses to external memory. In normal operation the ALE pulse is output every sixth oscillator cycle and may be used for external timing or clocking. However, during each access to external Data Memory (MOVX instruction), one ALE pulse is skipped.

PSEN: Program Store Enable. This active low signal is the read strobe to the external program memory. PSEN is activated every sixth oscillator cycle except that two PSEN activations are skipped during external data memory accesses.

$\overline{EA}$ : External Access Enable. This pin should be strapped to  $V_{SS}$  (Ground) for the UT69RH051.

XTAL1: Input to the inverting oscillator amplifier.

XTAL2: Output from the inverting oscillator amplifier.

Figure 2. UT69RH051 Pin Connections

#### 2.1 Hardware/Software Interface

# 2.1.1 Memory

The UT69RH051 has a separate address space for Program and Data Memory. Internally the UT69RH051 contains 256 bytes of Data Memory. It can address up to 64Kbytes of external Data Memory and 64Kbytes of external Program Memory.

# 2.1.1.1 Program Memory

There is no internal program memory in the UT69RH051. All program memory is accessed as external through ports P0 and P2. The  $\overline{EA}$  pin must be tied to  $V_{SS}$  (ground) to enable access to external locations  $0000_H$  through  $7FFF_H$ .

### 2.1.1.2 Data Memory

The UT69RH051 implements 256 bytes of internal data RAM. The upper 128 bytes of this RAM occupy a parallel address space to the SFRs. The CPU determines if the internal access to an address above 7FH is to the upper 128 bytes of RAM or to the SFR space by the addressing mode of the instruction. If direct addressing is used, the access is to the SFR space. If indirect addressing is used, the access is to the internal RAM. Stack operations are indirectly addressed so the upper portion of RAM can be used as stack space. Figure 3 shows the organization of the internal Data Memory.

The first 32 bytes are reserved for four register banks of eight bytes each. The processor uses one of the four banks as its working registers depending on the RS1 and RS0 bits in the PSW SFR. At reset, bank 0 is selected. If four register banks are not required, use the unused banks as general purpose scratch pad memory. The next 16 bytes (128 bits) are individually bit addressable. The remaining bytes are byte addressable and can be used as general purpose scratch pad memory. For addresses 0 - 7FH, use either direct or indirect addressing. For addresses larger than 7FH, use only indirect addressing.

In addition to the internal Data Memory, the processor can access 64 Kbytes of external Data Memory. The MOVX instruction accesses external Data Memory.

# 2.1.2 Special Function Registers

Table 3 contains the SFR memory map. Unoccupied addresses are not implemented on the device. Read accesses to these addresses will return unknown values and write accesses will have no effect.

Figure 3. Internal Data Memory Organization

了。我们就是一个人的一个人,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就 "我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人

# 2.1.3 Reset

The reset input is the RST pin. To reset, hold a the RST pin high for a minimum of 24 oscillator period while the oscillator is running. The CPU generates an internal reset from the external signal. The ports pins are driven to the reset state as soon as a valid high is detected on the RST pin.

While RST is high, <u>PSEN</u>, ALE, and the port pins are pulled weakly high. All SFRs are reset to their reset values as shown in table 3. The internal Data Memory content is indeterminate.

The processor will begin operation one machine cycle after the RST line is brought low. A memory access occurs immediately after the RST line is brought low, but the data is not brought into the processor. The memory access repeats on the next machine cycle and actual processing begins at that time.

### 2.1.4 Instruction Set

The instruction set for the UT69RH051 is compatible to the Intel MCS-51 instruction set used on the 8XC51FC.

**Table 3. SFR Memory Registers**

| F8         |                   | CH<br>00000000     | CCAP0H<br>XXXXXXXX  | CCAP1H<br>XXXXXXXX  | CCAP2H<br>XXXXXXXX  | CCAP3H<br>XXXXXXXX  | CCAP4H<br>XXXXXXXX  |                  | FF |

|------------|-------------------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|------------------|----|

| F0         | B<br>00000000     |                    |                     |                     |                     |                     |                     |                  | F7 |

| E8         |                   | CL<br>00000000     | CCAP0L<br>XXXXXXXX  | CCAP1L<br>XXXXXXXX  | CCAP2L<br>XXXXXXXX  | CCAP3L<br>XXXXXXXX  | CCAP4L<br>XXXXXXXX  |                  | EF |

| E0         | ACC<br>00000000   |                    | \ <u>-</u>          |                     |                     |                     |                     |                  | E7 |

| D8         | CCON<br>00X00000  | CMOD<br>OOXXX000   | CCAPM0<br>X00000000 | CCAPM1<br>X00000000 | CCAPM2<br>X00000000 | CCAPM3<br>X00000000 | CCAPM4<br>X00000000 |                  | DF |

| D0         | PSW<br>00000000   |                    |                     |                     |                     |                     |                     |                  | D7 |

| C8         | T2CON<br>00000000 | T2MOD<br>XXXXXXX00 | RCAP2L<br>00000000  | RCAP2H<br>00000000  | TL2<br>00000000     | TH2<br>00000000     |                     |                  | CF |

| <b>C</b> 0 |                   |                    |                     |                     |                     |                     |                     |                  | C7 |

| B8         | IP<br>X0000000    | SADEN<br>00000000  |                     |                     |                     |                     |                     | -                | BF |

| В0         | P3<br>11111111    |                    |                     |                     |                     |                     |                     | IPH<br>X00000000 | B7 |

| A8         | IE<br>00000000    | SADDR<br>00000000  |                     |                     |                     |                     |                     |                  | AF |

| <b>A</b> 0 | P2<br>11111111    |                    |                     |                     |                     |                     |                     |                  | A7 |

| 98         | SCON<br>00000000  | SBUF<br>XXXXXXXX   |                     |                     |                     |                     |                     |                  | 9F |

| 90         | P1<br>11111111    |                    |                     |                     |                     |                     |                     |                  | 97 |

| 88         | TCON<br>00000000  | TMOD<br>00000000   | TL0<br>00000000     | TL1<br>00000000     | TH0<br>00000000     | TH1<br>00000000     |                     |                  | 8F |

| 80         | P0<br>11111111    | SP<br>00000111     | DPL<br>00000000     | DPH<br>00000000     |                     |                     |                     | PCON<br>00XX00XX | 87 |

Notes:

1. Values shown are the reset values of the registers.

2. X = undefined.

### 3.0 RADIATION HARDNESS

The UT69RH051 incorporates special design and layout features which allow operation in high-level radiation environments. UTMC has developed special low-temperature processing techniques designed to enhance the total-dose radiation hardness of both the gate oxide and the field oxide while maintaining the

circuit density and reliability. For transient radiation hardness and latchup immunity, UTMC builds all radiation-hardened products on epitaxial wafers using an advanced twin-tub CMOS process. In addition, UTMC pays special attention to power and ground distribution during the design phase, minimizing dose-rate upset caused by rail collapse.

# RADIATION HARDNESS DESIGN SPECIFICATIONS 1

| PARAMETER          | CONDITION                         | MINIMUM | UNIT                        |

|--------------------|-----------------------------------|---------|-----------------------------|

| Total Dose         | +25°C per MIL-STD-883 Method 1019 | 1.0E6   | rads(Si)                    |

| Dose Rate Upset    | ≤ 4µs pulsewidth                  | 1.0E8   | rads(Si)/sec                |

| Dose Rate Survival | 20ns pulsewidth                   | 1.0E10  | rads(Si)/sec                |

| LET Threshold      | -55°C to +125°C                   | 36      | MeV-<br>cm <sup>2</sup> /mg |

| Neutron Fluence    | 1MeV equivalent                   | 1.0E14  | n/cm <sup>2</sup>           |

#### Note:

# 4.0 ABSOLUTE MAXIMUM RATINGS 1

(Referenced to V<sub>SS</sub>)

| SYMBOL           | PARAMETER                                         | LIMITS                      | UNITS |

|------------------|---------------------------------------------------|-----------------------------|-------|

| $V_{ m DD}$      | DC Supply Voltage                                 | -0.5 to 7.0                 | V     |

| V <sub>I/O</sub> | Voltage on Any Pin                                | -0.5 to V <sub>DD</sub> +3V | V     |

| T <sub>STG</sub> | Storage Temperature                               | -65 to +150                 | °C    |

| P <sub>D</sub>   | Maximum Power Dissipation                         | 750                         | mW    |

| $T_{J}$          | Maximum Junction Temperature                      | 175                         | °C    |

| $\Theta_{ m JC}$ | Thermal Resistance, Junction-to-Case <sup>2</sup> | 10                          | °C/W  |

| I <sub>I</sub>   | DC Input Current                                  | ± 10                        | mA    |

#### Notes:

2. Test per MIL-STD-883, Method 1012.

<sup>1.</sup> The UT69RH051 will not latchup during radiation exposure under recommended operating conditions.

<sup>1.</sup> Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 6.0 DC ELECTRICAL CHARACTERISTICS (Pre/Post-Radiation)\*

$V_{DD} = 5.0V \pm 10\%$ ; TA = -55°C < T<sub>C</sub> < +125°C)

| SYMBOL            | PARAMETER                                                             | CONDITION                     | MINIMUM | MAXIMUM              | UNIT |

|-------------------|-----------------------------------------------------------------------|-------------------------------|---------|----------------------|------|

| V <sub>IL</sub>   | Low-level Input Voltage                                               |                               | -0.5    | .8                   | V    |

| $V_{\mathrm{IH}}$ | High-level Input Voltage<br>(except XTAL2, RST, EA)                   |                               | 2.0     | V <sub>DD</sub> +0.3 | V    |

| $V_{IH1}$         | High-level Input Voltage<br>(XTAL, RST)                               |                               | 3.85    | V <sub>DD</sub> +0.3 | V    |

| V <sub>OL</sub>   | Low-level Output Voltage <sup>1</sup>                                 | $I_{OL} = 100\mu A$           |         | 0.3                  | V    |

|                   | (Ports 1, 2 and 3)                                                    | $I_{OL} = 1.6$ mA             |         | 0.45                 | V    |

|                   |                                                                       | $I_{OL} = 3.5 \text{mA}$      |         | 1.0                  | V    |

| V <sub>OL1</sub>  | Low-level Output Voltage <sup>1</sup>                                 | $I_{OL} = 200\mu A$           |         | 0.3                  | V    |

|                   | (Port 0, ALE/PROG, PŠEN)                                              | $I_{OL} = 3.2 \text{mA}$      |         | 0.45                 | V    |

|                   |                                                                       | $I_{OL} = 7.0 \text{mA}$      |         | 1.0                  | V    |

| $V_{OH}$          | High-level Output Voltage<br>(Ports 1, 2, and 3<br>ALE/PROG and PSEN) | $I_{OH} = -10\mu A$           | 4.2     |                      | V    |

|                   |                                                                       | $I_{OH} = -30\mu A$           | 3.8     |                      | V    |

|                   |                                                                       | $I_{OH} = -60\mu A$           | 3.0     |                      | V    |

| V <sub>OH1</sub>  | High-level Output Voltage                                             | $I_{OH} = -200\mu A$          | 4.2     |                      | V    |

|                   | (Port 0 in External Bus Mode)                                         | $I_{OH} = -3.2 \text{mA}$     | 3.8     |                      | V    |

|                   |                                                                       | $I_{OH} = -7.0 \text{mA}$     | 3.0     |                      | V    |

| I <sub>IL</sub>   | Logical 0 Input Current<br>(Ports 1, 2, and 3)                        | $V_{\rm IN} = 0.45 V$         |         | -50                  | μА   |

| ILI               | Input Leakage Current (Port 0)                                        | $V_{IN} = V_{IL}$ or $V_{IH}$ |         | ±10                  | μА   |

| $I_{\mathrm{TL}}$ | Logical 1 to 0 Transition Current (Ports 1, 2, and 3)                 | $V_{IN} = 2V$                 |         | -650                 | μА   |

| C <sub>IO</sub>   | Pin Capacitance                                                       | @ 1MHZ, 25°C                  |         | 10                   | pF   |

| $I_{CC}$          | Power Supply Current:<br>(Running at 16MHz)                           | Note 2                        |         | 52                   | mA   |

### Notes:

Post-radiation performance guaranteed at 25°C per MIL-STD-883.

Under steady state (non-transient) conditions, I<sub>OL</sub> must be limited externally as follows: 10mA

Maximum IOL per port pin: Maximum IOL per 8-bit port-

26mA Port 0:

Ports 1, 2, & 3: Maximum total IOL for all output pins:

15mA 71mA

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

2. See figures 4, 5, and 6 for test conditions.

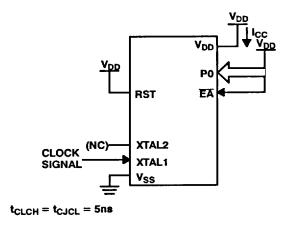

$\begin{tabular}{ll} Figure 4. I_{DD} Test Condition, Active Mode \\ All other pins disconnected \\ \end{tabular}$

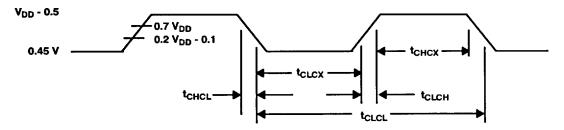

Figure 5. Clock Signal Waveform for  $I_{\rm CC}$  Tests in Active and Idle Modes  $t_{\rm CLCH} = t_{\rm CHCL} = 5 ns$

# 7.0 AC CHARACTERISTICS READ CYCLE (Post-Radiation)\*

$(V_{DD} = 5.0V \pm 10\%; -55^{\circ}C < T_{C} < +125^{\circ}C)$

| SYMBOL              | PARAMETER                          | MINIMUM                  | MAXIMUM                  | UNIT |

|---------------------|------------------------------------|--------------------------|--------------------------|------|

| t <sub>CLCL</sub>   | Clock Period                       | 50                       |                          | ns   |

| 1/t <sub>CLCL</sub> | Oscillator Frequency               |                          | 16                       | MHz  |

| tLHLL               | ALE Pulse Width                    | 2 t <sub>CLCL</sub> -40  |                          | ns   |

| t <sub>AVLL</sub>   | Address Valid to ALE Low           | t <sub>CLCL</sub> -40    |                          | ns   |

| t <sub>LLAX</sub>   | Address Hold after ALE Low         | t <sub>CLCL</sub> -30    |                          | ns   |

| t <sub>LLIV</sub>   | ALE Low to Valid Instruction In    |                          | 4 t <sub>CLCL</sub> -100 | ns   |

| t <sub>LLPL</sub>   | ALE Low to PSEN Low                | t <sub>CLCL</sub> -30    |                          | ns   |

| t <sub>PLPH</sub>   | PSEN Pulse Width                   | 3 t <sub>CLCL</sub> -45  |                          | ns   |

| t <sub>PLIV</sub>   | PSEN Low to Valid Instruction In   |                          | 3 t <sub>CLCL</sub> -105 | ns   |

| t <sub>PXIX</sub>   | Input Instruction Hold after PSEN  | 0                        |                          | ns   |

| t <sub>PXIZ</sub>   | Input Instruction Float After PSEN |                          | t <sub>CLCL</sub> -25    | ns   |

| t <sub>AVIV</sub>   | Address to Valid Instruction In    |                          | 5 t <sub>CLCL</sub> -105 | ns   |

| t <sub>PLAZ</sub>   | PSEN Low to Address Float          |                          | 10                       | ns   |

| t <sub>RLRH</sub>   | RD Pulse Width                     | 6 t <sub>CLCL</sub> -100 |                          | ns   |

| t <sub>WLWH</sub>   | WR Pulse Width                     | 6 t <sub>CLCL</sub> -100 |                          | ns   |

| t <sub>RLDV</sub>   | RD Low to Valid Data In            |                          | 5 t <sub>CLCL</sub> -165 | ns   |

| t <sub>RHDX</sub>   | Data Hold After RD                 | 0                        |                          | ns   |

| t <sub>RHDZ</sub>   | Data Float After RD                |                          | 2 t <sub>CLCL</sub> -60  | ns   |

| t <sub>LLDV</sub>   | ALE Low Valid Data In              |                          | 8 t <sub>CLCL</sub> -150 | ns   |

| t <sub>AVDV</sub>   | Address to Valid Data In           |                          | 9 t <sub>CLCL</sub> -165 | ns   |

| t <sub>LLWL</sub>   | ALE Low to RD or WR Low            | 3 t <sub>CLCL</sub> -50  | 3 t <sub>CLCL</sub> +50  | ns   |

| t <sub>AVWL</sub>   | Address Valid to WR Low            | 4 t <sub>CLCL</sub> -130 |                          | ns   |

| t <sub>QVWX</sub>   | Data Valid Before WR               | t <sub>CLCL</sub> -50    |                          | ns   |

| twHQX               | Data Hold After WR                 | t <sub>CLCL</sub> -50    |                          | ns   |

| t <sub>QVWH</sub>   | Data Valid to WR High              | 7 t <sub>CLCL</sub> -150 |                          | ns   |

| t <sub>RLAZ</sub>   | RD Low to Address Float            |                          | 0                        | ns   |

| twHLH               | RD or WR High to ALE High          | t <sub>CLCL</sub> -40    | t <sub>CLCL</sub> +40    | ns   |

Note:

Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019 at 1.0E6 rads(Si).

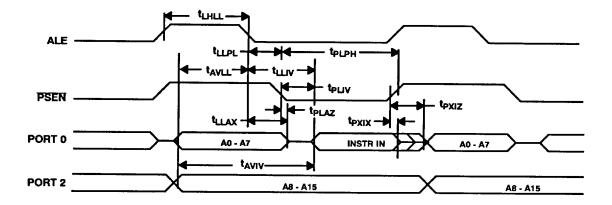

Figure 6. External Program Memory Read Timing Waveforms

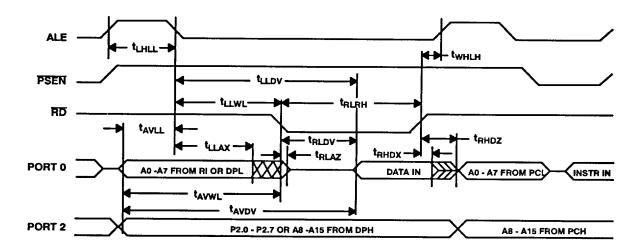

Figure 7. External Data Memory Read Cycle Waveforms

2. 2. 1915年 - 1

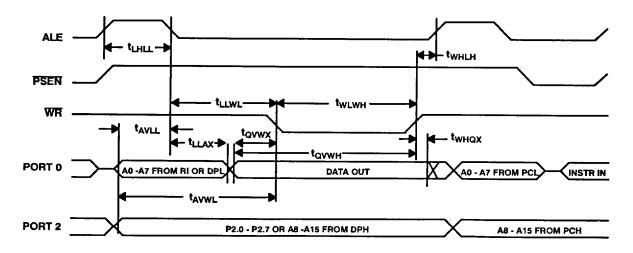

Figure 8. External Data Memory Write Cycle Waveforms

# 8.0 SERIAL PORT TIMING CHARACTERISTICS

$(V_{DD} = 5.0V \pm 10\%; -55^{\circ}C < T_{C} < +125^{\circ}C)$

| SYMBOL            | PARAMETER                                | MINIMUM                   | MAXIMUM                   | UNIT |

|-------------------|------------------------------------------|---------------------------|---------------------------|------|

| tXLXL             | Serial Port Clock Period                 | 12 t <sub>CLCL</sub> -10  | 12 t <sub>CLCL</sub> +10  | ns   |

| t <sub>QVXH</sub> | Output Data Setup to Clock Rising Edge   | 10 t <sub>CLCL</sub> -133 |                           | ns   |

| t <sub>XHQX</sub> | Output Data Hold after Clock Rising Edge | 2 t <sub>CLCL</sub> -70   |                           | ns   |

| t <sub>XHDX</sub> | Input Data Hold after Clock Rising Edge  | 0                         |                           | ns   |

| t <sub>XHDV</sub> | Clock Rising Edge to Input Data Valid    |                           | 10 t <sub>CLCL</sub> -133 | ns   |

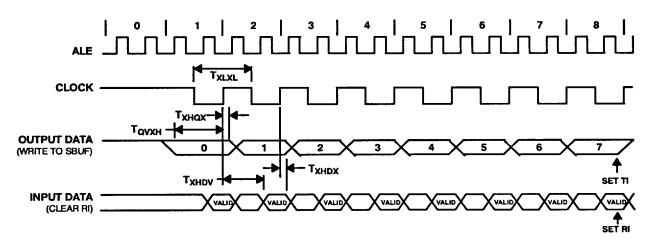

Figure 9. Serial Port Timing Waveforms

# 9.0 EXTERNAL CLOCK DRIVE TIMING CHARACTERISTICS

| SYMBOL              | PARAMETER            | MINIMUM | MAXIMUM | UNIT |

|---------------------|----------------------|---------|---------|------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency |         | 16      | MHz  |

| t <sub>CHCX</sub>   | High Time            | 20      |         | ns   |

| tCLCX               | Low Time             | 20      |         | ns   |

| t <sub>CLCH</sub>   | Rise Time            |         | 20      | ns   |

| t <sub>CHCL</sub>   | Fall Time            |         | 20      | ns   |

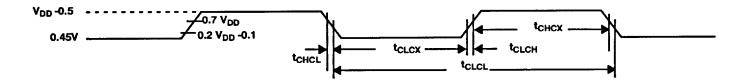

Figure 10. External Clock Drive Timing Waveforms

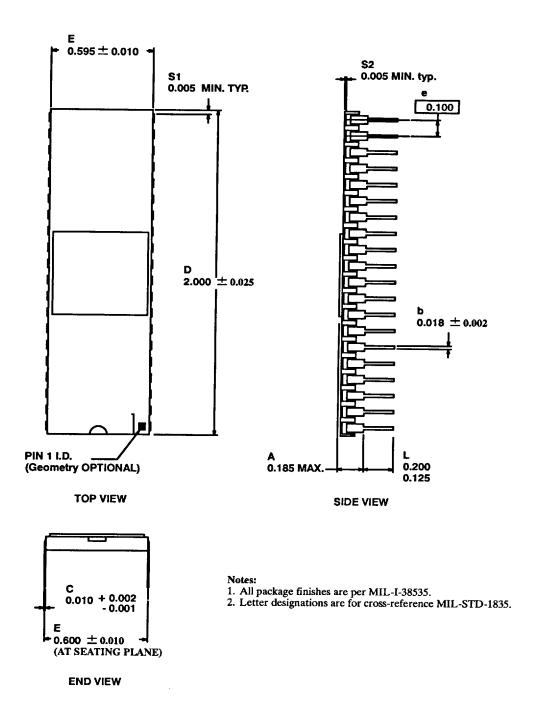

# 10.0 PACKAGING

Figure 11. 40-pin Side-Brazed DIP

# APPENDIX A Difference Between Intel 8XC51FC and UTMC69RH051

There are a few areas in which the UT69RH051 differs from the 8XC51FC. These differences will be covered in this section. In this discussion, 8XC51FC will be used generically to refer to all speed grades of the Intel 8XC51FC family, including the 20MHz 8XC51FC-1.

### 1.0 RESET

The UT69RH051 requires the RST input to be held high for at least 24 oscillator periods to guarantee the reset is completed in the chip. Also, the port pins are reset asynchronously as soon as the RST pin is pulled high. On the UT69RH051 all portions of the chip are reset synchronously when the RST pin is high during a rising edge of the input clock. When coming out of reset, the 8XC51FC takes 1 to 2 machine cycles to begin driving ALE and PSEN immediately after the RST is removed but the access during the first machine cycle after reset is ignored by the processor. The second cycle will repeat the access and processing will begin.

# 2.0 POWER SAVING MODES OF OPERATION

# 2.1 Idle Mode

Idle mode and the corresponding control bit in the PCON SFR have not been implemented in the UT69RH051. Setting the idle control bit will have no effect.

# 2.2 Power Down Mode

Power down mode and the corresponding control bit in the PCON register have not been implemented in the UT69RH051. Setting the power down control bit will have no effect. Also, the Power Off Flag in the PCON has not been implemented.

# 3.0 ON CIRCUIT EMULATION

The On Circuit Emulation mode of operation in the 8XC51FC has not been implemented in the UT69RH051.

# 4.0 OPERATING CONDITIONS

The operating voltage range for the 8XC51FC is  $5V \pm 20\%$ . The operating temperature range is  $0^{\circ}$  to  $70^{\circ}$ C. On the UT69RH051, the operating voltage range is  $5V \pm 10\%$ . The operating temperature range is  $-55^{\circ}$  to  $+125^{\circ}$ C.

# APPENDIX B Impact of External Program ROM

The 8051 family of microcontrollers, including the 8XC51FC, use ports 0 and 2 to access external memory. In implementations with external program memory, these two

ports are dedicated to the program ROM interface and can not be used as Input/Output ports. The UT69RH051 uses external program ROM, so ports 0 and 2 will not be available for I/O.

UT 692 HOSI-1-3-45 - PB

**343947 0004983 328**