#### **Features and Benefits**

- Micro-power latch operation

- 1.65 to 3.5 V battery operation

- Push-pull output eliminates the need for an external pullup resistor

- User configured, internally or externally controlled sample and sleep periods

- Floating the two clock pins results in the use of a fixed sampling clock internal to the sensor

- Toggling the clock pins allows the user to control the sampling and sleep times of the sensor for extreme low power operation

- External control of the clock pins allows the user to implement synchronous sampling of multiple sensors in direction detection systems

- Chopper stabilization

- Superior temperature stability

- Extremely low switchpoint drift

- Insensitive to physical stress

- Solid state reliability

- Small size

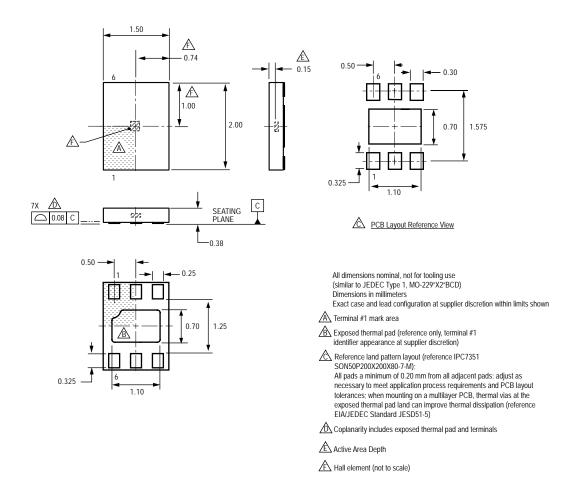

#### Package: 6-contact MLP/DFN (suffix EW)

$1.5 \text{ mm} \times 2 \text{ mm} \times 0.40 \text{ mm}$

Not to scale

#### **Description**

The A1174 is a micro-power, Hall-effect latch for use in portable devices that employ rotational detection systems, and have a power supply voltage between 1.65 and 3.5 V. The device has a single push-pull output structure and requires no external pull-up resistor for reliable operation.

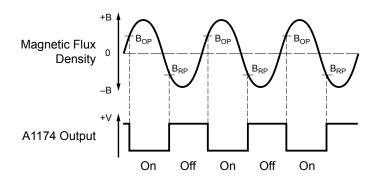

When a sufficient positive magnetic field is present on the device, the device output transitions to the low state and is latched in this state until a negative field of sufficient strength latches the device output into the high state. The latched output is ideal when using multiple sensors in rotational speed and direction sensing systems (for example, track ball and scroll bar systems in portable devices).

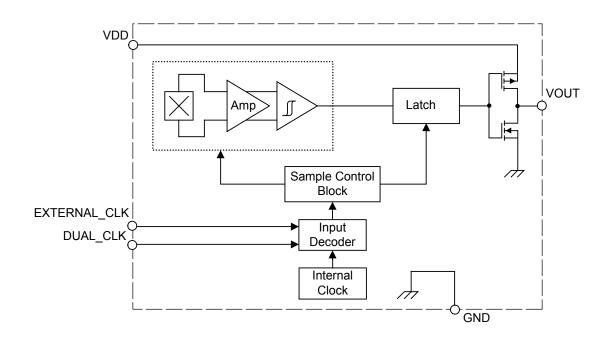

The device includes an innovative clocking scheme that satisfies the micro-power needs of almost any application, including track balls for PDAs and cell phones. Using the EXTERNAL\_CLK and DUAL\_CLK pins as described in this datasheet, the device can be set into various working modes.

In Dual Clock mode, the device switches between predefined slow and fast sampling rates. The average current consumption of the device is extremely low when rotation is not detected. In External Clock mode, the user sets the clock rate for the device to achieve the required on and off times for controlling average power. This user-determined clocking also helps to

Continued on the next page...

Figure 1. Timing diagram for output switching

#### **Description (continued)**

achieve synchronous clocking of multiple devices. This allows a defined phase relationship between the output transitions of each device in direction detection systems.

Improved stability is made possible through dynamic offset cancellation using chopper stabilization, which reduces the residual offset voltage normally caused by device overmolding, temperature dependencies, and thermal stress. Solid state reliability is provided by integrating, on a single silicon chip, a Hall-voltage generator, a small-signal amplifier, chopper stabilization, a latch, and a MOSFET output.

The device package is a 6-contact,  $1.5 \text{ mm} \times 2 \text{ mm}$ , 0.40 mm nominal overall height MLP/DFN, with exposed pad for enhanced thermal dissipation. It is lead (Pb) free, with 100% matte tin leadframe plating.

#### **Selection Guide**

| Part Number  | Packing*                    |  |

|--------------|-----------------------------|--|

| A1174EEWLT-T | 3000 pieces per 7-inch reel |  |

<sup>\*</sup>Contact Allegro® for additional packing options

## Pb

#### **Absolute Maximum Ratings**

| Characteristic                                       | Symbol                   | Notes   | Rating     | Units |

|------------------------------------------------------|--------------------------|---------|------------|-------|

| Forward Supply Voltage                               | $V_{DD}$                 |         | 5.0        | V     |

| Reverse Supply Voltage                               | $V_{RDD}$                |         | -0.3       | V     |

| Output Voltage                                       | V <sub>OUT</sub>         |         | 5.0        | V     |

| Reverse Output Voltage                               | V <sub>ROUT</sub>        |         | -0.3       | V     |

| EXTERNAL_CLK and DUAL_CLK Pins Input Voltage         | V <sub>IN</sub>          |         | 5.0        | V     |

| EXTERNAL_CLK and DUAL_CLK Pins Reverse Input Voltage | V <sub>RIN</sub>         |         | -0.3       | V     |

| Continuous Output Current                            | I <sub>OUT(sink)</sub>   |         | -1         | mA    |

|                                                      | I <sub>OUT(source)</sub> |         | 1          | mA    |

| Magnetic Flux Density*                               | В                        |         | Unlimited  | G     |

| Operating Ambient Temperature                        | T <sub>A</sub>           | Range E | -40 to 85  | °C    |

| Maximum Junction Temperature                         | T <sub>J</sub> (MAX)     |         | 165        | °C    |

| Storage Temperature                                  | T <sub>stg</sub>         |         | -65 to 170 | °C    |

<sup>\*1</sup>G = 0.1 mT (millitesla)

**Pin-out Diagram**

#### Terminal List

# VDD (1) (6) DUAL\_CLK NC (2) PAD (5) GND VOUT (3) (4) EXTERNAL\_CLK (Top View)

| Number | Name         | Function                                                                                           |

|--------|--------------|----------------------------------------------------------------------------------------------------|

| 1      | VDD          | Supply Voltage                                                                                     |

| 2      | NC           | No connect                                                                                         |

| 3      | VOUT         | Output                                                                                             |

| 4      | EXTERNAL_CLK | In combination with DUAL_CLK, allows external control of the device sampling period and duty cycle |

| 5      | GND          | Ground                                                                                             |

| 6      | DUAL_CLK     | In combination with EXTERNAL_CLK, drives the part in Dual Clock mode                               |

#### **Functional Block Diagram**

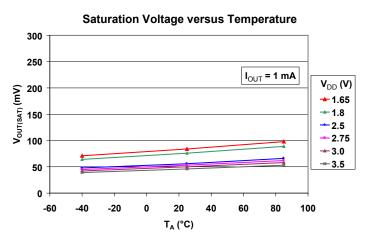

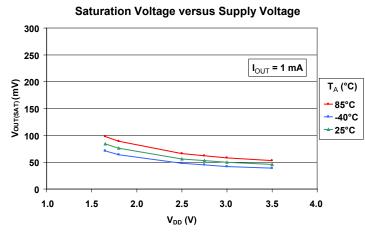

Operating Characteristics Valid over full operating voltage and ambient temperature ranges (unless otherwise specified)

| Characteristic                                   | Symbol                   | Test Conditions                                                                     | Min.                   | Typ.1                          | Max.                 | Unit |

|--------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|------------------------|--------------------------------|----------------------|------|

| Electrical Characteristics                       | •                        |                                                                                     |                        | •                              |                      |      |

| Supply Voltage <sup>2</sup>                      | .,                       | T <sub>A</sub> = 25°C                                                               | 1.65                   | _                              | 3.5                  | V    |

|                                                  | V <sub>DD</sub>          | –40°C ≥ T <sub>A</sub> ≥ 85°C                                                       | 1.8                    | _                              | 3.5                  | ٧    |

| Outside On Vallege                               | V <sub>OUT(SAT)</sub>    | NMOS on, I <sub>OUT</sub> = 1 mA                                                    | _                      | 100                            | 300                  | mV   |

| Output On Voltage                                | V <sub>OUT(HIGH)</sub>   | PMOS on, I <sub>OUT</sub> = 1 mA                                                    | V <sub>DD</sub> -300   | V <sub>DD</sub> -100           | _                    | mV   |

|                                                  | I <sub>DD(EN)</sub>      | Chip in awake state (enabled)                                                       | _                      | _                              | 2.0                  | mA   |

| Cumply Current                                   | I <sub>DD(DIS)</sub>     | Chip in sleep state (disabled)                                                      | _                      | -                              | 8.0                  | μA   |

| Supply Current                                   |                          | Normal Clock mode, V <sub>DD</sub> = 2.5 V                                          | _                      | _                              | 71                   | μΑ   |

|                                                  | I <sub>DD(AV)</sub>      | Normal Clock mode, V <sub>DD</sub> = 3.0 V                                          | _                      | _                              | 82                   | μA   |

| Internal Chopper Stabilization Clock Frequency   | f <sub>C</sub>           |                                                                                     | _                      | 200                            | _                    | kHz  |

| EXTERNAL_CLK and DUAL_CLK Pins Input Current     | I <sub>IN</sub>          | V <sub>EXTERNAL_CLK</sub> =V <sub>DD</sub> , V <sub>DUAL_CLK</sub> =V <sub>DD</sub> | _                      | 0.5                            | _                    | mA   |

| EXTERNAL_CLK and DUAL_CLK Pins Leakage Current   | I <sub>OFF</sub>         | V <sub>EXTERNAL_CLK</sub> =0V, V <sub>DUAL_CLK</sub> =0V                            | _                      | 0.02                           | _                    | μA   |

| Supply Slew Rate <sup>3</sup>                    | SR                       | t <sub>OFF</sub> = 100 ms                                                           | 0.1                    | _                              | _                    | V/ms |

| Normal Clock Mode Characteristics <sup>4</sup>   |                          |                                                                                     |                        |                                |                      |      |

| Normal Mode Awake Duration                       | t <sub>awake_norm</sub>  |                                                                                     | _                      | 25                             | 38                   | ms   |

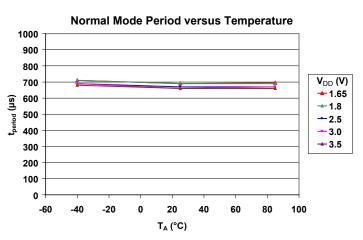

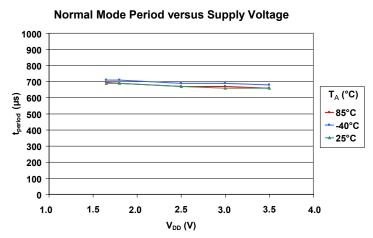

| Normal Mode Period                               | t <sub>period_norm</sub> |                                                                                     | _                      | 0.7                            | 1.05                 | ms   |

| External Clock Mode Characteristics <sup>4</sup> |                          |                                                                                     |                        |                                |                      |      |

| EXTERNAL_CLK and DUAL_CLK Pins Threshold         | V <sub>th(HIGH)</sub>    |                                                                                     | _                      | _                              | $0.75 \times V_{DD}$ | V    |

| EXTERNAL_CERTAIN DOAL_CERT IIIS THESHOLD         | $V_{th(LOW)}$            |                                                                                     | 0.25 × V <sub>DD</sub> | _                              | _                    | V    |

| External Clock Mode Awake Duration               | t <sub>awake_ext</sub>   | $V_{\text{EXTERNAL\_CLK}} > V_{\text{th(HIGH)}}$                                    | 38                     | _                              | _                    | ms   |

| External Clock Mode Period                       | t <sub>period_ext</sub>  | $V_{EXTERNAL\_CLK} > V_{th(HIGH)}$                                                  | 80                     | _                              | _                    | ms   |

| State Transition Delay <sup>5</sup>              | t <sub>delay_ext</sub>   |                                                                                     | _                      | 25                             | 38                   | ms   |

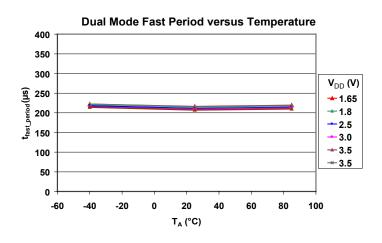

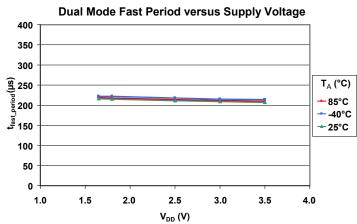

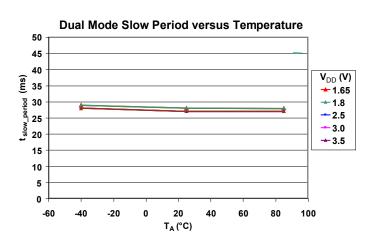

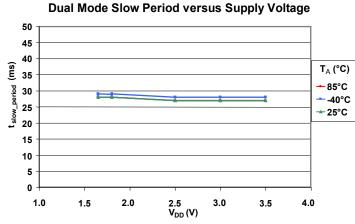

| Dual Clock Mode Characteristics <sup>4</sup>     | _                        |                                                                                     |                        |                                |                      |      |

| Dual Clock Mode Awake Duration                   | t <sub>awake_dual</sub>  |                                                                                     | _                      | 25                             | 38                   | ms   |

| Dual Clock Mode Fast Sampling Period             | t <sub>period_fast</sub> |                                                                                     | -                      | 8 ×<br>t <sub>awake_dual</sub> | _                    | ms   |

| Dual Clock Mode Slow Sampling Period             | t <sub>period_slow</sub> |                                                                                     | _                      | 28                             | -                    | ms   |

| Dual Clock Mode Timeout <sup>6</sup>             | t <sub>timeout</sub>     |                                                                                     | _                      | 100 × t <sub>period_slow</sub> | _                    | ms   |

| Magnetic Characteristics <sup>2</sup>            |                          |                                                                                     |                        |                                |                      |      |

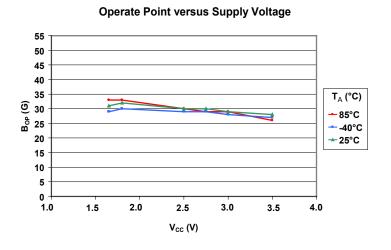

| Operate Point                                    | B <sub>OP</sub>          | South pole to device branded side                                                   | 5                      | 36                             | 55                   | G    |

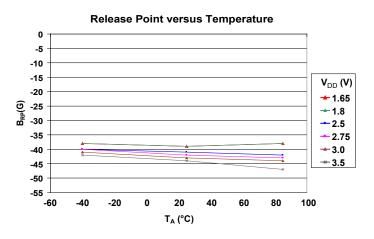

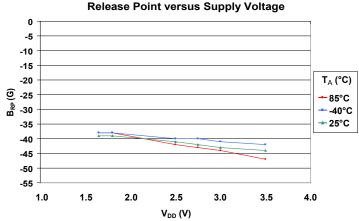

| Release Point                                    | B <sub>RP</sub>          | North pole to device branded side                                                   | <b>–</b> 55            | -36                            | <b>-</b> 5           | G    |

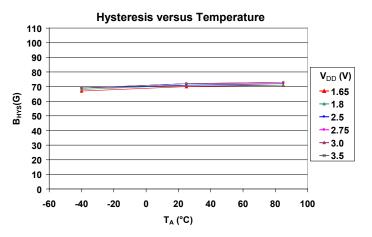

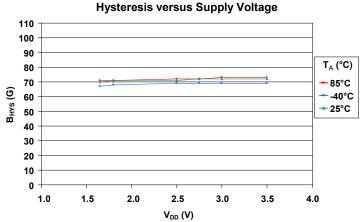

| Hysteresis                                       | B <sub>HYS</sub>         | B <sub>OP</sub> – B <sub>RP</sub>                                                   | _                      | 72                             | 110                  | G    |

<sup>&</sup>lt;sup>1</sup>Typical values are at T<sub>A</sub> = 25°C and V<sub>DD</sub> = 2.75 V. Performance may vary for individual units, within the specified maximum and minimum limits.

Allegro MicroSystems, Inc.

<sup>&</sup>lt;sup>2</sup>Magnetic operate and release points vary with supply voltage.

<sup>3</sup>If the device power supply is chopped, power-up slew rate dVDD / dt has to be adjusted to ensure correct functioning of the device. toFF is the time of the power cycle when  $V_{DD} < V_{DD}(min)$ .

<sup>&</sup>lt;sup>4</sup>Defined in the Functional Description section of this datasheet.

<sup>&</sup>lt;sup>5</sup>Time between external clock transition and resulting transition of the device between the awake and sleep states. See Functional Description section.

<sup>6</sup>lf no output transition is detected during the timeout interval, the device goes back into slow sampling. See Functional Description section.

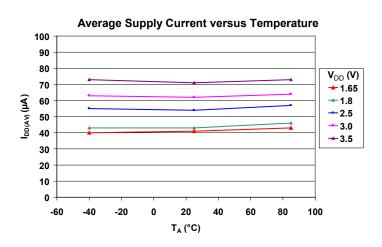

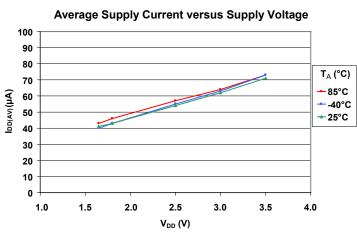

#### **Characteristic Performance**

#### **Operate Point versus Temperature** 75 70 65 60 $V_{DD}(V)$ 55 50 <del>----</del> 1.65 45 <del>--</del> 1.8 40 35 <del>---</del> 2.5 30 <del>-</del> 2.75 25 <del>\*</del> 3.0 20 **---** 3.5 15 10 5 0 -60 -40 -20 20 40 60 80 T<sub>A</sub> (°C)

## with Internally or Externally Controlled Sample and Sleep Periods for Track Ball and Scroll Wheel Applications

#### **Functional Description**

#### **Output State Operation**

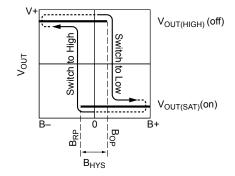

The output state (VOUT pin) of this device switches to low (on) when an incident magnetic field, perpendicular to the Hall sensor, exceeds the operate point threshold,  $B_{OP}$ . After turn-on, the output voltage is  $V_{OUT(SAT)}$  (see figure 2). When the magnetic field is reduced below the release point,  $B_{RP}$ , the device output goes high (off),  $V_{OUT(HIGH)}$ . The difference in the magnetic operate and release points is the hysteresis,  $B_{HYS}$ , of the device. This built-in hysteresis allows clean switching of the output even in the presence of external mechanical vibration and electrical noise.

Removal of the magnetic field leaves the device output latched low (on) if the last crossed switchpoint is  $B_{QP}$ , or latched high (off) if the last crossed switchpoint is  $B_{RP}$ .

Powering-on the device in the hysteresis range (less than  $B_{QP}$  and higher than  $B_{RP}$ ) gives an indeterminate output state. The correct state is attained after the first excursion beyond  $B_{QP}$  or  $B_{RP}$ .

#### **Micro-power Operation**

Micro-power operation of the device involves duty cycle control achieved by:

- powering all circuits in the chip and latching the device output state at the end of awake state periods, and

- turning off the bias current to most circuits in the chip and maintaining the device output state through sleep state periods.

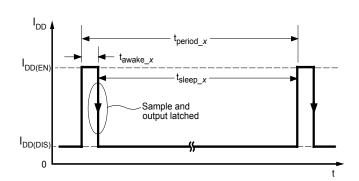

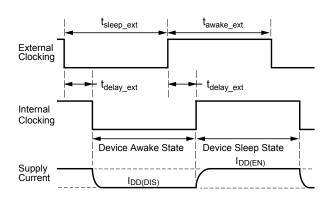

This is illustrated in figure 3. The awake state duration,  $t_{awake\_x}$ , is common in all defined modes of operation. The sleep state duration is set at a longer duration than the awake period in order to conserve power. During the sleep state, current consumption is insignificant (equal to  $I_{\rm DD(DIS)}$ ), but the device output does not switch in response to changing incident magnetic fields.

The device shows maximum current consumption,  $I_{DD(EN)}$ , during the awake state and minimal current consumption,  $I_{DD(DIS)}$ , during the sleep state. Average current,  $I_{DD(AV)}$ , for micro-power operation is derived from following formula:

$$I_{\rm DD(AV)} = \frac{I_{\rm DD(EN)} \times t_{\rm awake\_x} + I_{\rm DD(DIS)} \times t_{\rm sleep\_x}}{t_{\rm period\_x}} \quad \cdot \label{eq:Idde}$$

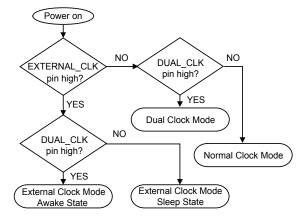

Three micro-power control modes are available:

- Normal Clock mode

- External Clock mode

- Dual Clock mode

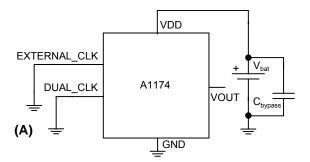

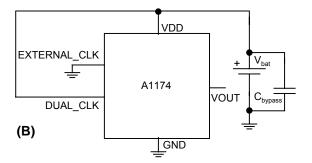

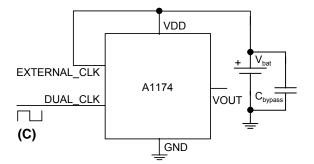

Selection of clock mode is determined by the configuration of the EXTERNAL\_CLK pin and the DUAL\_CLK pin, and applied voltages as illustrated in figure 4 and table 1.

**Normal Clock Mode** When both device clock pins are left floating or are grounded, the internal timing circuitry activates the sensor for  $t_{awake\_norm}$  and deactivates it for the remainder,  $t_{sleep}$ , of the duty cycle period,  $t_{period\_norm}$ . The short awake time

Figure 3. Micro-power behavior of the device

Figure 2. Device output switching logic

### Ultrasensitive Hall Effect Latch atrolled Sample and Sleep Periods

## with Internally or Externally Controlled Sample and Sleep Periods for Track Ball and Scroll Wheel Applications

allows stabilization prior to sensor sampling and data latching on the falling edge of the timing pulse. The output during the sleep time,  $t_{sleep}$ , is latched in the last sampled state.

**External Clock Mode** Applying a voltage greater than  $V_{th(HIGH)}$  to both clock pins puts the device into the awake state (without automatic cycling through the sleep state). The device uses the maximum defined supply current, reaching maximum power consumption.

Applying a voltage greater than  $V_{th(HIGH)}$  to the EXTERNAL\_CLK pin and a voltage lower than  $V_{th(LOW)}$  to the DUAL\_CLK pin puts the device into the sleep state (without automatic cycling through the awake state), and latches the device output in the output state determined during the prior awake state.

The duration of the awake and sleep periods can be controlled externally by applying a voltage greater than  $V_{th(HIGH)}$  to the

EXTERNAL\_CLK pin and applying an external clock to the DUAL\_CLK pin. The user can define the input sampling time and frequency to reach a target consumption current level, but the minimum sample time must remain longer than t<sub>awake\_ext</sub>. Note that the device should be periodically put into the awake state in order to update the device output state.

State Transition Delay, t<sub>ext\_delay</sub>, appears as the time between an external clock transition and the resulting transition of the device between the awake and the sleep state. This is illustrated in figure 5.

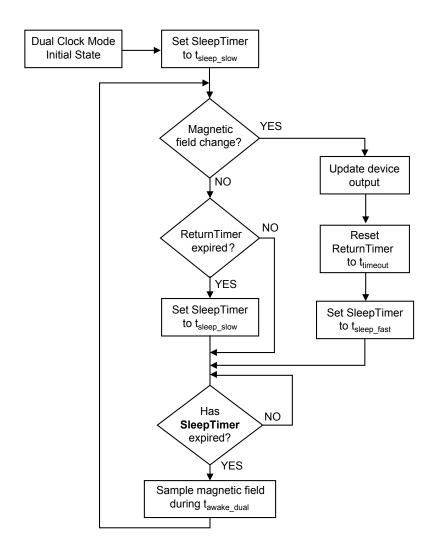

**Dual Clock Mode** When the EXTERNAL\_CLK pin is left floating, or is grounded, and the DUAL\_CLK pin is pulled to a voltage greater than V<sub>th(HIGH)</sub>, the device enters Dual Clock mode. Figure 6 gives an overview of the device operation algorithm in Dual Clock mode.

**Table 1. Clock Mode Selection Options**

| Connection       |              | Mode                        | Donovinski ovo                                                         |  |

|------------------|--------------|-----------------------------|------------------------------------------------------------------------|--|

| EXTERNAL_CLK Pin | DUAL_CLK Pin | Wode                        | Description                                                            |  |

| Low / NC         | Low / NC     | Normal Clock                | Awake and sleep state durations defined by device internal clock       |  |

| High             | High         | External Clock, Awake State | Awake and sleep state durations                                        |  |

| High             | Low          | External Clock, Sleep State | defined by external clock                                              |  |

| Low / NC         | High         | Dual Clock                  | Awake and sleep state durations defined by internal fast or slow clock |  |

High =  $V \ge V_{th(HIGH)}$ , Low =  $V \le V_{th(LOW)}$ , NC = no connect (float or connect to ground)

Figure 4. Clock mode selection algorithm; determined by clock pins connections in the application

Figure 5. External Clock mode clocking; t<sub>delay\_ext</sub> corresponding to the device transition delay into the awake or sleep states after an external clock transition

Initially, the device operates in the slow sampling state with a typical sleep time duration,  $t_{sleep\_slow}$ . The awake time duration,  $t_{awake}$ , is common in all defined modes of operation. After the first output state transition, the device switches into the fast sampling state, with a sleep time duration,  $t_{sleep\_fast}$ , of  $8 \times t_{awake\_dual}$ .

Fast input sampling ensures that the device does not miss any subsequent transitions of the incident magnetic field. This is advantageous in applications such as track ball monitoring, when the track ball can be rotated at very high speeds. If there is no output switching for the duration of the specified timeout,  $t_{timeout}$ , then the device switches back into the slow sampling state to conserve battery life in handheld devices.

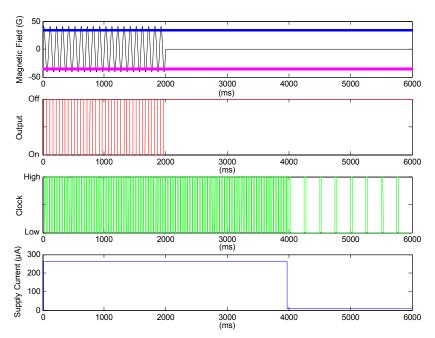

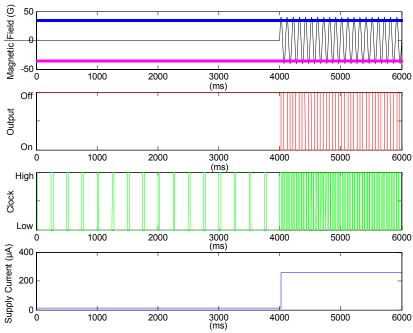

Figure 7 shows the case in which the field does not change within the  $t_{timeout}$  period. The behavior of the device in the presence of a rapidly changing magnetic field is shown in figure 8.

Figure 6. Dual Clock mode operation algorithm

Figure 7. Device output response in Dual Clock mode with no change of the magnetic field for the duration of  $t_{\text{timeout}}$

Figure 8. Device output response in Dual Clock mode with a rapid change of the magnetic field

## with Internally or Externally Controlled Sample and Sleep Periods for Track Ball and Scroll Wheel Applications

#### **Application Information**

It is strongly recommended that an external bypass capacitor be connected (in close proximity to the Hall sensor) between the supply and ground of the device to reduce both external noise and noise generated by the chopper stabilization technique (0.1 µF is a typical value). Additionally, it is recommended that, when possible, pins be tied to either the VDD pin or ground potential in order to improve the EMC performance of the device. However, it is feasible to float the EXTERNAL\_CLK and DUAL\_CLK pins in the application. In the case where these pins are floating. care should be taken to locate the device as far as possible from system antennas and transceivers.

The schematics on this page represent typical application circuits.

- (A) Device is working in Normal Clock mode. Power consumption is determined by device internal clock.

- (B) Device is working in Dual Clock mode. Power consumption is determined by device internal clock; frequent usage of device in fast sampling state.

- (C) Device is working in External Clock mode; externally-controlled power consumption.

- (D) Device is working in External Clock mode; high power consumption.

## Ultrasensitive Hall Effect Latch

## with Internally or Externally Controlled Sample and Sleep Periods for Track Ball and Scroll Wheel Applications

#### Package EW 6-Contact MLP/DFN

Copyright ©2008, Allegro MicroSystems, Inc.

The products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283; 5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719; 5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com